Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 4548                                                     |

| Number of Logic Elements/Cells | 90960                                                    |

| Total RAM Bits                 | 4520488                                                  |

| Number of I/O                  | 902                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 1508-BBGA, FCBGA                                         |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                    |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s90f1508c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section I–2 Altera Corporation

Stratix II devices are available in space-saving FineLine BGA® packages (see Tables 1–2 and 1–3).

| Table 1–2. Stratix II Package Options & I/O Pin Counts Notes (1), (2) |                                                                 |     |     |                           |                           |       |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|---------------------------|---------------------------|-------|--|

| Device                                                                | Device 484-Pin 484-Pin Hybrid FineLine BGA FineLine BGA BGA BGA |     |     | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |       |  |

| EP2S15                                                                | 342                                                             |     | 366 |                           |                           |       |  |

| EP2S30                                                                | 342                                                             |     | 500 |                           |                           |       |  |

| EP2S60 (3)                                                            | 334                                                             |     | 492 |                           | 718                       |       |  |

| EP2S90 (3)                                                            |                                                                 | 308 |     | 534                       | 758                       | 902   |  |

| EP2S130 (3)                                                           |                                                                 |     |     | 534                       | 742                       | 1,126 |  |

| EP2S180 (3)                                                           |                                                                 |     |     |                           | 742                       | 1,170 |  |

#### Notes to Table 1-2:

- (1) All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk11p, and clk11n) that can be used for data inputs.

- (2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as general-purpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

- (3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. Stratix II FineLine BGA Package Sizes                                                                   |         |         |         |         |         |         |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|--|--|--|

| Dimension         484 Pin         484-Pin<br>Hybrid         672 Pin         780 Pin         1,020 Pin         1,50 |         |         |         |         |         |         |  |  |  |

| Pitch (mm)                                                                                                         | 1.00    | 1.00    | 1.00    | 1.00    | 1.00    | 1.00    |  |  |  |

| Area (mm2)                                                                                                         | 529     | 729     | 729     | 841     | 1,089   | 1,600   |  |  |  |

| Length × width (mm × mm)                                                                                           | 23 × 23 | 27 × 27 | 27 × 27 | 29 × 29 | 33 × 33 | 40 × 40 |  |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

# Document Revision History

Table 1–6 shows the revision history for this chapter.

| Table 1–6. Document Revision History |                                                                                                                     |                    |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| Date and<br>Document<br>Version      | Changes Made                                                                                                        | Summary of Changes |  |  |

| May 2007, v4.2                       | Moved Document Revision History to the end of the chapter.                                                          | _                  |  |  |

| April 2006, v4.1                     | <ul> <li>Updated "Features" section.</li> <li>Removed Note 4 from Table 1–2.</li> <li>Updated Table 1–4.</li> </ul> | _                  |  |  |

| December 2005,<br>v4.0               | <ul><li>Updated Tables 1–2, 1–4, and 1–5.</li><li>Updated Figure 2–43.</li></ul>                                    | _                  |  |  |

| July 2005, v3.1                      | <ul> <li>Added vertical migration information, including<br/>Table 1–4.</li> <li>Updated Table 1–5.</li> </ul>      | _                  |  |  |

| May 2005, v3.0                       | <ul><li>Updated "Features" section.</li><li>Updated Table 1–2.</li></ul>                                            | _                  |  |  |

| March 2005,<br>v2.1                  | Updated "Introduction" and "Features" sections.                                                                     | _                  |  |  |

| January 2005,<br>v2.0                | Added note to Table 1–2.                                                                                            | _                  |  |  |

| October 2004,<br>v1.2                | Updated Tables 1-2, 1-3, and 1-5.                                                                                   | _                  |  |  |

| July 2004, v1.1                      | <ul><li>Updated Tables 1–1 and 1–2.</li><li>Updated "Features" section.</li></ul>                                   |                    |  |  |

| February 2004,<br>v1.0               | Added document to the Stratix II Device Handbook.                                                                   | _                  |  |  |

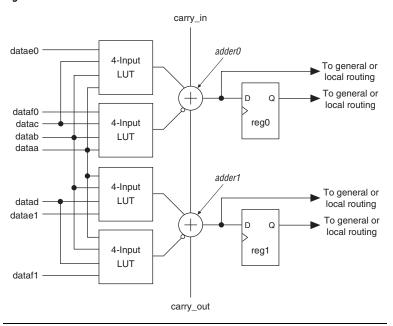

Figure 2-11. ALM in Arithmetic Mode

While operating in arithmetic mode, the ALM can support simultaneous use of the adder's carry output along with combinational logic outputs. In this operation, the adder output is ignored. This usage of the adder with the combinational logic output provides resource savings of up to 50% for functions that can use this ability. An example of such functionality is a conditional operation, such as the one shown in Figure 2–12. The equation for this example is:

$$R = (X < Y) ? Y : X$$

To implement this function, the adder is used to subtract 'Y' from 'X.' If 'X' is less than 'Y,' the carry\_out signal is '1.' The carry\_out signal is fed to an adder where it drives out to the LAB local interconnect. It then feeds to the LAB-wide syncload signal. When asserted, syncload selects the syncdata input. In this case, the data 'Y' drives the syncdata inputs to the registers. If 'X' is greater than or equal to 'Y,' the syncload signal is de-asserted and 'X' drives the data port of the registers.

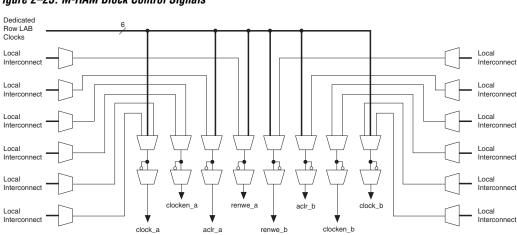

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M-RAM block registers (renwe, address, byte enable, datain, and output registers). The output register can be bypassed. The six labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 2–23.

Figure 2-23. M-RAM Block Control Signals

The R4, R24, C4, and direct link interconnects from adjacent LABs on either the right or left side drive the M-RAM block local interconnect. Up to 16 direct link input connections to the M-RAM block are possible from the left adjacent LABs and another 16 possible from the right adjacent LABs M-RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–24 shows an example floorplan for the EP2S130 device and the location of the M-RAM interfaces. Figures 2–25 and 2–26 show the interface between the M-RAM block and the logic array.

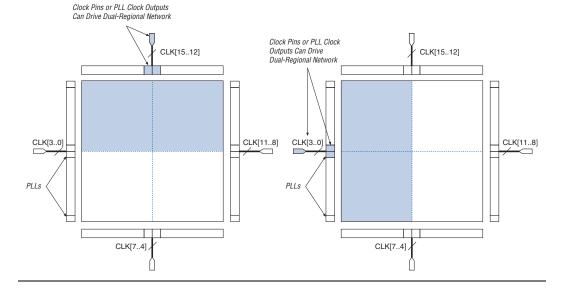

Figure 2-33. Dual-Regional Clocks

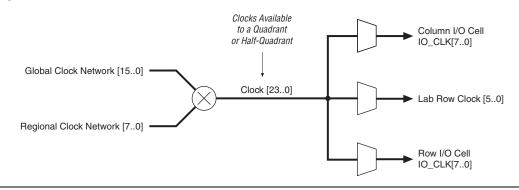

### Combined Resources

Within each quadrant, there are 24 distinct dedicated clocking resources consisting of 16 global clock lines and eight regional clock lines. Multiplexers are used with these clocks to form busses to drive LAB row clocks, column IOE clocks, or row IOE clocks. Another multiplexer is used at the LAB level to select three of the six row clocks to feed the ALM registers in the LAB (see Figure 2–34).

Figure 2-34. Hierarchical Clock Networks Per Quadrant

| Table 2- | Table 2–14. DQS & DQ Bus Mode Support (Part 2 of 2) Note (1) |                        |                        |                          |                             |  |  |  |

|----------|--------------------------------------------------------------|------------------------|------------------------|--------------------------|-----------------------------|--|--|--|

| Device   | Package                                                      | Number of<br>×4 Groups | Number of ×8/×9 Groups | Number of ×16/×18 Groups | Number of<br>×32/×36 Groups |  |  |  |

| EP2S90   | 484-pin Hybrid FineLine BGA                                  | 8                      | 4                      | 0                        | 0                           |  |  |  |

|          | 780-pin FineLine BGA                                         | 18                     | 8                      | 4                        | 0                           |  |  |  |

|          | 1,020-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |

|          | 1,508-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |

| EP2S130  | 780-pin FineLine BGA                                         | 18                     | 8                      | 4                        | 0                           |  |  |  |

|          | 1,020-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |

|          | 1,508-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |

| EP2S180  | 1,020-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |

|          | 1,508-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |

Notes to Table 2-14:

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

The Stratix II device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.

Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK[15..12]p feed the phase circuitry on the top of the device and clock pins CLK[7..4]p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits.

Figure 2–56 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

<sup>(1)</sup> Check the pin table for each DQS/DQ group in the different modes.

| Table 2–27. Document Revision History (Part 2 of 2) |                                                                                                                                                                                                                                                                                                                                                                                                               |                    |  |  |  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| Date and<br>Document<br>Version                     | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                  | Summary of Changes |  |  |  |

| January 2005,<br>v2.0                               | <ul> <li>Updated the "MultiVolt I/O Interface" and "TriMatrix Memory" sections.</li> <li>Updated Tables 2–3, 2–17, and 2–19.</li> </ul>                                                                                                                                                                                                                                                                       | _                  |  |  |  |

| October 2004,<br>v1.2                               | • Updated Tables 2–9, 2–16, 2–26, and 2–27.                                                                                                                                                                                                                                                                                                                                                                   | _                  |  |  |  |

| July 2004, v1.1                                     | <ul> <li>Updated note to Tables 2–9 and 2–16.</li> <li>Updated Tables 2–16, 2–17, 2–18, 2–19, and 2–20.</li> <li>Updated Figures 2–41, 2–42, and 2–57.</li> <li>Removed 3 from list of SERDES factor J.</li> <li>Updated "High-Speed Differential I/O with DPA Support" section.</li> <li>In "Dedicated Circuitry with DPA Support" section, removed XSBI and changed RapidIO to Parallel RapidIO.</li> </ul> | _                  |  |  |  |

| February 2004,<br>v1.0                              | Added document to the Stratix II Device Handbook.                                                                                                                                                                                                                                                                                                                                                             | _                  |  |  |  |

the Device & Pin Options dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix II devices, eliminating the need for external logic. For Stratix II devices, CRC is computed by the device during configuration and checked against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

### **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix II devices to perform error detection automatically. This error detection circuitry in Stratix II devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

### Software Interface

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the Device & Pin Options dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

# Document Revision History

Table 3–7 shows the revision history for this chapter.

| Table 3–7. Document Revision History (Part 1 of 2) |                                                                    |                    |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------|--------------------|--|--|--|--|

| Date and<br>Document<br>Version                    | Changes Made                                                       | Summary of Changes |  |  |  |  |

| May 2007, v4.2                                     | Moved Document Revision History section to the end of the chapter. | _                  |  |  |  |  |

|                                                    | Updated the "Temperature Sensing Diode (TSD)" section.             | _                  |  |  |  |  |

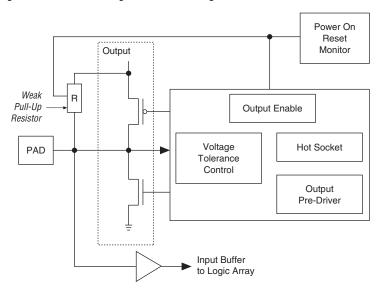

Figure 4–1. Hot Socketing Circuit Block Diagram for Stratix II Devices

The POR circuit monitors  $V_{CCINT}$  voltage level and keeps I/O pins tristated until the device is in user mode. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  is present to keep the I/O pins from floating. The 3.3-V tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  and/or  $V_{CCPD}$  are powered, and it prevents the I/O pins from driving out when the device is not in user mode. The hot socket circuit prevents I/O pins from internally powering  $V_{CCIO}$ ,  $V_{CCINT}$ , and  $V_{CCPD}$  when driven by external signals before the device is powered.

Figure 4–2 shows a transistor level cross section of the Stratix II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{\text{CCIO}}$  is powered before  $V_{\text{CCINT}}$  or if the I/O pad voltage is higher than  $V_{\text{CCIO}}$ . This also applies for sudden voltage spikes during hot insertion. There is no current path from signal I/O pins to  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  or  $V_{\text{CCPD}}$  during hot insertion. The  $V_{\text{PAD}}$  leakage current charges the 3.3-V tolerant circuit capacitance.

| Table 5–2. Maximum Duty Cycles in Voltage Transitions |                        |                        |                        |      |  |  |  |

|-------------------------------------------------------|------------------------|------------------------|------------------------|------|--|--|--|

| Symbol                                                | Parameter              | Condition              | Maximum<br>Duty Cycles | Unit |  |  |  |

| V <sub>I</sub>                                        | Maximum duty cycles    | V <sub>I</sub> = 4.0 V | 100                    | %    |  |  |  |

|                                                       | in voltage transitions | V <sub>I</sub> = 4.1 V | 90                     | %    |  |  |  |

|                                                       |                        | V <sub>I</sub> = 4.2 V | 50                     | %    |  |  |  |

|                                                       |                        | V <sub>I</sub> = 4.3 V | 30                     | %    |  |  |  |

|                                                       |                        | V <sub>I</sub> = 4.4 V | 17                     | %    |  |  |  |

|                                                       |                        | V <sub>I</sub> = 4.5 V | 10                     | %    |  |  |  |

### **Recommended Operating Conditions**

Table 5–3 contains the Stratix II device family recommended operating conditions.

| Table 5-           | Table 5–3. Stratix II Device Recommended Operating Conditions (Part 1 of 2) Note (1) |                                               |                 |                   |      |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------|-----------------------------------------------|-----------------|-------------------|------|--|--|--|--|

| Symbol             | Parameter                                                                            | Conditions                                    | Minimum         | Maximum           | Unit |  |  |  |  |

| $V_{\text{CCINT}}$ | Supply voltage for internal logic                                                    | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms (3) | 1.15            | 1.25              | V    |  |  |  |  |

| V <sub>CCIO</sub>  | Supply voltage for input and output buffers, 3.3-V operation                         | 100 μs $\leq$ risetime $\leq$ 100 ms (3), (6) | 3.135<br>(3.00) | 3.465<br>(3.60)   | V    |  |  |  |  |

|                    | Supply voltage for input and output buffers, 2.5-V operation                         | 100 μs ≤ risetime ≤ 100 ms (3)                | 2.375           | 2.625             | ٧    |  |  |  |  |

|                    | Supply voltage for input and output buffers, 1.8-V operation                         | 100 μs ≤ risetime ≤ 100 ms <i>(3)</i>         | 1.71            | 1.89              | ٧    |  |  |  |  |

|                    | Supply voltage for output buffers, 1.5-V operation                                   | 100 μs ≤ risetime ≤ 100 ms <i>(3)</i>         | 1.425           | 1.575             | V    |  |  |  |  |

|                    | Supply voltage for input and output buffers, 1.2-V operation                         | 100 μs ≤ risetime ≤ 100 ms <i>(3)</i>         | 1.14            | 1.26              | ٧    |  |  |  |  |

| V <sub>CCPD</sub>  | Supply voltage for pre-drivers as well as configuration and JTAG I/O buffers.        | 100 μs ≤ risetime ≤ 100 ms (4)                | 3.135           | 3.465             | V    |  |  |  |  |

| $V_{CCA}$          | Analog power supply for PLLs                                                         | 100 μs ≤ risetime ≤ 100 ms <i>(3)</i>         | 1.15            | 1.25              | V    |  |  |  |  |

| V <sub>CCD</sub>   | Digital power supply for PLLs                                                        | 100 μs ≤ risetime ≤ 100 ms (3)                | 1.15            | 1.25              | ٧    |  |  |  |  |

| Vı                 | Input voltage (see Table 5-2)                                                        | (2), (5)                                      | -0.5            | 4.0               | ٧    |  |  |  |  |

| Vo                 | Output voltage                                                                       |                                               | 0               | V <sub>CCIO</sub> | V    |  |  |  |  |

| Table 5-3. Stratix II Device Recommended Operating Conditions (Part 2 of 2) Note (1) |                                           |                      |             |     |    |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------|----------------------|-------------|-----|----|--|--|

| Symbol                                                                               | Parameter Conditions Minimum Maximum Unit |                      |             |     |    |  |  |

| $T_{J}$                                                                              | Operating junction temperature            | For commercial use   | 0           | 85  | °C |  |  |

|                                                                                      |                                           | For industrial use   | -40         | 100 | °C |  |  |

|                                                                                      |                                           | For military use (7) | <b>-</b> 55 | 125 | °C |  |  |

#### Notes to Table 5-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 μs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, your Stratix II device does not configure successfully. If your system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, you must hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

- (7) For more information, refer to the Stratix II Military Temperature Range Support technical brief.

### **DC Electrical Characteristics**

Table 5–4 shows the Stratix II device family DC electrical characteristics.

| Table 5-            | Table 5-4. Stratix II Device DC Operating Conditions (Part 1 of 2)       Note (1) |                                                 |              |         |         |         |      |  |  |

|---------------------|-----------------------------------------------------------------------------------|-------------------------------------------------|--------------|---------|---------|---------|------|--|--|

| Symbol              | Parameter                                                                         | Conditions                                      |              | Minimum | Typical | Maximum | Unit |  |  |

| I <sub>I</sub>      | Input pin leakage current                                                         | V <sub>I</sub> = V <sub>CCIOmax</sub> to 0 \    | <i>I (2)</i> | -10     |         | 10      | μА   |  |  |

| I <sub>OZ</sub>     | Tri-stated I/O pin leakage current                                                | $V_O = V_{CCIOmax}$ to 0                        | V (2)        | -10     |         | 10      | μА   |  |  |

| I <sub>CCINTO</sub> | V <sub>CCINT</sub> supply current                                                 | $V_{CCINT}$ supply current $V_{I}$ = ground, no |              |         | 0.25    | (3)     | Α    |  |  |

|                     | (standby)                                                                         | load, no toggling                               | EP2S30       |         | 0.30    | (3)     | Α    |  |  |

|                     |                                                                                   | inputs $T_J = 25^{\circ} C$                     | EP2S60       |         | 0.50    | (3)     | Α    |  |  |

|                     |                                                                                   |                                                 | EP2S90       |         | 0.62    | (3)     | Α    |  |  |

|                     |                                                                                   |                                                 | EP2S130      |         | 0.82    | (3)     | Α    |  |  |

|                     |                                                                                   |                                                 | EP2S180      |         | 1.12    | (3)     | Α    |  |  |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current                                                  | V <sub>I</sub> = ground, no                     | EP2S15       |         | 2.2     | (3)     | mA   |  |  |

|                     | (standby)                                                                         | load, no toggling                               | EP2S30       |         | 2.7     | (3)     | mA   |  |  |

|                     |                                                                                   | inputs<br>T <sub>.l</sub> = 25° C,              | EP2S60       |         | 3.6     | (3)     | mA   |  |  |

|                     |                                                                                   | $V_{CCPD} = 3.3V$                               | EP2S90       |         | 4.3     | (3)     | mA   |  |  |

|                     |                                                                                   |                                                 | EP2S130      |         | 5.4     | (3)     | mA   |  |  |

|                     |                                                                                   |                                                 | EP2S180      |         | 6.8     | (3)     | mA   |  |  |

| Table 5–34. Output Timing Measurement Methodology for Output Pins         Notes (1), (2), (3) |                           |               |               |                       |                     |                     |                       |

|-----------------------------------------------------------------------------------------------|---------------------------|---------------|---------------|-----------------------|---------------------|---------------------|-----------------------|

| I/O Standard                                                                                  |                           | Lo            | ading and     | Terminatio            | n                   |                     | Measurement<br>Point  |

|                                                                                               | <b>R</b> <sub>δ</sub> (Ω) | $R_D(\Omega)$ | $R_T(\Omega)$ | V <sub>CCIO</sub> (V) | V <sub>TT</sub> (V) | C <sub>L</sub> (pF) | V <sub>MEAS</sub> (V) |

| LVTTL (4)                                                                                     |                           |               |               | 3.135                 |                     | 0                   | 1.5675                |

| LVCMOS (4)                                                                                    |                           |               |               | 3.135                 |                     | 0                   | 1.5675                |

| 2.5 V (4)                                                                                     |                           |               |               | 2.375                 |                     | 0                   | 1.1875                |

| 1.8 V (4)                                                                                     |                           |               |               | 1.710                 |                     | 0                   | 0.855                 |

| 1.5 V (4)                                                                                     |                           |               |               | 1.425                 |                     | 0                   | 0.7125                |

| PCI (5)                                                                                       |                           |               |               | 2.970                 |                     | 10                  | 1.485                 |

| PCI-X (5)                                                                                     |                           |               |               | 2.970                 |                     | 10                  | 1.485                 |

| SSTL-2 Class I                                                                                | 25                        |               | 50            | 2.325                 | 1.123               | 0                   | 1.1625                |

| SSTL-2 Class II                                                                               | 25                        |               | 25            | 2.325                 | 1.123               | 0                   | 1.1625                |

| SSTL-18 Class I                                                                               | 25                        |               | 50            | 1.660                 | 0.790               | 0                   | 0.83                  |

| SSTL-18 Class II                                                                              | 25                        |               | 25            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V HSTL Class I                                                                            | 50                        |               | 50            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V HSTL Class II                                                                           | 25                        |               | 25            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.5-V HSTL Class I                                                                            | 50                        |               | 50            | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.5-V HSTL Class II                                                                           |                           |               | 25            | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.2-V HSTL with OCT                                                                           | 50                        |               |               | 1.140                 |                     | 0                   | 0.570                 |

| Differential SSTL-2 Class I                                                                   | 50                        |               | 50            | 2.325                 | 1.123               | 0                   | 1.1625                |

| Differential SSTL-2 Class II                                                                  | 25                        |               | 25            | 2.325                 | 1.123               | 0                   | 1.1625                |

| Differential SSTL-18 Class I                                                                  | 50                        |               | 50            | 1.660                 | 0.790               | 0                   | 0.83                  |

| Differential SSTL-18 Class II                                                                 | 25                        |               | 25            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.5-V Differential HSTL Class I                                                               | 50                        |               | 50            | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.5-V Differential HSTL Class II                                                              |                           |               | 25            | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.8-V Differential HSTL Class I                                                               | 50                        |               | 50            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V Differential HSTL Class II                                                              | 25                        |               | 25            | 1.660                 | 0.790               | 0                   | 0.83                  |

| LVDS                                                                                          |                           | 100           |               | 2.325                 |                     | 0                   | 1.1625                |

| HyperTransport                                                                                |                           | 100           |               | 2.325                 |                     | 0                   | 1.1625                |

| LVPECL                                                                                        |                           | 100           |               | 3.135                 |                     | 0                   | 1.5675                |

### Notes to Table 5–34:

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for  $V_{\text{MEAS}}$  at buffer output is  $0.5 \times V_{\text{CCIO}}.$

- (3) Input stimulus edge rate is 0 to  $V_{CC}$  in 0.2 ns (internal signal) from the driver preceding the I/O buffer.

- (4) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT}$  = 1.15 V with less than 30-mV ripple

- (5)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$

| Table 5-          | 36. Stratix II Performan                                                                                                        | ce Notes | (Part 3 of 6)                 | ) Note        | e (1)                       |                      |                      |                      |      |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|--|--|

|                   | Resources Used                                                                                                                  |          |                               |               | Performance                 |                      |                      |                      |      |  |  |

| Applications      |                                                                                                                                 | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |  |  |

| DSP               | 9 × 9-bit multiplier (5)                                                                                                        | 0        | 0                             | 1             | 430.29                      | 409.16               | 373.13               | 320.10               | MHz  |  |  |

| block             | 18 × 18-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |  |  |

|                   | 18 × 18-bit<br>multiplier (7)                                                                                                   | 0        | 0                             | 1             | 450.04                      | 428.08               | 391.23               | 335.12               | MHz  |  |  |

|                   | 36 × 36-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 250.00                      | 238.15               | 217.48               | 186.60               | MHz  |  |  |

|                   | 36 × 36-bit multiplier (6)                                                                                                      | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |  |  |

|                   | 18-bit, four-tap FIR filter                                                                                                     | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |  |  |

| Larger<br>designs | 8-bit,16-tap parallel<br>FIR filter                                                                                             | 58       | 0                             | 4             | 259.06                      | 240.61               | 217.15               | 185.01               | MHz  |  |  |

|                   | 8-bit, 1024-point,<br>streaming, three<br>multipliers and five<br>adders FFT function                                           | 2976     | 22                            | 9             | 398.72                      | 364.03               | 355.23               | 306.37               | MHz  |  |  |

|                   | 8-bit, 1024-point,<br>streaming, four<br>multipliers and two<br>adders FFT function                                             | 2781     | 22                            | 12            | 398.56                      | 409.16               | 347.22               | 311.13               | MHz  |  |  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function | 984      | 5                             | 3             | 425.17                      | 365.76               | 346.98               | 292.39               | MHz  |  |  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function   | 919      | 5                             | 4             | 427.53                      | 378.78               | 357.14               | 307.59               | MHz  |  |  |

| O. mahal                 | Downwater                                         | -3 Speed<br>Grade (2) |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | 11   |

|--------------------------|---------------------------------------------------|-----------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|------|

| Symbol                   | Parameter                                         | Min (4)               | Max   | Min (4)               | Max   | Min (5)           | Max   | Min (4)           | Max   | Unit |

| t <sub>MEGARC</sub>      | Synchronous read cycle time                       | 1,866                 | 2,774 | 1,866                 | 2,911 | 1,777<br>1,866    | 3,189 | 1,777<br>1,866    | 3,716 | ps   |

| t <sub>MEGAWERESU</sub>  | Write or read enable setup time before clock      | 144                   |       | 151                   |       | 165<br>165        |       | 192               |       | ps   |

| t <sub>MEGAWEREH</sub>   | Write or read enable hold time after clock        | 39                    |       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGABESU</sub>    | Byte enable setup time before clock               | 50                    |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGABEH</sub>     | Byte enable hold time after clock                 | 39                    |       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGADATAASU</sub> | A port data setup time before clock               | 50                    |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGADATAAH</sub>  | A port data hold time after clock                 | 243                   |       | 255                   |       | 279<br>279        |       | 325               |       | ps   |

| t <sub>MEGAADDRASU</sub> | A port address setup time before clock            | 589                   |       | 618                   |       | 677<br>677        |       | 789               |       | ps   |

| t <sub>MEGAADDRAH</sub>  | A port address hold time after clock              | 241                   |       | 253                   |       | 277<br>277        |       | 322               |       | ps   |

| t <sub>MEGADATABSU</sub> | B port setup time before clock                    | 50                    |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGADATABH</sub>  | B port hold time after clock                      | 243                   |       | 255                   |       | 279<br>279        |       | 325               |       | ps   |

| t <sub>MEGAADDRBSU</sub> | B port address setup time before clock            | 589                   |       | 618                   |       | 677<br>677        |       | 789               |       | ps   |

| t <sub>MEGAADDRBH</sub>  | B port address hold time after clock              | 241                   |       | 253                   |       | 277<br>277        |       | 322               |       | ps   |

| t <sub>MEGADATACO1</sub> | Clock-to-output delay when using output registers | 480                   | 715   | 480                   | 749   | 457<br>480        | 821   | 480               | 957   | ps   |

| t <sub>MEGADATACO2</sub> | Clock-to-output delay without output registers    | 1,950                 | 2,899 | 1,950                 | 3,042 | 1,857<br>1,950    | 3,332 | 1,950             | 3,884 | ps   |

| t <sub>MEGACLKL</sub>    | Minimum clock low time                            | 1,250                 |       | 1,312                 |       | 1,437<br>1,437    |       | 1,675             |       | ps   |

|                     |                   |                  | Minimu     | m Timing   | -3                    | -3<br>Speed<br>Grade<br>(4) | -4<br>Speed<br>Grade | -5             |      |

|---------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------------|----------------------|----------------|------|

| I/O Standard        | Drive<br>Strength | Parameter        | Industrial | Commercial | Speed<br>Grade<br>(3) |                             |                      | Speed<br>Grade | Unit |

| SSTL-18             | 4 mA              | t <sub>OP</sub>  | 909        | 953        | 1690                  | 1773                        | 1942                 | 2012           | ps   |

| Class I             |                   | t <sub>DIP</sub> | 929        | 975        | 1756                  | 1843                        | 2018                 | 2102           | ps   |

|                     | 6 mA              | t <sub>OP</sub>  | 914        | 958        | 1656                  | 1737                        | 1903                 | 1973           | ps   |

|                     |                   | t <sub>DIP</sub> | 934        | 980        | 1722                  | 1807                        | 1979                 | 2063           | ps   |

|                     | 8 mA              | t <sub>OP</sub>  | 894        | 937        | 1640                  | 1721                        | 1885                 | 1954           | ps   |

|                     |                   | t <sub>DIP</sub> | 914        | 959        | 1706                  | 1791                        | 1961                 | 2044           | ps   |

|                     | 10 mA             | t <sub>OP</sub>  | 898        | 942        | 1638                  | 1718                        | 1882                 | 1952           | ps   |

|                     |                   | t <sub>DIP</sub> | 918        | 964        | 1704                  | 1788                        | 1958                 | 2042           | ps   |

|                     | 12 mA<br>(1)      | t <sub>OP</sub>  | 891        | 936        | 1626                  | 1706                        | 1869                 | 1938           | ps   |

|                     |                   | t <sub>DIP</sub> | 911        | 958        | 1692                  | 1776                        | 1945                 | 2028           | ps   |

| SSTL-18<br>Class II | 8 mA              | t <sub>OP</sub>  | 883        | 925        | 1597                  | 1675                        | 1835                 | 1904           | ps   |

|                     |                   | t <sub>DIP</sub> | 903        | 947        | 1663                  | 1745                        | 1911                 | 1994           | ps   |

|                     | 16 mA             | t <sub>OP</sub>  | 894        | 937        | 1578                  | 1655                        | 1813                 | 1882           | ps   |

|                     |                   | t <sub>DIP</sub> | 914        | 959        | 1644                  | 1725                        | 1889                 | 1972           | ps   |

|                     | 18 mA             | t <sub>OP</sub>  | 890        | 933        | 1585                  | 1663                        | 1821                 | 1890           | ps   |

|                     |                   | t <sub>DIP</sub> | 910        | 955        | 1651                  | 1733                        | 1897                 | 1980           | ps   |

|                     | 20 mA             | t <sub>OP</sub>  | 890        | 933        | 1583                  | 1661                        | 1819                 | 1888           | ps   |

|                     | (1)               | t <sub>DIP</sub> | 910        | 955        | 1649                  | 1731                        | 1895                 | 1978           | ps   |

| 1.8-V HSTL          | 4 mA              | t <sub>OP</sub>  | 912        | 956        | 1608                  | 1687                        | 1848                 | 1943           | ps   |

| Class I             |                   | t <sub>DIP</sub> | 932        | 978        | 1674                  | 1757                        | 1924                 | 2033           | ps   |

|                     | 6 mA              | t <sub>OP</sub>  | 917        | 962        | 1595                  | 1673                        | 1833                 | 1928           | ps   |

|                     |                   | t <sub>DIP</sub> | 937        | 984        | 1661                  | 1743                        | 1909                 | 2018           | ps   |

|                     | 8 mA              | t <sub>OP</sub>  | 896        | 940        | 1586                  | 1664                        | 1823                 | 1917           | ps   |

|                     |                   | t <sub>DIP</sub> | 916        | 962        | 1652                  | 1734                        | 1899                 | 2007           | ps   |

|                     | 10 mA             | t <sub>OP</sub>  | 900        | 944        | 1591                  | 1669                        | 1828                 | 1923           | ps   |

|                     |                   | t <sub>DIP</sub> | 920        | 966        | 1657                  | 1739                        | 1904                 | 2013           | ps   |

|                     | 12 mA             | t <sub>OP</sub>  | 892        | 936        | 1585                  | 1663                        | 1821                 | 1916           | ps   |

|                     | (1)               | t <sub>DIP</sub> | 912        | 958        | 1651                  | 1733                        | 1897                 | 2006           | ps   |

| Table 5–77. Maximum Input Toggle Rate on Stratix II Devices (Part 2 of 2) |                       |     |     |                    |     |     |                                 |     |     |

|---------------------------------------------------------------------------|-----------------------|-----|-----|--------------------|-----|-----|---------------------------------|-----|-----|

| Input I/O Standard                                                        | Column I/O Pins (MHz) |     |     | Row I/O Pins (MHz) |     |     | Dedicated Clock Inputs<br>(MHz) |     |     |

| •                                                                         | -3                    | -4  | -5  | -3                 | -4  | -5  | -3                              | -4  | -5  |

| 1.8-V HSTL Class II                                                       | 500                   | 500 | 500 | 500                | 500 | 500 | 500                             | 500 | 500 |

| PCI (1)                                                                   | 500                   | 500 | 450 | -                  | -   | -   | 500                             | 500 | 400 |

| PCI-X (1)                                                                 | 500                   | 500 | 450 | -                  | -   | -   | 500                             | 500 | 400 |

| 1.2-V HSTL (2)                                                            | 280                   | -   | -   | -                  | -   | -   | 280                             | -   | -   |

| Differential SSTL-2 Class I (1), (3)                                      | 500                   | 500 | 500 | -                  | -   | -   | 500                             | 500 | 500 |

| Differential SSTL-2 Class II (1), (3)                                     | 500                   | 500 | 500 | -                  | -   | -   | 500                             | 500 | 500 |

| Differential SSTL-18 Class I (1), (3)                                     | 500                   | 500 | 500 | -                  | -   | -   | 500                             | 500 | 500 |

| Differential SSTL-18 Class II (1), (3)                                    | 500                   | 500 | 500 | -                  | -   | -   | 500                             | 500 | 500 |

| 1.8-V Differential HSTL<br>Class I (1), (3)                               | 500                   | 500 | 500 | -                  | -   | -   | 500                             | 500 | 500 |

| 1.8-V Differential HSTL<br>Class II (1), (3)                              | 500                   | 500 | 500 | -                  | -   | -   | 500                             | 500 | 500 |

| 1.5-V Differential HSTL<br>Class I (1), (3)                               | 500                   | 500 | 500 | -                  | -   | -   | 500                             | 500 | 500 |

| 1.5-V Differential HSTL<br>Class II (1), (3)                              | 500                   | 500 | 500 | -                  | -   | -   | 500                             | 500 | 500 |

| HyperTransport technology (4)                                             | -                     | -   | -   | 520                | 520 | 420 | 717                             | 717 | 640 |

| LVPECL (1)                                                                | -                     | -   | -   | -                  | -   | -   | 450                             | 450 | 400 |

| LVDS (5)                                                                  | -                     | -   | -   | 520                | 520 | 420 | 717                             | 717 | 640 |

| LVDS (6)                                                                  | -                     | -   | -   | -                  | -   | -   | 450                             | 450 | 400 |

### *Notes to Table 5–77:*

- (1) Row clock inputs don't support PCI, PCI-X, LVPECL, and differential HSTL and SSTL standards.

- (2) 1.2-V HSTL is only supported on column I/O pins.

- (3) Differential HSTL and SSTL standards are only supported on column clock and DQS inputs.

- (4) HyperTransport technology is only supported on row I/O and row dedicated clock input pins.

- (5) These numbers apply to I/O pins and dedicated clock pins in the left and right I/O banks.

- (6) These numbers apply to dedicated clock pins in the top and bottom I/O banks.

| Table 5–78. Maxi | mum Output | t Toggle R | ate on St  | ratix II De | vices (Pa | art 1 of 5) | No    | ote (1)             |       |       |

|------------------|------------|------------|------------|-------------|-----------|-------------|-------|---------------------|-------|-------|

| I/O Standard     | Drive      | Colum      | n I/O Pins | (MHz)       | Row I     | /0 Pins (I  | /IHz) | Clock Outputs (MHz) |       |       |

| i/O Stanuaru     | Strength   | -3         | -4         | -5          | -3        | -4          | -5    | -3                  | -4    | -5    |

| 3.3-V LVTTL      | 4 mA       | 270        | 225        | 210         | 270       | 225         | 210   | 270                 | 225   | 210   |

|                  | 8 mA       | 435        | 355        | 325         | 435       | 355         | 325   | 435                 | 355   | 325   |

|                  | 12 mA      | 580        | 475        | 420         | 580       | 475         | 420   | 580                 | 475   | 420   |

|                  | 16 mA      | 720        | 594        | 520         | -         | -           | -     | 720                 | 594   | 520   |

|                  | 20 mA      | 875        | 700        | 610         | -         | -           | -     | 875                 | 700   | 610   |

|                  | 24 mA      | 1,030      | 794        | 670         | -         | -           | -     | 1,030               | 794   | 670   |

| 3.3-V LVCMOS     | 4 mA       | 290        | 250        | 230         | 290       | 250         | 230   | 290                 | 250   | 230   |

|                  | 8 mA       | 565        | 480        | 440         | 565       | 480         | 440   | 565                 | 480   | 440   |

|                  | 12 mA      | 790        | 710        | 670         | -         | -           | -     | 790                 | 710   | 670   |

|                  | 16 mA      | 1,020      | 925        | 875         | -         | -           | -     | 1,020               | 925   | 875   |

|                  | 20 mA      | 1,066      | 985        | 935         | -         | -           | -     | 1,066               | 985   | 935   |

|                  | 24 mA      | 1,100      | 1,040      | 1,000       | -         | -           | -     | 1,100               | 1,040 | 1,000 |

| 2.5-V            | 4 mA       | 230        | 194        | 180         | 230       | 194         | 180   | 230                 | 194   | 180   |

| LVTTL/LVCMOS     | 8 mA       | 430        | 380        | 380         | 430       | 380         | 380   | 430                 | 380   | 380   |

|                  | 12 mA      | 630        | 575        | 550         | 630       | 575         | 550   | 630                 | 575   | 550   |

|                  | 16 mA      | 930        | 845        | 820         | -         | -           | -     | 930                 | 845   | 820   |

| 1.8-V            | 2 mA       | 120        | 109        | 104         | 120       | 109         | 104   | 120                 | 109   | 104   |

| LVTTL/LVCMOS     | 4 mA       | 285        | 250        | 230         | 285       | 250         | 230   | 285                 | 250   | 230   |

|                  | 6 mA       | 450        | 390        | 360         | 450       | 390         | 360   | 450                 | 390   | 360   |

|                  | 8 mA       | 660        | 570        | 520         | 660       | 570         | 520   | 660                 | 570   | 520   |

|                  | 10 mA      | 905        | 805        | 755         | -         | -           | -     | 905                 | 805   | 755   |

|                  | 12 mA      | 1,131      | 1,040      | 990         | -         | -           | -     | 1,131               | 1,040 | 990   |

| 1.5-V            | 2 mA       | 244        | 200        | 180         | 244       | 200         | 180   | 244                 | 200   | 180   |

| LVTTL/LVCMOS     | 4 mA       | 470        | 370        | 325         | 470       | 370         | 325   | 470                 | 370   | 325   |

|                  | 6 mA       | 550        | 430        | 375         | -         | -           | -     | 550                 | 430   | 375   |

|                  | 8 mA       | 625        | 495        | 420         | -         | -           | -     | 625                 | 495   | 420   |

| SSTL-2 Class I   | 8 mA       | 400        | 300        | 300         | -         | -           | -     | 400                 | 300   | 300   |

|                  | 12 mA      | 400        | 400        | 350         | 400       | 350         | 350   | 400                 | 400   | 350   |

| SSTL-2 Class II  | 16 mA      | 350        | 350        | 300         | 350       | 350         | 300   | 350                 | 350   | 300   |

|                  | 20 mA      | 400        | 350        | 350         | -         | -           | -     | 400                 | 350   | 350   |

|                  | 24 mA      | 400        | 400        | 350         | -         | -           | -     | 400                 | 400   | 350   |

Table 5–82. Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -3 Devices Notes (1), (2)

|                                 | Maximum DCD Based on I/O Standard of Input Feeding the DDIO Clock Port<br>(No PLL in Clock Path) |             |        |             |                                       |      |  |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------|-------------|--------|-------------|---------------------------------------|------|--|--|--|

| Row DDIO Output I/O<br>Standard | TTL/0                                                                                            | CMOS        | SSTL-2 | SSTL/HSTL   | LVDS/<br>HyperTransport<br>Technology | Unit |  |  |  |

|                                 | 3.3 & 2.5 V                                                                                      | 1.8 & 1.5 V | 2.5 V  | 1.8 & 1.5 V | 3.3 V                                 |      |  |  |  |

| 3.3-V LVTTL                     | 260                                                                                              | 380         | 145    | 145         | 110                                   | ps   |  |  |  |

| 3.3-V LVCMOS                    | 210                                                                                              | 330         | 100    | 100         | 65                                    | ps   |  |  |  |

| 2.5 V                           | 195                                                                                              | 315         | 85     | 85          | 75                                    | ps   |  |  |  |

| 1.8 V                           | 150                                                                                              | 265         | 85     | 85          | 120                                   | ps   |  |  |  |

| 1.5-V LVCMOS                    | 255                                                                                              | 370         | 140    | 140         | 105                                   | ps   |  |  |  |

| SSTL-2 Class I                  | 175                                                                                              | 295         | 65     | 65          | 70                                    | ps   |  |  |  |

| SSTL-2 Class II                 | 170                                                                                              | 290         | 60     | 60          | 75                                    | ps   |  |  |  |

| SSTL-18 Class I                 | 155                                                                                              | 275         | 55     | 50          | 90                                    | ps   |  |  |  |

| 1.8-V HSTL Class I              | 150                                                                                              | 270         | 60     | 60          | 95                                    | ps   |  |  |  |

| 1.5-V HSTL Class I              | 150                                                                                              | 270         | 55     | 55          | 90                                    | ps   |  |  |  |

| LVDS/ HyperTransport technology | 180                                                                                              | 180         | 180    | 180         | 180                                   | ps   |  |  |  |

Notes to Table 5-82:

- (1) The information in Table 5–82 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Here is an example for calculating the DCD in percentage for a DDIO output on a row I/O on a -3 device:

If the input I/O standard is SSTL-2 and the DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 60 ps (see Table 5–82). If the clock frequency is 267 MHz, the clock period T is:

$$T = 1/f = 1/267 \text{ MHz} = 3.745 \text{ ns} = 3745 \text{ ps}$$

Calculate the DCD as a percentage:

$$(T/2 - DCD) / T = (3745ps/2 - 60ps) / 3745ps = 48.4\%$$

(for low boundary)

$$(T/2 + DCD) / T = (3745 ps/2 + 60 ps) / 3745ps = 51.6\%$$

(for high boundary)

### External Memory Interface Specifications

Tables 5–94 through 5–101 contain Stratix II device specifications for the dedicated circuitry used for interfacing with external memory devices.

| Table 5–94. DLL Frequency Range Specifications |                                     |      |  |  |  |  |  |

|------------------------------------------------|-------------------------------------|------|--|--|--|--|--|

| Frequency Mode                                 | Resolution<br>(Degrees)             |      |  |  |  |  |  |

| 0                                              | 100 to 175                          | 30   |  |  |  |  |  |

| 1                                              | 150 to 230                          | 22.5 |  |  |  |  |  |

| 2                                              | 200 to 310                          | 30   |  |  |  |  |  |

| 3                                              | 240 to 400 (-3 speed grade)         | 36   |  |  |  |  |  |

|                                                | 240 to 350 (-4 and -5 speed grades) | 36   |  |  |  |  |  |

Table 5–95 lists the maximum delay in the fast timing model for the Stratix II DQS delay buffer. Multiply the number of delay buffers that you are using in the DQS logic block to get the maximum delay achievable in your system. For example, if you implement a  $90^{\circ}$  phase shift at 200 MHz, you use three delay buffers in mode 2. The maximum achievable delay from the DQS block is then  $3 \times .416$  ps = 1.248 ns.

| Table 5–95. DQS Delay Buffer Maximum Delay in Fast Timing Model |       |    |  |  |  |  |  |

|-----------------------------------------------------------------|-------|----|--|--|--|--|--|

| Frequency Mode                                                  | Unit  |    |  |  |  |  |  |

| 0                                                               | 0.833 | ns |  |  |  |  |  |

| 1, 2, 3                                                         | 0.416 | ns |  |  |  |  |  |

| Table 5–96. DQS Period Jitter Specifications for DLL-Delayed Clock (tDQS_JITTER) Note (1) |            |            |      |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|------------|------------|------|--|--|--|--|--|--|

| Number of DQS Delay Buffer<br>Stages (2)                                                  | Commercial | Industrial | Unit |  |  |  |  |  |  |

| 1                                                                                         | 80         | 110        | ps   |  |  |  |  |  |  |

| 2                                                                                         | 110        | 130        | ps   |  |  |  |  |  |  |

| 3                                                                                         | 130        | 180        | ps   |  |  |  |  |  |  |

| 4                                                                                         | 160        | 210        | ps   |  |  |  |  |  |  |

Notes to Table 5-96:

- (1) Peak-to-peak period jitter on the phase shifted DQS clock.

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.