Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 4548                                                    |

| Number of Logic Elements/Cells | 90960                                                   |

| Total RAM Bits                 | 4520488                                                 |

| Number of I/O                  | 534                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA                                                |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s90f780c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timing Model                                          | 5–20 |

|-------------------------------------------------------|------|

| Preliminary & Final Timing                            | 5–20 |

| I/O Timing Measurement Methodology                    |      |

| Performance                                           |      |

| Internal Timing Parameters                            | 5–34 |

| Stratix II Clock Timing Parameters                    | 5–41 |

| Clock Network Skew Adders                             | 5–50 |

| IOE Programmable Delay                                | 5–51 |

| Default Capacitive Loading of Different I/O Standards | 5–52 |

| I/O Delays                                            |      |

| Maximum Input & Output Clock Toggle Rate              | 5–66 |

| Duty Cycle Distortion                                 | 5–77 |

| DCD Measurement Techniques                            | 5–78 |

| High-Speed I/O Specifications                         | 5–87 |

| PLL Timing Specifications                             | 5–91 |

| External Memory Interface Specifications              | 5–94 |

| JTAG Timing Specifications                            | 5–96 |

| Document Revision History                             | 5–97 |

| Chapter 6. Reference & Ordering Information           |      |

| Software                                              |      |

| Device Pin-Outs                                       |      |

| Ordering Information                                  |      |

| Document Revision History                             | 6–2  |

| Visual Cue                          | Meaning                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italic type                         | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                     | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <project name="">.pof file.</project></file>                                                                                                                                                                     |

| Initial Capital Letters             | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                  | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                        | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{datal}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , $\mathtt{e.g.}$ , $\mathtt{resetn}$ .                                                                                               |

|                                     | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc. | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| •••                                 | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                   | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                     | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| CAUTION                             | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process.                                                                                                                                         |

| WARNING                             | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                        |

| 4                                   | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                 | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

ii Altera Corporation

# Document Revision History

Table 1–6 shows the revision history for this chapter.

| Table 1–6. Document Revision History |                                                                                                                     |                    |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| Date and<br>Document<br>Version      | Changes Made                                                                                                        | Summary of Changes |  |  |  |

| May 2007, v4.2                       | Moved Document Revision History to the end of the chapter.                                                          | _                  |  |  |  |

| April 2006, v4.1                     | <ul> <li>Updated "Features" section.</li> <li>Removed Note 4 from Table 1–2.</li> <li>Updated Table 1–4.</li> </ul> | _                  |  |  |  |

| December 2005,<br>v4.0               | <ul><li>Updated Tables 1–2, 1–4, and 1–5.</li><li>Updated Figure 2–43.</li></ul>                                    | _                  |  |  |  |

| July 2005, v3.1                      | <ul> <li>Added vertical migration information, including<br/>Table 1–4.</li> <li>Updated Table 1–5.</li> </ul>      | _                  |  |  |  |

| May 2005, v3.0                       | <ul><li>Updated "Features" section.</li><li>Updated Table 1–2.</li></ul>                                            | _                  |  |  |  |

| March 2005,<br>v2.1                  | Updated "Introduction" and "Features" sections.                                                                     | _                  |  |  |  |

| January 2005,<br>v2.0                | Added note to Table 1–2.                                                                                            | _                  |  |  |  |

| October 2004,<br>v1.2                | Updated Tables 1-2, 1-3, and 1-5.                                                                                   | _                  |  |  |  |

| July 2004, v1.1                      | <ul><li>Updated Tables 1–1 and 1–2.</li><li>Updated "Features" section.</li></ul>                                   |                    |  |  |  |

| February 2004,<br>v1.0               | Added document to the Stratix II Device Handbook.                                                                   | _                  |  |  |  |

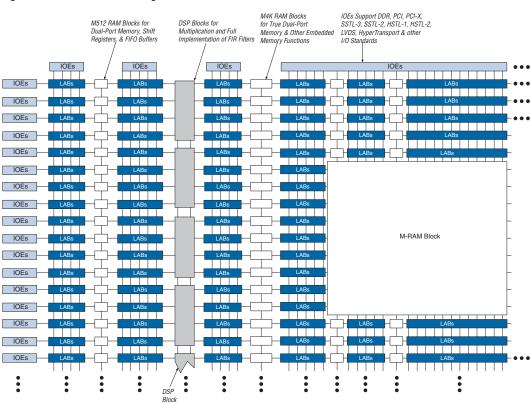

Each Stratix II device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with dedicated clocks, these registers provide exceptional performance and interface support with external memory devices such as DDR and DDR2 SDRAM, RLDRAM II, and QDR II SRAM devices. High-speed serial interface channels with dynamic phase alignment (DPA) support data transfer at up to 1 Gbps using LVDS or HyperTransport™ technology I/O standards.

Figure 2–1 shows an overview of the Stratix II device.

Figure 2-1. Stratix II Block Diagram

For the packing of two five-input functions into one ALM, the functions must have at least two common inputs. The common inputs are dataa and datab. The combination of a four-input function with a five-input function requires one common input (either dataa or datab).

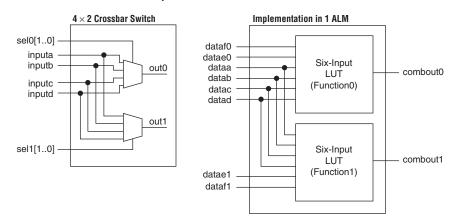

In the case of implementing two six-input functions in one ALM, four inputs must be shared and the combinational function must be the same. For example, a  $4 \times 2$  crossbar switch (two 4-to-1 multiplexers with common inputs and unique select lines) can be implemented in one ALM, as shown in Figure 2–8. The shared inputs are dataa, datab, datac, and datad, while the unique select lines are datae0 and dataf0 for function0, and datae1 and dataf1 for function1. This crossbar switch consumes four LUTs in a four-input LUT-based architecture.

Figure 2-8. 4 × 2 Crossbar Switch Example

In a sparsely used device, functions that could be placed into one ALM may be implemented in separate ALMs. The Quartus II Compiler spreads a design out to achieve the best possible performance. As a device begins to fill up, the Quartus II software automatically utilizes the full potential of the Stratix II ALM. The Quartus II Compiler automatically searches for functions of common inputs or completely independent functions to be placed into one ALM and to make efficient use of the device resources. In addition, you can manually control resource usage by setting location assignments.

Any six-input function can be implemented utilizing inputs dataa, datab, datac, datad, and either datae0 and dataf0 or datae1 and dataf1. If datae0 and dataf0 are utilized, the output is driven to register0, and/or register0 is bypassed and the data drives out to the interconnect using the top set of output drivers (see Figure 2–9). If

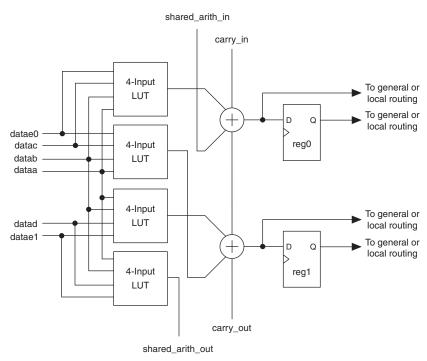

Figure 2-13. ALM in Shared Arithmetic Mode

Note to Figure 2-13:

(1) Inputs dataf0 and dataf1 are available for register packing in shared arithmetic mode.

Adder trees can be found in many different applications. For example, the summation of the partial products in a logic-based multiplier can be implemented in a tree structure. Another example is a correlator function that can use a large adder tree to sum filtered data samples in a given time frame to recover or to de-spread data which was transmitted utilizing spread spectrum technology.

An example of a three-bit add operation utilizing the shared arithmetic mode is shown in Figure 2–14. The partial sum (S[2..0]) and the partial carry (C[2..0]) is obtained using the LUTs, while the result (R[2..0]) is computed using the dedicated adders.

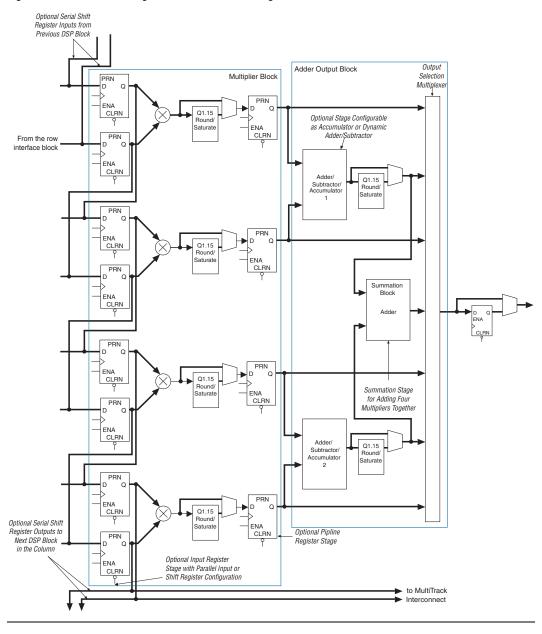

Figure 2-28. DSP Block Diagram for 18 x 18-Bit Configuration

## **Fast PLLs**

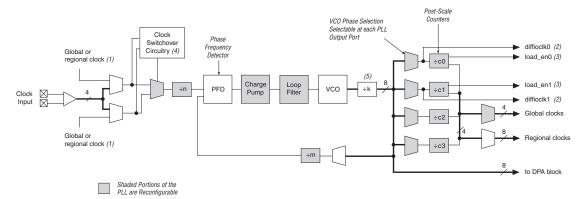

Stratix II devices contain up to eight fast PLLs with high-speed serial interfacing ability. Figure 2–45 shows a diagram of the fast PLL.

Figure 2–45. Stratix II Device Fast PLL Notes (1), (2), (3)

#### Notes to Figure 2-45:

- (1) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES circuitry. Stratix II devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a differential I/O SERDES control signal.

- (4) Stratix II fast PLLs only support manual clock switchover.

- (5) If the design enables this ÷2 counter, then the device can use a VCO frequency range of 150 to 520 MHz.

See the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information on enhanced and fast PLLs. See "High-Speed Differential I/O with DPA Support" on page 2–96 for more information on high-speed differential I/O support.

## I/O Structure

The Stratix II IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- On-chip driver series termination

- On-chip parallel termination

- On-chip termination for differential standards

- Programmable pull-up during configuration

| Table 2- | 14. DQS & DQ Bus Mode Supp  | ort (Part 2 of 2       | Note (1)               |                          |                             |

|----------|-----------------------------|------------------------|------------------------|--------------------------|-----------------------------|

| Device   | Package                     | Number of<br>×4 Groups | Number of ×8/×9 Groups | Number of ×16/×18 Groups | Number of<br>×32/×36 Groups |

| EP2S90   | 484-pin Hybrid FineLine BGA | 8                      | 4                      | 0                        | 0                           |

|          | 780-pin FineLine BGA        | 18                     | 8                      | 4                        | 0                           |

|          | 1,020-pin FineLine BGA      | 36                     | 18                     | 8                        | 4                           |

|          | 1,508-pin FineLine BGA      | 36                     | 18                     | 8                        | 4                           |

| EP2S130  | 780-pin FineLine BGA        | 18                     | 8                      | 4                        | 0                           |

|          | 1,020-pin FineLine BGA      | 36                     | 18                     | 8                        | 4                           |

|          | 1,508-pin FineLine BGA      | 36                     | 18                     | 8                        | 4                           |

| EP2S180  | 1,020-pin FineLine BGA      | 36                     | 18                     | 8                        | 4                           |

|          | 1,508-pin FineLine BGA      | 36                     | 18                     | 8                        | 4                           |

Notes to Table 2-14:

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

The Stratix II device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.

Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK[15..12]p feed the phase circuitry on the top of the device and clock pins CLK[7..4]p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits.

Figure 2–56 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

<sup>(1)</sup> Check the pin table for each DQS/DQ group in the different modes.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. Disable the bus-hold feature when the I/O pin has been configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$  to weakly pull the signal level to the last-driven state. See the *DC & Switching Characteristics* chapter in the *Stratix II Device Handbook, Volume 1*, for the specific sustaining current driven through this resistor and overdrive current used to identify the next-driven input level. This information is provided for each  $V_{CCIO}$  voltage level.

The bus-hold circuitry is active only after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

## Programmable Pull-Up Resistor

Each Stratix II device I/O pin provides an optional programmable pull-up resistor during user mode. If you enable this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) weakly holds the output to the  $V_{CCIO}$  level of the output pin's bank.

Programmable pull-up resistors are only supported on user I/O pins, and are not supported on dedicated configuration pins, JTAG pins or dedicated clock pins.

## Advanced I/O Standard Support

Stratix II device IOEs support the following I/O standards:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

- 3.3-V PCI-X mode 1

- LVDS

- LVPECL (on input and output clocks only)

- HyperTransport technology

- Differential 1.5-V HSTL Class I and II

- Differential 1.8-V HSTL Class I and II

- Differential SSTL-18 Class I and II

- Differential SSTL-2 Class I and II

For more information on JTAG, see the following documents:

- The IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing for Stratix II & Stratix II GX Devices chapter of the Stratix II Device Handbook, Volume 2 or the Stratix II GX Device Handbook, Volume 2

- Jam Programming & Test Language Specification

## SignalTap II Embedded Logic Analyzer

Stratix II devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

## Configuration

The logic, circuitry, and interconnects in the Stratix II architecture are configured with CMOS SRAM elements. Altera® FPGA devices are reconfigurable and every device is tested with a high coverage production test program so you do not have to perform fault testing and can instead focus on simulation and design verification.

Stratix II devices are configured at system power-up with data stored in an Altera configuration device or provided by an external controller (e.g., a MAX® II device or microprocessor). Stratix II devices can be configured using the fast passive parallel (FPP), active serial (AS), passive serial (PS), passive parallel asynchronous (PPA), and JTAG configuration schemes. The Stratix II device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix II devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy.

In addition to the number of configuration methods supported, Stratix II devices also offer the design security, decompression, and remote system upgrade features. The design security feature, using configuration bitstream encryption and AES technology, provides a mechanism to protect your designs. The decompression feature allows Stratix II FPGAs to receive a compressed configuration bitstream and decompress this data in real-time, reducing storage requirements and configuration time. The remote system upgrade feature allows real-time system upgrades from remote locations of your Stratix II designs. For more information, see "Configuration Schemes" on page 3–7.

you need to support configuration input voltages of 1.8 V/1.5 V, you should set the VCCSEL to a logic high and the  $V_{CCIO}$  of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

## **Configuration Schemes**

You can load the configuration data for a Stratix II device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix II device. A configuration device can automatically configure a Stratix II device at system power-up.

You can configure multiple Stratix II devices in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

Stratix II FPGAs offer the following:

- Configuration data decompression to reduce configuration file storage

- Design security using configuration data encryption to protect your designs

- Remote system upgrades for remotely updating your Stratix II designs

Table 3–5 summarizes which configuration features can be used in each configuration scheme.

| Configuration Scheme | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |  |

|----------------------|--------------------------------------------------|-----------------|---------------|--------------------------|--|

| FPP                  | MAX II device or microprocessor and flash device | <b>√</b> (1)    | <b>√</b> (1)  | <b>✓</b>                 |  |

|                      | Enhanced configuration device                    |                 | <b>√</b> (2)  | ~                        |  |

| AS                   | Serial configuration device                      | ✓               | ✓             | <b>√</b> (3)             |  |

| PS                   | MAX II device or microprocessor and flash device | <b>✓</b>        | ~             | <b>✓</b>                 |  |

|                      | Enhanced configuration device                    | ✓               | ✓             | <b>✓</b>                 |  |

|                      | Download cable (4)                               | <b>✓</b>        | <b>✓</b>      |                          |  |

| Symbol               | Parameter                   | Conditions                     | Minimum                 | Typical | Maximum                | Unit |

|----------------------|-----------------------------|--------------------------------|-------------------------|---------|------------------------|------|

| V <sub>CCIO</sub>    | Output supply voltage       |                                | 1.71                    | 1.80    | 1.89                   | V    |

| $V_{REF}$            | Input reference voltage     |                                | 0.85                    | 0.90    | 0.95                   | ٧    |

| $V_{TT}$             | Termination voltage         |                                | 0.85                    | 0.90    | 0.95                   | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage |                                | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage  |                                | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage |                                | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage  |                                |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage   | I <sub>OH</sub> = 16 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage    | $I_{OH} = -16 \text{ mA } (1)$ |                         |         | 0.4                    | ٧    |

#### Note to Table 5-27:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–2             | Table 5–28. 1.8-V HSTL Class I & II Differential Specifications |            |         |         |                           |      |  |  |  |  |

|-----------------------|-----------------------------------------------------------------|------------|---------|---------|---------------------------|------|--|--|--|--|

| Symbol                | Parameter                                                       | Conditions | Minimum | Typical | Maximum                   | Unit |  |  |  |  |

| V <sub>CCIO</sub>     | I/O supply voltage                                              |            | 1.71    | 1.80    | 1.89                      | V    |  |  |  |  |

| V <sub>DIF</sub> (DC) | DC input differential voltage                                   |            | 0.2     |         | V <sub>CCIO</sub> + 0.6 V | V    |  |  |  |  |

| V <sub>CM</sub> (DC)  | DC common mode input voltage                                    |            | 0.78    |         | 1.12                      | V    |  |  |  |  |

| V <sub>DIF</sub> (AC) | AC differential input voltage                                   |            | 0.4     |         | V <sub>CCIO</sub> + 0.6 V | V    |  |  |  |  |

| V <sub>OX</sub> (AC)  | AC differential cross point voltage                             |            | 0.68    |         | 0.90                      | V    |  |  |  |  |

|                                    |                                                                                         |                                    | Resista           | nce Toleran       | ce   |

|------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|------|

| Symbol                             | Description                                                                             | Conditions                         | Commercial<br>Max | Industrial<br>Max | Unit |

| 25-Ω R <sub>S</sub><br>3.3/2.5     | Internal series termination without calibration (25- $\Omega$ setting)                  | V <sub>CCIO</sub> = 3.3/2.5 V      | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub><br>3.3/2.5/1.8 | Internal series termination without calibration (50- $\Omega$ setting)                  | $V_{CCIO} = 3.3/2.5/1.8 \text{ V}$ | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub> 1.5            | Internal series termination without calibration (50- $\Omega$ setting)                  | V <sub>CCIO</sub> = 1.5 V          | ±36               | ±36               | %    |

| R <sub>D</sub>                     | Internal differential termination for LVDS or HyperTransport technology (100-Ω setting) | V <sub>CCIO</sub> = 2.5 V          | ±20               | ±25               | %    |

## **Pin Capacitance**

Table 5–32 shows the Stratix II device family pin capacitance.

| Table 5–32. Stratix II Device Capacitance Note (1) |                                                                                                                             |         |      |  |  |  |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|------|--|--|--|--|--|

| Symbol                                             | Parameter                                                                                                                   | Typical | Unit |  |  |  |  |  |

| $C_{IOTB}$                                         | Input capacitance on I/O pins in I/O banks 3, 4, 7, and 8.                                                                  | 5.0     | pF   |  |  |  |  |  |

| C <sub>IOLR</sub>                                  | Input capacitance on I/O pins in I/O banks 1, 2, 5, and 6, including high-speed differential receiver and transmitter pins. | 6.1     | pF   |  |  |  |  |  |

| C <sub>CLKTB</sub>                                 | Input capacitance on top/bottom clock input pins: CLK [47] and CLK [1215].                                                  | 6.0     | pF   |  |  |  |  |  |

| C <sub>CLKLR</sub>                                 | Input capacitance on left/right clock inputs: CLK0, CLK2, CLK8, CLK10.                                                      | 6.1     | pF   |  |  |  |  |  |

| C <sub>CLKLR+</sub>                                | Input capacitance on left/right clock inputs: CLK1, CLK3, CLK9, and CLK11.                                                  | 3.3     | pF   |  |  |  |  |  |

| C <sub>OUTFB</sub>                                 | Input capacitance on dual-purpose clock output/feedback pins in PLL banks 9, 10, 11, and 12.                                | 6.7     | pF   |  |  |  |  |  |

## Note to Table 5–32:

(1) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within  $\pm 0.5 pF$

| Table 5-          | 36. Stratix II Performan                                                                                                        | ce Notes | (Part 3 of 6)                 | ) Note        | e (1)                |                      |                      |                      |      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|------|

|                   |                                                                                                                                 | Re       | esources Us                   | ed            | Performance          |                      |                      |                      |      |

|                   | Applications                                                                                                                    |          | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| DSP               | 9 × 9-bit multiplier (5)                                                                                                        | 0        | 0                             | 1             | 430.29               | 409.16               | 373.13               | 320.10               | MHz  |

| block             | 18 × 18-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 410.17               | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18 × 18-bit<br>multiplier (7)                                                                                                   | 0        | 0                             | 1             | 450.04               | 428.08               | 391.23               | 335.12               | MHz  |

|                   | 36 × 36-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 250.00               | 238.15               | 217.48               | 186.60               | MHz  |

|                   | $36 \times 36$ -bit multiplier (6)                                                                                              | 0        | 0                             | 1             | 410.17               | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18-bit, four-tap FIR filter                                                                                                     | 0        | 0                             | 1             | 410.17               | 390.01               | 356.12               | 305.06               | MHz  |

| Larger<br>designs | 8-bit,16-tap parallel<br>FIR filter                                                                                             | 58       | 0                             | 4             | 259.06               | 240.61               | 217.15               | 185.01               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, three<br>multipliers and five<br>adders FFT function                                           | 2976     | 22                            | 9             | 398.72               | 364.03               | 355.23               | 306.37               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, four<br>multipliers and two<br>adders FFT function                                             | 2781     | 22                            | 12            | 398.56               | 409.16               | 347.22               | 311.13               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function | 984      | 5                             | 3             | 425.17               | 365.76               | 346.98               | 292.39               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function   | 919      | 5                             | 4             | 427.53               | 378.78               | 357.14               | 307.59               | MHz  |

|                   |                                                                                                                                    | Re    | esources Us                   | ed            | Performance          |                      |                      |                      |      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|------|

| Applications      |                                                                                                                                    | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| Larger<br>designs | 8-bit, 1024-point,<br>single output, two<br>parallel FFT engines,<br>burst, three multiplier<br>and five adders FFT<br>function    | 1725  | 10                            | 6             | 430.29               | 401.92               | 373.13               | 319.08               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, two<br>parallel FFT engines,<br>burst, four multipliers<br>and two adders FFT<br>function     | 1594  | 10                            | 8             | 422.65               | 407.33               | 373.13               | 329.10               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function  | 2361  | 10                            | 9             | 315.45               | 342.81               | 325.73               | 284.25               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function    | 2165  | 10                            | 12            | 373.13               | 369.54               | 317.96               | 256.14               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, two<br>parallel FFT engines,<br>burst, three multipliers<br>and five adders FFT<br>function | 3996  | 14                            | 18            | 378.50               | 367.10               | 332.33               | 288.68               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, two<br>parallel FFT engines,<br>burst, four multipliers<br>and two adders FFT<br>function   | 3604  | 14                            | 24            | 391.38               | 361.14               | 340.25               | 280.89               | MHz  |

## **Internal Timing Parameters**

See Tables 5–37 through 5–42 for internal timing parameters.

| Table 5–37. LE_FF Internal Timing Microparameters |                                     |                       |     |                       |     |                   |     |                   |     |       |  |

|---------------------------------------------------|-------------------------------------|-----------------------|-----|-----------------------|-----|-------------------|-----|-------------------|-----|-------|--|

| Cumbal                                            | Dovometou                           | -3 Speed<br>Grade (1) |     | -3 Speed<br>Grade (2) |     | -4 Speed<br>Grade |     | -5 Speed<br>Grade |     | 11-14 |  |

| Symbol                                            | Parameter                           | Min (3)               | Max | Min (3)               | Max | Min (4)           | Max | Min (3)           | Max | Unit  |  |

| t <sub>SU</sub>                                   | LE register setup time before clock | 90                    |     | 95                    |     | 104<br>104        |     | 121               |     | ps    |  |

| t <sub>H</sub>                                    | LE register hold time after clock   | 149                   |     | 157                   |     | 172<br>172        |     | 200               |     | ps    |  |

| t <sub>CO</sub>                                   | LE register clock-to-output delay   | 62                    | 94  | 62                    | 99  | 59<br>62          | 109 | 62                | 127 | ps    |  |

| t <sub>CLR</sub>                                  | Minimum clear pulse width           | 204                   |     | 214                   |     | 234<br>234        |     | 273               |     | ps    |  |

| t <sub>PRE</sub>                                  | Minimum preset pulse width          | 204                   |     | 214                   |     | 234<br>234        |     | 273               |     | ps    |  |

| t <sub>CLKL</sub>                                 | Minimum clock low time              | 612                   |     | 642                   |     | 703<br>703        |     | 820               |     | ps    |  |

| t <sub>CLKH</sub>                                 | Minimum clock high time             | 612                   |     | 642                   |     | 703<br>703        |     | 820               |     | ps    |  |

| t <sub>LUT</sub>                                  |                                     | 162                   | 378 | 162                   | 397 | 162<br>170        | 435 | 162               | 507 | ps    |  |

| t <sub>ADDER</sub>                                |                                     | 354                   | 619 | 354                   | 650 | 354<br>372        | 712 | 354               | 829 | ps    |  |

### Notes to Table 5-37:

- (1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Oursela al               | Parameter                                         | -3 Speed<br>Grade <i>(2)</i> |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | 11-:4  |

|--------------------------|---------------------------------------------------|------------------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|--------|

| Symbol                   | Parameter                                         | Min (4)                      | Max   | Min (4)               | Max   | Min<br>(5)        | Max   | Min (4)           | Max   | - Unit |

| t <sub>M512DATACO1</sub> | Clock-to-output delay when using output registers | 298                          | 478   | 298                   | 501   | 284<br>298        | 548   | 298               | 640   | ps     |

| t <sub>M512DATACO2</sub> | Clock-to-output delay without output registers    | 2,102                        | 2,345 | 2,102                 | 2,461 | 2,003<br>2,102    | 2,695 | 2,102             | 3,141 | ps     |

| t <sub>M512CLKL</sub>    | Minimum clock low time                            | 1,315                        |       | 1,380                 |       | 1,512<br>1,512    |       | 1,762             |       | ps     |

| t <sub>M512CLKH</sub>    | Minimum clock high time                           | 1,315                        |       | 1,380                 |       | 1,512<br>1,512    |       | 1,762             |       | ps     |

| t <sub>M512CLR</sub>     | Minimum clear pulse width                         | 144                          |       | 151                   |       | 165<br>165        |       | 192               |       | ps     |

### Notes to Table 5-40:

- (1) F<sub>MAX</sub> of M512 block obtained using the Quartus II software does not necessarily equal to 1/TM512RC.

- $(2) \quad \text{These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.}$

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (5) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| 0                      | Dovomotov                                    | -3 Speed<br>Grade <i>(2)</i> |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       |      |

|------------------------|----------------------------------------------|------------------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|------|

| Symbol                 | Parameter                                    | Min (4)                      | Max   | Min (4)               | Max   | Min<br>(5)        | Max   | Min (4)           | Max   | Unit |

| t <sub>M4KRC</sub>     | Synchronous read cycle time                  | 1,462                        | 2,240 | 1,462                 | 2,351 | 1,393<br>1,462    | 2,575 | 1,462             | 3,000 | ps   |

| t <sub>M4KWERESU</sub> | Write or read enable setup time before clock | 22                           |       | 23                    |       | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KWEREH</sub>  | Write or read enable hold time after clock   | 203                          |       | 213                   |       | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KBESU</sub>   | Byte enable setup time before clock          | 22                           |       | 23                    |       | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KBEH</sub>    | Byte enable hold time after clock            | 203                          |       | 213                   |       | 233<br>233        |       | 272               |       | ps   |

| Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 2 of 8) |                   |                  |            |            |                       |                       |                |                |      |  |  |  |

|-----------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|--|--|--|

|                                                                       | Drive<br>Strength | Parameter        | Minimu     | m Timing   | -3                    | -3                    | -4             | -5             |      |  |  |  |

| I/O Standard                                                          |                   |                  | Industrial | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |  |  |  |

| LVCMOS                                                                | 4 mA              | t <sub>OP</sub>  | 1041       | 1091       | 2036                  | 2136                  | 2340           | 2448           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 1061       | 1113       | 2102                  | 2206                  | 2416           | 2538           | ps   |  |  |  |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 952        | 999        | 1786                  | 1874                  | 2053           | 2153           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 972        | 1021       | 1852                  | 1944                  | 2129           | 2243           | ps   |  |  |  |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 926        | 971        | 1720                  | 1805                  | 1977           | 2075           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 946        | 993        | 1786                  | 1875                  | 2053           | 2165           | ps   |  |  |  |

|                                                                       | 16 mA             | t <sub>OP</sub>  | 933        | 978        | 1693                  | 1776                  | 1946           | 2043           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 953        | 1000       | 1759                  | 1846                  | 2022           | 2133           | ps   |  |  |  |

|                                                                       | 20 mA             | t <sub>OP</sub>  | 921        | 965        | 1677                  | 1759                  | 1927           | 2025           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 941        | 987        | 1743                  | 1829                  | 2003           | 2115           | ps   |  |  |  |

|                                                                       | 24 mA<br>(1)      | t <sub>OP</sub>  | 909        | 954        | 1659                  | 1741                  | 1906           | 2003           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 929        | 976        | 1725                  | 1811                  | 1982           | 2093           | ps   |  |  |  |

| 2.5 V                                                                 | 4 mA              | t <sub>OP</sub>  | 1004       | 1053       | 2063                  | 2165                  | 2371           | 2480           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 1024       | 1075       | 2129                  | 2235                  | 2447           | 2570           | ps   |  |  |  |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 955        | 1001       | 1841                  | 1932                  | 2116           | 2218           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 975        | 1023       | 1907                  | 2002                  | 2192           | 2308           | ps   |  |  |  |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 934        | 980        | 1742                  | 1828                  | 2002           | 2101           | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 954        | 1002       | 1808                  | 1898                  | 2078           | 2191           | ps   |  |  |  |

|                                                                       | 16 mA             | t <sub>OP</sub>  | 918        | 962        | 1679                  | 1762                  | 1929           | 2027           | ps   |  |  |  |

|                                                                       | (1)               | t <sub>DIP</sub> | 938        | 984        | 1745                  | 1832                  | 2005           | 2117           | ps   |  |  |  |

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 2 of 5) |                   |                 |         |          |              |           |          |                         |          |      |  |

|-----------------------------------------------------------------------------|-------------------|-----------------|---------|----------|--------------|-----------|----------|-------------------------|----------|------|--|

|                                                                             |                   |                 | Maximur | n Output | Clock To     | ggle Rate | e Derati | ng Facto                | rs (ps/p | F)   |  |

| I/O Standard                                                                | Drive<br>Strength | Column I/O Pins |         |          | Row I/O Pins |           |          | Dedicated Clock Outputs |          |      |  |

|                                                                             | oog               | -3              | -4      | -5       | -3           | -4        | -5       | -3                      | -4       | -5   |  |

| 1.8-V                                                                       | 2 mA              | 951             | 1421    | 1421     | 951          | 1421      | 1421     | 904                     | 1421     | 1421 |  |

| LVTTL/LVCMOS                                                                | 4 mA              | 405             | 516     | 516      | 405          | 516       | 516      | 393                     | 516      | 516  |  |

|                                                                             | 6 mA              | 261             | 325     | 325      | 261          | 325       | 325      | 253                     | 325      | 325  |  |

|                                                                             | 8 mA              | 223             | 274     | 274      | 223          | 274       | 274      | 224                     | 274      | 274  |  |

|                                                                             | 10 mA             | 194             | 236     | 236      | -            | -         | 1        | 199                     | 236      | 236  |  |

|                                                                             | 12 mA             | 174             | 209     | 209      | -            | -         | -        | 180                     | 209      | 209  |  |

| 1.5-V                                                                       | 2 mA              | 652             | 963     | 963      | 652          | 963       | 963      | 618                     | 963      | 963  |  |

| LVTTL/LVCMOS                                                                | 4 mA              | 333             | 347     | 347      | 333          | 347       | 347      | 270                     | 347      | 347  |  |

|                                                                             | 6 mA              | 182             | 247     | 247      | -            | -         | -        | 198                     | 247      | 247  |  |

|                                                                             | 8 mA              | 135             | 194     | 194      | -            | -         | -        | 155                     | 194      | 194  |  |

| SSTL-2 Class I                                                              | 8 mA              | 364             | 680     | 680      | 364          | 680       | 680      | 350                     | 680      | 680  |  |

|                                                                             | 12 mA             | 163             | 207     | 207      | 163          | 207       | 207      | 188                     | 207      | 207  |  |

| SSTL-2 Class II                                                             | 16 mA             | 118             | 147     | 147      | 118          | 147       | 147      | 94                      | 147      | 147  |  |

|                                                                             | 20 mA             | 99              | 122     | 122      | -            | -         | -        | 87                      | 122      | 122  |  |

|                                                                             | 24 mA             | 91              | 116     | 116      | -            | -         | -        | 85                      | 116      | 116  |  |

| SSTL-18 Class I                                                             | 4 mA              | 458             | 570     | 570      | 458          | 570       | 570      | 505                     | 570      | 570  |  |

|                                                                             | 6 mA              | 305             | 380     | 380      | 305          | 380       | 380      | 336                     | 380      | 380  |  |

|                                                                             | 8 mA              | 225             | 282     | 282      | 225          | 282       | 282      | 248                     | 282      | 282  |  |

|                                                                             | 10 mA             | 167             | 220     | 220      | 167          | 220       | 220      | 190                     | 220      | 220  |  |

|                                                                             | 12 mA             | 129             | 175     | 175      | -            | -         | -        | 148                     | 175      | 175  |  |

| SSTL-18 Class II                                                            | 8 mA              | 173             | 206     | 206      | -            | -         | -        | 155                     | 206      | 206  |  |

|                                                                             | 16 mA             | 150             | 160     | 160      | -            | -         | -        | 140                     | 160      | 160  |  |

|                                                                             | 18 mA             | 120             | 130     | 130      | -            | -         | -        | 110                     | 130      | 130  |  |

|                                                                             | 20 mA             | 109             | 127     | 127      | -            | -         | -        | 94                      | 127      | 127  |  |

| SSTL-2 Class I                                                              | 8 mA              | 364             | 680     | 680      | 364          | 680       | 680      | 350                     | 680      | 680  |  |

|                                                                             | 12 mA             | 163             | 207     | 207      | 163          | 207       | 207      | 188                     | 207      | 207  |  |

| SSTL-2 Class II                                                             | 16 mA             | 118             | 147     | 147      | 118          | 147       | 147      | 94                      | 147      | 147  |  |

|                                                                             | 20 mA             | 99              | 122     | 122      | -            | -         | -        | 87                      | 122      | 122  |  |

|                                                                             | 24 mA             | 91              | 116     | 116      | -            | -         | -        | 85                      | 116      | 116  |  |