# E·XFL

## Altera - EP2S90F780C4N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 4548                                                       |

| Number of Logic Elements/Cells | 90960                                                      |

| Total RAM Bits                 | 4520488                                                    |

| Number of I/O                  | 534                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA, FCBGA                                            |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s90f780c4n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## About this Handbook

This handbook provides comprehensive information about the Altera® Stratix<sup>®</sup> II family of devices.

## How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                     | Contact<br>Method | Address                   |

|---------------------------------|-------------------|---------------------------|

| Technical support               | Website           | www.altera.com/support    |

| Technical training              | Website           | www.altera.com/training   |

|                                 | Email             | custrain@altera.com       |

| Product literature              | Email             | www.altera.com/literature |

| Altera literature services      | Website           | literature@altera.com     |

| Non-technical support (General) | Email             | nacomp@altera.com         |

| (Software Licensing)            | Email             | authorization@altera.com  |

Note to table:

(1) You can also contact your local Altera sales office or sales representative.

## Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                     |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                  |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file. |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: <i>AN 75: High-Speed Board Design.</i>                                                                                                                                                      |

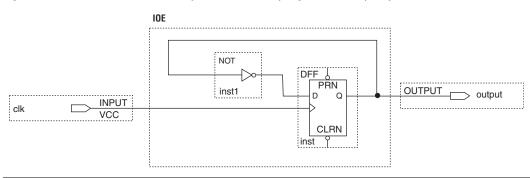

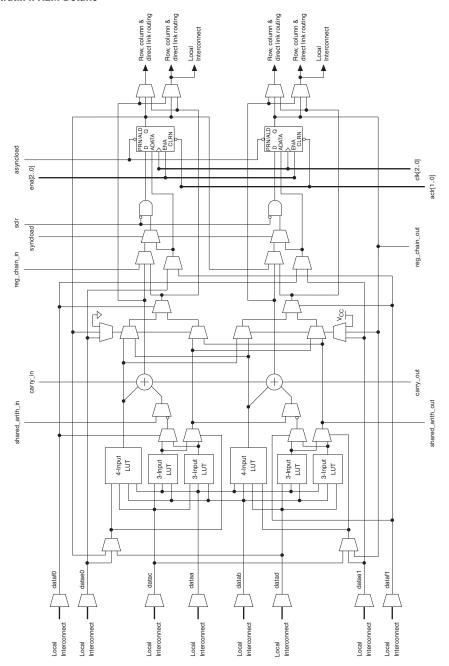

Figure 2–6. Stratix II ALM Details

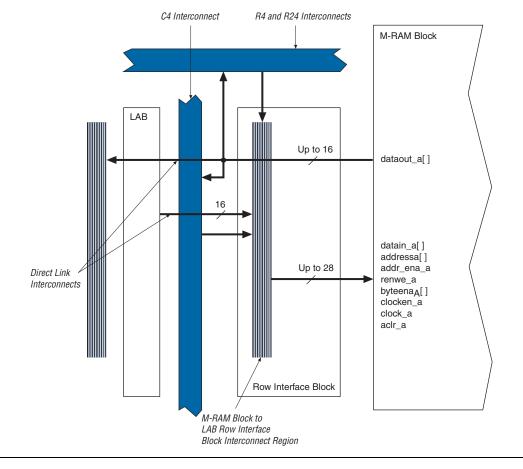

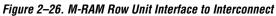

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

Figure 2–28. DSP Block Diagram for 18 × 18-Bit Configuration

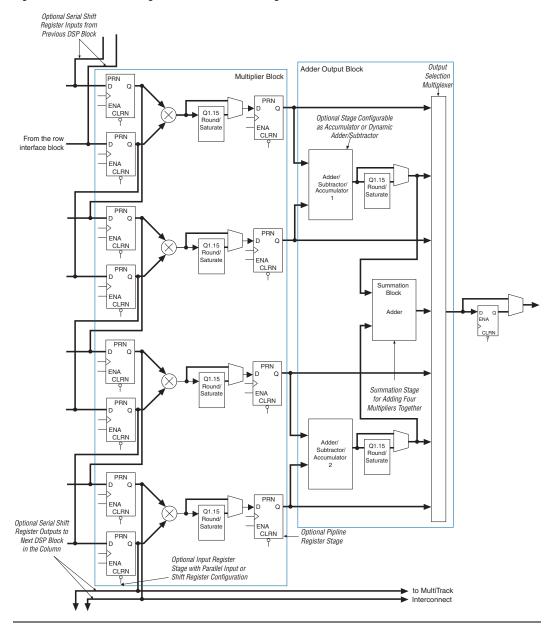

#### Figure 2–39. External PLL Output Clock Control Blocks

#### Notes to Figure 2–39:

- These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

- (2) The clock control block feeds to a multiplexer within the PLL\_OUT pin's IOE. The PLL\_OUT pin is a dual-purpose pin. Therefore, this multiplexer selects either an internal signal or the output of the clock control block.

For the global clock control block, the clock source selection can be controlled either statically or dynamically. The user has the option of statically selecting the clock source by using the Quartus II software to set specific configuration bits in the configuration file (**.sof** or **.pof**) or the user can control the selection dynamically by using internal logic to drive the multiplexor select inputs. When selecting statically, the clock source can be set to any of the inputs to the select multiplexor. When selecting the clock source dynamically, you can either select between two PLL outputs (such as the C0 or C1 outputs from one PLL), between two PLLs (such as the C0/C1 clock output of one PLL or the C0/C1 clock output of the other PLL), between two clock pins (such as CLK0 or CLK1), or between a combination of clock pins or PLL outputs. The clock outputs from corner PLLs cannot be dynamically selected through the global control block.

For the regional and PLL\_OUT clock control block, the clock source selection can only be controlled statically using configuration bits. Any of the inputs to the clock select multiplexor can be set as the clock source.

The Quartus II software enables the PLLs and their features without requiring any external devices. Table 2–9 shows the PLLs available for each Stratix II device and their type.

| Table 2–9. Si | Table 2–9. Stratix II Device PLL Availability |              |              |              |              |              |              |              |              |               |              |              |  |

|---------------|-----------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|--------------|--------------|--|

| <b>.</b> .    | Fast PLLs                                     |              |              |              |              |              |              |              |              | Enhanced PLLs |              |              |  |

| Device        | 1                                             | 2            | 3            | 4            | 7            | 8            | 9            | 10           | 5            | 6             | 11           | 12           |  |

| EP2S15        | $\checkmark$                                  | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              | $\checkmark$ | $\checkmark$  |              |              |  |

| EP2S30        | >                                             | >            | >            | $\checkmark$ |              |              |              |              | $\checkmark$ | $\checkmark$  |              |              |  |

| EP2S60 (1)    | >                                             | >            | >            | $\checkmark$ | $\checkmark$ | >            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ |  |

| EP2S90 (2)    | >                                             | >            | >            | $\checkmark$ | $\checkmark$ | >            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ |  |

| EP2S130 (3)   | >                                             | >            | >            | $\checkmark$ | $\checkmark$ | >            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ |  |

| EP2S180       | $\checkmark$                                  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ |  |

#### Notes to Table 2–9:

(1) EP2S60 devices in the 1020-pin package contain 12 PLLs. EP2S60 devices in the 484-pin and 672-pin packages contain fast PLLs 1–4 and enhanced PLLs 5 and 6.

(2) EP2S90 devices in the 1020-pin and 1508-pin packages contain 12 PLLs. EP2S90 devices in the 484-pin and 780-pin packages contain fast PLLS 1–4 and enhanced PLLs 5 and 6.

(3) EP2S130 devices in the 1020-pin and 1508-pin packages contain 12PLLs. The EP2S130 device in the 780-pin package contains fast PLLs 1–4 and enhanced PLLs 5 and 6.

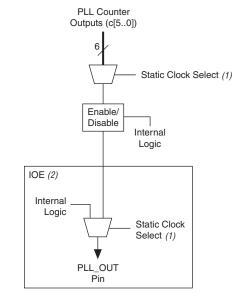

*Figure 2–43. Global & Regional Clock Connections from Top & Bottom Clock Pins & Enhanced PLL Outputs Notes (1), (2), and (3)*

#### Notes to Figure 2–43:

- (1) EP2S15 and EP2S30 devices only have two enhanced PLLs (5 and 6), but the connectivity from these two PLLs to the global and regional clock networks remains the same as shown.

- (2) If the design uses the feedback input, you lose one (or two, if FBIN is differential) external clock output pin.

- (3) The enhanced PLLs can also be driven through the global or regional clock netowrks. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

## **Dedicated Circuitry with DPA Support**

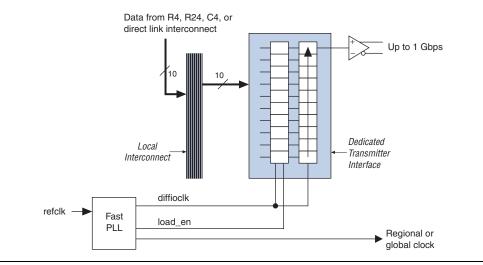

Stratix II devices support source-synchronous interfacing with LVDS or HyperTransport signaling at up to 1 Gbps. Stratix II devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by an integer factor W = 1 through 32. For example, a HyperTransport technology application where the data rate is 1,000 Mbps and the clock rate is 500 MHz would require that W be set to 2. The SERDES factor *J* determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor *J* can be set to 4, 5, 6, 7, 8, 9, or 10 and does not have to equal the PLL clock-multiplication W value. A design using the dynamic phase aligner also supports all of these *J* factor values. For a *J* factor of 1, the Stratix II device bypasses the SERDES block. For a *J* factor of 2, the Stratix II device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. Figure 2–58 shows the block diagram of the Stratix II transmitter channel.

Figure 2–58. Stratix II Transmitter Channel

Each Stratix II receiver channel features a DPA block for phase detection and selection, a SERDES, a synchronizer, and a data realigner circuit. You can bypass the dynamic phase aligner without affecting the basic sourcesynchronous operation of the channel. In addition, you can dynamically switch between using the DPA block or bypassing the block via a control signal from the logic array. Figure 2–59 shows the block diagram of the Stratix II receiver channel. The Quartus II software has an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. Turn on the **Auto Usercode** option by clicking **Device & Pin Options**, then **General**, in the **Settings** dialog box (Assignments menu).

| Table 3–2. Stratix II Boundary-Scan Register Length |                               |  |  |  |  |  |  |

|-----------------------------------------------------|-------------------------------|--|--|--|--|--|--|

| Device                                              | Boundary-Scan Register Length |  |  |  |  |  |  |

| EP2S15                                              | 1,140                         |  |  |  |  |  |  |

| EP2S30                                              | 1,692                         |  |  |  |  |  |  |

| EP2S60                                              | 2,196                         |  |  |  |  |  |  |

| EP2S90                                              | 2,748                         |  |  |  |  |  |  |

| EP2S130                                             | 3,420                         |  |  |  |  |  |  |

| EP2S180                                             | 3,948                         |  |  |  |  |  |  |

| Table 3–3. 32 | Table 3–3. 32-Bit Stratix II Device IDCODE |                                                  |               |   |  |  |  |  |  |  |  |  |

|---------------|--------------------------------------------|--------------------------------------------------|---------------|---|--|--|--|--|--|--|--|--|

|               | IDCODE (32 Bits) (1)                       |                                                  |               |   |  |  |  |  |  |  |  |  |

| Device        | Version<br>(4 Bits)                        | (4 Bits) Part Number (16 Bits) Bits) LSB (1 Bit) |               |   |  |  |  |  |  |  |  |  |

| EP2S15        | 0000                                       | 0010 0000 1001 0001                              | 000 0110 1110 | 1 |  |  |  |  |  |  |  |  |

| EP2S30        | 0000                                       | 0010 0000 1001 0010                              | 000 0110 1110 | 1 |  |  |  |  |  |  |  |  |

| EP2S60        | 0001                                       | 0010 0000 1001 0011                              | 000 0110 1110 | 1 |  |  |  |  |  |  |  |  |

| EP2S90        | 0000                                       | 0010 0000 1001 0100                              | 000 0110 1110 | 1 |  |  |  |  |  |  |  |  |

| EP2S130       | 0000                                       | 0010 0000 1001 0101                              | 000 0110 1110 | 1 |  |  |  |  |  |  |  |  |

| EP2S180       | 0000                                       | 0010 0000 1001 0110                              | 000 0110 1110 | 1 |  |  |  |  |  |  |  |  |

#### Notes to Table 3–3:

(1) The most significant bit (MSB) is on the left.

(2) The IDCODE's least significant bit (LSB) is always 1.

P

Stratix, Stratix II, Cyclone, and Cyclone II devices must be within the first 17 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix, Stratix II, Cyclone, and Cyclone II devices are in the 18th or after they fail configuration. This does not affect SignalTap II.

#### P

An encryption configuration file is the same size as a nonencryption configuration file. When using a serial configuration scheme such as passive serial (PS) or active serial (AS), configuration time is the same whether or not the design security feature is enabled. If the fast passive parallel (FPP) scheme us used with the design security or decompression feature, a 4× DCLK is required. This results in a slower configuration time when compared to the configuration time of an FPGA that has neither the design security, nor decompression feature enabled. For more information about this feature, refer to *AN 341: Using the Design Security Feature in Stratix II Devices.* Contact your local Altera sales representative to request this document.

#### Device Configuration Data Decompression

Stratix II FPGAs support decompression of configuration data, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory, and transmit this compressed bit stream to Stratix II FPGAs. During configuration, the Stratix II FPGA decompresses the bit stream in real time and programs its SRAM cells.

Stratix II FPGAs support decompression in the FPP (when using a MAX II device/microprocessor and flash memory), AS and PS configuration schemes. Decompression is not supported in the PPA configuration scheme nor in JTAG-based configuration.

#### Remote System Upgrades

Shortened design cycles, evolving standards, and system deployments in remote locations are difficult challenges faced by modern system designers. Stratix II devices can help effectively deal with these challenges with their inherent re-programmability and dedicated circuitry to perform remote system updates. Remote system updates help deliver feature enhancements and bug fixes without costly recalls, reduce time to market, and extend product life.

Stratix II FPGAs feature dedicated remote system upgrade circuitry to facilitate remote system updates. Soft logic (Nios<sup>®</sup> processor or user logic) implemented in the Stratix II device can download a new configuration image from a remote location, store it in configuration memory, and direct the dedicated remote system upgrade circuitry to initiate a reconfiguration cycle. The dedicated circuitry performs error detection during and after the configuration process, recovers from any error condition by reverting back to a safe configuration image, and provides

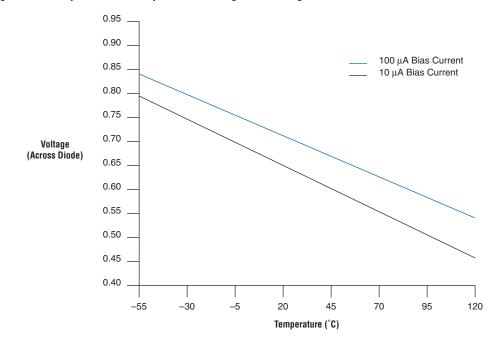

The temperature-sensing diode works for the entire operating range, as shown in Figure 3–2.

Figure 3–2. Temperature vs. Temperature-Sensing Diode Voltage

The temperature sensing diode is a very sensitive circuit which can be influenced by noise coupled from other traces on the board, and possibly within the device package itself, depending on device usage. The interfacing device registers temperature based on milivolts of difference as seen at the TSD. Switching I/O near the TSD pins can affect the temperature reading. Altera recommends you take temperature readings during periods of no activity in the device (for example, standby mode where no clocks are toggling in the device), such as when the nearby I/Os are at a DC state, and disable clock networks in the device.

## Automated Single Event Upset (SEU) Detection

Stratix II devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. Some applications that require the device to operate error free at high elevations or in close proximity to Earth's North or South Pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by

| Table 5- | Table 5–3. Stratix II Device Recommended Operating Conditions (Part 2 of 2)   Note (1) |                      |         |         |      |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------|----------------------|---------|---------|------|--|--|--|--|--|

| Symbol   | Parameter                                                                              | Conditions           | Minimum | Maximum | Unit |  |  |  |  |  |

| TJ       | Operating junction temperature                                                         | For commercial use   | 0       | 85      | °C   |  |  |  |  |  |

|          |                                                                                        | For industrial use   | -40     | 100     | °C   |  |  |  |  |  |

|          |                                                                                        | For military use (7) | -55     | 125     | °C   |  |  |  |  |  |

#### Notes to Table 5–3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 µs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, your Stratix II device does not configure successfully. If your system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, you must hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6)  $V_{CCIO}$  maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

- (7) For more information, refer to the *Stratix II Military Temperature Range Support* technical brief.

## **DC Electrical Characteristics**

Table 5-4 shows the Stratix II device family DC electrical characteristics.

| Table 5-            | 4. Stratix II Device DC Op            | erating Conditions                 | (Part 1 of 2) | Note (1) |         |         |      |

|---------------------|---------------------------------------|------------------------------------|---------------|----------|---------|---------|------|

| Symbol              | Parameter                             | Conditio                           | ins           | Minimum  | Typical | Maximum | Unit |

| I <sub>I</sub>      | Input pin leakage current             | $V_I = V_{CCIOmax}$ to 0 V         | -10           |          | 10      | μA      |      |

| I <sub>OZ</sub>     | Tri-stated I/O pin<br>leakage current | $V_{O} = V_{CCIOmax}$ to 0         | -10           |          | 10      | μA      |      |

| I <sub>CCINT0</sub> | V <sub>CCINT</sub> supply current     | $V_I = ground, no$                 | EP2S15        |          | 0.25    | (3)     | А    |

|                     | (standby)                             | load, no toggling<br>inputs        | EP2S30        |          | 0.30    | (3)     | А    |

|                     |                                       | $T_J = 25^{\circ} C$               | EP2S60        |          | 0.50    | (3)     | А    |

|                     |                                       | E                                  | EP2S90        |          | 0.62    | (3)     | Α    |

|                     |                                       |                                    | EP2S130       |          | 0.82    | (3)     | А    |

|                     |                                       |                                    | EP2S180       |          | 1.12    | (3)     | А    |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current      | $V_I = ground, no$                 | EP2S15        |          | 2.2     | (3)     | mA   |

|                     | (standby)                             | load, no toggling                  | EP2S30        |          | 2.7     | (3)     | mA   |

|                     |                                       | inputs<br>T <sub>.1</sub> = 25° C, | EP2S60        |          | 3.6     | (3)     | mA   |

|                     |                                       | $V_{CCPD} = 3.3V$                  | EP2S90        |          | 4.3     | (3)     | mA   |

|                     |                                       |                                    | EP2S130       |          | 5.4     | (3)     | mA   |

|                     |                                       |                                    | EP2S180       |          | 6.8     | (3)     | mA   |

The performance numbers in Table 5–36 are extracted from the Quartus II software version 5.1 SP1.

| Table 5–3           | 36. Stratix II Performand                    | ce Notes | (Part 1 of 6)                 | Note          | e (1)                       |                             |                                     |        |      |

|---------------------|----------------------------------------------|----------|-------------------------------|---------------|-----------------------------|-----------------------------|-------------------------------------|--------|------|

|                     |                                              | R        | esources Us                   | ed            | Performance                 |                             |                                     |        |      |

|                     | Applications                                 | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade<br>(3) | -4 -5<br>Speed Speed<br>Grade Grade |        | Unit |

| LE                  | 16-to-1 multiplexer (4)                      | 21       | 0                             | 0             | 654.87                      | 625.0                       | 523.83                              | 460.4  | MHz  |

|                     | 32-to-1 multiplexer (4)                      | 38       | 0                             | 0             | 519.21                      | 473.26                      | 464.25                              | 384.17 | MHz  |

|                     | 16-bit counter                               | 16       | 0                             | 0             | 566.57                      | 538.79                      | 489.23                              | 421.05 | MHz  |

|                     | 64-bit counter                               | 64       | 0                             | 0             | 244.31                      | 232.07                      | 209.11                              | 181.38 | MHz  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>32 × 18 bit          | 0        | 1                             | 0             | 500.00                      | 476.19                      | 434.02                              | 373.13 | MHz  |

| M512<br>block       | FIFO 32 x 18 bit                             | 22       | 1                             | 0             | 500.00                      | 476.19                      | 434.78                              | 373.13 | MHz  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>128 x 36 bit (8)     | 0        | 1                             | 0             | 540.54                      | 515.46                      | 469.48                              | 401.60 | MHz  |

| M4K<br>block        | True dual-port RAM 128 $\times$ 18 bit (8)   | 0        | 1                             | 0             | 540.54                      | 515.46                      | 469.48                              | 401.60 | MHz  |

|                     | FIFO<br>128 × 36 bit                         | 22       | 1                             | 0             | 530.22                      | 499.00                      | 469.48                              | 401.60 | MHz  |

|                     | Simple dual-port RAM 128 $\times$ 36 bit (9) | 0        | 1                             | 0             | 475.28                      | 453.30                      | 413.22                              | 354.10 | MHz  |

|                     | True dual-port RAM 128 $\times$ 18 bit (9)   | 0        | 1                             | 0             | 475.28                      | 453.30                      | 413.22                              | 354.10 | MHz  |

|                     |                                      | R     | esources Us                   | ed            | Performance                 |                             |                      |                      |     |  |

|---------------------|--------------------------------------|-------|-------------------------------|---------------|-----------------------------|-----------------------------|----------------------|----------------------|-----|--|

| Applications        |                                      | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade<br>(3) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Uni |  |

| TriMatrix<br>Memory | Single port<br>RAM 4K × 144 bit      | 0     | 1                             | 0             | 349.65                      | 333.33                      | 303.95               | 261.09               | MHz |  |

| M-RAM<br>block      | Simple dual-port<br>RAM 4K × 144 bit | 0     | 1                             | 0             | 420.16                      | 400.00                      | 364.96               | 313.47               | MHz |  |

|                     | True dual-port<br>RAM 4K × 144 bit   | 0     | 1                             | 0             | 349.65                      | 333.33                      | 303.95               | 261.09               | MHz |  |

|                     | Single port<br>RAM 8K × 72 bit       | 0     | 1                             | 0             | 354.60                      | 337.83                      | 307.69               | 263.85               | MHz |  |

|                     | Simple dual-port<br>RAM 8K × 72 bit  | 0     | 1                             | 0             | 420.16                      | 400.00                      | 364.96               | 313.47               | MHz |  |

|                     | True dual-port<br>RAM 8K × 72 bit    | 0     | 1                             | 0             | 349.65                      | 333.33                      | 303.95               | 261.09               | MH  |  |

|                     | Single port<br>RAM 16K × 36 bit      | 0     | 1                             | 0             | 364.96                      | 347.22                      | 317.46               | 271.73               | MH  |  |

|                     | Simple dual-port<br>RAM 16K × 36 bit | 0     | 1                             | 0             | 420.16                      | 400.00                      | 364.96               | 313.47               | MH  |  |

|                     | True dual-port<br>RAM 16K × 36 bit   | 0     | 1                             | 0             | 359.71                      | 342.46                      | 313.47               | 268.09               | MH  |  |

|                     | Single port<br>RAM 32K × 18 bit      | 0     | 1                             | 0             | 364.96                      | 347.22                      | 317.46               | 271.73               | MH  |  |

|                     | Simple dual-port<br>RAM 32K × 18 bit | 0     | 1                             | 0             | 420.16                      | 400.0                       | 364.96               | 313.47               | MH  |  |

| -                   | True dual-port<br>RAM 32K × 18 bit   | 0     | 1                             | 0             | 359.71                      | 342.46                      | 313.47               | 268.09               | MH  |  |

|                     | Single port<br>RAM 64K × 9 bit       | 0     | 1                             | 0             | 364.96                      | 347.22                      | 317.46               | 271.73               | MH  |  |

|                     | Simple dual-port<br>RAM 64K × 9 bit  | 0     | 1                             | 0             | 420.16                      | 400.0                       | 364.96               | 313.47               | MH  |  |

|                     | True dual-port<br>RAM 64K × 9 bit    | 0     | 1                             | 0             | 359.71                      | 342.46                      | 313.47               | 268.09               | MH  |  |

## **Internal Timing Parameters**

See Tables 5–37 through 5–42 for internal timing parameters.

| Quanda al          | Parameter                              | -3 Speed<br>Grade (1) |     | -3 Speed<br>Grade (2) |     | -4 Speed<br>Grade |     | -5 Speed<br>Grade |     | Unit |

|--------------------|----------------------------------------|-----------------------|-----|-----------------------|-----|-------------------|-----|-------------------|-----|------|

| Symbol             |                                        | Min<br><i>(3)</i>     | Max | Min<br><i>(3)</i>     | Max | Min<br>(4)        | Max | Min<br><i>(3)</i> | Max |      |

| t <sub>SU</sub>    | LE register setup time before<br>clock | 90                    |     | 95                    |     | 104<br>104        |     | 121               |     | ps   |

| t <sub>H</sub>     | LE register hold time after clock      | 149                   |     | 157                   |     | 172<br>172        |     | 200               |     | ps   |

| t <sub>co</sub>    | LE register clock-to-output delay      | 62                    | 94  | 62                    | 99  | 59<br>62          | 109 | 62                | 127 | ps   |

| t <sub>CLR</sub>   | Minimum clear pulse width              | 204                   |     | 214                   |     | 234<br>234        |     | 273               |     | ps   |

| t <sub>PRE</sub>   | Minimum preset pulse width             | 204                   |     | 214                   |     | 234<br>234        |     | 273               |     | ps   |

| t <sub>CLKL</sub>  | Minimum clock low time                 | 612                   |     | 642                   |     | 703<br>703        |     | 820               |     | ps   |

| t <sub>CLKH</sub>  | Minimum clock high time                | 612                   |     | 642                   |     | 703<br>703        |     | 820               |     | ps   |

| t <sub>lut</sub>   |                                        | 162                   | 378 | 162                   | 397 | 162<br>170        | 435 | 162               | 507 | ps   |

| t <sub>adder</sub> |                                        | 354                   | 619 | 354                   | 650 | 354<br>372        | 712 | 354               | 829 | ps   |

#### Notes to Table 5–37:

- (1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Sumbol                   | Parameter                                               | -3 Speed<br>Grade <i>(2)</i> |       | -3 Speed<br>Grade <i>(</i> 3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | Unit |

|--------------------------|---------------------------------------------------------|------------------------------|-------|-------------------------------|-------|-------------------|-------|-------------------|-------|------|

| Symbol                   |                                                         | Min<br>(4)                   | Max   | Min<br>(4)                    | Max   | Min<br>(5)        | Max   | Min<br>(4)        | Max   | Unit |

| t <sub>M512DATACO1</sub> | Clock-to-output delay<br>when using output<br>registers | 298                          | 478   | 298                           | 501   | 284<br>298        | 548   | 298               | 640   | ps   |

| t <sub>m512Dataco2</sub> | Clock-to-output delay without output registers          | 2,102                        | 2,345 | 2,102                         | 2,461 | 2,003<br>2,102    | 2,695 | 2,102             | 3,141 | ps   |

| t <sub>M512CLKL</sub>    | Minimum clock low time                                  | 1,315                        |       | 1,380                         |       | 1,512<br>1,512    |       | 1,762             |       | ps   |

| t <sub>M512CLKH</sub>    | Minimum clock high time                                 | 1,315                        |       | 1,380                         |       | 1,512<br>1,512    |       | 1,762             |       | ps   |

| t <sub>M512CLR</sub>     | Minimum clear pulse width                               | 144                          |       | 151                           |       | 165<br>165        |       | 192               |       | ps   |

#### Notes to Table 5-40:

Г

(1)  $F_{MAX}$  of M512 block obtained using the Quartus II software does not necessarily equal to 1/TM512RC.

(2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

(3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

(4) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

(5) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–41. M4K Block Internal Timing Microparameters (Part 1 of 2) Note (1) |                                              |                       |       |                       |       |                   |       |                   |       |      |

|------------------------------------------------------------------------------|----------------------------------------------|-----------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|------|

| Symbol                                                                       |                                              | -3 Speed<br>Grade (2) |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | 11   |

|                                                                              | Parameter                                    | Min<br>(4)            | Max   | Min<br>(4)            | Max   | Min<br>(5)        | Max   | Min<br>(4)        | Max   | Unit |

| t <sub>M4KRC</sub>                                                           | Synchronous read cycle time                  | 1,462                 | 2,240 | 1,462                 | 2,351 | 1,393<br>1,462    | 2,575 | 1,462             | 3,000 | ps   |

| t <sub>M4KWERESU</sub>                                                       | Write or read enable setup time before clock | 22                    |       | 23                    |       | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KWEREH</sub>                                                        | Write or read enable hold time after clock   | 203                   |       | 213                   |       | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KBESU</sub>                                                         | Byte enable setup time before clock          | 22                    |       | 23                    |       | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KBEH</sub>                                                          | Byte enable hold time after clock            | 203                   |       | 213                   |       | 233<br>233        |       | 272               |       | ps   |

| Table 5–65. EP2S180 Column Pins Global Clock Timing Parameters |                |            |          |          |          |      |  |  |  |

|----------------------------------------------------------------|----------------|------------|----------|----------|----------|------|--|--|--|

| Parameter                                                      | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |

|                                                                | Industrial     | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |

| t <sub>CIN</sub>                                               | 2.003          | 2.100      | 3.652    | 3.993    | 4.648    | ns   |  |  |  |

| t <sub>COUT</sub>                                              | 1.846          | 1.935      | 3.398    | 3.715    | 4.324    | ns   |  |  |  |

| t <sub>PLLCIN</sub>                                            | -0.3           | -0.29      | 0.053    | 0.054    | 0.058    | ns   |  |  |  |

| t <sub>PLLCOUT</sub>                                           | -0.457         | -0.455     | -0.201   | -0.224   | -0.266   | ns   |  |  |  |

| Table 5–66. EP2S180 Row Pins Regional Clock Timing Parameters |                |            |          |          |          |      |  |  |  |  |

|---------------------------------------------------------------|----------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                     | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

|                                                               | Industrial     | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                              | 1.759          | 1.844      | 3.273    | 3.577    | 4.162    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                             | 1.764          | 1.849      | 3.269    | 3.573    | 4.157    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                           | -0.542         | -0.541     | -0.317   | -0.353   | -0.414   | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.537         | -0.536     | -0.321   | -0.357   | -0.419   | ns   |  |  |  |  |

| Table 5–67. EP2S180 Row Pins Global Clock Timing Parameters |                |            |          |          |          |      |  |  |  |

|-------------------------------------------------------------|----------------|------------|----------|----------|----------|------|--|--|--|

| Parameter                                                   | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |

|                                                             | Industrial     | Commercial | Grade    | Grade    | Grade    | UIII |  |  |  |

| t <sub>CIN</sub>                                            | 1.763          | 1.850      | 3.285    | 3.588    | 4.176    | ns   |  |  |  |

| t <sub>COUT</sub>                                           | 1.768          | 1.855      | 3.281    | 3.584    | 4.171    | ns   |  |  |  |

| t <sub>PLLCIN</sub>                                         | -0.542         | -0.542     | -0.319   | -0.355   | -0.42    | ns   |  |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.537         | -0.537     | -0.323   | -0.359   | -0.425   | ns   |  |  |  |

| Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 6 of 8) |                   |                  |            |            |                       |                       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |  |

|-----------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| I/O Standard                                                          | Drive<br>Strength | Parameter        | Minimu     | -3         | -3                    | -4                    | -5    |                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |  |

|                                                                       |                   |                  | Industrial | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Grade | Speed<br>Grade                                                                                                                                                                                                                                                                                                                                                                                                                     | Unit |  |

| Differential                                                          | 8 mA              | t <sub>OP</sub>  | 913        | 957        | 1715                  | 1799                  | 1971  | 2041                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

| SSTL-2 Class I                                                        |                   | t <sub>DIP</sub> | 933        | 979        | 1781                  | 1869                  | 2047  | 2131                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 896        | 940        | 1672                  | 1754                  | 1921  | 1991                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 916        | 962        | 1738                  | 1824                  | 1997  | rade   Grade     971   2041     971   2131     921   1991     997   2081     849   1918     925   2008     836   1905     912   1993     912   1993     912   2012     013   2102     903   1973     979   2063     885   1954     961   2044     882   1952     958   2042     869   1938     945   2028     835   1904     911   1994     813   1882     889   1972     821   1890     837   1980     8397   1980     819   1888 | ps   |  |

| Differential                                                          | 16 mA             | t <sub>OP</sub>  | 876        | 918        | 1609                  | 1688                  | 1849  | 1918                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

| SSTL-2 Class II                                                       |                   | t <sub>DIP</sub> | 896        | 940        | 1675                  | 1758                  | 1925  | 2008                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       | 20 mA             | t <sub>OP</sub>  | 877        | 919        | 1598                  | 1676                  | 1836  | 1905                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 897        | 941        | 1664                  | 1746                  | 1912  | 1995                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       | 24 mA             | t <sub>OP</sub>  | 872        | 915        | 1596                  | 1674                  | 1834  | 1903                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 892        | 937        | 1662                  | 1744                  | 1910  | 1993                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

| Differential                                                          | 4 mA              | t <sub>OP</sub>  | 909        | 953        | 1690                  | 1773                  | 1942  | 2012                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

| SSTL-18<br>Class I                                                    |                   | t <sub>DIP</sub> | 929        | 975        | 1756                  | 1843                  | 2018  | 2102                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       | 6 mA              | t <sub>OP</sub>  | 914        | 958        | 1656                  | 1737                  | 1903  | 1973                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 934        | 980        | 1722                  | 1807                  | 1979  | Speed<br>Grade     2041     2131     1991     2081     1993     2008     1995     1993     2012     1973     2063     1954     2044     1952     2042     1938     2028     1994     1994     1994     1994     1994     1882     1972     1880     1980     1888                                                                                                                                                                  | ps   |  |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 894        | 937        | 1640                  | 1721                  | 1885  | 1954                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 914        | 959        | 1706                  | 1791                  | 1961  | 2044                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       | 10 mA             | t <sub>OP</sub>  | 898        | 942        | 1638                  | 1718                  | 1882  | 1952                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 918        | 964        | 1704                  | 1788                  | 1958  | 2042                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 891        | 936        | 1626                  | 1706                  | 1869  | 1938                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 911        | 958        | 1692                  | 1776                  | 1945  | 2028                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

| Differential                                                          | 8 mA              | t <sub>OP</sub>  | 883        | 925        | 1597                  | 1675                  | 1835  | 1904                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

| SSTL-18<br>Class II                                                   |                   | t <sub>DIP</sub> | 903        | 947        | 1663                  | 1745                  | 1911  | 1994                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

| 0.000 11                                                              | 16 mA             | t <sub>OP</sub>  | 894        | 937        | 1578                  | 1655                  | 1813  | 1882                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 914        | 959        | 1644                  | 1725                  | 1889  | 1972                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       | 18 mA             | t <sub>OP</sub>  | 890        | 933        | 1585                  | 1663                  | 1821  | 1890                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 910        | 955        | 1651                  | 1733                  | 1897  | 1980                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       | 20 mA             | t <sub>OP</sub>  | 890        | 933        | 1583                  | 1661                  | 1819  | 1888                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

|                                                                       |                   | t <sub>DIP</sub> | 910        | 955        | 1649                  | 1731                  | 1895  | 1978                                                                                                                                                                                                                                                                                                                                                                                                                               | ps   |  |

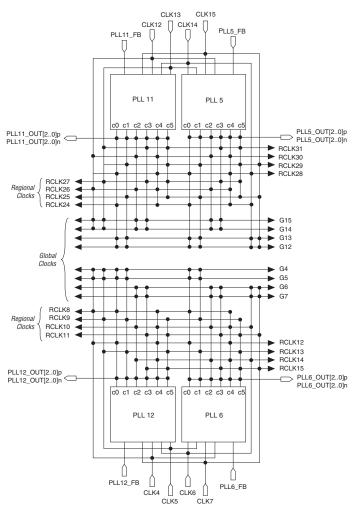

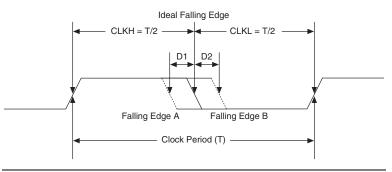

DCD expressed in absolution derivation, for example, D1 or D2 in Figure 5–7, is clock-period independent. DCD can also be expressed as a percentage, and the percentage number is clock-period dependent. DCD as a percentage is defined as

(T/2 – D1) / T (the low percentage boundary)

(T/2 + D2) / T (the high percentage boundary)

### **DCD Measurement Techniques**

DCD is measured at an FPGA output pin driven by registers inside the corresponding I/O element (IOE) block. When the output is a single data rate signal (non-DDIO), only one edge of the register input clock (positive or negative) triggers output transitions (Figure 5–8). Therefore, any DCD present on the input clock signal or caused by the clock input buffer or different input I/O standard does not transfer to the output signal.

Figure 5–8. DCD Measurement Technique for Non-DDIO (Single-Data Rate) Outputs