Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 4548                                                     |

| Number of Logic Elements/Cells | 90960                                                    |

| Total RAM Bits                 | 4520488                                                  |

| Number of I/O                  | 534                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BBGA                                                 |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s90f780c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

iν

| Open-Drain Output                                                                                       | 2–84 |

|---------------------------------------------------------------------------------------------------------|------|

| Bus Hold                                                                                                |      |

| Programmable Pull-Up Resistor                                                                           |      |

| Advanced I/O Standard Support                                                                           |      |

| On-Chip Termination                                                                                     |      |

| MultiVolt I/O Interface                                                                                 |      |

| High-Speed Differential I/O with DPA Support                                                            |      |

| Dedicated Circuitry with DPA Support                                                                    |      |

| Fast PLL & Channel Layout                                                                               |      |

| Document Revision History                                                                               |      |

| Chapter 3. Configuration & Testing                                                                      |      |

| IEEE Std. 1149.1 JTAG Boundary-Scan Support                                                             | 3_1  |

| SignalTap II Embedded Logic Analyzer                                                                    |      |

| Configuration                                                                                           |      |

| Operating Modes                                                                                         |      |

| Configuration Schemes                                                                                   |      |

| Configuring Stratix II FPGAs with JRunner                                                               |      |

| Programming Serial Configuration Devices with SRunner                                                   | 3_10 |

| Configuring Stratix II FPGAs with the MicroBlaster Driver                                               |      |

| PLL Reconfiguration                                                                                     |      |

| Temperature Sensing Diode (TSD)                                                                         |      |

| Automated Single Event Upset (SEU) Detection                                                            | 3_13 |

| Custom-Built Circuitry                                                                                  |      |

| Software Interface                                                                                      |      |

| Document Revision History                                                                               |      |

| Document Revision History                                                                               | 0 14 |

| Chapter 4. Hot Socketing & Power-On Reset                                                               |      |

| Stratix II                                                                                              |      |

| Hot-Socketing Specifications                                                                            | 4–1  |

| Devices Can Be Driven Before Power-Up                                                                   |      |

| I/O Pins Remain Tri-Stated During Power-Up                                                              |      |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> , V <sub>CCINT</sub> or V <sub>CCPD</sub> Power Supplies |      |

| Hot Socketing Feature Implementation in Stratix II Devices                                              |      |

| Power-On Reset Circuitry                                                                                |      |

| Document Revision History                                                                               |      |

| Chapter 5. DC & Switching Characteristics                                                               |      |

| Operating Conditions                                                                                    | 5.1  |

| Absolute Maximum Ratings                                                                                |      |

|                                                                                                         |      |

| Recommended Operating Conditions                                                                        |      |

|                                                                                                         |      |

| I/O Standard Specifications                                                                             |      |

| Bus Hold Specifications On-Chip Termination Specifications                                              |      |

| *                                                                                                       |      |

| Pin Capacitance                                                                                         |      |

| Power Consumption                                                                                       | 5–20 |

Stratix II devices are available in up to three speed grades, -3, -4, and -5, with -3 being the fastest. Table 1-5 shows Stratix II device speed-grade offerings.

| Table 1–5. Stratix II Device Speed Grades |                      |                            |                                      |                            |                            |                              |                              |  |

|-------------------------------------------|----------------------|----------------------------|--------------------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--|

| Device                                    | Temperature<br>Grade | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |  |

| EP2S15                                    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |  |

|                                           | Industrial           | -4                         |                                      | -4                         |                            |                              |                              |  |

| EP2S30                                    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |  |

|                                           | Industrial           | -4                         |                                      | -4                         |                            |                              |                              |  |

| EP2S60                                    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            | -3, -4, -5                   |                              |  |

|                                           | Industrial           | -4                         |                                      | -4                         |                            | -4                           |                              |  |

| EP2S90                                    | Commercial           |                            | -4, -5                               |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |  |

|                                           | Industrial           |                            |                                      |                            |                            | -4                           | -4                           |  |

| EP2S130                                   | Commercial           |                            |                                      |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |  |

|                                           | Industrial           |                            |                                      |                            |                            | -4                           | -4                           |  |

| EP2S180                                   | Commercial           |                            |                                      |                            | _                          | -3, -4, -5                   | -3, -4, -5                   |  |

|                                           | Industrial           | •                          |                                      |                            |                            | -4                           | -4                           |  |

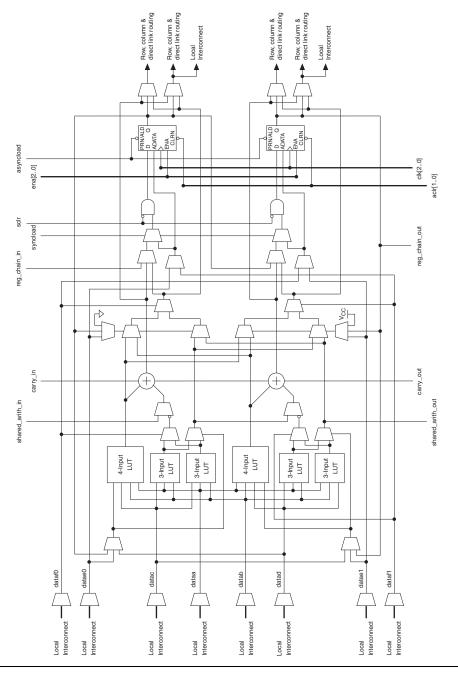

Figure 2-6. Stratix II ALM Details

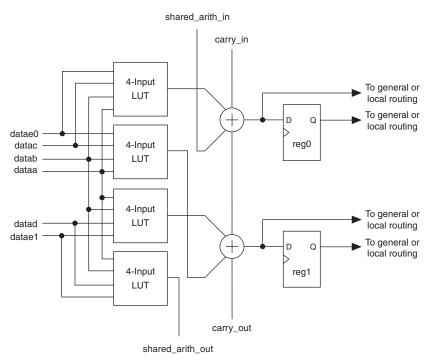

Figure 2-13. ALM in Shared Arithmetic Mode

Note to Figure 2-13:

(1) Inputs dataf0 and dataf1 are available for register packing in shared arithmetic mode.

Adder trees can be found in many different applications. For example, the summation of the partial products in a logic-based multiplier can be implemented in a tree structure. Another example is a correlator function that can use a large adder tree to sum filtered data samples in a given time frame to recover or to de-spread data which was transmitted utilizing spread spectrum technology.

An example of a three-bit add operation utilizing the shared arithmetic mode is shown in Figure 2–14. The partial sum (S[2..0]) and the partial carry (C[2..0]) is obtained using the LUTs, while the result (R[2..0]) is computed using the dedicated adders.

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between LABs, TriMatrix memory, DSP blocks, and Row IOEs. The R24 row interconnects can cross M-RAM blocks. R24 row interconnects drive to other row or column interconnects at every fourth LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

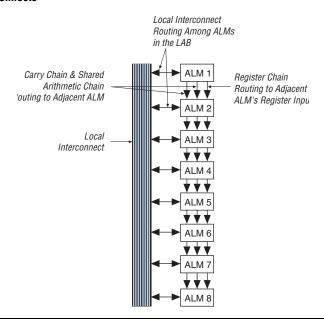

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect. These column resources include:

- Shared arithmetic chain interconnects in an LAB

- Carry chain interconnects in an LAB and from LAB to LAB

- Register chain interconnects in an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix II devices include an enhanced interconnect structure in LABs for routing shared arithmetic chains and carry chains for efficient arithmetic functions. The register chain connection allows the register output of one ALM to connect directly to the register input of the next ALM in the LAB for fast shift registers. These ALM to ALM connections bypass the local interconnect. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–17 shows the shared arithmetic chain, carry chain and register chain interconnects.

Figure 2–17. Shared Arithmetic Chain, Carry Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–18 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

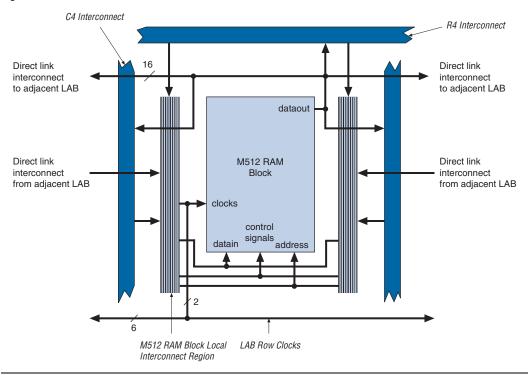

Figure 2-20. M512 RAM Block LAB Row Interface

#### M4K RAM Blocks

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

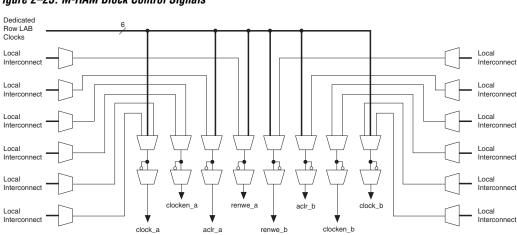

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M-RAM block registers (renwe, address, byte enable, datain, and output registers). The output register can be bypassed. The six labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 2–23.

Figure 2-23. M-RAM Block Control Signals

The R4, R24, C4, and direct link interconnects from adjacent LABs on either the right or left side drive the M-RAM block local interconnect. Up to 16 direct link input connections to the M-RAM block are possible from the left adjacent LABs and another 16 possible from the right adjacent LABs M-RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–24 shows an example floorplan for the EP2S130 device and the location of the M-RAM interfaces. Figures 2–25 and 2–26 show the interface between the M-RAM block and the logic array.

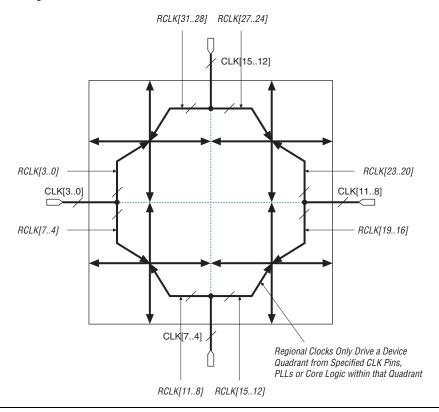

Figure 2-32. Regional Clocks

### Dual-Regional Clock Network

A single source (CLK pin or PLL output) can generate a dual-regional clock by driving two regional clock network lines in adjacent quadrants (one from each quadrant). This allows logic that spans multiple quadrants to utilize the same low skew clock. The routing of this clock signal on an entire side has approximately the same speed but slightly higher clock skew when compared with a clock signal that drives a single quadrant. Internal logic-array routing can also drive a dual-regional clock. Clock pins and enhanced PLL outputs on the top and bottom can drive horizontal dual-regional clocks. Clock pins and fast PLL outputs on the left and right can drive vertical dual-regional clocks, as shown in Figure 2–33. Corner PLLs cannot drive dual-regional clocks.

The Quartus II software enables the PLLs and their features without requiring any external devices. Table 2–9 shows the PLLs available for each Stratix II device and their type.

| Davisa      |          |          |          | Fast     | PLLs     |          |          |          |          | Enhanced PLLs |          |          |

|-------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|----------|----------|

| Device      | 1        | 2        | 3        | 4        | 7        | 8        | 9        | 10       | 5        | 6             | 11       | 12       |

| EP2S15      | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          |          | <b>✓</b> | <b>✓</b>      |          |          |

| EP2S30      | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          |          | <b>✓</b> | <b>✓</b>      |          |          |

| EP2S60 (1)  | <b>✓</b>      | <b>✓</b> | <b>✓</b> |

| EP2S90 (2)  | <b>✓</b>      | <b>✓</b> | <b>✓</b> |

| EP2S130 (3) | <b>✓</b>      | <b>✓</b> | <b>✓</b> |

| EP2S180     | <b>/</b> | <b>✓</b>      | <b>✓</b> | <b>/</b> |

#### Notes to Table 2-9:

- (1) EP2S60 devices in the 1020-pin package contain 12 PLLs. EP2S60 devices in the 484-pin and 672-pin packages contain fast PLLs 1–4 and enhanced PLLs 5 and 6.

- (2) EP2S90 devices in the 1020-pin and 1508-pin packages contain 12 PLLs. EP2S90 devices in the 484-pin and 780-pin packages contain fast PLLS 1–4 and enhanced PLLs 5 and 6.

- (3) EP2S130 devices in the 1020-pin and 1508-pin packages contain 12PLLs. The EP2S130 device in the 780-pin package contains fast PLLs 1–4 and enhanced PLLs 5 and 6.

### **Enhanced PLLs**

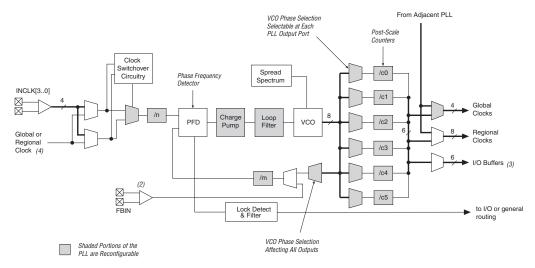

Stratix II devices contain up to four enhanced PLLs with advanced clock management features. Figure 2–44 shows a diagram of the enhanced PLL.

Figure 2–44. Stratix II Enhanced PLL Note (1)

#### *Notes to Figure 2–44:*

- (1) Each clock source can come from any of the four clock pins that are physically located on the same side of the device as the PLL.

- (2) If the feedback input is used, you lose one (or two, if FBIN is differential) external clock output pin.

- (3) Each enhanced PLL has three differential external clock outputs or six single-ended external clock outputs.

- (4) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

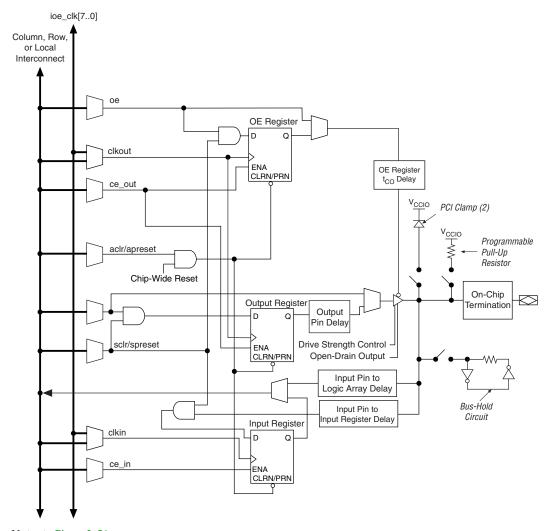

Figure 2–51 shows the IOE in bidirectional configuration.

Figure 2–51. Stratix II IOE in Bidirectional I/O Configuration

Notes to Figure 2-51:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

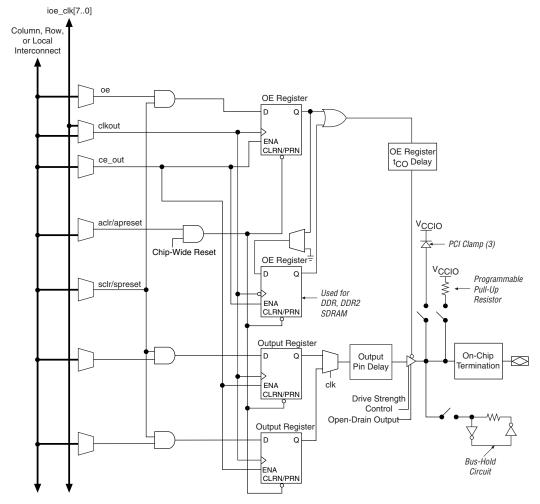

Figure 2–54. Stratix II IOE in DDR Output I/O Configuration Notes (1), (2)

*Notes to Figure 2–54:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The tri-state buffer is active low. The DDIO megafunction represents the tri-state buffer as active-high with an inverter at the OE register data port. Similarly, the aclr and apreset signals are also active-high at the input ports of the DDIO megafunction.

- (3) The optional PCI clamp is only available on column I/O pins.

| Table 2–20. Supported TDO/TDI Voltage Combinations (Part 2 of 2) |              |                                                              |                           |                           |                           |                           |  |  |

|------------------------------------------------------------------|--------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|

| Device                                                           | TDI Input    | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |                           |  |  |

| Device                                                           | Buffer Power | V <sub>CC10</sub> = 3.3 V                                    | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V | V <sub>CCIO</sub> = 1.5 V | V <sub>CC10</sub> = 1.2 V |  |  |

| Non-Stratix II                                                   | VCC = 3.3 V  | <b>√</b> (1)                                                 | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |

|                                                                  | VCC = 2.5 V  | <b>✓</b> (1), (4)                                            | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |

|                                                                  | VCC = 1.8 V  | <b>✓</b> (1), (4)                                            | <b>✓</b> (2), (5)         | ~                         | Level shifter required    | Level shifter required    |  |  |

|                                                                  | VCC = 1.5 V  | <b>√</b> (1), (4)                                            | <b>√</b> (2), (5)         | <b>√</b> (6)              | ✓                         | <b>✓</b>                  |  |  |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

## High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

For high-speed source synchronous interfaces such as POS-PHY 4, Parallel RapidIO, and HyperTransport, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix II device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for user-controlled byte boundary shifting. This simplifies designs while saving ALM resources. You can use an ALM-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

## **Fast PLL & Channel Layout**

The receiver and transmitter channels are interleaved such that each I/O bank on the left and right side of the device has one receiver channel and one transmitter channel per LAB row. Figure 2–60 shows the fast PLL and channel layout in the EP2S15 and EP2S30 devices. Figure 2–61 shows the fast PLL and channel layout in the EP2S60 to EP2S180 devices.

LVDS DPA DΡΔ LVDS Clock Clock Clock Clock Quadrant Quadrant 2 Fast Fast PLL 1 PLL 4 Fast Fast PLL 3 PLL 2 2 Quadrant Quadrant LVDS DPA DΡΔ LVDS Clock Clock Clock Clock

Figure 2–60. Fast PLL & Channel Layout in the EP2S15 & EP2S30 Devices Note (1)

*Note to Figure 2–60:*

(1) See Table 2–21 for the number of channels each device supports.

## 4. Hot Socketing & Power-On Reset

SII51004-3.2

Stratix<sup>®</sup> II devices offer hot socketing, which is also known as hot plug-in or hot swap, and power sequencing support without the use of any external devices. You can insert or remove a Stratix II board in a system during system operation without causing undesirable effects to the running system bus or the board that was inserted into the system.

The hot socketing feature also removes some of the difficulty when you use Stratix II devices on printed circuit boards (PCBs) that also contain a mixture of 5.0-, 3.3-, 2.5-, 1.8-, 1.5- and 1.2-V devices. With the Stratix II hot socketing feature, you no longer need to ensure a proper power-up sequence for each device on the board.

The Stratix II hot socketing feature provides:

- Board or device insertion and removal without external components or board manipulation

- Support for any power-up sequence

- Non-intrusive I/O buffers to system buses during hot insertion

This chapter also discusses the power-on reset (POR) circuitry in Stratix II devices. The POR circuitry keeps the devices in the reset state until the  $V_{CC}$  is within operating range.

## Stratix II Hot-Socketing Specifications

Stratix II devices offer hot socketing capability with all three features listed above without any external components or special design requirements. The hot socketing feature in Stratix II devices allows:

- The device can be driven before power-up without any damage to the device itself.

- I/O pins remain tri-stated during power-up. The device does not drive out before or during power-up, thereby affecting other buses in operation.

- Signal pins do not drive the  $V_{CCIO}$ ,  $V_{CCPD}$ , or  $V_{CCINT}$  power supplies. External input signals to I/O pins of the device do not internally power the  $V_{CCIO}$  or  $V_{CCINT}$  power supplies of the device via internal paths within the device.

I<sub>IOPIN</sub> is the current at any user I/O pin on the device. This specification takes into account the pin capacitance, but not board trace and external loading capacitance. Additional capacitance for trace, connector, and loading needs must be considered separately. For the AC specification, the peak current duration is 10 ns or less because of power-up transients. For more information, refer to the Hot-Socketing & Power-Sequencing Feature & Testing for Altera Devices white paper.

A possible concern regarding hot-socketing is the potential for latch-up. Latch-up can occur when electrical subsystems are hot-socketed into an active system. During hot-socketing, the signal pins may be connected and driven by the active system before the power supply can provide current to the device's  $V_{CC}$  and ground planes. This condition can lead to latch-up and cause a low-impedance path from  $V_{CC}$  to ground within the device. As a result, the device extends a large amount of current, possibly causing electrical damage. Nevertheless, Stratix II devices are immune to latch-up when hot-socketing.

## Hot Socketing Feature Implementation in Stratix II Devices

The hot socketing feature turns off the output buffer during the power-up event (either  $V_{\rm CCINT}, V_{\rm CCIO},$  or  $V_{\rm CCPD}$  supplies) or power down. The hot-socket circuit will generate an internal HOTSCKT signal when either  $V_{\rm CCINT}, V_{\rm CCIO},$  or  $V_{\rm CCPD}$  is below threshold voltage. The HOTSCKT signal will cut off the output buffer to make sure that no DC current (except for weak pull up leaking) leaks through the pin. When  $V_{\rm CC}$  ramps up very slowly,  $V_{\rm CC}$  is still relatively low even after the POR signal is released and the configuration is finished. The CONF\_DONE, nCEO, and nSTATUS pins fail to respond, as the output buffer can not flip from the state set by the hot socketing circuit at this low  $V_{\rm CC}$  voltage. Therefore, the hot socketing circuit has been removed on these configuration pins to make sure that they are able to operate during configuration. It is expected behavior for these pins to drive out during power-up and power-down sequences.

Each I/O pin has the following circuitry shown in Figure 4–1.

# Document Revision History

Table 4–1 shows the revision history for this chapter.

| Table 4–1. Document Revision History |                                                                                                                                                               |                                                             |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| Date and<br>Document<br>Version      | Changes Made                                                                                                                                                  | Summary of Changes                                          |  |  |  |  |

| May 2007, v3.2                       | Moved the Document Revision History section to the end of the chapter.                                                                                        | _                                                           |  |  |  |  |

| April 2006,<br>v3.1                  | Updated "Signal Pins Do Not Drive the VCCIO,<br>VCCINT or VCCPD Power Supplies" section.                                                                      | <ul> <li>Updated hot socketing AC specification.</li> </ul> |  |  |  |  |

| May 2005, v3.0                       | <ul> <li>Updated "Signal Pins Do Not Drive the VCCIO,<br/>VCCINT or VCCPD Power Supplies" section.</li> <li>Removed information on ESD protection.</li> </ul> | _                                                           |  |  |  |  |

| January 2005,<br>v2.1                | Updated input rise and fall time.                                                                                                                             | _                                                           |  |  |  |  |

| January 2005,<br>v2.0                | Updated the "Hot Socketing Feature Implementation in Stratix II Devices", "ESD Protection", and "Power-On Reset Circuitry" sections.                          | _                                                           |  |  |  |  |

| July 2004, v1.1                      | <ul><li>Updated all tables.</li><li>Added tables.</li></ul>                                                                                                   | _                                                           |  |  |  |  |

| February 2004,<br>v1.0               | Added document to the Stratix II Device Handbook.                                                                                                             | _                                                           |  |  |  |  |

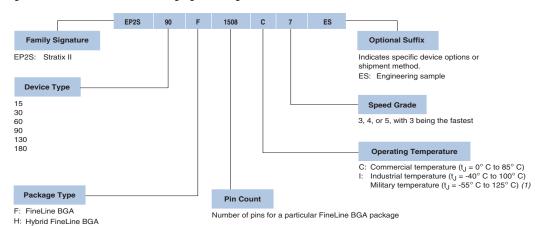

Figure 6-1. Stratix II Device Packaging Ordering Information

Note to Figure 6-1:

Applicable to I4 devices. For more information, refer to the Stratix II Military Temperature Range Support technical brief.

## Document Revision History

Table 6–1 shows the revision history for this chapter.

| Table 6–1. Document Revision History |                                                                        |                                                        |  |  |  |  |

|--------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| Date and<br>Document<br>Version      | Changes Made                                                           | Summary of Changes                                     |  |  |  |  |

| April 2011,<br>v2.2                  | Updated Figure 6–1.                                                    | Added operating junction temperature for military use. |  |  |  |  |

| May 2007,<br>v2.1                    | Moved the Document Revision History section to the end of the chapter. | _                                                      |  |  |  |  |

| January<br>2005, v2.0                | Contact information was removed.                                       | _                                                      |  |  |  |  |

| October<br>2004, v1.1                | Updated Figure 6–1.                                                    | _                                                      |  |  |  |  |

| February<br>2004, v1.0               | Added document to the Stratix II Device Handbook.                      | _                                                      |  |  |  |  |