Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 4548                                                    |

| Number of Logic Elements/Cells | 90960                                                   |

| Total RAM Bits                 | 4520488                                                 |

| Number of I/O                  | 534                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 780-BBGA                                                |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s90f780i4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section I–2 Altera Corporation

Stratix II devices are available in space-saving FineLine BGA® packages (see Tables 1–2 and 1–3).

| Table 1–2. S | Stratix II Package      | Options & I/O                        | Pin Counts                 | Notes (1), (2)             |                           |                           |

|--------------|-------------------------|--------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------|

| Device       | 484-Pin<br>FineLine BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |

| EP2S15       | 342                     |                                      | 366                        |                            |                           |                           |

| EP2S30       | 342                     |                                      | 500                        |                            |                           |                           |

| EP2S60 (3)   | 334                     |                                      | 492                        |                            | 718                       |                           |

| EP2S90 (3)   |                         | 308                                  |                            | 534                        | 758                       | 902                       |

| EP2S130 (3)  |                         |                                      |                            | 534                        | 742                       | 1,126                     |

| EP2S180 (3)  |                         |                                      |                            |                            | 742                       | 1,170                     |

#### Notes to Table 1-2:

- (1) All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk11p, and clk11n) that can be used for data inputs.

- (2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as general-purpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

- (3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. St            | Table 1–3. Stratix II FineLine BGA Package Sizes |                   |         |         |           |           |  |  |  |  |  |  |

|--------------------------|--------------------------------------------------|-------------------|---------|---------|-----------|-----------|--|--|--|--|--|--|

| Dimension                | 484 Pin                                          | 484-Pin<br>Hybrid | 672 Pin | 780 Pin | 1,020 Pin | 1,508 Pin |  |  |  |  |  |  |

| Pitch (mm)               | 1.00                                             | 1.00              | 1.00    | 1.00    | 1.00      | 1.00      |  |  |  |  |  |  |

| Area (mm2)               | 529                                              | 729               | 729     | 841     | 1,089     | 1,600     |  |  |  |  |  |  |

| Length × width (mm × mm) | 23 × 23                                          | 27 × 27           | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |  |  |  |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

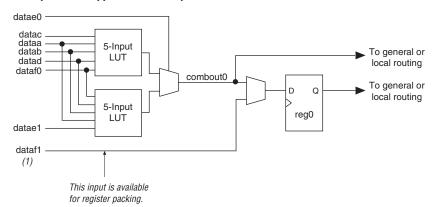

Figure 2–10. Template for Supported Seven-Input Functions in Extended LUT Mode

Note to Figure 2-10:

If the seven-input function is unregistered, the unused eighth input is available for register packing. The second register, reg1, is not available.

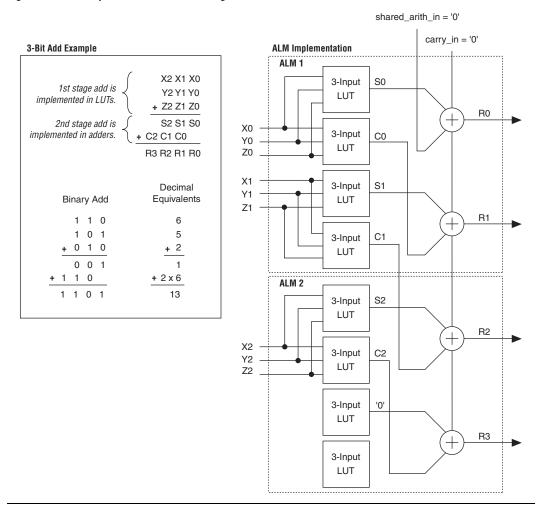

#### Arithmetic Mode

The arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An ALM in arithmetic mode uses two sets of two four-input LUTs along with two dedicated full adders. The dedicated adders allow the LUTs to be available to perform pre-adder logic; therefore, each adder can add the output of two four-input functions. The four LUTs share the dataa and datab inputs. As shown in Figure 2–11, the carry-in signal feeds to adder0, and the carry-out from adder0 feeds to carry-in of adder1. The carry-out from adder1 drives to adder0 of the next ALM in the LAB. ALMs in arithmetic mode can drive out registered and/or unregistered versions of the adder outputs.

Figure 2-14. Example of a 3-bit Add Utilizing Shared Arithmetic Mode

#### **Shared Arithmetic Chain**

In addition to the dedicated carry chain routing, the shared arithmetic chain available in shared arithmetic mode allows the ALM to implement a three-input add. This significantly reduces the resources necessary to implement large adder trees or correlator functions.

The shared arithmetic chains can begin in either the first or fifth ALM in an LAB. The Quartus II Compiler creates shared arithmetic chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long shared

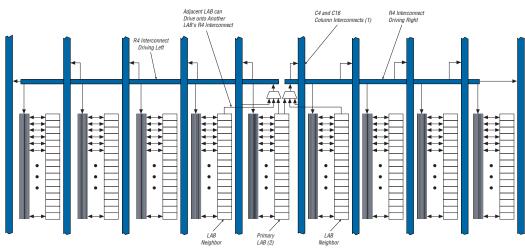

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2-16 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2–16. R4 Interconnect Connections Notes (1), (2), (3)

#### *Notes to Figure 2–16:*

- (1) C4 and C16 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

- (3) The LABs in Figure 2–16 show the 16 possible logical outputs per LAB.

Figure 2–41. Global & Regional Clock Connections from Center Clock Pins & Fast PLL Outputs Note (1)

#### Notes to Figure 2-41:

- (1) EP2S15 and EP2S30 devices only have four fast PLLs (1, 2, 3, and 4), but the connectivity from these four PLLs to the global and regional clock networks remains the same as shown.

- (2) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

| Table 2–11. Global & Region of 2)                        | al Clo   | ck Cor   | nectio   | ons fro  | т Тор    | Clock    | Pins     | & Enha   | anced    | PLL O    | utputs   | (Pa      | art 1    |

|----------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global & Regional<br>Clock Network Connectivity | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| Clock pins                                               |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK12p                                                   | <b>\</b> | <b>~</b> | <        |          |          | <b>\</b> |          |          |          | <b>~</b> |          |          |          |

| CLK13p                                                   | <b>✓</b> | <b>✓</b> | <b>\</b> |          |          |          | <b>~</b> |          |          |          |          |          | <b>~</b> |

| CLK14p                                                   | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15p                                                   | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |

| CLK12n                                                   |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13n                                                   |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |          |          | <b>✓</b> |

| CLK14n                                                   |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15n                                                   |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |

| Drivers from internal logic                              |          | ı        |          | ı        |          | ı        | ı        |          | ı        | ı        |          | ı        |          |

| GCLKDRV0                                                 |          | <b>~</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                 |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                 |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                 |          |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                 |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                 |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                 |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                 |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                 |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                 |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                 |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                 |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL 5 outputs                                   |          | I        | 1        | I        | 1        | I        | I        | 1        | I        | I        | 1        | I        |          |

| c0                                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| c2                                                       | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| c3                                                       | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

#### **Fast PLLs**

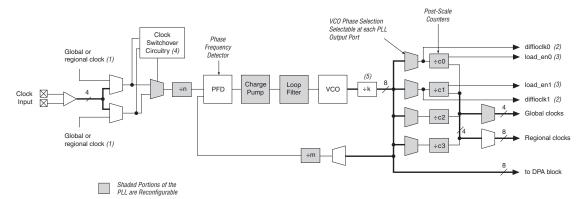

Stratix II devices contain up to eight fast PLLs with high-speed serial interfacing ability. Figure 2–45 shows a diagram of the fast PLL.

Figure 2–45. Stratix II Device Fast PLL Notes (1), (2), (3)

#### Notes to Figure 2-45:

- (1) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES circuitry. Stratix II devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a differential I/O SERDES control signal.

- (4) Stratix II fast PLLs only support manual clock switchover.

- (5) If the design enables this ÷2 counter, then the device can use a VCO frequency range of 150 to 520 MHz.

See the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information on enhanced and fast PLLs. See "High-Speed Differential I/O with DPA Support" on page 2–96 for more information on high-speed differential I/O support.

## I/O Structure

The Stratix II IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- On-chip driver series termination

- On-chip parallel termination

- On-chip termination for differential standards

- Programmable pull-up during configuration

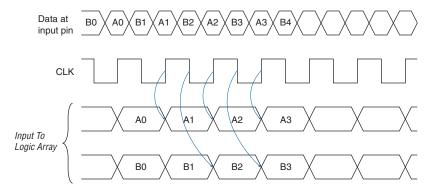

Figure 2-53. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from ALMs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–54 shows the IOE configured for DDR output. Figure 2–55 shows the DDR output timing diagram.

you need to support configuration input voltages of 1.8 V/1.5 V, you should set the VCCSEL to a logic high and the  $V_{CCIO}$  of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

## **Configuration Schemes**

You can load the configuration data for a Stratix II device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix II device. A configuration device can automatically configure a Stratix II device at system power-up.

You can configure multiple Stratix II devices in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

Stratix II FPGAs offer the following:

- Configuration data decompression to reduce configuration file storage

- Design security using configuration data encryption to protect your designs

- Remote system upgrades for remotely updating your Stratix II designs

Table 3–5 summarizes which configuration features can be used in each configuration scheme.

| Configuration Scheme | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |

|----------------------|--------------------------------------------------|-----------------|---------------|--------------------------|

| FPP                  | MAX II device or microprocessor and flash device | <b>√</b> (1)    | <b>√</b> (1)  | <b>✓</b>                 |

|                      | Enhanced configuration device                    |                 | <b>√</b> (2)  | ~                        |

| AS                   | Serial configuration device                      | ✓               | ✓             | <b>√</b> (3)             |

| PS                   | MAX II device or microprocessor and flash device | <b>✓</b>        | ~             | <b>✓</b>                 |

|                      | Enhanced configuration device                    | ✓               | ✓             | <b>✓</b>                 |

|                      | Download cable (4)                               | <b>✓</b>        | <b>✓</b>      |                          |

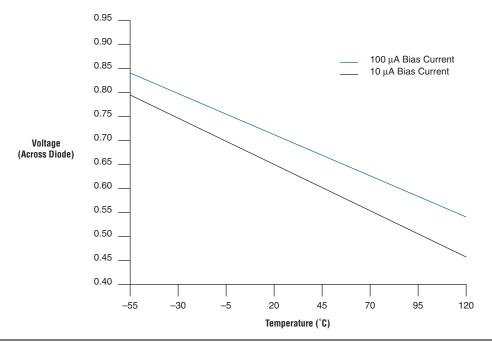

The temperature-sensing diode works for the entire operating range, as shown in Figure 3–2.

Figure 3–2. Temperature vs. Temperature-Sensing Diode Voltage

The temperature sensing diode is a very sensitive circuit which can be influenced by noise coupled from other traces on the board, and possibly within the device package itself, depending on device usage. The interfacing device registers temperature based on milivolts of difference as seen at the TSD. Switching I/O near the TSD pins can affect the temperature reading. Altera recommends you take temperature readings during periods of no activity in the device (for example, standby mode where no clocks are toggling in the device), such as when the nearby I/Os are at a DC state, and disable clock networks in the device.

Automated Single Event Upset (SEU) Detection Stratix II devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. Some applications that require the device to operate error free at high elevations or in close proximity to Earth's North or South Pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by

| Table 5                 | -21. SSTL-2 Class I & II Diff               | erential Spec | eifications                  |                         |                      |      |

|-------------------------|---------------------------------------------|---------------|------------------------------|-------------------------|----------------------|------|

| Symbol                  | Parameter                                   | Conditions    | Minimum                      | Typical                 | Maximum              | Unit |

| $V_{\text{CCIO}}$       | Output supply voltage                       |               | 2.375                        | 2.500                   | 2.625                | V    |

| V <sub>SWING</sub> (DC) | DC differential input voltage               |               | 0.36                         |                         |                      | V    |

| V <sub>X</sub> (AC)     | AC differential input cross point voltage   |               | $(V_{CCIO}/2) - 0.2$         |                         | $(V_{CCIO}/2) + 0.2$ | V    |

| V <sub>SWING</sub> (AC) | AC differential input voltage               |               | 0.7                          |                         |                      | V    |

| V <sub>ISO</sub>        | Input clock signal offset voltage           |               |                              | 0.5 × V <sub>CCIO</sub> |                      | V    |

| $\Delta V_{ISO}$        | Input clock signal offset voltage variation |               |                              | ±200                    |                      | mV   |

| V <sub>OX</sub> (AC)    | AC differential output cross point voltage  |               | (V <sub>CCIO</sub> /2) - 0.2 |                         | $(V_{CCIO}/2) + 0.2$ | V    |

| Table 5-             | -22. 1.2-V HSTL Specificatio | ns                       |                          |                        |                          |      |

|----------------------|------------------------------|--------------------------|--------------------------|------------------------|--------------------------|------|

| Symbol               | Parameter                    | Conditions               | Minimum                  | Typical                | Maximum                  | Unit |

| V <sub>CCIO</sub>    | Output supply voltage        |                          | 1.14                     | 1.20                   | 1.26                     | V    |

| V <sub>REF</sub>     | Reference voltage            |                          | 0.48 × V <sub>CCIO</sub> | $0.50 \times V_{CCIO}$ | 0.52 × V <sub>CCIO</sub> | ٧    |

| V <sub>IH</sub> (DC) | High-level DC input voltage  |                          | V <sub>REF</sub> + 0.08  |                        | V <sub>CCIO</sub> + 0.15 | ٧    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage   |                          | -0.15                    |                        | $V_{REF} - 0.08$         | V    |

| V <sub>IH</sub> (AC) | High-level AC input voltage  |                          | V <sub>REF</sub> + 0.15  |                        | V <sub>CCIO</sub> + 0.24 | ٧    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage   |                          | -0.24                    |                        | $V_{REF} - 0.15$         | V    |

| V <sub>OH</sub>      | High-level output voltage    | I <sub>OH</sub> = 8 mA   | V <sub>REF</sub> + 0.15  |                        | V <sub>CCIO</sub> + 0.15 | V    |

| V <sub>OL</sub>      | Low-level output voltage     | $I_{OH} = -8 \text{ mA}$ | -0.15                    |                        | $V_{REF} - 0.15$         | ٧    |

| Symbol               | Parameter                   | Conditions                    | Minimum                 | Typical | Maximum                | Unit |

|----------------------|-----------------------------|-------------------------------|-------------------------|---------|------------------------|------|

| V <sub>CCIO</sub>    | Output supply voltage       |                               | 1.425                   | 1.500   | 1.575                  | V    |

| V <sub>REF</sub>     | Input reference voltage     |                               | 0.713                   | 0.750   | 0.788                  | V    |

| V <sub>TT</sub>      | Termination voltage         |                               | 0.713                   | 0.750   | 0.788                  | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage |                               | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage  |                               | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage |                               | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage  |                               |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage   | I <sub>OH</sub> = 8 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage    | $I_{OH} = -8 \text{ mA } (1)$ |                         |         | 0.4                    | V    |

#### Note to Table 5-23:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5-2            | 4. 1.5-V HSTL Class II Specif | ications                       |                         |         |                        |      |

|----------------------|-------------------------------|--------------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                     | Minimum                 | Typical | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                                | 1.425                   | 1.500   | 1.575                  | V    |

| $V_{REF}$            | Input reference voltage       |                                | 0.713                   | 0.750   | 0.788                  | ٧    |

| V <sub>TT</sub>      | Termination voltage           |                                | 0.713                   | 0.750   | 0.788                  | ٧    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                                | V <sub>REF</sub> + 0.1  |         |                        | ٧    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                                | -0.3                    |         | V <sub>REF</sub> - 0.1 | ٧    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                                | V <sub>REF</sub> + 0.2  |         |                        | ٧    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                                |                         |         | V <sub>REF</sub> – 0.2 | ٧    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 16 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage      | $I_{OH} = -16 \text{ mA } (1)$ |                         |         | 0.4                    | V    |

#### Note to Table 5-24:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

**Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part 2 of 2)**Notes (1), 2

|                                |                                                                        |                                | Resist            | ance Toleranc     | e    |

|--------------------------------|------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|------|

| Symbol                         | Description                                                            | Conditions                     | Commercial<br>Max | Industrial<br>Max | Unit |

| 50-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (50- $\Omega$ setting)    | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (50-Ω setting)         | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>2.5     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 25-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration (25-Ω setting)            | V <sub>CCIO</sub> = 1.8 V      | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.8 V      | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>1.8     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.8 V      | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.5     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.5 V      | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50-Ω setting)         | V <sub>CCIO</sub> = 1.5 V      | ±36               | ±36               | %    |

| 50-Ω R <sub>T</sub><br>1.5     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.5 V      | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.2     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.2 V      | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2 V      | ±50               | ±50               | %    |

| 50-Ω R <sub>T</sub><br>1.2     | Internal parallel termination with calibration (50- $\Omega$ setting)  | V <sub>CCIO</sub> = 1.2 V      | ±10               | ±15               | %    |

#### Notes for Table 5-30:

<sup>(1)</sup> The resistance tolerances for calibrated SOCT and POCT are for the moment of calibration. If the temperature or voltage changes over time, the tolerance may also change.

<sup>(2)</sup> On-chip parallel termination with calibration is only supported for input pins.

| Table 5-          | 36. Stratix II Performan                                                                                                        | ce Notes | (Part 3 of 6)                 | ) Note        | e (1)                       |                      |                      |                      |      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|

|                   |                                                                                                                                 | Re       | esources Us                   | ed            |                             | Pei                  | formance             | !                    |      |

|                   | Applications                                                                                                                    | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| DSP               | 9 × 9-bit multiplier (5)                                                                                                        | 0        | 0                             | 1             | 430.29                      | 409.16               | 373.13               | 320.10               | MHz  |

| block             | 18 × 18-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18 × 18-bit<br>multiplier (7)                                                                                                   | 0        | 0                             | 1             | 450.04                      | 428.08               | 391.23               | 335.12               | MHz  |

|                   | 36 × 36-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 250.00                      | 238.15               | 217.48               | 186.60               | MHz  |

|                   | $36 \times 36$ -bit multiplier (6)                                                                                              | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

| Larger            | 18-bit, four-tap FIR filter                                                                                                     | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

| Larger<br>designs | 8-bit,16-tap parallel<br>FIR filter                                                                                             | 58       | 0                             | 4             | 259.06                      | 240.61               | 217.15               | 185.01               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, three<br>multipliers and five<br>adders FFT function                                           | 2976     | 22                            | 9             | 398.72                      | 364.03               | 355.23               | 306.37               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, four<br>multipliers and two<br>adders FFT function                                             | 2781     | 22                            | 12            | 398.56                      | 409.16               | 347.22               | 311.13               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function | 984      | 5                             | 3             | 425.17                      | 365.76               | 346.98               | 292.39               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function   | 919      | 5                             | 4             | 427.53                      | 378.78               | 357.14               | 307.59               | MHz  |

| Cumbal                       | Dovomatav                                                                                        |         | peed<br>le <i>(1)</i> |         | peed<br>e <i>(2)</i> |                | peed<br>ide | -5 S <sub> </sub><br>Gra | peed<br>ide | I I m i 4 |

|------------------------------|--------------------------------------------------------------------------------------------------|---------|-----------------------|---------|----------------------|----------------|-------------|--------------------------|-------------|-----------|

| Symbol                       | Parameter                                                                                        | Min (3) | Max                   | Min (3) | Max                  | Min (4)        | Max         | Min (3)                  | Max         | Unit      |

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                     | 50      |                       | 52      |                      | 57<br>57       |             | 67                       |             | ps        |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                       | 180     |                       | 189     |                      | 206<br>206     |             | 241                      |             | ps        |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                       | 0       | 0                     | 0       | 0                    | 0              | 0           | 0                        | 0           | ps        |

| tinreg2PIPE9                 | Input register to DSP block pipeline register in 9 × 9-bit mode                                  | 1,312   | 2,030                 | 1,312   | 2,030                | 1,250<br>1,312 | 2,334       | 1,312                    | 2,720       | ps        |

| t <sub>INREG2PIPE18</sub>    | Input register to DSP<br>block pipeline register<br>in 18 × 18-bit mode                          | 1,302   | 2,010                 | 1,302   | 2,110                | 1,240<br>1,302 | 2,311       | 1,302                    | 2,693       | ps        |

| tinreg2PIPE36                | Input register to DSP<br>block pipeline register<br>in 36 × 36-bit mode                          | 1,302   | 2,010                 | 1,302   | 2,110                | 1,240<br>1,302 | 2,311       | 1,302                    | 2,693       | ps        |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP block pipeline<br>register to output<br>register delay in two-<br>multipliers adder<br>mode  | 924     | 1,450                 | 924     | 1,522                | 880<br>924     | 1,667       | 924                      | 1,943       | ps        |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP block pipeline<br>register to output<br>register delay in four-<br>multipliers adder<br>mode | 1,134   | 1,850                 | 1,134   | 1,942                | 1,080<br>1,134 | 2,127       | 1,134                    | 2,479       | ps        |

| t <sub>PD9</sub>             | Combinational input to output delay for $9 \times 9$                                             | 2,100   | 2,880                 | 2,100   | 3,024                | 2,000<br>2,100 | 3,312       | 2,100                    | 3,859       | ps        |

| t <sub>PD18</sub>            | Combinational input to output delay for 18 × 18                                                  | 2,110   | 2,990                 | 2,110   | 3,139                | 2,010<br>2,110 | 3,438       | 2,110                    | 4,006       | ps        |

| t <sub>PD36</sub>            | Combinational input to output delay for 36 × 36                                                  | 2,939   | 4,450                 | 2,939   | 4,672                | 2,800<br>2,939 | 5,117       | 2,939                    | 5,962       | ps        |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                        | 2,212   |                       | 2,322   |                      | 2,543<br>2,543 |             | 2,964                    |             | ps        |

## **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, intra-clock network skew adder is not specified. Table 5–68 specifies the clock skew between any two clock networks driving registers in the IOE.

| Table 5–68. Clock Network Specifications |                                  |     |     |      |    |  |  |

|------------------------------------------|----------------------------------|-----|-----|------|----|--|--|

| Name                                     | Description                      | Тур | Max | Unit |    |  |  |

| Clock skew adder                         | Inter-clock network, same side   |     |     | ±50  | ps |  |  |

| EP2S15, EP2S30,<br>EP2S60 (1)            | Inter-clock network, entire chip |     |     | ±100 | ps |  |  |

| Clock skew adder<br>EP2S90 (1)           | Inter-clock network, same side   |     |     | ±55  | ps |  |  |

|                                          | Inter-clock network, entire chip |     |     | ±110 | ps |  |  |

| Clock skew adder                         | Inter-clock network, same side   |     |     | ±63  | ps |  |  |

| EP2S130 (1)                              | Inter-clock network, entire chip |     |     | ±125 | ps |  |  |

| Clock skew adder                         | Inter-clock network, same side   |     |     | ±75  | ps |  |  |

| EP2S180 (1)                              | Inter-clock network, entire chip |     |     | ±150 | ps |  |  |

Note to Table 5-68:

<sup>(1)</sup> This is in addition to intra-clock network skew, which is modeled in the Quartus II software.

| Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 5 of 8) |                   |                  |                           |      |                       |                       |                |      |                |

|-----------------------------------------------------------------------|-------------------|------------------|---------------------------|------|-----------------------|-----------------------|----------------|------|----------------|

|                                                                       |                   |                  | Minimu                    | -3   | -3                    | -4                    | -5             | Unit |                |

| I/O Standard                                                          | Drive<br>Strength | Parameter        | Industrial Commercial Gra |      | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade |      | Speed<br>Grade |

| 1.8-V HSTL                                                            | 16 mA             | t <sub>OP</sub>  | 877                       | 919  | 1385                  | 1453                  | 1591           | 1680 | ps             |

| Class II                                                              |                   | t <sub>DIP</sub> | 897                       | 941  | 1451                  | 1523                  | 1667           | 1770 | ps             |

|                                                                       | 18 mA             | t <sub>OP</sub>  | 879                       | 921  | 1394                  | 1462                  | 1602           | 1691 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 899                       | 943  | 1460                  | 1532                  | 1678           | 1781 | ps             |

|                                                                       | 20 mA             | t <sub>OP</sub>  | 879                       | 921  | 1402                  | 1471                  | 1611           | 1700 | ps             |

|                                                                       | (1)               | t <sub>DIP</sub> | 899                       | 943  | 1468                  | 1541                  | 1687           | 1790 | ps             |

| 1.5-V HSTL                                                            | 4 mA              | t <sub>OP</sub>  | 912                       | 956  | 1607                  | 1686                  | 1847           | 1942 | ps             |

| Class I                                                               |                   | t <sub>DIP</sub> | 932                       | 978  | 1673                  | 1756                  | 1923           | 2032 | ps             |

|                                                                       | 6 mA              | t <sub>OP</sub>  | 917                       | 961  | 1588                  | 1666                  | 1825           | 1920 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 937                       | 983  | 1654                  | 1736                  | 1901           | 2010 | ps             |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 899                       | 943  | 1590                  | 1668                  | 1827           | 1922 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 919                       | 965  | 1656                  | 1738                  | 1903           | 2012 | ps             |

|                                                                       | 10 mA             | t <sub>OP</sub>  | 900                       | 943  | 1592                  | 1670                  | 1829           | 1924 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 920                       | 965  | 1658                  | 1740                  | 1905           | 2014 | ps             |

|                                                                       | 12 mA<br>(1)      | t <sub>OP</sub>  | 893                       | 937  | 1590                  | 1668                  | 1827           | 1922 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 913                       | 959  | 1656                  | 1738                  | 1903           | 2012 | ps             |

| 1.5-V HSTL                                                            | 16 mA             | t <sub>OP</sub>  | 881                       | 924  | 1431                  | 1501                  | 1644           | 1734 | ps             |

| Class II                                                              |                   | t <sub>DIP</sub> | 901                       | 946  | 1497                  | 1571                  | 1720           | 1824 | ps             |

|                                                                       | 18 mA             | t <sub>OP</sub>  | 884                       | 927  | 1439                  | 1510                  | 1654           | 1744 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 904                       | 949  | 1505                  | 1580                  | 1730           | 1834 | ps             |

|                                                                       | 20 mA<br>(1)      | t <sub>OP</sub>  | 886                       | 929  | 1450                  | 1521                  | 1666           | 1757 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 906                       | 951  | 1516                  | 1591                  | 1742           | 1847 | ps             |

| 1.2-V HSTL                                                            |                   | t <sub>OP</sub>  | 958                       | 1004 | 1602                  | 1681                  | -              | -    | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 978                       | 1026 | 1668                  | 1751                  | -              | -    | ps             |

| PCI                                                                   |                   | t <sub>OP</sub>  | 1028                      | 1082 | 1956                  | 2051                  | 2244           | 2070 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 1048                      | 1104 | 2022                  | 2121                  | 2320           | 2160 | ps             |

| PCI-X                                                                 |                   | t <sub>OP</sub>  | 1028                      | 1082 | 1956                  | 2051                  | 2244           | 2070 | ps             |

|                                                                       |                   | t <sub>DIP</sub> | 1048                      | 1104 | 2022                  | 2121                  | 2320           | 2160 | ps             |

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 2 of 5) |         |                                                           |      |      |              |      |      |                         |      |      |

|-----------------------------------------------------------------------------|---------|-----------------------------------------------------------|------|------|--------------|------|------|-------------------------|------|------|

|                                                                             |         | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |      |      |              |      |      |                         |      |      |

| I/O Standard Drive<br>Strength                                              |         | Column I/O Pins                                           |      |      | Row I/O Pins |      |      | Dedicated Clock Outputs |      |      |

|                                                                             | ouengui | -3                                                        | -4   | -5   | -3           | -4   | -5   | -3                      | -4   | -5   |

| 1.8-V                                                                       | 2 mA    | 951                                                       | 1421 | 1421 | 951          | 1421 | 1421 | 904                     | 1421 | 1421 |

| LVTTL/LVCMOS                                                                | 4 mA    | 405                                                       | 516  | 516  | 405          | 516  | 516  | 393                     | 516  | 516  |

|                                                                             | 6 mA    | 261                                                       | 325  | 325  | 261          | 325  | 325  | 253                     | 325  | 325  |

|                                                                             | 8 mA    | 223                                                       | 274  | 274  | 223          | 274  | 274  | 224                     | 274  | 274  |

|                                                                             | 10 mA   | 194                                                       | 236  | 236  | -            | -    | 1    | 199                     | 236  | 236  |

|                                                                             | 12 mA   | 174                                                       | 209  | 209  | -            | -    | -    | 180                     | 209  | 209  |

| 1.5-V                                                                       | 2 mA    | 652                                                       | 963  | 963  | 652          | 963  | 963  | 618                     | 963  | 963  |

| LVTTL/LVCMOS                                                                | 4 mA    | 333                                                       | 347  | 347  | 333          | 347  | 347  | 270                     | 347  | 347  |

|                                                                             | 6 mA    | 182                                                       | 247  | 247  | -            | -    | -    | 198                     | 247  | 247  |

|                                                                             | 8 mA    | 135                                                       | 194  | 194  | -            | -    | -    | 155                     | 194  | 194  |

| SSTL-2 Class I                                                              | 8 mA    | 364                                                       | 680  | 680  | 364          | 680  | 680  | 350                     | 680  | 680  |

|                                                                             | 12 mA   | 163                                                       | 207  | 207  | 163          | 207  | 207  | 188                     | 207  | 207  |

| SSTL-2 Class II                                                             | 16 mA   | 118                                                       | 147  | 147  | 118          | 147  | 147  | 94                      | 147  | 147  |

|                                                                             | 20 mA   | 99                                                        | 122  | 122  | -            | -    | -    | 87                      | 122  | 122  |

|                                                                             | 24 mA   | 91                                                        | 116  | 116  | -            | -    | -    | 85                      | 116  | 116  |

| SSTL-18 Class I                                                             | 4 mA    | 458                                                       | 570  | 570  | 458          | 570  | 570  | 505                     | 570  | 570  |

|                                                                             | 6 mA    | 305                                                       | 380  | 380  | 305          | 380  | 380  | 336                     | 380  | 380  |

|                                                                             | 8 mA    | 225                                                       | 282  | 282  | 225          | 282  | 282  | 248                     | 282  | 282  |

|                                                                             | 10 mA   | 167                                                       | 220  | 220  | 167          | 220  | 220  | 190                     | 220  | 220  |

|                                                                             | 12 mA   | 129                                                       | 175  | 175  | -            | -    | -    | 148                     | 175  | 175  |

| SSTL-18 Class II                                                            | 8 mA    | 173                                                       | 206  | 206  | -            | -    | -    | 155                     | 206  | 206  |

|                                                                             | 16 mA   | 150                                                       | 160  | 160  | -            | -    | -    | 140                     | 160  | 160  |

|                                                                             | 18 mA   | 120                                                       | 130  | 130  | -            | -    | -    | 110                     | 130  | 130  |

|                                                                             | 20 mA   | 109                                                       | 127  | 127  | -            | -    | -    | 94                      | 127  | 127  |

| SSTL-2 Class I                                                              | 8 mA    | 364                                                       | 680  | 680  | 364          | 680  | 680  | 350                     | 680  | 680  |

|                                                                             | 12 mA   | 163                                                       | 207  | 207  | 163          | 207  | 207  | 188                     | 207  | 207  |

| SSTL-2 Class II                                                             | 16 mA   | 118                                                       | 147  | 147  | 118          | 147  | 147  | 94                      | 147  | 147  |

|                                                                             | 20 mA   | 99                                                        | 122  | 122  | -            | -    | -    | 87                      | 122  | 122  |

|                                                                             | 24 mA   | 91                                                        | 116  | 116  | -            | -    | -    | 85                      | 116  | 116  |

Table 5–102 shows the JTAG timing parameters and values for Stratix II devices.

| Table 5–102. Stratix II JTAG Timing Parameters & Values |                                          |     |        |      |  |  |

|---------------------------------------------------------|------------------------------------------|-----|--------|------|--|--|

| Symbol                                                  | Parameter                                | Min | Max    | Unit |  |  |

| $t_{JCP}$                                               | TCK clock period                         | 30  |        | ns   |  |  |

| t <sub>JCH</sub>                                        | TCK clock high time                      | 13  |        | ns   |  |  |

| t <sub>JCL</sub>                                        | TCK clock low time                       | 13  |        | ns   |  |  |

| t <sub>JPSU</sub>                                       | JTAG port setup time                     | 3   |        | ns   |  |  |

| t <sub>JPH</sub>                                        | JTAG port hold time                      | 5   |        | ns   |  |  |

| t <sub>JPCO</sub>                                       | JTAG port clock to output                |     | 11 (1) | ns   |  |  |

| t <sub>JPZX</sub>                                       | JTAG port high impedance to valid output |     | 14 (1) | ns   |  |  |

| $t_{JPXZ}$                                              | JTAG port valid output to high impedance |     | 14 (1) | ns   |  |  |

Note to Table 5-102:

(1) A 1 ns adder is required for each  $V_{\rm CCIO}$  voltage step down from 3.3 V. For example,  $t_{\rm JPCO}$  = 12 ns if  $V_{\rm CCIO}$  of the TDO I/O bank = 2.5 V, or 13 ns if it equals 1.8 V.

## Document Revision History

Table 5–103 shows the revision history for this chapter.

| Table 5–103. Document Revision History (Part 1 of 3) |                                                                                                                                                                                      |                                                                                                                 |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Date and<br>Document<br>Version                      | Changes Made                                                                                                                                                                         | Summary of Changes                                                                                              |  |  |  |

| April 2011, v4.5                                     | Updated Table 5–3.                                                                                                                                                                   | Added operating junction temperature for military use.                                                          |  |  |  |

| July 2009, v4.4                                      | Updated Table 5–92.                                                                                                                                                                  | Updated the spread spectrum modulation frequency (f <sub>SS</sub> ) from (100 kHz–500 kHz) to (30 kHz–150 kHz). |  |  |  |

| May 2007, v4.3                                       | <ul> <li>Updated R<sub>CONF</sub> in Table 5–4.</li> <li>Updated f<sub>IN</sub> (min) in Table 5–92.</li> <li>Updated f<sub>IN</sub> and f<sub>INPFD</sub> in Table 5–93.</li> </ul> | _                                                                                                               |  |  |  |

|                                                      | Moved the Document Revision History section to the end of the chapter.                                                                                                               | _                                                                                                               |  |  |  |