Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | •                                                                        |

| RAM Size                   | 38 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                   |

| Supplier Device Package    | 8-MSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f510-e-ms |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device    | Program Memory | Data Memory  | I/O | Timers |  |

|-----------|----------------|--------------|-----|--------|--|

| Device    | Flash (words)  | SRAM (bytes) | 1/0 | 8-bit  |  |

| PIC16F506 | 1024           | 67           | 12  | 1      |  |

| PIC12F510 | 1024           | 38           | 6   | 1      |  |

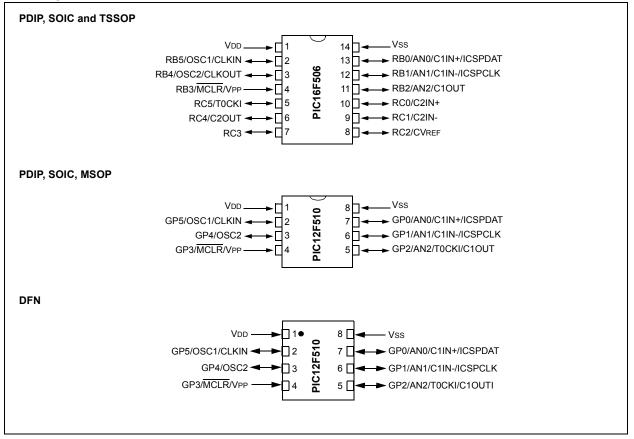

# **Pin Diagrams**

| Name                  | Function | Input Type | Output<br>Type | Description                                                                                                                |

|-----------------------|----------|------------|----------------|----------------------------------------------------------------------------------------------------------------------------|

| RB0/AN0/C1IN+/ICSPDAT | RB0      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | AN0      | AN         | —              | ADC channel input.                                                                                                         |

|                       | C1IN+    | AN         | —              | Comparator 1 input.                                                                                                        |

|                       | ICSPDAT  | ST         | CMOS           | In-Circuit Serial Programming data pin.                                                                                    |

| RB1/AN1/C1IN-/ICSPCLK | RB1      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | AN1      | AN         |                | ADC channel input.                                                                                                         |

|                       | C1IN-    | AN         |                | Comparator 1 input.                                                                                                        |

|                       | ICSPCLK  | ST         | _              | In-Circuit Serial Programming clock pin.                                                                                   |

| RB2/AN2/C1OUT         | RB2      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | AN2      | AN         |                | ADC channel input.                                                                                                         |

|                       | C10UT    | _          | CMOS           | Comparator 1 output.                                                                                                       |

| RB3/MCLR/Vpp          | RB3      | TTL        | _              | Standard TTL input. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.             |

|                       | MCLR     | ST         | —              | MCLR input – weak pull-up always enabled in this mode.                                                                     |

|                       | Vpp      | HV         |                | Programming voltage input.                                                                                                 |

| RB4/OSC2/CLKOUT       | RB4      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | OSC2     | _          | XTAL           | XTAL oscillator output pin.                                                                                                |

|                       | CLKOUT   | _          | CMOS           | EXTRC/INTOSC CLKOUT pin (Fosc/4).                                                                                          |

| RB5/OSC1/CLKIN        | RB5      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | OSC1     | XTAL       | _              | XTAL oscillator input pin.                                                                                                 |

|                       | CLKIN    | ST         | _              | EXTRC/EC Schmitt Trigger input.                                                                                            |

| RC0/C2IN+             | RC0      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2IN+    | AN         | _              | Comparator 2 input.                                                                                                        |

| RC1/C2IN-             | RC1      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2IN-    | AN         | _              | Comparator 2 input.                                                                                                        |

| RC2/CVREF             | RC2      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | CVREF    |            | AN             | Programmable Voltage Reference output.                                                                                     |

| RC3                   | RC3      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

| RC4/C2OUT             | RC4      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2OUT    |            | CMOS           | Comparator 2 output.                                                                                                       |

| RC5/T0CKI             | RC5      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | T0CKI    | ST         | _              | Timer0 clock input.                                                                                                        |

| Vdd                   | Vdd      | Р          |                | Positive supply for logic and I/O pins.                                                                                    |

| Vss                   | Vss      | Р          | _              | Ground reference for logic and I/O pins.                                                                                   |

TABLE 3-3: PIN DESCRIPTIONS – PIC16F506

**Legend:** I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input, AN = Analog Voltage, HV = High Voltage

| W-1           | W-1                                                             | W-1                                                                                                                                                                       | W-1                                                            | W-1               | W-1             | W-1             | W-1   |

|---------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------|-----------------|-----------------|-------|

| RBWU          | RBPU                                                            | TOCS                                                                                                                                                                      | TOSE                                                           | PSA               | PS2             | PS1             | PS0   |

| bit 7         |                                                                 |                                                                                                                                                                           |                                                                |                   |                 |                 | bit ( |

|               |                                                                 |                                                                                                                                                                           |                                                                |                   |                 |                 |       |

| Legend:       |                                                                 |                                                                                                                                                                           |                                                                |                   |                 |                 |       |

| R = Readabl   | le bit                                                          | W = Writable                                                                                                                                                              | bit                                                            | U = Unimpler      | nented bit, rea | d as '0'        |       |

| -n = Value at | t POR                                                           | '1' = Bit is set                                                                                                                                                          |                                                                | '0' = Bit is cle  | ared            | x = Bit is unkr | nown  |

| bit 7         | <b>RBWU:</b> Enable V<br>1 = Disabled<br>0 = Enabled            | Vake-up On Pin (                                                                                                                                                          | Change bit (RB0                                                | ), RB1, RB3, RB4) |                 |                 |       |

| bit 6         | <b>RBPU:</b> Enable W<br>1 = Disabled<br>0 = Enabled            | /eak Pull-Ups bit                                                                                                                                                         | (RB0, RB1, RB                                                  | 3, RB4)           |                 |                 |       |

| bit 5         | <b>TOCS:</b> Timer0 CI<br>1 = Transition o<br>0 = Internal inst |                                                                                                                                                                           |                                                                |                   |                 |                 |       |

| bit 4         | <b>TOSE:</b> Timer0 Sc<br>1 = Increment c<br>0 = Increment c    | Ũ                                                                                                                                                                         | nsition on T0CK                                                | •                 |                 |                 |       |

| bit 3         | PSA: Prescaler A<br>1 = Prescaler a<br>0 = Prescaler a          | ssigned to the W                                                                                                                                                          |                                                                |                   |                 |                 |       |

| bit 2-0       | PS<2:0>: Presca                                                 | ler Rate Select b                                                                                                                                                         | its                                                            |                   |                 |                 |       |

|               | Bit V                                                           | alue Timer0                                                                                                                                                               | Rate WDT R                                                     | ate               |                 |                 |       |

|               | 0<br>0<br>0<br>1<br>1<br>1<br>1                                 | D0         1:2           D1         1:4           L0         1:8           L1         1:13           D01         1:30           D11         1:6           L1         1:12 | 1 : 2<br>1 : 4<br>6 1 : 8<br>2 1 : 16<br>4 1 : 32<br>28 1 : 64 |                   |                 |                 |       |

## REGISTER 4-4: OPTION\_REG: OPTION REGISTER (PIC16F506)

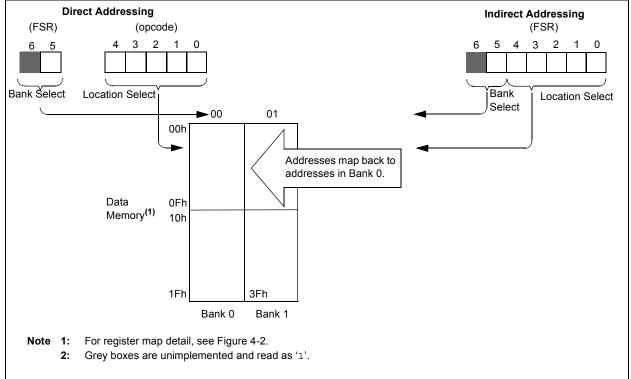

# 4.8 Indirect Data Addressing: INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### 4.8.1 INDIRECT ADDRESSING EXAMPLE

- · Register file 07 contains the value 10h

- · Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-1.

# EXAMPLE 4-1:

#### -1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT   | MOVLW<br>MOVWF<br>CLRF<br>INCF<br>BTFSC<br>GOTO | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear INDF register<br>;inc pointer<br>;all done?<br>;NO, clear next |

|--------|-------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|

| CONTIN | UE                                              |                                               |                                                                                                         |

|        | :                                               |                                               | ;YES, continue                                                                                          |

|        | :                                               |                                               |                                                                                                         |

|        |                                                 |                                               |                                                                                                         |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16F506** – Uses FSR<6:5>. Selects from Bank 0 to Bank 3. FSR<7> is unimplemented, read as '1'.

**PIC12F510** – Uses FSR<5>. Selects from Bank 0 to Bank 1. FSR<7:6> are unimplemented, read as '11'.

# PIC12F510/16F506

0

Q

Q

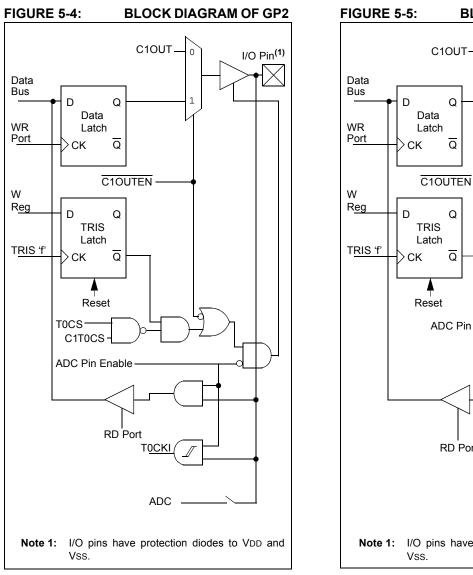

**BLOCK DIAGRAM OF RB2**

I/O Pin<sup>(1)</sup>

$\mathbf{X}$

Q Q ADC Pin Enable RD Port ADC \_ Note 1: I/O pins have protection diodes to VDD and

# TABLE 5-1: SUMMARY OF PORT REGISTERS

| Address | Name                    | Bit 7 | Bit 6 | Bit 5     | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|-------|-------|-----------|------------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | TRISGPIO <sup>(1)</sup> |       |       | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | TRISB <sup>(2)</sup>    | _     | —     | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | TRISC <sup>(2)</sup>    | _     | _     | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | OPTION <sup>(1)</sup>   | GPWU  | GPPU  | TOCS      | TOSE       | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup>   | RBWU  | RBPU  | TOCS      | TOSE       | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| 03h     | STATUS <sup>(1)</sup>   | GPWUF | CWUF  | PA0       | TO         | PD    | Z     | DC    | С     | 0001 1xxx                     | qq0q quuu <b>(3)</b>            |

| 03h     | STATUS <sup>(2)</sup>   | RBWUF | CWUF  | PA0       | TO         | PD    | Z     | DC    | С     | 0001 1xxx                     | qq0q quuu <sup>(3)</sup>        |

| 06h     | GPIO <sup>(1)</sup>     | _     | _     | GP5       | GP4        | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                         |

| 06h     | PORTB <sup>(2)</sup>    | —     | —     | RB5       | RB4        | RB3   | RB2   | RB1   | RB0   | xx xxxx                       | uu uuuu                         |

| 07h     | PORTC <sup>(2)</sup>    | _     |       | RC5       | RC4        | RC3   | RC2   | RC1   | RC0   | xx xxxx                       | uu uuuu                         |

$\label{eq:logend: Legend: Legend: -= unimplemented read as `0', x = unknown, u = unchanged, q = depends on condition.$

Note 1: PIC12F510 only.

2: PIC16F506 only.

3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

# TABLE 5-2: I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC16F506)

| Priority | RB0       | RB1       | RB2   | RB3        | RB4         | RB5        |

|----------|-----------|-----------|-------|------------|-------------|------------|

| 1        | AN0/C1IN+ | AN1/C1IN- | AN2   | Input/MCLR | OSC2/CLKOUT | OSC1/CLKIN |

| 2        | TRISB     | TRISB     | C10UT | —          | TRISB       | TRISB      |

| 3        | _         |           | TRISB | _          | _           |            |

# TABLE 5-3: I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC16F506)

| Priority | RC0   | RC1   | RC2   | RC3   | RC4   | RC5   |

|----------|-------|-------|-------|-------|-------|-------|

| 1        | C2IN+ | C2IN- | CVREF | TRISC | C2OUT | TOCKI |

| 2        | TRISC | TRISC | TRISC |       | TRISC | TRISC |

# TABLE 5-4:I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC12F510)

| Priority | GP0       | GP1       | GP2    | GP3        | GP4    | GP5        |

|----------|-----------|-----------|--------|------------|--------|------------|

| 1        | AN0/C1IN+ | AN1/C1IN- | AN2    | Input/MCLR | OSC2   | OSC1/CLKIN |

| 2        | TRISIO    | TRISIO    | C10UT  | _          | TRISIO | TRISIO     |

| 3        | _         | _         | TOCKI  | _          | _      | _          |

| 4        |           | —         | TRISIO | —          | _      | _          |

# PIC12F510/16F506

#### 9.1.6 ANALOG CONVERSION RESULT REGISTER

The ADRES register contains the results of the last conversion. These results are present during the sampling period of the next analog conversion process. After the sampling period is over, ADRES is cleared (= 0). A 'leading one' is then right shifted into the ADRES to serve as an internal conversion complete bit. As each bit weight, starting with the MSB, is converted, the leading one is shifted right and the converted bit is stuffed into ADRES. After a total of 9 right

shifts of the 'leading one' have taken place, the conversion is complete; the 'leading one' has been shifted out and the GO/DONE bit is cleared.

If the GO/DONE bit is cleared in software during a conversion, the conversion stops. The data in ADRES is the partial conversion result. This data is valid for the bit weights that have been converted. The position of the 'leading one' determines the number of bits that have been converted. The bits that were not converted before the GO/DONE was cleared are unrecoverable.

## REGISTER 9-1: ADCON0: A/D CONTROL REGISTER (PIC12F510)

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|---------|-------|

| ANS1  | ANS0  | ADCS1 | ADCS0 | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |       |       |       |       |       |         | bit 0 |

| Legend:            |                                                    |                                                                                                                                                                  |                                                                                                          |                                                                                                                       |

|--------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| R = Read           | able bit                                           | W = Writable bit                                                                                                                                                 | U = Unimplemented bit                                                                                    | , read as '0'                                                                                                         |

| -n = Value         | e at POR                                           | '1' = Bit is set                                                                                                                                                 | '0' = Bit is cleared                                                                                     | x = Bit is unknown                                                                                                    |

| bit 7-6            | 00 = No<br>01 = AN<br>10 = AN                      | <b>0&gt;:</b> ADC Analog Input Pin S<br>pins configured for analog in<br>2 configured as an analog ir<br>2 and AN0 configured as an<br>2, AN1 and AN0 configured | nput<br>iput<br>alog inputs                                                                              |                                                                                                                       |

| bit 5-4            | ADCS<<br>00 = FO<br>01 = FO<br>10 = FO<br>11 = IN  | sc/8<br>sc/4                                                                                                                                                     | s Select bits                                                                                            |                                                                                                                       |

| bit 3-2            | 00 = Ch<br>01 = Ch<br>10 = Ch                      | <b>0&gt;:</b> ADC Channel Select bits<br>annel AN0<br>annel AN1<br>annel AN2<br>V absolute voltage reference                                                     |                                                                                                          |                                                                                                                       |

| bit 1              | 1 = AD0<br>auto<br>0 = AD0                         | omatically cleared by hardwa                                                                                                                                     | Setting this bit starts an Al<br>are when the ADC is done con<br>in progress. Manually clearin           | DC conversion cycle. This bit<br>verting.<br>Ig this bit while a conversion is                                        |

| bit 0              | 1 = AD0                                            | ADC Enable bit<br>C module is operating<br>C module is shut-off and con                                                                                          | sumes no power                                                                                           |                                                                                                                       |

| Note 1:<br>2:      | less of the pir<br>input to the co<br>that the ADC | n function previously defined omparator and the ADC will b                                                                                                       | . The only exception to this is<br>be active at the same time. It is<br>nput does not affect their appli | forced into Analog mode, regard-<br>the comparator, where the analog<br>the users responsibility to ensur-<br>cation. |

| 3:                 |                                                    | s default to 11 after any Res                                                                                                                                    |                                                                                                          |                                                                                                                       |

| <u></u> <i>A</i> . |                                                    | hit is clear the GO/DONE hit                                                                                                                                     | cannot ha sat                                                                                            |                                                                                                                       |

4: If the ADON bit is clear, the GO/DONE bit cannot be set.

# 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC12F510/16F506 devices can be operated in up to six different oscillator modes. The user can program up to three Configuration bits (FOSC<1:0> [PIC12F510], FOSC<2:0> [PIC16F506]). To select one of these modes:

| •LP:     | Low-Power Crystal                                   |

|----------|-----------------------------------------------------|

| •XT:     | Crystal/Resonator                                   |

| •HS:     | High-Speed Crystal/Resonator<br>(PIC16F506 only)    |

| •INTOSC: | Internal 4/8 MHz Oscillator                         |

| •EXTRC:  | External Resistor/Capacitor                         |

| •EC:     | External High-Speed Clock Input<br>(PIC16F506 only) |

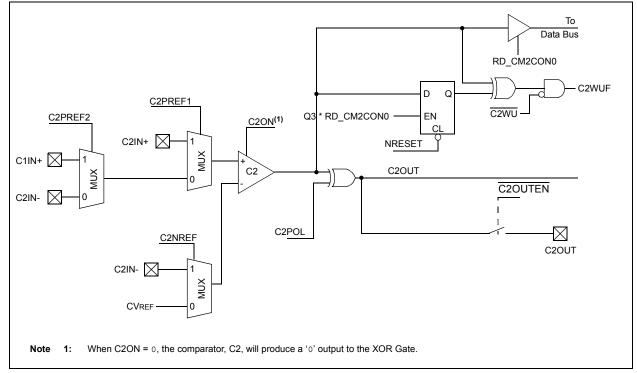

#### 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

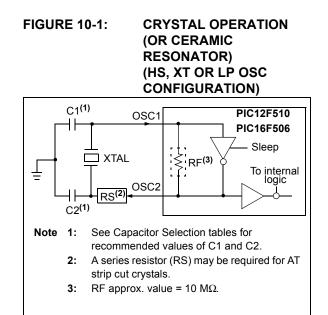

In HS (PIC16F506), XT or LP modes, a crystal or ceramic resonator is connected to the (GP5/RB5)/ OSC1/(CLKIN) and (GP4/RB4)/OSC2/(CLKOUT) pins to establish oscillation (Figure 10-1). The PIC12F510/ 16F506 oscillator designs require the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS (PIC16F506), XT or LP modes, the device can have an external clock source drive the (GP5/ RB5)/OSC1/CLKIN pin (Figure 10-2). When the part is used in this fashion, the output drive levels on the OSC2 pin are very weak. This pin should be left open and unloaded. Also, when using this mode, the external clock should observe the frequency limits for the clock mode chosen (HS, XT or LP).

- Note 1: This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

- The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/or the Oscillator mode may be required.

#### FIGURE 10-2:

EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 10-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS – PIC12F510/16F506<sup>(1)</sup>

| Osc.<br>Type      | Resonator<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|-------------------|--------------------|------------------|------------------|

| XT                | 4.0 MHz            | 30 pF            | 30 pF            |

| HS <sup>(2)</sup> | 16 MHz             | 10-47 pF         | 10-47 pF         |

- Note 1: These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

- 2: PIC16F506 only.

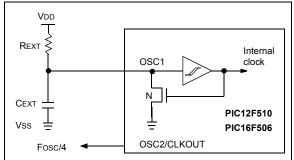

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no capacitance or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

**Section 13.0 "Electrical Characteristics"**, shows RC frequency variation from part-to-part due to normal process variation. The variation is larger for larger values of R (since leakage current variation will affect RC frequency more for large R) and for smaller values of C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications section for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

FIGURE 10-5: EXTERNAL RC OSCILLATOR MODE

#### 10.2.5 INTERNAL 4/8 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4/8 MHz (nominal) system clock (see **Section 13.0 "Electrical Characteristics"** for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal RC oscillator. This location is always uncode protected, regardless of the code-protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

**Note:** Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part so it can be reprogrammed correctly later.

For the PIC12F510/16F506 devices, only bits <7:1> of OSCCAL are used for calibration. See Register 4-5 for more information.

**Note:** The 0 bit of OSCCAL is unimplemented and should be written as '0' when modifying OSCCAL for compatibility with future devices.

# PIC12F510/16F506

## 10.12 In-Circuit Serial Programming™ (ICSP™)

The PIC12F510/16F506 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the GP1/RB1 and GP0/RB0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1/RB1 becomes the programming clock and GP0/RB0 becomes the programming data. Both GP1/RB1 and GP0/RB0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is supplied to the device. Depending on the command and if the command was a Load or a Read, 14 bits of program data are then supplied to or from the device. For complete details of serial programming, please refer to the PIC12F510/16F506 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 10-15.

#### FIGURE 10-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

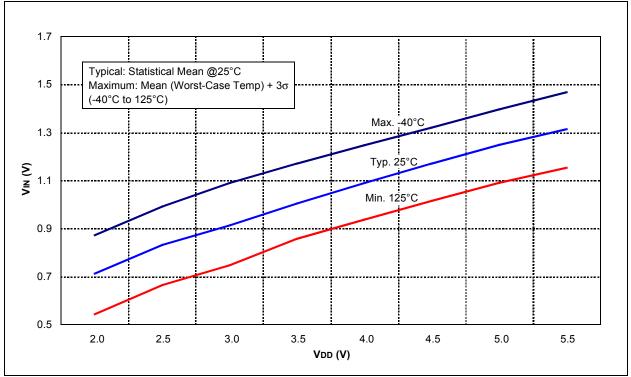

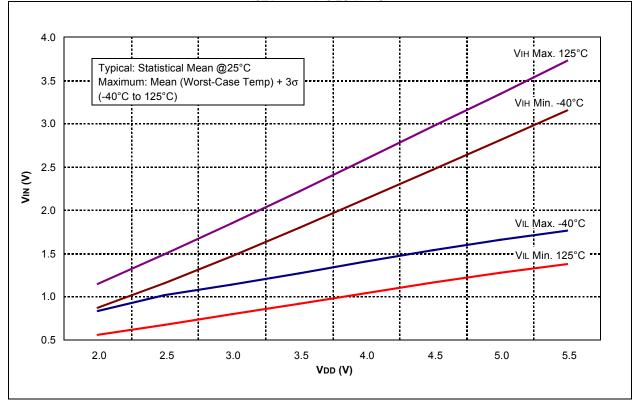

## 13.1 DC Characteristics: PIC12F510/16F506 (Industrial)

| DC Characteristics |              |                                                                 | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) |                    |             |          |                                                                                                     |

|--------------------|--------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|----------|-----------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym          | Characteristic                                                  | Min                                                                                                                                    | Typ <sup>(1)</sup> | Max         | Units    | Conditions                                                                                          |

| D001               | Vdd          | Supply Voltage                                                  | 2.0                                                                                                                                    |                    | 5.5         | V        | See Figure 14-1                                                                                     |

| D002               | Vdr          | RAM Data Retention Voltage <sup>(2)</sup>                       | _                                                                                                                                      | 1.5*               |             | V        | Device in Sleep mode                                                                                |

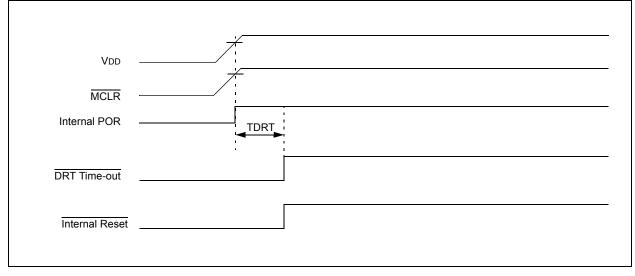

| D003               | VPOR         | VDD Start Voltage to ensure<br>Power-on Reset                   | —                                                                                                                                      | Vss                |             | V        | See Section 10.4 "Power-on<br>Reset (POR)" for details                                              |

| D004               | SVDD         | VDD Rise Rate to ensure<br>Power-on Reset                       | 0.05*                                                                                                                                  | —                  |             | V/ms     | See Section 10.4 "Power-on<br>Reset (POR)" for details                                              |

| D010               | IDD          | Supply Current <sup>(3,4)</sup>                                 | _                                                                                                                                      | 175<br>0.625       | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, VDD = 2.0V<br>Fosc = 4 MHz, VDD = 5.0V                                                |

|                    |              |                                                                 | _                                                                                                                                      | 250<br>1.0         | 450<br>1.5  | μA<br>mA | Fosc = 8 MHz, Vdd = 2.0V<br>Fosc = 8 MHz, Vdd = 5.0V                                                |

|                    |              |                                                                 |                                                                                                                                        | 1.4                | 2.0         | mA       | Fosc = 20 MHz, VDD = 5.0V                                                                           |

|                    |              |                                                                 | _                                                                                                                                      | 11<br>38           | 15<br>52    | μΑ<br>μΑ | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                                              |

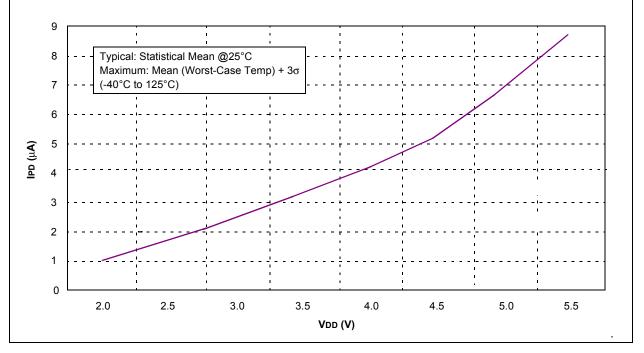

| D020               | IPD          | Power-down Current <sup>(5)</sup>                               | _                                                                                                                                      | 0.1<br>0.35        | 1.2<br>2.4  | μA<br>μA | VDD = 2.0V<br>VDD = 5.0V                                                                            |

| D022               | Iwdt         | WDT Current <sup>(5)</sup>                                      | _                                                                                                                                      | 1.0<br>7.0         | 3.0<br>16.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                                            |

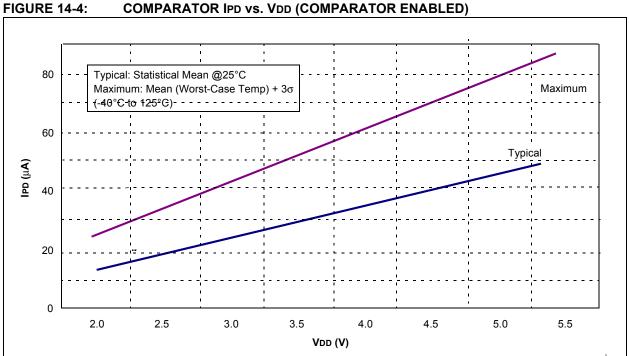

| D023               | ICMP         | Comparator Current <sup>(5)</sup>                               | _                                                                                                                                      | 15<br>55           | 22<br>67    | μΑ<br>μΑ | VDD = 2.0V (per comparator)<br>VDD = 5.0V (per comparator)                                          |

| D022               | ICVREF       | CVREF Current <sup>(5)</sup>                                    | _                                                                                                                                      | 30<br>75           | 60<br>125   | μΑ<br>μΑ | VDD = 2.0V (high range)<br>VDD = 5.0V (high range)                                                  |

| D023               | IFVR         | Internal 0.6V Fixed Voltage<br>Reference Current <sup>(5)</sup> |                                                                                                                                        | 85<br>175          | 120<br>205  | μΑ<br>μΑ | $V_{DD}$ = 2.0V (0.6V reference and<br>1 comparator enabled)<br>$V_{DD}$ = 5.0V (0.6V reference and |

|                    |              |                                                                 |                                                                                                                                        |                    |             |          | 1 comparator enabled)                                                                               |

| D024               | $\Delta$ IAD | A/D Conversion Current <sup>(5)</sup>                           | —                                                                                                                                      | 120                | 150         | μA       | 2.0V                                                                                                |

|                    |              |                                                                 |                                                                                                                                        | 200                | 250         | μA       | 5.0V                                                                                                |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

**3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

4: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

**5:** For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

**6:** Does not include current through REXT. The current through the resistor can be estimated by the formula: I = VDD/2REXT (mA) with REXT in kΩ.

# 15.0 PACKAGING

# 15.1 Package Marking Information

8-Lead PDIP

14-Lead PDIP

8-Lead SOIC (3.90 mm)

8-Lead 2x3 DFN\*

Example

Example

Example

| BE0 |

|-----|

| 610 |

| 17  |

|     |

#### TABLE 15-1: 8-LEAD 2X3 DFN (MC) TOP MARKING

| Part Number       | Marking |

|-------------------|---------|

| PIC12F510(T)-I/MC | BS0     |

| PIC12F510-E/MC    | BT0     |

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                          | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | In the event the full Microchip part number cannot be marked on one line, it the carried over to the next line, thus limiting the number of availal characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |

\* Standard PIC<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PIC device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

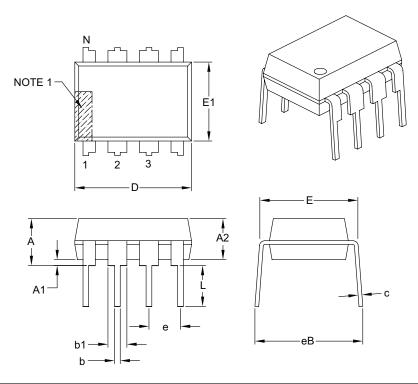

# 8-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      | INCHES   |      |

|----------------------------|----------|------|----------|------|

| Dimensio                   | n Limits | MIN  | NOM      | MAX  |

| Number of Pins             | N        |      | 8        |      |

| Pitch                      | е        |      | .100 BSC |      |

| Top to Seating Plane       | A        | -    | -        | .210 |

| Molded Package Thickness   | A2       | .115 | .130     | .195 |

| Base to Seating Plane      | A1       | .015 | -        | -    |

| Shoulder to Shoulder Width | E        | .290 | .310     | .325 |

| Molded Package Width       | E1       | .240 | .250     | .280 |

| Overall Length             | D        | .348 | .365     | .400 |

| Tip to Seating Plane       | L        | .115 | .130     | .150 |

| Lead Thickness             | с        | .008 | .010     | .015 |

| Upper Lead Width           | b1       | .040 | .060     | .070 |

| Lower Lead Width           | b        | .014 | .018     | .022 |

| Overall Row Spacing §      | eB       | _    | -        | .430 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

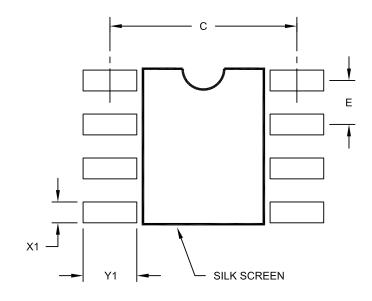

# 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

| Units                   |    | MILLIMETERS |          |      |

|-------------------------|----|-------------|----------|------|

| Dimension Limits        |    | MIN         | NOM      | MAX  |

| Contact Pitch           | Е  |             | 1.27 BSC |      |

| Contact Pad Spacing     | С  |             | 5.40     |      |

| Contact Pad Width (X8)  | X1 |             |          | 0.60 |

| Contact Pad Length (X8) | Y1 |             |          | 1.55 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

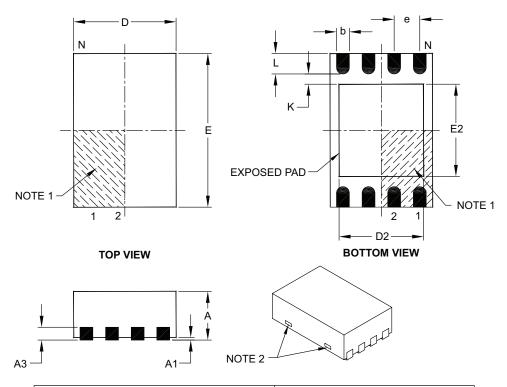

# 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |      |      |

|------------------------|------------------|-------------|------|------|

|                        | Dimension Limits | MIN         | NOM  | MAX  |

| Number of Pins         | N                | 8           |      |      |

| Pitch                  | е                | 0.50 BSC    |      |      |

| Overall Height         | A                | 0.80        | 0.90 | 1.00 |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |      |      |

| Overall Length         | D                | 2.00 BSC    |      |      |

| Overall Width          | E                | 3.00 BSC    |      |      |

| Exposed Pad Length     | D2               | 1.30        | -    | 1.75 |

| Exposed Pad Width      | E2               | 1.50        | -    | 1.90 |

| Contact Width          | b                | 0.18        | 0.25 | 0.30 |

| Contact Length         | L                | 0.30        | 0.40 | 0.50 |

| Contact-to-Exposed Pad | K                | 0.20        | -    | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-123B

# **Т**

| Timer0                                         |        |

|------------------------------------------------|--------|

| Timer0                                         |        |

| Timer0 (TMR0) Module                           | 39     |

| TMR0 with External Clock                       |        |

| Timing Diagrams and Specifications             | 91     |

| Timing Parameter Symbology and Load Conditions | 91     |

| TRIS Registers                                 | 27     |

| w                                              |        |

| Wake-up from Sleep                             | 69     |

| Watchdog Timer (WDT)                           | 55, 66 |

| Period                                         |        |

| Programming Considerations                     |        |

| WWW Address                                    | 108    |

| WWW, On-Line Support                           | 3      |

| Z                                              |        |

|                                                |        |