Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 38 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                   |

| Supplier Device Package    | 8-MSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f510-i-ms |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Міскоснір PIC12F510/16F506

# 8/14-Pin, 8-Bit Flash Microcontroller

# **Devices Included In This Data Sheet:**

- PIC16F506

- PIC12F510

# High-Performance RISC CPU:

- · Only 33 Single-Word Instructions to Learn

- All Single-Cycle Instructions except for Program Branches, which are Two-Cycle

- 12-Bit Wide Instructions

- Two-Level Deep Hardware Stack

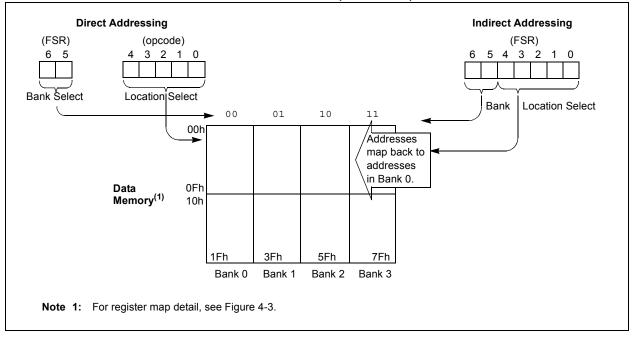

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- · 8-Bit Wide Data Path

- 10 Special Function Hardware Registers (PIC12F510)

- 13 Special Function Hardware Registers (PIC16F506)

- · Operating Speed:

- DC 8 MHz Crystal Oscillator (PIC12F510)

- DC 500 ns instruction cycle (PIC12F510)

- DC 20 MHz Crystal Oscillator (PIC16F506)

- DC 200 ns instruction cycle (PIC16F506)

#### **Special Microcontroller Features:**

- 4 or 8 MHz Selectable Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debugging (ICD) Support

- Power-on Reset (POR)

- Device Reset Timer (DRT):

- Short DRT (1.125 ms, typical) for INTOSC, EXTRC and EC

- DRT (18 ms, typical) for HS, XT and LP

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

- · Selectable Internal Weak Pull-Ups on I/O Pins

- · Power-Saving Sleep mode

- Wake-up from Sleep on Pin Change

- · Wake-up from Sleep on Comparator Change

- · Selectable Oscillator Options:

- INTOSC: 4/8 MHz precision Internal oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- LP: Power-saving, low-frequency crystal

- HS: High-speed crystal/resonator (PIC16F506 only)

- EC: High-speed external clock input (PIC16F506 only)

- Analog-to-Digital (A/D) Converter:

- 8-bit resolution

- 4-input channels (1 channel is dedicated to conversion of the internal 0.6V absolute voltage reference)

- High Current Sink/Source for Direct LED Drive

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

#### Low-Power Features/CMOS Technology:

- Operating Current:

- < 175 μA @ 2V, 4 MHz, typical

- Standby Current:

- 100 nA @ 2V, typical

- · Low-Power, High-Speed Flash Technology:

- 100,000 cycle Flash endurance

- > 40-year retention

- Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V

- Wide Temperature Range:

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

# Peripheral Features (PIC12F510):

- 6 I/O Pins:

- 5 I/O pins with individual direction control

- 1 input only pin

- 1 Analog Comparator with Absolute Reference

#### Peripheral Features (PIC16F506):

- 12 I/O Pins:

- 11 I/O pins with individual direction control

- 1 input only pin

- 2 Analog Comparators with Absolute Reference and Programmable Reference

| Device    | Program Memory | Data Memory  | I/O | Timers |  |

|-----------|----------------|--------------|-----|--------|--|

| Device    | Flash (words)  | SRAM (bytes) | 1/0 | 8-bit  |  |

| PIC16F506 | 1024           | 67           | 12  | 1      |  |

| PIC12F510 | 1024           | 38           | 6   | 1      |  |

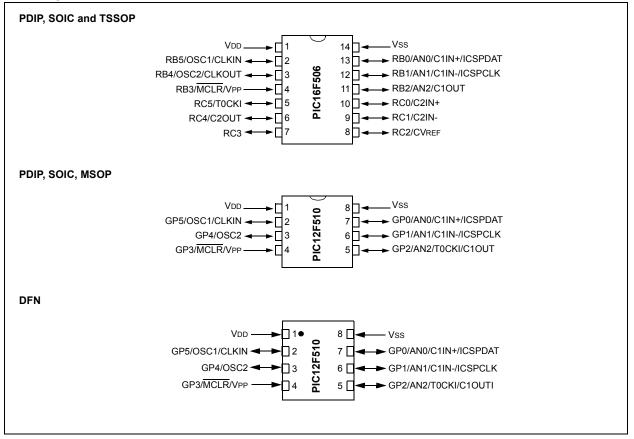

# **Pin Diagrams**

#### Table of Contents

| 1.0   | General Description                                  | 5     |  |  |  |  |

|-------|------------------------------------------------------|-------|--|--|--|--|

| 2.0   | PIC12F510/16F506 Device Varieties                    | 7     |  |  |  |  |

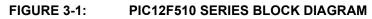

| 3.0   | Architectural Overview                               | 9     |  |  |  |  |

| 4.0   | Memory Organization                                  | 15    |  |  |  |  |

| 5.0   | I/O Port                                             | 27    |  |  |  |  |

| 6.0   | TMR0 Module and TMR0 Register                        | 39    |  |  |  |  |

| 7.0   | Comparator(s)                                        | 43    |  |  |  |  |

| 8.0   | Comparator Voltage Reference Module (PIC16F506 only) | 49    |  |  |  |  |

| 9.0   | Analog-to-Digital (A/D) Converter                    | 51    |  |  |  |  |

| 10.0  | Special Features Of The CPU                          | 55    |  |  |  |  |

|       | Instruction Set Summary                              |       |  |  |  |  |

| 12.0  | Development Support                                  | 79    |  |  |  |  |

| 13.0  | Electrical Characteristics                           | 83    |  |  |  |  |

| 14.0  | DC and AC Characteristics Graphs and Charts          | 97    |  |  |  |  |

| 15.0  | Packaging                                            | . 105 |  |  |  |  |

| Index |                                                      | . 117 |  |  |  |  |

| The N | ficrochip Web Site                                   | . 119 |  |  |  |  |

| Custo | Customer Change Notification Service                 |       |  |  |  |  |

|       | Customer Support                                     |       |  |  |  |  |

| Read  | Reader Response                                      |       |  |  |  |  |

| Produ | roduct Identification System                         |       |  |  |  |  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 2.0 PIC12F510/16F506 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12F510/16F506 Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices, but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry code, password or ID number.

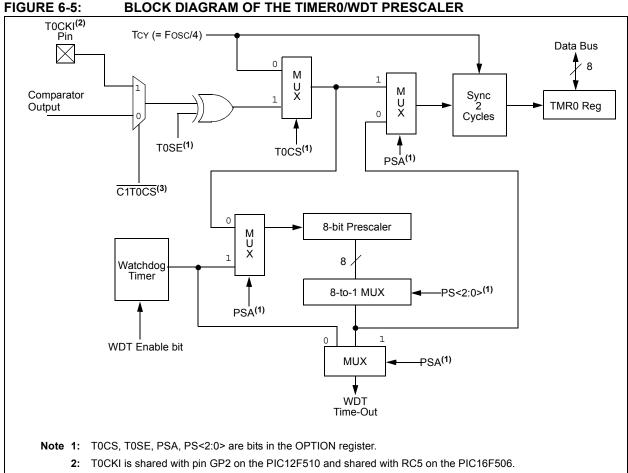

#### 4.4 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, that contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<7:0> bits.

- Note 1: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin (i.e., note that TRIS overrides Option control of GPPU/RBPU and GPWU/RBWU).

- **2:** If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

#### REGISTER 4-3: OPTION\_REG: OPTION REGISTER (PIC12F510)

| W-1         | W-1  | W-1  | W-1  | W-1 | W-1 | W-1 | W-1 |

|-------------|------|------|------|-----|-----|-----|-----|

| GPWU        | GPPU | TOCS | TOSE | PSA | PS2 | PS1 | PS0 |

| bit 7 bit 0 |      |      |      |     |     |     |     |

| Legend:    |                                                                                                            |                                                             |                                                                           |                                    |                    |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Reada  | eadable bit W = Writable bit                                                                               |                                                             | U                                                                         | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value | at POR '1' =                                                                                               | Bit is set                                                  | '0'                                                                       | = Bit is cleared                   | x = Bit is unknown |  |  |  |

| bit 7      | <b>GPWU:</b> Enable Wake-u<br>1 = Disabled<br>0 = Enabled                                                  | p On Pin Chang                                              | e bit (GP0, GP                                                            | 1, GP3)                            |                    |  |  |  |

| bit 6      | <b>GPPU:</b> Enable Weak Pu<br>1 = Disabled<br>0 = Enabled                                                 | ull-Ups bit (GP0,                                           | GP1, GP3)                                                                 |                                    |                    |  |  |  |

| bit 5      | 1 = Transition on TOCI                                                                                     |                                                             |                                                                           |                                    |                    |  |  |  |

| bit 4      | <b>T0SE:</b> Timer0 Source E<br>1 = Increment on high<br>0 = Increment on low-1                            | -to-low transition                                          |                                                                           |                                    |                    |  |  |  |

| bit 3      | <ul> <li>PSA: Prescaler Assignr</li> <li>1 = Prescaler assigner</li> <li>0 = Prescaler assigner</li> </ul> | d to the WDT                                                |                                                                           |                                    |                    |  |  |  |

| bit 2-0    | PS<2:0>: Prescaler Rat                                                                                     | e Select bits                                               |                                                                           |                                    |                    |  |  |  |

|            | Bit Value                                                                                                  | Timer0 Rate                                                 | WDT Rate                                                                  |                                    |                    |  |  |  |

|            | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                       | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 |                                    |                    |  |  |  |

# 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

| Note: | On the PIC12F510, I/O PORTB is refer- |  |  |  |

|-------|---------------------------------------|--|--|--|

|       | enced as GPIO. On the PIC16F506, I/O  |  |  |  |

|       | PORTB is referenced as PORTB.         |  |  |  |

## 5.1 PORTB/GPIO

PORTB/GPIO is an 8-bit I/O register. Only the loworder 6 bits are used (RB/GP<5:0>). Bits 7 and 6 are unimplemented and read as '0's. Please note that RB3/ GP3 is an input only pin. The Configuration Word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during a port read. Pins RB0/GP0, RB1/GP1, RB3/GP3 and RB4 (PIC16F506 only) can be configured with weak pull-up and also for wake-up on change. The wake-up on change and weak <u>pull-up</u> functions are not pin selectable. If RB3/GP3/MCLR is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

# 5.2 PORTC (PIC16F506 Only)

PORTC is an 8-bit I/O register. Only the low-order 6 bits are used (RC<5:0>). Bits 7 and 6 are unimplemented and read as '0's.

# 5.3 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exception is RB3/GP3, which are input only, and the TOCKI pin, which may be controlled by the OPTION register. See Register 4-3.

| Note: | A read of the port reads the pins, not the<br>output data latches. That is, if an output<br>driver on a pin is enabled and driven high |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|

|       | but the external system is holding it low, a<br>read of the port will indicate that the pin is<br>low.                                 |

**Note:** The TRIS registers are write-only and are set (output drivers disabled) upon Reset.

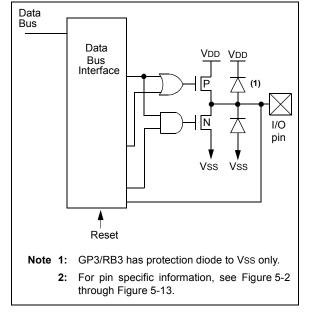

# 5.4 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except RB3/GP3 which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except RB3/GP3) can be programmed individually as input or output.

FIGURE 5-1:

#### PIC12F510/16F506 EQUIVALENT CIRCUIT FOR PIN DRIVE<sup>(2)</sup>

# TABLE 5-1: SUMMARY OF PORT REGISTERS

| Address | Name                    | Bit 7 | Bit 6 | Bit 5     | Bit 4                | Bit 3 | Bit 2 | Bit 1   | Bit 0   | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|-------|-------|-----------|----------------------|-------|-------|---------|---------|-------------------------------|---------------------------------|

| N/A     | TRISGPIO <sup>(1)</sup> |       |       | I/O Contr | ol Registe           | r     |       |         |         | 11 1111                       | 11 1111                         |

| N/A     | TRISB <sup>(2)</sup>    | _     | —     | I/O Contr | I/O Control Register |       |       | 11 1111 | 11 1111 |                               |                                 |

| N/A     | TRISC <sup>(2)</sup>    | _     | _     | I/O Contr | ol Registe           | r     |       |         |         | 11 1111                       | 11 1111                         |

| N/A     | OPTION <sup>(1)</sup>   | GPWU  | GPPU  | TOCS      | TOSE                 | PSA   | PS2   | PS1     | PS0     | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup>   | RBWU  | RBPU  | TOCS      | TOSE                 | PSA   | PS2   | PS1     | PS0     | 1111 1111                     | 1111 1111                       |

| 03h     | STATUS <sup>(1)</sup>   | GPWUF | CWUF  | PA0       | TO                   | PD    | Z     | DC      | С       | 0001 1xxx                     | qq0q quuu <b>(3)</b>            |

| 03h     | STATUS <sup>(2)</sup>   | RBWUF | CWUF  | PA0       | TO                   | PD    | Z     | DC      | С       | 0001 1xxx                     | qq0q quuu <sup>(3)</sup>        |

| 06h     | GPIO <sup>(1)</sup>     | _     | _     | GP5       | GP4                  | GP3   | GP2   | GP1     | GP0     | xx xxxx                       | uu uuuu                         |

| 06h     | PORTB <sup>(2)</sup>    | —     | —     | RB5       | RB4                  | RB3   | RB2   | RB1     | RB0     | xx xxxx                       | uu uuuu                         |

| 07h     | PORTC <sup>(2)</sup>    | _     |       | RC5       | RC4                  | RC3   | RC2   | RC1     | RC0     | xx xxxx                       | uu uuuu                         |

$\label{eq:logend: Legend: Legend: -= unimplemented read as `0', x = unknown, u = unchanged, q = depends on condition.$

Note 1: PIC12F510 only.

2: PIC16F506 only.

3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

# TABLE 5-2: I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC16F506)

| Priority | RB0       | RB1       | RB2   | RB3        | RB4         | RB5        |

|----------|-----------|-----------|-------|------------|-------------|------------|

| 1        | AN0/C1IN+ | AN1/C1IN- | AN2   | Input/MCLR | OSC2/CLKOUT | OSC1/CLKIN |

| 2        | TRISB     | TRISB     | C10UT | —          | TRISB       | TRISB      |

| 3        | _         |           | TRISB | _          | _           |            |

# TABLE 5-3: I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC16F506)

| Priority | RC0   | RC1   | RC2   | RC3   | RC4   | RC5   |

|----------|-------|-------|-------|-------|-------|-------|

| 1        | C2IN+ | C2IN- | CVREF | TRISC | C2OUT | TOCKI |

| 2        | TRISC | TRISC | TRISC |       | TRISC | TRISC |

# TABLE 5-4:I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC12F510)

| Priority | GP0       | GP1       | GP2    | GP3        | GP4    | GP5        |

|----------|-----------|-----------|--------|------------|--------|------------|

| 1        | AN0/C1IN+ | AN1/C1IN- | AN2    | Input/MCLR | OSC2   | OSC1/CLKIN |

| 2        | TRISIO    | TRISIO    | C10UT  | _          | TRISIO | TRISIO     |

| 3        | _         | —         | TOCKI  | _          | _      | _          |

| 4        |           | —         | TRISIO | —          | _      | _          |

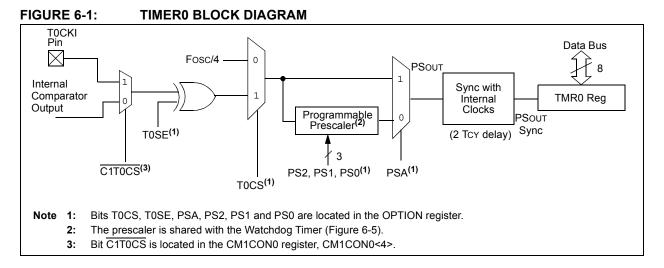

# 6.0 TMR0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select:

- Edge select for external clock

- External clock from either the T0CKI pin or from the output of the comparator

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

There are two types of Counter mode. The first Counter mode uses the T0CKI pin to increment Timer0. It is selected by setting the T0CKI bit (OPTION<5>), setting the  $\overline{C1T0CS}$  bit (CM1CON0<4>) and setting the  $\overline{C1OUTEN}$  bit (CM1CON0<6>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 With An External Clock".

The second Counter mode uses the output of the comparator to increment Timer0. It can be entered in two different ways. The first way is selected by setting the TOCS bit (OPTION<5>), and clearing the C1TOCS bit (CM1CON0<4>) (C1OUTEN [CM1CON0<6>] does not affect this mode of operation). This enables an internal connection between the comparator and the Timer0.

The second way is selected by setting the T0CS bit (OPTION<5>), setting the C1T0CS bit (CM1CON0) and clearing the C10UTEN bit (CM1CON0<6>). This allows the output of the comparator onto the T0CKI pin, while keeping the T0CKI input active. Therefore, any comparator change on the COUT pin is fed back into the T0CKI input. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input as discussed in Section 6.1 "Using Timer0 With An External Clock".

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 6.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

#### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

# EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

|        | •           |                          |

|--------|-------------|--------------------------|

| CLRWDT |             | ;Clear WDT               |

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| MOVLW  | `00xx1111'b | ;These 3 lines (5, 6, 7) |

| OPTION |             | ;are required only if    |

|        |             | ;desired                 |

| CLRWDT |             | ;PS<2:0> are 000 or 001  |

| MOVLW  | `00xx1xxx'b | ;Set Postscaler to       |

| OPTION |             | ;desired WDT rate        |

|        |             |                          |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

| EXAMPLE 6-2: | CHANGING PRESCALER |

|--------------|--------------------|

|              | (WDT→TIMER0)       |

| CLRWDT |           | ;Clear WDT and      |

|--------|-----------|---------------------|

|        |           | ;prescaler          |

| MOVLW  | `xxx0xxx' | ;Select TMR0, new   |

|        |           | ;prescale value and |

|        |           | ;clock source       |

| OPTION |           |                     |

3: Bit C1T0CS is located in the CM1CON0 register.

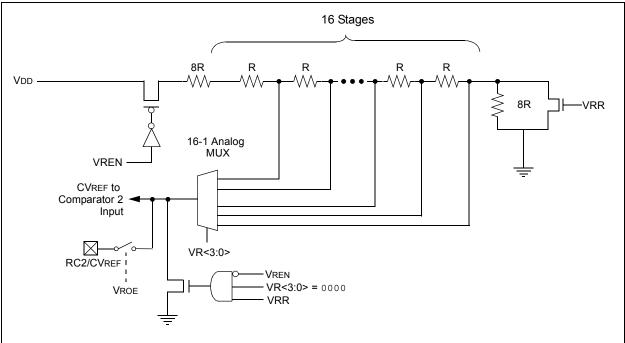

# 8.0 COMPARATOR VOLTAGE REFERENCE MODULE (PIC16F506 ONLY)

The comparator voltage reference module also allows the selection of an internally generated voltage reference for one of the C2 comparator inputs. The VRCON register (Register 8-1) controls the voltage reference module shown in Figure 8-1.

# 8.1 Configuring The Voltage Reference

The voltage reference can output 32 voltage levels; 16 in a high range and 16 in a low range.

Equation 8-1 determines the output voltages:

#### **EQUATION 8-1:**

$VRR = 1 (low range): CVREF = (VR < 3:0 > /24) \times VDD$ VRR = 0 (high range):CVREF = (VDD/4) + (VR < 3:0 > x VDD/32)

# 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep CVREF from approaching VSS or VDD. The exception is when the module is disabled by clearing the VREN bit (VRCON<7>). When disabled, the reference voltage is VSS when VR<3:0> is '0000' and the VRR (VRCON<5>) bit is set. This allows the comparator to detect a zero-crossing and not consume the CVREF module current.

The voltage reference is VDD derived and, therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the comparator voltage reference can be found in Section 13.2 "DC Characteristics: PIC12F510/16F506 (Extended)".

#### REGISTER 8-1: VRCON: VOLTAGE REFERENCE CONTROL REGISTER (PIC16F506 ONLY)

| R/W-0 | R/W-0 | R/W-1 | U-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-------|-------|-----|-------|-------|-------|-------|

| VREN  | VROE  | VRR   | —   | VR3   | VR2   | VR1   | VR0   |

| bit 7 |       |       |     |       |       |       | bit 0 |

| Legend:    |          |                                                |                                     |                                |  |

|------------|----------|------------------------------------------------|-------------------------------------|--------------------------------|--|

| R = Read   | able bit | W = Writable bit                               | U = Unimplemented bit,<br>otherwise | read as '0', except if denoted |  |

| -n = Value | e at POR | '1' = Bit is set                               | '0' = Bit is cleared                | x = Bit is unknown             |  |

| bit 7      | VREN: C  | VREF Enable bit                                |                                     |                                |  |

|            |          | F is powered on<br>F is powered down, no curre | ent is drawn                        |                                |  |

| bit 6      | VROE: C  | VROE: CVREF Output Enable bit <sup>(1)</sup>   |                                     |                                |  |

|            |          | r output is onabled                            |                                     |                                |  |

1 = CVREF output is enabled

0 = CVREF output is disabled

bit 5 VRR: CVREF Range Selection bit

1 = Low range

0 = High range

bit 4 Unimplemented: Read as '1'

- bit 3-0 VR<3:0> CVREF Value Selection bit

- When VRR = 1: CVREF = (VR < 3:0 > /24)\*VDD

- When VRR = 0: CVREF = VDD/4 + (VR < 3:0 > /32)\*VDD

- **Note 1:** When this bit is set, the TRIS for the CVREF pin is overridden and the analog voltage is placed on the CVREF pin.

- 2: CVREF controls for ratio metric reference applies to Comparator 2 on the PIC16F506 only.

#### FIGURE 8-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

#### TABLE 8-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Add | Name                   | Bit 7 | Bit 6   | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1   | Bit 0 | Value on<br>POR | Value on all other Resets |

|-----|------------------------|-------|---------|-------|---------|-------|--------|---------|-------|-----------------|---------------------------|

| 0Ch | VRCON                  | VREN  | VROE    | VRR   | _       | VR3   | VR2    | VR1     | VR0   | 001- 1111       | 001- 1111                 |

| 08h | CM1CON0 <sup>(1)</sup> | C10UT | C10UTEN | C1POL | C1T0CS  | C10N  | C1NREF | C1PREF  | C1WU  | 1111 1111       | uuuu uuuu                 |

| 0Bh | CM2CON0 <sup>(1)</sup> | C2OUT | C2OUTEN | C2POL | C2PREF2 | C2ON  | C2NREF | C2PREF1 | C2WU  | 1111 1111       | uuuu uuuu                 |

$\label{eq:Legend: Legend: Legend: u = unchanged, - = unimplemented, read as `0`.$

Note 1: PIC16F506 only.

#### 9.1.6 ANALOG CONVERSION RESULT REGISTER

The ADRES register contains the results of the last conversion. These results are present during the sampling period of the next analog conversion process. After the sampling period is over, ADRES is cleared (= 0). A 'leading one' is then right shifted into the ADRES to serve as an internal conversion complete bit. As each bit weight, starting with the MSB, is converted, the leading one is shifted right and the converted bit is stuffed into ADRES. After a total of 9 right

shifts of the 'leading one' have taken place, the conversion is complete; the 'leading one' has been shifted out and the GO/DONE bit is cleared.

If the GO/DONE bit is cleared in software during a conversion, the conversion stops. The data in ADRES is the partial conversion result. This data is valid for the bit weights that have been converted. The position of the 'leading one' determines the number of bits that have been converted. The bits that were not converted before the GO/DONE was cleared are unrecoverable.

## REGISTER 9-1: ADCON0: A/D CONTROL REGISTER (PIC12F510)

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|---------|-------|

| ANS1  | ANS0  | ADCS1 | ADCS0 | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |       |       |       |       |       |         | bit 0 |

| Legend:            |                                                    |                                                                                                                                                                  |                                                                                                          |                                                                                                                       |  |

|--------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| R = Readable bit   |                                                    | W = Writable bit                                                                                                                                                 | U = Unimplemented bit, read as '0'                                                                       |                                                                                                                       |  |

| -n = Value         | e at POR                                           | '1' = Bit is set                                                                                                                                                 | '0' = Bit is cleared                                                                                     | x = Bit is unknown                                                                                                    |  |

| bit 7-6            | 00 = No<br>01 = AN<br>10 = AN                      | <b>0&gt;:</b> ADC Analog Input Pin S<br>pins configured for analog in<br>2 configured as an analog ir<br>2 and AN0 configured as an<br>2, AN1 and AN0 configured | nput<br>iput<br>alog inputs                                                                              |                                                                                                                       |  |

| bit 5-4            | ADCS<<br>00 = FO<br>01 = FO<br>10 = FO<br>11 = IN  | sc/8<br>sc/4                                                                                                                                                     | s Select bits                                                                                            |                                                                                                                       |  |

| bit 3-2            | 00 = Ch<br>01 = Ch<br>10 = Ch                      | <b>0&gt;:</b> ADC Channel Select bits<br>annel AN0<br>annel AN1<br>annel AN2<br>V absolute voltage reference                                                     |                                                                                                          |                                                                                                                       |  |

| bit 1              | 1 = AD0<br>auto<br>0 = AD0                         | omatically cleared by hardwa                                                                                                                                     | Setting this bit starts an Al<br>are when the ADC is done con<br>in progress. Manually clearin           | DC conversion cycle. This bit<br>verting.<br>Ig this bit while a conversion is                                        |  |

| bit 0              | 1 = AD0                                            | ADC Enable bit<br>C module is operating<br>C module is shut-off and con                                                                                          | sumes no power                                                                                           |                                                                                                                       |  |

| Note 1:<br>2:      | less of the pir<br>input to the co<br>that the ADC | n function previously defined omparator and the ADC will b                                                                                                       | . The only exception to this is<br>be active at the same time. It is<br>nput does not affect their appli | forced into Analog mode, regard-<br>the comparator, where the analog<br>the users responsibility to ensur-<br>cation. |  |

| 3:                 |                                                    | s default to 11 after any Res                                                                                                                                    |                                                                                                          |                                                                                                                       |  |

| <u></u> <i>A</i> . |                                                    | hit is clear the GO/DONE hit                                                                                                                                     | cannot ha sat                                                                                            |                                                                                                                       |  |

4: If the ADON bit is clear, the GO/DONE bit cannot be set.

| Mnemonic, |      | Description                                       | Cycles           | 12-1   | Bit Opc | ode  | Status   | Notes   |

|-----------|------|---------------------------------------------------|------------------|--------|---------|------|----------|---------|

| Opera     | ands | Description                                       | Cycles           | MSb    |         | LSb  | Affected | Notes   |

| ADDWF     | f, d | Add W and f                                       | 1                | 0001   | 11df    | ffff | C, DC, Z | 1, 2, 4 |

| ANDWF     | f, d | AND W with f                                      | 1                | 0001   | 01df    | ffff | Z        | 2, 4    |

| CLRF      | f    | Clear f                                           | 1                | 0000   | 011f    | ffff | Z        | 4       |

| CLRW      | -    | Clear W                                           | 1                | 0000   | 0100    | 0000 | Z        |         |

| COMF      | f, d | Complement f                                      | 1                | 0010   | 01df    | ffff | Z        |         |

| DECF      | f, d | Decrement f                                       | 1                | 0000   | 11df    | ffff | Z        | 2, 4    |

| DECFSZ    | f, d | Decrement f, Skip if 0                            | 1 <sup>(2)</sup> | 0010   | 11df    | ffff | None     | 2, 4    |

| INCF      | f, d | Increment f                                       | 1                | 0010   | 10df    | ffff | Z        | 2, 4    |

| INCFSZ    | f, d | Increment f, Skip if 0                            | 1 <sup>(2)</sup> | 0011   | 11df    | ffff | None     | 2, 4    |

| IORWF     | f, d | Inclusive OR W with f                             | 1                | 0001   | 00df    | ffff | Z        | 2, 4    |

| MOVF      | f, d | Move f                                            | 1                | 0010   | 00df    | ffff | Z        | 2, 4    |

| MOVWF     | f    | Move W to f                                       | 1                | 0000   | 001f    | ffff | None     | 1, 4    |

| NOP       | _    | No Operation                                      | 1                | 0000   | 0000    | 0000 | None     |         |

| RLF       | f, d | Rotate left f through Carry                       | 1                | 0011   | 01df    | ffff | С        | 2, 4    |

| RRF       | f, d | Rotate right f through Carry                      | 1                | 0011   | 00df    | ffff | С        | 2, 4    |

| SUBWF     | f, d | Subtract W from f                                 | 1                | 0000   | 10df    | ffff | C, DC, Z | 1, 2, 4 |

| SWAPF     | f, d | Swap f                                            | 1                | 0011   | 10df    | ffff | None     | 2, 4    |

| XORWF     | f, d | Exclusive OR W with f                             | 1                | 0001   | 10df    | ffff | Z        | 2, 4    |

|           | ·    | BIT-ORIENTED FILE REGISTE                         | R OPER           | ATIONS | ;       |      | 1        |         |

| BCF       | f, b | Bit Clear f                                       | 1                | 0100   | bbbf    | ffff | None     | 2, 4    |

| BSF       | f, b | Bit Set f                                         | 1                | 0101   | bbbf    | ffff | None     | 2, 4    |

| BTFSC     | f, b | Bit Test f, Skip if Clear                         | 1 <sup>(2)</sup> | 0110   | bbbf    | ffff | None     | ,       |

| BTFSS     | f, b | Bit Test f, Skip if Set                           | 1 <sup>(2)</sup> | 0111   | bbbf    | ffff | None     |         |

|           | ,    | LITERAL AND CONTROL C                             | PERATIO          | ONS    |         |      |          | 1       |

| ANDLW     | k    | AND literal with W                                | 1                | 1110   | kkkk    | kkkk | Z        |         |

| CALL      | k    | Call Subroutine                                   | 2                | 1001   | kkkk    | kkkk | None     | 1       |

| CLRWDT    | _    | Clear Watchdog Timer                              | 1                | 0000   | 0000    | 0100 | TO, PD   |         |

| GOTO      | k    | Unconditional branch                              | 2                | 101k   | kkkk    | kkkk | None     |         |

| IORLW     | k    | Inclusive OR literal with W                       | 1                | 1101   | kkkk    | kkkk | Z        |         |

| MOVLW     | k    | Move literal to W                                 | 1                | 1100   | kkkk    | kkkk | None     |         |

| OPTION    | _    | Load OPTION register                              | 1                | 0000   | 0000    | 0010 | None     |         |

| RETLW     | k    | Return, place literal in W                        | 2                | 1000   | kkkk    | kkkk | None     |         |

| SLEEP     | _    | Go into Standby mode                              | 1                | 0000   | 0000    | 0011 | TO, PD   |         |

| TRIS      | f    | Load TRIS register                                | 1                | 0000   | 0000    | Offf | None     | 3       |

| XORLW     | k    | Exclusive OR literal to W                         | 1                | 1111   | kkkk    | kkkk | Z        | -       |

| Note 1:   |      | bit of the Program Counter will be forced to a 'o | ' by any i       |        |         |      |          | cept fo |

#### TABLE 11-2: INSTRUCTION SET SUMMARY

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 6, causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

4: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                  |

| Operation:       | $(f) - 1 \rightarrow (dest)$                                                                                                                      |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is 'o',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                           |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                               |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                          |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                |  |  |  |

| Operation:       | (f) – 1 $\rightarrow$ d; skip if result = 0                                                                                                                                                                                                                                                                                                     |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '0', the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '0', then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a<br>two-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                      |

| Operands:        | $0 \le k \le 511$                                                                                                                                                                            |

| Operation:       | $k \rightarrow PC<8:0>;$<br>STATUS <6:5> $\rightarrow PC<10:9>$                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                         |

| Description:     | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS <6:5>. GOTO is a two-<br>cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |  |  |  |

| Operation:       | (W) .OR. (k) $\rightarrow$ (W)                                                                                            |  |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |  |  |  |  |  |

# 12.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 12.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 and PIC24 families of microcontrollers and the dsPIC30 and dsPIC33 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 12.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 12.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

# 12.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 12.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 12.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC<sup>®</sup> and MCU devices. It debugs and programs PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high speed, noise tolerant, lowvoltage differential signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 12.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

# 12.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

#### TABLE 13-1: COMPARATOR SPECIFICATIONS

| Sym   | Characteristics              | Min   | Тур | Max       | Units | Comments       |

|-------|------------------------------|-------|-----|-----------|-------|----------------|

| Vos   | Input Offset Voltage         | —     | ±3  | ±10       | mV    | (Vdd - 1.5V)/2 |

| Vсм   | Input Common Mode Voltage    | 0     | _   | Vdd - 1.5 | V     |                |

| CMRR  | Common Mode Rejection Ratio  | +55*  | _   | —         | dB    |                |

| TRT   | Response Time <sup>(1)</sup> | —     | 150 | 400*      | ns    | Internal       |

| VIVRF | Internal Voltage Reference   | 0.550 | 0.6 | 0.650     | V     |                |

These parameters are characterized but not tested. \*

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD - 1.5V.

#### TABLE 13-2: COMPARATOR VOLTAGE REFERENCE (CVREF) SPECIFICATIONS

| Sym   | Characteristics                  | Min        | Тур       | Max   | Units | Comments             |

|-------|----------------------------------|------------|-----------|-------|-------|----------------------|

| CVRES | Resolution                       | _          | VDD/24*   | _     | LSb   | Low Range (VRR = 1)  |

|       |                                  | —          | VDD/32    | —     | LSb   | High Range (VRR = 0) |

|       | Absolute Accuracy                | _          |           | ±1/2* | LSb   | Low Range (VRR = 1)  |

|       |                                  | —          |           | ±1/2* | LSb   | High Range (VRR = 0) |

|       | Unit Resistor Value (R)          | _          | 2K*       | _     | Ω     |                      |

|       |                                  | —          |           |       |       |                      |

|       | Settling Time <sup>(1)</sup>     | _          |           | 10*   | μs    |                      |

| *     | These parameters are characteriz | zed but no | t tested. |       |       |                      |

These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

#### TABLE 13-3: A/D CONVERTER CHARACTERISTICS (PIC16F506/PIC12F510)

| Param<br>No. | Sym  | Characteristic                                    | Min  | Тур†                      | Мах            | Units | Conditions                               |

|--------------|------|---------------------------------------------------|------|---------------------------|----------------|-------|------------------------------------------|

| A01          | Nr   | Resolution                                        |      |                           | 8 bits         | bit   |                                          |

| A03          | EIL  | Integral Error                                    | _    | —                         | ± 1.5          | LSb   | VDD = 5.0V                               |

| A04          | Edl  | Differential Error                                | _    | —                         | -1 < EDL ≤ 1.5 | LSb   | No missing codes to<br>8 bits VDD = 5.0V |

| A05          | EFS  | Full-scale Range                                  | 2    | —                         | 5.5*           | V     | Vdd                                      |

| A06          | EOFF | Offset Error                                      | _    | —                         | ± 1.5          | LSb   | VDD = 5.0V                               |

| A07          | Egn  | Gain Error                                        | -0.5 | —                         | +1.75          | LSb   | VDD = 5.0V                               |

| A10          |      | Monotonicity                                      | _    | guaranteed <sup>(1)</sup> | _              |       | $Vss \leq Vain \leq Vdd$                 |

| A25          | VAIN | Analog Input Voltage                              | Vss  | —                         | Vdd            | V     |                                          |

| A30          | Zain | Recommended Impedance<br>of Analog Voltage Source | _    | —                         | 10             | kΩ    |                                          |

These parameters are characterized but not tested.

† Data in the "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only are not tested.

Note 1: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

| VDD (Volts)   | Temperature (°C) | Min | Тур  | Max  | Units |

|---------------|------------------|-----|------|------|-------|

| RB0 (GP0)/RB1 | (GP1)            |     |      |      |       |

| 2.0           | -40              | 73K | 105K | 186K | Ω     |

|               | 25               | 73K | 113K | 187K | Ω     |

|               | 85               | 82K | 123K | 190K | Ω     |

|               | 125              | 86K | 132k | 190K | Ω     |

| 5.5           | -40              | 15K | 21K  | 33K  | Ω     |

|               | 25               | 15K | 22K  | 34K  | Ω     |

|               | 85               | 19K | 26k  | 35K  | Ω     |

|               | 125              | 23K | 29K  | 35K  | Ω     |

| RB3 (GP3)     |                  |     |      |      |       |

| 2.0           | -40              | 63K | 81K  | 96K  | Ω     |

|               | 25               | 77K | 93K  | 116K | Ω     |

|               | 85               | 82K | 96k  | 116K | Ω     |

|               | 125              | 86K | 100K | 119K | Ω     |

| 5.5           | -40              | 16K | 20k  | 22K  | Ω     |

|               | 25               | 16K | 21K  | 23K  | Ω     |

|               | 85               | 24K | 25k  | 28K  | Ω     |

|               | 125              | 26K | 27K  | 29K  | Ω     |

# TABLE 13-9: PULL-UP RESISTOR RANGES