Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 38 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f510-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table of Contents

| 1.0   | General Description                                  | 5     |

|-------|------------------------------------------------------|-------|

| 2.0   | PIC12F510/16F506 Device Varieties                    | 7     |

| 3.0   | Architectural Overview                               | 9     |

| 4.0   | Memory Organization                                  | 15    |

| 5.0   | I/O Port                                             | 27    |

| 6.0   | TMR0 Module and TMR0 Register                        | 39    |

| 7.0   | Comparator(s)                                        | 43    |

| 8.0   | Comparator Voltage Reference Module (PIC16F506 only) | 49    |

| 9.0   | Analog-to-Digital (A/D) Converter                    | 51    |

| 10.0  | Special Features Of The CPU                          | 55    |

|       | Instruction Set Summary                              |       |

| 12.0  | Development Support                                  | 79    |

| 13.0  | Electrical Characteristics                           | 83    |

| 14.0  | DC and AC Characteristics Graphs and Charts          | 97    |

| 15.0  | Packaging                                            | . 105 |

| Index |                                                      | . 117 |

| The N | ficrochip Web Site                                   | . 119 |

| Custo | mer Change Notification Service                      | . 119 |

|       | mer Support                                          |       |

| Read  | er Response                                          | . 120 |

| Produ | Ict Identification System                            | . 121 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

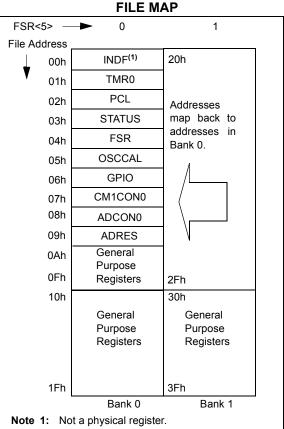

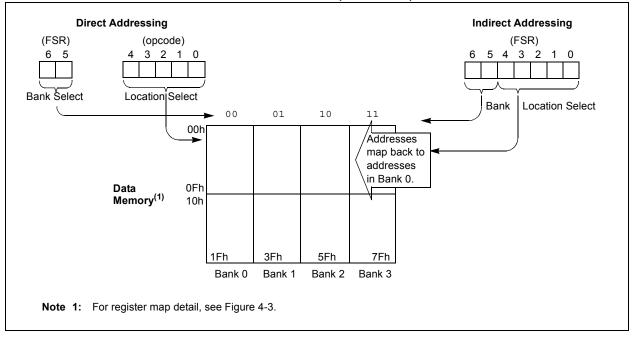

#### 4.2 **Data Memory Organization**

Data memory is composed of registers or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers (SFRs) and General Purpose Registers (GPRs).

The Special Function Registers include the TMR0 register, the Program Counter (PCL), the STATUS register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Function Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC12F510, the register file is composed of 10 Special Function Registers, 6 General Purpose Registers and 32 General Purpose Registers accessed by banking (see Figure 4-2).

For the PIC16F506, the register file is composed of 13 Special Function Registers, 3 General Purpose Registers and 64 General Purpose Registers, accessed by banking (see Figure 4-3).

GENERAL PURPOSE REGISTER 4.2.1 FILE

The General Purpose Register file is accessed either directly or indirectly through the File Select Register (FSR). See Section 4.8 "Indirect Data Addressing: INDF and FSR Registers".

#### FIGURE 4-3: PIC16F506 REGISTER FILE MAP

#### FSR<6:5> 00 01 10 11 File Address INDF<sup>(1)</sup> 00h 20h 40h 60h TMR0 01h 02h PCL 03h STATUS 04h FSR OSCCAL 05h Addresses map back to addresses in Bank 0. PORTB 06h PORTC 07h CM1CON0 08h ADCON0 09h ADRES 0Ah CM2CON0 0Bh 0Ch VRCON 0Dh General Purpose Registers 0Fh 2Fh 4Fh 6Fh 10h 30h 50h 70h General General General General Purpose Purpose Purpose Purpose Registers Registers Registers Registers 5Fh 7Fh 1Fh 3Fh Bank 0 Bank 1 Bank 2 Bank 3

Note 1: Not a physical register.

#### FIGURE 4-2: PIC12F510 REGISTER

| Address            | Name    | Bit 7        | Bit 6                | Bit 5        | Bit 4        | Bit 3        | Bit 2     | Bit 1   | Bit 0 | Value on<br>Power-on<br>Reset |  |  |  |

|--------------------|---------|--------------|----------------------|--------------|--------------|--------------|-----------|---------|-------|-------------------------------|--|--|--|

| N/A                | TRIS    | I/O Control  | Registers (TR        | ISB, TRISC   | ;)           |              |           |         |       | 11 1111                       |  |  |  |

| N/A                | OPTION  | Contains co  | ontrol bits to co    | onfigure Tim | er0 and Time | r0/WDT Pre   | scaler    |         |       | 1111 1111                     |  |  |  |

| 00h                | INDF    | Uses conte   | nts of FSR to        | address dat  | a memory (no | t a physical | register) |         |       | xxxx xxxx                     |  |  |  |

| 01h                | TMR0    | Timer0 Mod   | r0 Module Register   |              |              |              |           |         |       |                               |  |  |  |

| 02h <sup>(1)</sup> | PCL     | Low Order    | w Order 8 bits of PC |              |              |              |           |         |       |                               |  |  |  |

| 03h                | STATUS  | RBWUF        | CWUF                 | PA0          | TO           | PD           | Z         | DC      | С     | 0001 1xxx                     |  |  |  |

| 04h                | FSR     | Indirect Dat | a Memory Ad          | dress Pointe | er           |              |           |         |       | 100x xxxx                     |  |  |  |

| 05h                | OSCCAL  | CAL6         | CAL5                 | CAL4         | CAL3         | CAL2         | CAL1      | CAL0    | —     | 1111 111-                     |  |  |  |

| 06h                | PORTB   | _            | _                    | RB5          | RB4          | RB3          | RB2       | RB1     | RB0   | xx xxxx                       |  |  |  |

| 07h                | PORTC   | —            | _                    | RC5          | RC4          | RC3          | RC2       | RC1     | RC0   | xx xxxx                       |  |  |  |

| 08h                | CM1CON0 | C10UT        | C10UTEN              | C1POL        | C1T0CS       | C10N         | C1NREF    | C1PREF  | C1WU  | 1111 1111                     |  |  |  |

| 09h                | ADCON0  | ANS1         | ANS0                 | ADCS1        | ADCS0        | CHS1         | CHS0      | GO/DONE | ADON  | 1111 1100                     |  |  |  |

| 0Ah                | ADRES   | ADC Conve    | ersion Result        |              |              |              |           |         |       | xxxx xxxx                     |  |  |  |

| 0Bh                | CM2CON0 | C2OUT        | C2OUTEN              | C2POL        | C2PREF2      | C2ON         | C2NREF    | C2PREF1 | C2WU  | 1111 1111                     |  |  |  |

| 0Ch                | VRCON   | VREN         | VROE                 | VRR          | (2)          | VR3          | VR2       | VR1     | VR0   | 0011 1111                     |  |  |  |

### TABLE 4-2: SPECIAL FUNCTION REGISTER SUMMARY – PIC16F506

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0' (if applicable). Shaded cells = unimplemented or unused.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 "Program Counter" for an explanation of how to access these bits.

2: Unimplemented bit VRCON<4> read as '1'.

### 4.3 STATUS Register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see **Section 11.0 "Instruction Set Summary"**.

| R/W-0         | R/W-0                                                                                   | R/W-0                                                                                                            | R-1                                                          | R-1                                                     | R/W-x                                    | R/W-x                       | R/W-x         |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------|------------------------------------------|-----------------------------|---------------|--|--|--|--|--|--|

| GPWUF         | CWUF                                                                                    | PA0                                                                                                              | TO                                                           | PD                                                      | Z                                        | DC                          | С             |  |  |  |  |  |  |

| bit 7         | •                                                                                       |                                                                                                                  |                                                              |                                                         | •                                        |                             | bit           |  |  |  |  |  |  |

|               |                                                                                         |                                                                                                                  |                                                              |                                                         |                                          |                             |               |  |  |  |  |  |  |

| Legend:       |                                                                                         |                                                                                                                  |                                                              |                                                         |                                          |                             |               |  |  |  |  |  |  |

| R = Readable  |                                                                                         | W = Writable b                                                                                                   | it                                                           | •                                                       | mented bit, read a                       |                             |               |  |  |  |  |  |  |

| -n = Value at | POR                                                                                     | '1' = Bit is set                                                                                                 |                                                              | '0' = Bit is cle                                        | ared                                     | x = Bit is unkno            | wn            |  |  |  |  |  |  |

| bit 7         | <b>GPWUF</b> : GPIC                                                                     |                                                                                                                  | Sleep on pin c                                               | hange                                                   |                                          |                             |               |  |  |  |  |  |  |

|               |                                                                                         | <ul><li>1 = Reset due to wake-up from Sleep on pin change</li><li>0 = After power-up or other Reset</li></ul>    |                                                              |                                                         |                                          |                             |               |  |  |  |  |  |  |

| bit 6         | CWUF: Compa                                                                             | arator Reset bit                                                                                                 |                                                              |                                                         |                                          |                             |               |  |  |  |  |  |  |

|               |                                                                                         | to wake-up from<br>er-up or other Res                                                                            | • •                                                          | parator change                                          |                                          |                             |               |  |  |  |  |  |  |

| bit 5         | 1 = Page 1 (20<br>0 = Page 0 (00<br>Each page is 5<br>Using the PA0                     | 00h-1FFh)<br>512 bytes.<br>bit as a general                                                                      | purpose read/v                                               |                                                         | es which do not us<br>with future produc | se it for program p<br>cts. | age preselect |  |  |  |  |  |  |

| bit 4         |                                                                                         | er-up, CLRWDT ins                                                                                                | struction, or SL                                             | EEP instruction                                         |                                          |                             |               |  |  |  |  |  |  |

| L:1. 0        |                                                                                         | ne-out occurred                                                                                                  |                                                              |                                                         |                                          |                             |               |  |  |  |  |  |  |

| bit 3         |                                                                                         | wn bit<br>er-up or by the CL<br>on of the SLEEP                                                                  |                                                              | on                                                      |                                          |                             |               |  |  |  |  |  |  |

| bit 2         | <b>Z</b> : Zero bit<br>1 = The result                                                   | of an arithmetic of an arithmetic of                                                                             | or logic operation                                           |                                                         |                                          |                             |               |  |  |  |  |  |  |

| bit 1         | <u>ADDWF:</u><br>1 = A carry fro<br>0 = A carry fro<br><u>SUBWF:</u><br>1 = A borrow fr | y/Borrow bit (for <i>i</i><br>m the 4th low-ord<br>m the 4th low-ord<br>rom the 4th low-or<br>rom the 4th low-or | ler bit of the re<br>ler bit of the re<br>order bit of the i | sult occurred<br>sult did not occu<br>result did not oc | ır                                       |                             |               |  |  |  |  |  |  |

| bit 0         | C: Carry/Borro<br>ADDWF :<br>1 = A carry occ<br>0 = A carry did                         | curred 1                                                                                                         | SUBWF and RR<br>UBWF :<br>= A borrow did<br>= A borrow oc    | not occur                                               | RRF OF RLF:                              | or MSb, respectiv           | ely           |  |  |  |  |  |  |

### REGISTER 4-1: STATUS: STATUS REGISTER (PIC12F510)

### 4.4 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, that contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<7:0> bits.

- Note 1: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin (i.e., note that TRIS overrides Option control of GPPU/RBPU and GPWU/RBWU).

- **2:** If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

### REGISTER 4-3: OPTION\_REG: OPTION REGISTER (PIC12F510)

| W-1   | W-1  | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|------|------|------|-----|-----|-----|-------|

| GPWU  | GPPU | TOCS | TOSE | PSA | PS2 | PS1 | PS0   |

| bit 7 |      |      |      |     |     |     | bit 0 |

| Legend:    |                                                                                                            |                                                             |                                                                           |                     |                    |

|------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|---------------------|--------------------|

| R = Reada  | ble bit W = V                                                                                              | Writable bit                                                | U                                                                         | = Unimplemented bit | , read as '0'      |

| -n = Value | at POR '1' =                                                                                               | Bit is set                                                  | '0'                                                                       | = Bit is cleared    | x = Bit is unknown |

| bit 7      | <b>GPWU:</b> Enable Wake-u<br>1 = Disabled<br>0 = Enabled                                                  | p On Pin Chang                                              | e bit (GP0, GP                                                            | 1, GP3)             |                    |

| bit 6      | <b>GPPU:</b> Enable Weak Pu<br>1 = Disabled<br>0 = Enabled                                                 | ull-Ups bit (GP0,                                           | GP1, GP3)                                                                 |                     |                    |

| bit 5      | <b>TOCS:</b> Timer0 Clock So<br>1 = Transition on TOCI<br>0 = Internal instruction                         | KI pin                                                      | KOUT)                                                                     |                     |                    |

| bit 4      | <b>T0SE:</b> Timer0 Source E<br>1 = Increment on high<br>0 = Increment on low-1                            | -to-low transition                                          |                                                                           |                     |                    |

| bit 3      | <ul> <li>PSA: Prescaler Assignr</li> <li>1 = Prescaler assigner</li> <li>0 = Prescaler assigner</li> </ul> | d to the WDT                                                |                                                                           |                     |                    |

| bit 2-0    | PS<2:0>: Prescaler Rat                                                                                     | e Select bits                                               |                                                                           |                     |                    |

|            | Bit Value                                                                                                  | Timer0 Rate                                                 | WDT Rate                                                                  |                     |                    |

|            | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                       | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 |                     |                    |

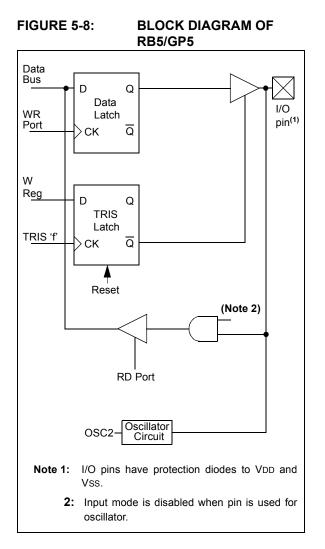

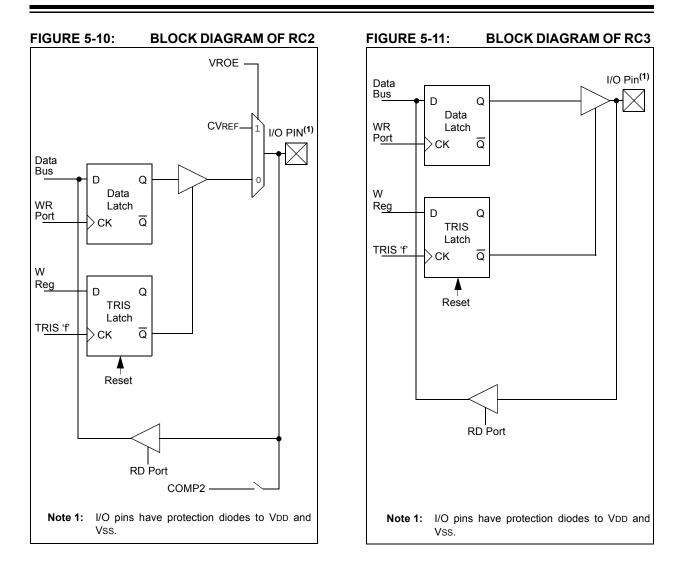

#### FIGURE 5-9: **BLOCK DIAGRAM OF** RC0/RC1 Data Bus D Q Data I/O WR Latch pin<sup>(1)</sup> P<u>ort</u> Q СК W Reg D Q TRIS Latch TRIS 'f' CK Q Reset Comp Pin Enable

RD Port

Vss.

COMP2

Note 1: I/O pins have protection diodes to VDD and

### TABLE 5-1: SUMMARY OF PORT REGISTERS

| Address | Name                    | Bit 7 | Bit 6 | Bit 5     | Bit 4      | Bit 3 | Bit 2 | Bit 1   | Bit 0   | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|-------|-------|-----------|------------|-------|-------|---------|---------|-------------------------------|---------------------------------|

| N/A     | TRISGPIO <sup>(1)</sup> |       |       | I/O Contr | ol Registe | r     |       |         |         | 11 1111                       | 11 1111                         |

| N/A     | TRISB <sup>(2)</sup>    | _     | —     | I/O Contr | ol Registe | r     |       |         |         | 11 1111                       | 11 1111                         |

| N/A     | TRISC <sup>(2)</sup>    | _     | _     | I/O Contr | ol Registe | r     |       | 11 1111 | 11 1111 |                               |                                 |

| N/A     | OPTION <sup>(1)</sup>   | GPWU  | GPPU  | TOCS      | TOSE       | PSA   | PS2   | PS1     | PS0     | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup>   | RBWU  | RBPU  | TOCS      | TOSE       | PSA   | PS2   | PS1     | PS0     | 1111 1111                     | 1111 1111                       |

| 03h     | STATUS <sup>(1)</sup>   | GPWUF | CWUF  | PA0       | TO         | PD    | Z     | DC      | С       | 0001 1xxx                     | qq0q quuu <b>(3)</b>            |

| 03h     | STATUS <sup>(2)</sup>   | RBWUF | CWUF  | PA0       | TO         | PD    | Z     | DC      | С       | 0001 1xxx                     | qq0q quuu <sup>(3)</sup>        |

| 06h     | GPIO <sup>(1)</sup>     | _     | _     | GP5       | GP4        | GP3   | GP2   | GP1     | GP0     | xx xxxx                       | uu uuuu                         |

| 06h     | PORTB <sup>(2)</sup>    | —     | —     | RB5       | RB4        | RB3   | RB2   | RB1     | RB0     | xx xxxx                       | uu uuuu                         |

| 07h     | PORTC <sup>(2)</sup>    | _     |       | RC5       | RC4        | RC3   | RC2   | RC1     | RC0     | xx xxxx                       | uu uuuu                         |

$\label{eq:logend: Legend: Legend: -= unimplemented read as `0', x = unknown, u = unchanged, q = depends on condition.$

Note 1: PIC12F510 only.

2: PIC16F506 only.

3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

### TABLE 5-2: I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC16F506)

| Priority | RB0       | RB1       | RB2   | RB3        | RB4         | RB5        |

|----------|-----------|-----------|-------|------------|-------------|------------|

| 1        | AN0/C1IN+ | AN1/C1IN- | AN2   | Input/MCLR | OSC2/CLKOUT | OSC1/CLKIN |

| 2        | TRISB     | TRISB     | C10UT | —          | TRISB       | TRISB      |

| 3        | _         |           | TRISB | _          | _           |            |

### TABLE 5-3: I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC16F506)

| Priority | RC0   | RC1   | RC2   | RC3   | RC4   | RC5   |

|----------|-------|-------|-------|-------|-------|-------|

| 1        | C2IN+ | C2IN- | CVREF | TRISC | C2OUT | TOCKI |

| 2        | TRISC | TRISC | TRISC |       | TRISC | TRISC |

### TABLE 5-4:I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC12F510)

| Priority | GP0       | GP1       | GP2    | GP3        | GP4    | GP5        |

|----------|-----------|-----------|--------|------------|--------|------------|

| 1        | AN0/C1IN+ | AN1/C1IN- | AN2    | Input/MCLR | OSC2   | OSC1/CLKIN |

| 2        | TRISIO    | TRISIO    | C10UT  | _          | TRISIO | TRISIO     |

| 3        | _         | _         | TOCKI  | _          | _      | _          |

| 4        |           | —         | TRISIO | —          | _      | _          |

| TABLE 5-5: | REQUIR | REQUIREMENTS FOR DIGITAL PIN OPERATION (PIC12F510) |          |          |     |     |     |          |          |  |  |  |  |

|------------|--------|----------------------------------------------------|----------|----------|-----|-----|-----|----------|----------|--|--|--|--|

|            | GP0    | GP0                                                | GP1      | GP1      | GP2 | GP2 | GP3 | GP4      | GP5      |  |  |  |  |

| CM1CON0    |        |                                                    |          |          |     |     |     |          |          |  |  |  |  |

| C1ON       | 0      | 1                                                  | 0        | 1        | 0   | 1   |     | —        | —        |  |  |  |  |

| C1PREF     | _      | 0                                                  | _        | 1        | —   | —   | —   | -        | —        |  |  |  |  |

| C1NREF     | _      |                                                    | _        | 0        |     | _   |     | _        | _        |  |  |  |  |

| C1T0CS     |        | _                                                  | _        | _        | _   | 1   | _   | _        | _        |  |  |  |  |

| C1OUTEN    | _      | —                                                  | _        | —        | _   | 1   | _   | _        | —        |  |  |  |  |

| CM2CON0    |        |                                                    |          |          |     |     |     |          |          |  |  |  |  |

| C2ON       | _      | _                                                  | —        | _        | —   | —   |     | —        | —        |  |  |  |  |

| C2PREF1    | _      | _                                                  | —        | —        | —   | _   |     | _        | —        |  |  |  |  |

| C2PREF2    | _      | _                                                  | —        | —        | —   |     | —   | _        | —        |  |  |  |  |

| C2NREF     | —      |                                                    | —        | —        |     |     | _   | —        | —        |  |  |  |  |

| C2OUTEN    |        | —                                                  | _        | _        | _   | _   | —   | _        | _        |  |  |  |  |

| VRCON0     |        |                                                    |          |          |     |     |     |          |          |  |  |  |  |

| VROE       | —      | _                                                  | —        | —        | —   | _   | _   | —        | —        |  |  |  |  |

| VREN       | —      | —                                                  | —        | —        | —   | —   | —   | —        | —        |  |  |  |  |

| OPTION     |        |                                                    |          |          |     |     |     |          |          |  |  |  |  |

| TOCS       | —      | _                                                  | —        | _        |     | 0   | _   | —        | —        |  |  |  |  |

| ADCON0     |        |                                                    |          |          |     |     |     |          |          |  |  |  |  |

| ANS<1:0>   | 00, 01 | 00, 01                                             | 00,01,10 | 00,01,10 | 00  | 00  |     | —        | —        |  |  |  |  |

| CONFIG     |        |                                                    |          |          |     |     | -   |          |          |  |  |  |  |

| MCLRE      | —      |                                                    | —        | —        | _   | _   | —   | —        | —        |  |  |  |  |

| INTOSC     | —      |                                                    | —        | —        | _   | —   | _   | —        | —        |  |  |  |  |

| LP         | —      |                                                    | —        | —        | _   | _   | _   | Disabled | Disabled |  |  |  |  |

| EXTRC      | —      |                                                    | —        | —        | _   | —   | —   |          | Disabled |  |  |  |  |

| XT         | —      | _                                                  | —        |          |     |     |     | Disabled | Disabled |  |  |  |  |

|            |        |                                                    |          |          |     |     |     |          |          |  |  |  |  |

### TABLE 5-5: REQUIREMENTS FOR DIGITAL PIN OPERATION (PIC12F510)

**Note 1:** Multiple column entries for a pin demonstrate the different permutations to arrive at digital functionality for the pin.

2: Shaded cells indicate the bit status does not affect the pins digital functionality.

| ABLE 5-6: REQUIREMENTS FOR DIGITAL PIN OPERATION (PIC16F506 PORTB)(1), (2) |        |       |       |          |          |     |     |     |          |          |  |

|----------------------------------------------------------------------------|--------|-------|-------|----------|----------|-----|-----|-----|----------|----------|--|

|                                                                            | RB0    | RB0   | RB0   | RB1      | RB1      | RB2 | RB2 | RB3 | RB4      | RB5      |  |

| CM1CON0                                                                    |        |       |       |          |          |     |     |     |          |          |  |

| C10N                                                                       | —      | 0     | 1     | 0        | 1        | 0   | 1   |     | —        | _        |  |

| C1PREF                                                                     | _      | _     | 0     |          |          |     | _   |     |          |          |  |

| C1NREF                                                                     | —      | _     | _     | —        | 0        |     | _   | _   | —        |          |  |

| C1T0CS                                                                     | —      | _     |       | _        | —        |     | _   |     | _        | _        |  |

| C1OUTEN                                                                    | —      | _     |       | _        | —        | —   | 1   | —   | _        | _        |  |

| CM2CON0                                                                    |        |       |       |          |          |     |     |     |          |          |  |

| C2ON                                                                       | 1      | —     | —     | —        | —        | _   | _   |     | —        | _        |  |

| C2PREF1                                                                    | 0      | _     | _     | _        | _        |     | _   | _   | —        |          |  |

| C2PREF2                                                                    | 1      | —     | _     | _        | —        | _   | —   | _   | —        | _        |  |

| C2NREF                                                                     | —      | _     | —     | _        | —        |     | _   | _   | —        | _        |  |

| C2OUTEN                                                                    | —      | _     | _     | _        | _        | _   | _   | _   | -        | _        |  |

| OPTION                                                                     |        |       |       |          |          |     |     |     |          |          |  |

| TOCS                                                                       | —      |       |       |          |          | _   |     |     | —        |          |  |

| ADCON0                                                                     |        |       |       |          |          |     |     |     |          |          |  |

| ANS<1:0>                                                                   | 00, 01 | 00,01 | 00,01 | 00,01,10 | 00,01,10 | 00  | 00  | _   | —        |          |  |

| CONFIG                                                                     |        |       |       |          |          |     |     |     |          |          |  |

| MCLRE                                                                      | —      | —     | —     | —        | —        |     |     | 0   | —        | _        |  |

| INTOSC                                                                     | —      | _     | —     | _        | —        |     | _   | _   | —        | _        |  |

| LP                                                                         | _      | _     | _     | _        | _        |     | _   | _   | Disabled | Disabled |  |

| EXTRC                                                                      |        | —     | _     | _        | —        | _   | —   | _   | —        | Disabled |  |

| ХТ                                                                         |        |       |       |          |          |     | —   | —   | Disabled | Disabled |  |

| EC                                                                         |        | —     | —     |          | —        | _   | —   | —   | —        | Disabled |  |

| HS                                                                         |        | —     |       | —        | —        | _   | —   | —   | Disabled | Disabled |  |

| INTOSC CLKOUT                                                              |        | —     | —     | —        | —        | _   | —   | —   |          | Disabled |  |

| EXTRC CLOCKOUT                                                             | —      | —     |       | —        |          | _   |     |     | Disabled | Disabled |  |

### TABLE 5-6: REQUIREMENTS FOR DIGITAL PIN OPERATION (PIC16F506 PORTB)<sup>(1), (2)</sup>

**Note 1:** Multiple column entries for a pin demonstrate the different permutations to arrive at digital functionality for the pin.

2: Shaded cells indicate the bit status does not affect the pins digital functionality.

### TABLE 5-7: REQUIREMENTS FOR DIGITAL PIN OPERATION (PIC16F506 PORTC)<sup>(1), (2)</sup>

|                  |             |             |          |            |           | •         |             |             | ,           |            |

|------------------|-------------|-------------|----------|------------|-----------|-----------|-------------|-------------|-------------|------------|

|                  | RC0         | RC0         | RC1      | RC1        | RC2       | RC3       | RC4         | RC4         | RC5         | RC5        |

| CM2CON0          |             |             |          |            |           |           |             |             |             |            |

| C2ON             | 0           | 1           | 0        | 1          |           |           | 0           | 1           |             |            |

| C2PREF1          |             | 0           |          |            | _         |           |             |             | _           |            |

| C2PREF2          | —           | 0           | —        |            | —         | —         | —           | —           | —           | —          |

| C2NREF           | —           | —           | —        | 0          | —         | —         | —           | —           | —           | —          |

| C2OUTEN          |             | —           | _        | _          | _         | _         | _           | 1           | _           |            |

| VRCON0           |             |             | •        |            |           |           |             |             |             |            |

| VROE             |             |             |          |            | 0         |           |             |             | _           |            |

| OPTION           | •           | -           | •        | •          |           |           |             |             |             |            |

| TOCS             | —           | —           | —        |            | _         | —         | _           | —           | 0           | —          |

| Note 1: Multiple | column entr | ies for a r | in demon | strata tha | different | normutati | one to arri | ve at digit | al function | nality for |

**Note 1:** Multiple column entries for a pin demonstrate the different permutations to arrive at digital functionality for the pin.

2: Shaded cells indicate the bit status does not affect the pins digital functionality.

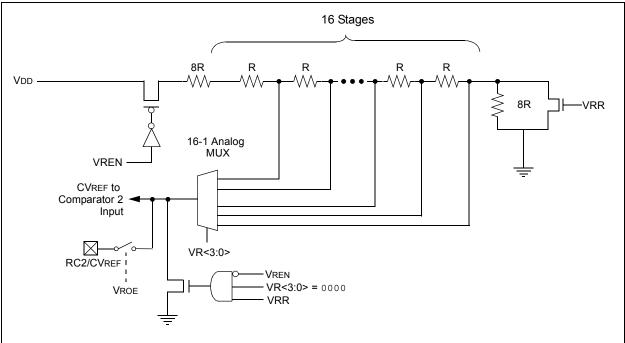

### FIGURE 8-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

### TABLE 8-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Add | Name                   | Bit 7 | Bit 6   | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1   | Bit 0 | Value on<br>POR | Value on all other Resets |

|-----|------------------------|-------|---------|-------|---------|-------|--------|---------|-------|-----------------|---------------------------|

| 0Ch | VRCON                  | VREN  | VROE    | VRR   | _       | VR3   | VR2    | VR1     | VR0   | 001- 1111       | 001- 1111                 |

| 08h | CM1CON0 <sup>(1)</sup> | C10UT | C10UTEN | C1POL | C1T0CS  | C10N  | C1NREF | C1PREF  | C1WU  | 1111 1111       | uuuu uuuu                 |

| 0Bh | CM2CON0 <sup>(1)</sup> | C2OUT | C2OUTEN | C2POL | C2PREF2 | C2ON  | C2NREF | C2PREF1 | C2WU  | 1111 1111       | uuuu uuuu                 |

$\label{eq:Legend: Legend: Legend: u = unchanged, - = unimplemented, read as `0`.$

Note 1: PIC16F506 only.

Γ

## REGISTER 10-1: CONFIG: CONFIGURATION WORD REGISTER (PIC12F510)<sup>(1)</sup>

| —      | _ |  | _ | _ | — | _ | —     |

|--------|---|--|---|---|---|---|-------|

| bit 15 |   |  |   |   |   |   | bit 8 |

|          |                               |                         | T            | r <u>—</u>       | r          | Т     | 1     |

|----------|-------------------------------|-------------------------|--------------|------------------|------------|-------|-------|

| —        |                               | IOSCFS                  | MCLRE        | CP               | WDTE       | FOSC1 | FOSC0 |

| bit 7    |                               |                         |              |                  |            |       | bit 0 |

|          |                               |                         |              |                  |            |       |       |

| bit 15-6 | Unimplement                   | t <b>ed</b> : Read as ' | 1'           |                  |            |       |       |

| bit 5    | IOSCFS: Inter                 | rnal Oscillator         | Frequency Se | elect bit        |            |       |       |

|          | 1 = 8 MHz IN                  | •                       |              |                  |            |       |       |

|          | 0 = 4 MHz IN                  | FOSC speed              |              |                  |            |       |       |

| bit 4    | MCLRE: Mast                   | ter Clear Enab          | le bit       |                  |            |       |       |

|          | 1 = GP3/MCL                   |                         |              |                  |            |       |       |

|          | 0 = GP3/MCL                   | •                       | s as GP3, MC | LR internally ti | ied to VDD |       |       |

| bit 3    | CP: Code Pro                  | tection bit             |              |                  |            |       |       |

|          | 1 = Code prot                 |                         |              |                  |            |       |       |

|          | 0 = Code prot                 | ection on               |              |                  |            |       |       |

| bit 2    | WDTE: Watch                   | ndog Timer En           | able bit     |                  |            |       |       |

|          | 1 = WDT enat                  |                         |              |                  |            |       |       |

|          | 0 = WDT disa                  |                         |              |                  |            |       |       |

| bit 1-0  | FOSC<1:0>: (                  | Oscillator Sele         | ction bits   |                  |            |       |       |

|          | 00 = LP oscilla               |                         |              |                  |            |       |       |

|          | 01 = XT oscill<br>10 = INTOSC |                         |              |                  |            |       |       |

|          | 10 = INTOSC<br>11 = EXTRC \   |                         |              |                  |            |       |       |

|          |                               | mur 1.120 IIIS          |              |                  |            |       |       |

- **Note 1:** Refer to the "*PIC12F510 Memory Programming Specification*" (DS41257) to determine how to access the Configuration Word.

- 2: It is the responsibility of the application designer to ensure the use of the 1.125 ms (nominal) DRT will result in acceptable operation. Refer to Electrical Specifications for VDD rise time and stability requirements for this mode of operation.

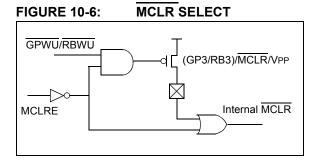

### 10.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external MCLR function. When programmed, the MCLR function is tied to the internal VDD and the pin is assigned to be a I/O. See Figure 10-6.

### 10.4 Power-on Reset (POR)

The PIC12F510/16F506 devices incorporate an onchip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. The POR is active regardless of the state of the MCLR enable bit. An internal weak pull-up resistor is implemented using a transistor (refer to Table 13-3 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create an external Power-on Reset. A maximum rise time for VDD is specified. See **Section 13.0 "Electrical Characteristics"** for details.

When the devices start normal operation (exit the Reset condition), device operating parameters (volt-age, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 10-7.

The Power-on Reset circuit and the Device Reset Timer (see Section 10.5 "Device Reset Timer (DRT)") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR, internal or external, to be high. After the time-out period, it will reset the Reset latch and thus end the on-chip Reset signal.

A power-up example where  $\overline{\text{MCLR}}$  is held low is shown in Figure 10-8. VDD is allowed to rise and stabilize before bringing  $\overline{\text{MCLR}}$  high. The chip will actually come out of Reset TDRT msec after  $\overline{\text{MCLR}}$  goes high.

In Figure 10-9, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be (GP3/RB3). The VDD is stable before the Start-up timer times out and there is no problem in getting a proper Reset. However, Figure 10-10 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 10-9).

| Note: | When the devices start normal operation (exit the Reset condition), device operat- |

|-------|------------------------------------------------------------------------------------|

|       | ing parameters (voltage, frequency,                                                |

|       | temperature, etc.) must be met to ensure                                           |

|       | operation. If these conditions are not met,                                        |

|       | the device must be held in Reset until the                                         |

|       | operating conditions are met.                                                      |

For additional information, refer to Application Notes AN522, *"Power-Up Considerations"* (DS00522) and AN607, *"Power-up Trouble Shooting"* (DS00607).

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label ] SLEEP                                                                                                                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \mbox{ prescaler}; \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                                                                    |

| Status Affected: | TO, PD, RBWUF                                                                                                                                                                                                                                                                                                 |

| Description:     | Time-out Status bit (TO) is set. The<br>Power-down Status bit (PD) is<br>cleared.<br>RBWUF is unaffected.<br>The WDT and its prescaler are<br>cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped.<br>See Section 10.9 "Power-Down<br>Mode (Sleep)" on Sleep for more<br>details. |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                         |

| Operation:       | See description below                                                                                                                                                                                                |

| Status Affected: | С                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'. |

| SUBWF            | Subtract W from f                                                                                                                                                                               |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                      |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                    |  |  |

| Operation:       | $(f) - (W) \rightarrow (dest)$                                                                                                                                                                  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                        |  |  |

| Description:     | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'<br>is '0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                          |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

|                  | C register 'f                                                                                                                                                                                                         |

| SWAPF            | Swap Nibbles in f                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                   |

| Operation:       | (f<3:0>) → (dest<7:4>);<br>(f<7:4>) → (dest<3:0>)                                                                                                                              |

| Status Affected: | None                                                                                                                                                                           |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>'0', the result is placed in W<br>register. If 'd' is '1', the result is<br>placed in register 'f'. |

### 12.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

### 12.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 12.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

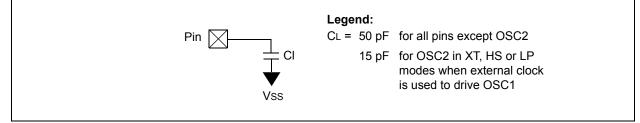

### 13.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

| 2. TppS |                                  |        |                |

|---------|----------------------------------|--------|----------------|

| Т       |                                  |        |                |

| F F     | requency                         | T Time | e              |

| Lower   | case (pp) and their meanings:    |        |                |

| рр      |                                  |        |                |

| 2       | То                               | mc     | MCLR           |

| ck      | CLKOUT                           | osc    | Oscillator     |

| су      | Cycle Time                       | os     | OSC1           |

| drt     | Device Reset Timer               | tO     | ТОСКІ          |

| io      | I/O port                         | wdt    | Watchdog Timer |

| Uppero  | case letters and their meanings: |        |                |

| S       |                                  |        |                |

| F       | Fall                             | Р      | Period         |

| н       | High                             | R      | Rise           |

| I       | Invalid (high-impedance)         | V      | Valid          |

| L       | Low                              | Z      | High-impedance |

### FIGURE 13-5: LOAD CONDITIONS

### FIGURE 13-6: EXTERNAL CLOCK TIMING

NOTES:

NOTES:

### INDEX

| Α               |    |

|-----------------|----|

| ALU             | 9  |

| Assembler       |    |

| MPASM Assembler | 80 |

### В

| Block Diagram                |    |

|------------------------------|----|

| Comparator for the PIC12F510 |    |

| Comparator for the PIC16F506 |    |

| On-Chip Reset Circuit        | 64 |

| Timer0                       |    |

| TMR0/WDT Prescaler           |    |

| Watchdog Timer               | 67 |

| Brown-Out Protection Circuit | 68 |

### С

| C Compilers                          |        |

|--------------------------------------|--------|

| MPLAB C18                            | 80     |

| MPLAB C30                            | 80     |

| Carry                                | 9      |

| Clocking Scheme                      |        |

| Code Protection                      | 55, 69 |

| Configuration Bits                   |        |

| Configuration Word (PIC12F510)       |        |

| Configuration Word (PIC16F506)       |        |

| Customer Change Notification Service |        |

| Customer Notification Service        | 108    |

| Customer Support                     | 108    |

## D

| DC                                        | 88 |

|-------------------------------------------|----|

| DC Characteristics (Extended)             | 87 |

| DC Characteristics (Industrial)           | 86 |

| DC Characteristics (Industrial, Extended) | 88 |

| Development Support                       | 79 |

| Digit Carry                               | 9  |

|                                           |    |

### Ε

| rata3 |

|-------|

| ala   |

## F

Family of Devices PIC12F510/16F506......5 FSR.......24

### I

| I/O Interfacing                |        |

|--------------------------------|--------|

| I/O Ports                      |        |

| I/O Programming Considerations |        |

| ID Locations                   | 55, 69 |

| INDF                           |        |

| Indirect Data Addressing       |        |

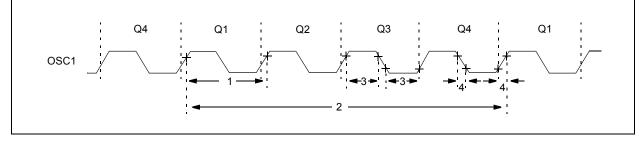

| Instruction Cycle              | 14     |

| Instruction Flow/Pipelining    |        |

| Instruction Set Summary        | 72     |

| Internet Address               | 108    |

| L                              |        |

| Loading of PC                  |        |

## Μ

| Memory Organization 15                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Memory 16                                                                                                                                                                                                                                              |

| Program Memory (PIC12F510/16F506) 15                                                                                                                                                                                                                        |

| Microchip Internet Web Site 108                                                                                                                                                                                                                             |

| MPLAB ASM30 Assembler, Linker, Librarian 80                                                                                                                                                                                                                 |

| MPLAB ICD 2 In-Circuit Debugger 81                                                                                                                                                                                                                          |

| MPLAB ICE 2000 High-Performance Universal                                                                                                                                                                                                                   |

| In-Circuit Emulator                                                                                                                                                                                                                                         |

| MPLAB ICE 4000 High-Performance Universal                                                                                                                                                                                                                   |

| In-Circuit Emulator 81                                                                                                                                                                                                                                      |

| MPLAB Integrated Development Environment Software 79                                                                                                                                                                                                        |

| MPLAB PM3 Device Programmer 81                                                                                                                                                                                                                              |

| MPLINK Object Linker/MPLIB Object Librarian 80                                                                                                                                                                                                              |

| 0                                                                                                                                                                                                                                                           |

| -                                                                                                                                                                                                                                                           |

| OPTION Register                                                                                                                                                                                                                                             |

| OSC Selection                                                                                                                                                                                                                                               |

| OSCCAL Register                                                                                                                                                                                                                                             |

| Oscillator Configurations 58                                                                                                                                                                                                                                |

| Oscillator Types                                                                                                                                                                                                                                            |

| HS58                                                                                                                                                                                                                                                        |

| LP 58                                                                                                                                                                                                                                                       |

| RC                                                                                                                                                                                                                                                          |

| XT58                                                                                                                                                                                                                                                        |

| Р                                                                                                                                                                                                                                                           |

| -                                                                                                                                                                                                                                                           |

| PIC12F510/16F506 Device Varieties7                                                                                                                                                                                                                          |

| PICSTART Plus Development Programmer 82                                                                                                                                                                                                                     |

| POR                                                                                                                                                                                                                                                         |

| Device Reset Timer (DRT) 55, 66                                                                                                                                                                                                                             |

| PD                                                                                                                                                                                                                                                          |

| Power-on Reset (POR)55                                                                                                                                                                                                                                      |

| TO                                                                                                                                                                                                                                                          |

| PORTB                                                                                                                                                                                                                                                       |

| Power-down Mode                                                                                                                                                                                                                                             |

| Prescaler                                                                                                                                                                                                                                                   |

| Program Counter                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                             |