#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 38 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VFDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (2x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f510t-i-mc |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device    | Program Memory | Data Memory  | I/O | Timers |

|-----------|----------------|--------------|-----|--------|

| Device    | Flash (words)  | SRAM (bytes) | 1/0 | 8-bit  |

| PIC16F506 | 1024           | 67           | 12  | 1      |

| PIC12F510 | 1024           | 38           | 6   | 1      |

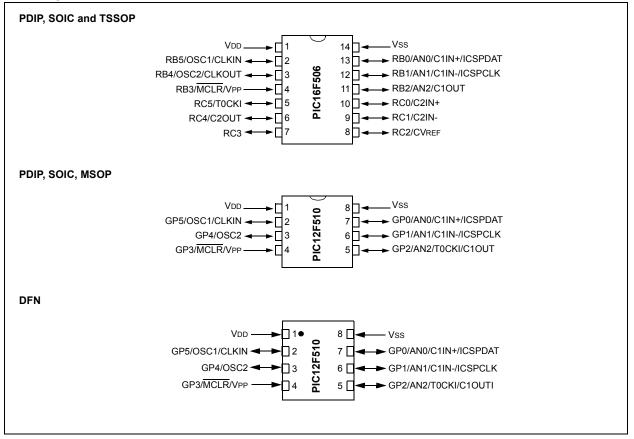

### **Pin Diagrams**

NOTES:

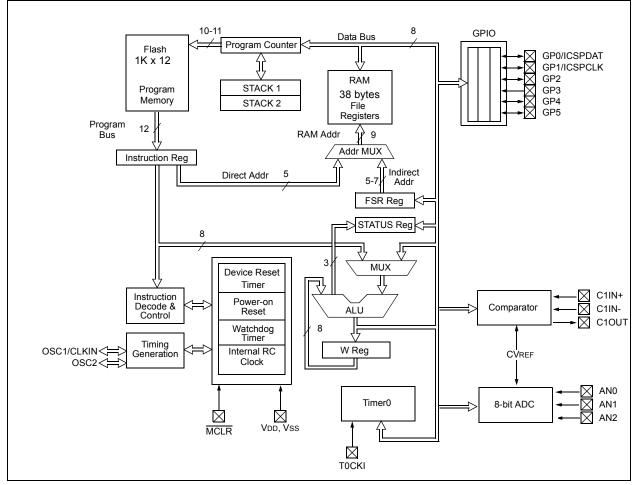

## 1.0 GENERAL DESCRIPTION

The PIC12F510/16F506 devices from Microchip Technology are low-cost, high-performance, 8-bit, fullystatic, Flash-based CMOS microcontrollers. They employ a RISC architecture with only 33 single-word/ single-cycle instructions. All instructions are singlecycle except for program branches, which take two cycles. The PIC12F510/16F506 devices deliver performance in an order of magnitude higher than their competitors in the same price category. The 12-bit wide instructions are highly symmetrical, resulting in a typical 2:1 code compression over other 8-bit microcontrollers in its class. The easy-to-use and easyto-remember instruction set reduces development time significantly.

The PIC12F510/16F506 products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external Reset circuitry. There are four oscillator configurations to choose from (six on the PIC16F506), including INTOSC Internal Oscillator mode and the Power-Saving LP (Low-power) Oscillator mode. Power-Saving Sleep mode, Watchdog Timer and code protection features improve system cost, power and reliability.

The PIC12F510/16F506 devices allow the customer to take full advantage of Microchip's price leadership in Flash programmable microcontrollers, while benefiting from the Flash programmable flexibility.

The PIC12F510/16F506 products are supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a 'C' compiler, a low-cost development programmer and a full featured programmer. All the tools are supported on  $IBM^{\textcircled{R}}$  PC and compatible machines.

## 1.1 Applications

The PIC12F510/16F506 devices fit in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The Flash technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make these microcontrollers perfect for applications with space limitations. Low-cost, low-power, high-performance, ease-of-use and I/O flexibility make the PIC12F510/16F506 devices very versatile, even in areas where no microcontroller use has been considered before (e.g., timer functions, logic and PLDs in larger systems and coprocessor applications).

|             |                                      | PIC16F506                   | PIC12F510                      |

|-------------|--------------------------------------|-----------------------------|--------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                          | 8                              |

| Memory      | Flash Program Memory (words)         | 1024                        | 1024                           |

|             | Data Memory (bytes)                  | 67                          | 38                             |

| Peripherals | Timer Module(s)                      | TMR0                        | TMR0                           |

|             | Wake-up from Sleep on Pin Change     | Yes                         | Yes                            |

| Features    | I/O Pins                             | 11                          | 5                              |

|             | Input Only Pin                       | 1                           | 1                              |

|             | Internal Pull-ups                    | Yes                         | Yes                            |

|             | In-Circuit Serial Programming        | Yes                         | Yes                            |

|             | Number of Instructions               | 33                          | 33                             |

|             | Packages                             | 14-pin PDIP, SOIC,<br>TSSOP | 8-pin PDIP, SOIC, MSOP,<br>DFN |

#### TABLE 1-1: PIC12F510/16F506 DEVICES

The PIC12F510/16F506 devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect, high I/O current capability and precision internal oscillator.

The PIC12F510/16F506 devices use serial programming with data pin RB0/GP0 and clock pin RB1/GP1.

| IABLE 3-2:     PIN DESCRIPTIONS - PIC12F510 |            |            |                |                                                                                                                            |  |

|---------------------------------------------|------------|------------|----------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Name                                        | I/O/P Type | Input Type | Output<br>Type | Description                                                                                                                |  |

| GP0/AN0/C1IN+/ICSPDAT                       | GP0        | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |  |

|                                             | AN0        | AN         | —              | ADC channel input.                                                                                                         |  |

|                                             | C1IN+      | AN         | —              | Comparator input.                                                                                                          |  |

|                                             | ICSPDAT    | ST         | CMOS           | In-Circuit Serial Programming data pin.                                                                                    |  |

| GP1/AN1/C1IN-/ICSPCLK                       | GP1        | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |  |

|                                             | AN1        | AN         | —              | ADC channel input.                                                                                                         |  |

|                                             | C1IN-      | AN         | —              | Comparator input.                                                                                                          |  |

|                                             | ICSPCLK    | ST         | —              | In-Circuit Serial Programming clock pin.                                                                                   |  |

| GP2/AN2/T0CKI/C1OUT                         | GP2        | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |  |

|                                             | AN2        | AN         | —              | ADC channel input.                                                                                                         |  |

|                                             | TOCKI      | ST         | —              | Timer0 clock input.                                                                                                        |  |

|                                             | C10UT      | _          | CMOS           | Comparator output.                                                                                                         |  |

| GP3/MCLR/Vpp                                | GP3        | TTL        | —              | Standard TTL input. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change.     |  |

|                                             | MCLR       | ST         | —              | MCLR input – weak pull-up always enabled in this mode.                                                                     |  |

|                                             | Vpp        | HV         | —              | Programming Voltage input.                                                                                                 |  |

| GP4/OSC2                                    | GP4        | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |  |

|                                             | OSC2       | —          | XTAL           | XTAL oscillator output pin.                                                                                                |  |

| GP5/OSC1/CLKIN                              | GP5        | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |  |

|                                             | OSC1       | XTAL       | —              | XTAL oscillator input pin.                                                                                                 |  |

|                                             | CLKIN      | ST         |                | EXTRC Schmitt Trigger input.                                                                                               |  |

| Vdd                                         | Vdd        | Р          | _              | Positive supply for logic and I/O pins.                                                                                    |  |

| Vss                                         | Vss        | Р          | _              | Ground reference for logic and I/O pins.                                                                                   |  |

TABLE 3-2: PIN DESCRIPTIONS – PIC12F510

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input, AN = Analog Voltage, HV = High Voltage

| Name                  | Function | Input Type | Output<br>Type | Description                                                                                                                |

|-----------------------|----------|------------|----------------|----------------------------------------------------------------------------------------------------------------------------|

| RB0/AN0/C1IN+/ICSPDAT | RB0      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | AN0      | AN         | —              | ADC channel input.                                                                                                         |

|                       | C1IN+    | AN         | —              | Comparator 1 input.                                                                                                        |

|                       | ICSPDAT  | ST         | CMOS           | In-Circuit Serial Programming data pin.                                                                                    |

| RB1/AN1/C1IN-/ICSPCLK | RB1      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | AN1      | AN         |                | ADC channel input.                                                                                                         |

|                       | C1IN-    | AN         |                | Comparator 1 input.                                                                                                        |

|                       | ICSPCLK  | ST         | _              | In-Circuit Serial Programming clock pin.                                                                                   |

| RB2/AN2/C1OUT         | RB2      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | AN2      | AN         |                | ADC channel input.                                                                                                         |

|                       | C10UT    | _          | CMOS           | Comparator 1 output.                                                                                                       |

| RB3/MCLR/Vpp          | RB3      | TTL        | _              | Standard TTL input. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.             |

|                       | MCLR     | ST         | —              | MCLR input – weak pull-up always enabled in this mode.                                                                     |

|                       | Vpp      | HV         |                | Programming voltage input.                                                                                                 |

| RB4/OSC2/CLKOUT       | RB4      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | OSC2     | _          | XTAL           | XTAL oscillator output pin.                                                                                                |

|                       | CLKOUT   |            | CMOS           | EXTRC/INTOSC CLKOUT pin (Fosc/4).                                                                                          |

| RB5/OSC1/CLKIN        | RB5      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | OSC1     | XTAL       | _              | XTAL oscillator input pin.                                                                                                 |

|                       | CLKIN    | ST         | _              | EXTRC/EC Schmitt Trigger input.                                                                                            |

| RC0/C2IN+             | RC0      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2IN+    | AN         | _              | Comparator 2 input.                                                                                                        |

| RC1/C2IN-             | RC1      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2IN-    | AN         | _              | Comparator 2 input.                                                                                                        |

| RC2/CVREF             | RC2      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | CVREF    |            | AN             | Programmable Voltage Reference output.                                                                                     |

| RC3                   | RC3      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

| RC4/C2OUT             | RC4      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2OUT    |            | CMOS           | Comparator 2 output.                                                                                                       |

| RC5/T0CKI             | RC5      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | T0CKI    | ST         | _              | Timer0 clock input.                                                                                                        |

| Vdd                   | Vdd      | Р          |                | Positive supply for logic and I/O pins.                                                                                    |

| Vss                   | Vss      | Р          | _              | Ground reference for logic and I/O pins.                                                                                   |

TABLE 3-3: PIN DESCRIPTIONS – PIC16F506

**Legend:** I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input, AN = Analog Voltage, HV = High Voltage

# 4.5 OSCCAL Register

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal precision 4/8 MHz oscillator. It contains seven bits for calibration.

| Note: | Erasing the device will also erase the pre- |

|-------|---------------------------------------------|

|       | programmed internal calibration value for   |

|       | the internal oscillator. The calibration    |

|       | value must be read prior to erasing the     |

|       | part so it can be reprogrammed correctly    |

|       | later.                                      |

After you move in the calibration constant, do not change the value. See Section 10.2.5 "Internal 4/8 MHz RC Oscillator".

#### REGISTER 4-5: OSCCAL: OSCILLATOR CALIBRATION REGISTER

| R/W-1 | U-0   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | —     |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 7-1 | CAL<6:0>: Oscillator Calibration bits |

|---------|---------------------------------------|

|         | 0111111 = Maximum frequency           |

|         | •                                     |

|         | •                                     |

|         | •                                     |

|         | 000001                                |

|         | 0000000 = Center frequency            |

|         | 1111111                               |

|         | •                                     |

|         | •                                     |

|         | •                                     |

|         | 1000000 = Minimum frequency           |

| bit 0   | Unimplemented: Read as '0'            |

## 4.6 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

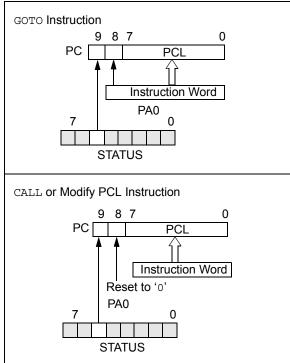

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The Program Counter (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4-4).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-4).

Instructions where the PCL is the destination or modify PCL instructions include MOVWF PC, ADDWF PC and BSF PC, 5.

Note: Because PC<8> is cleared in the CALL instruction or any modify PCL instruction, all subroutine calls or computed jumps are limited to the first 256 locations of any program memory page (512 words long).

### FIGURE 4-4: LOADING OF PC BRANCH INSTRUCTIONS

## 4.6.1 EFFECTS OF RESET

The PC is set upon a Reset, which means that the PC addresses the last location in the last page (i.e., the oscillator calibration instruction). After executing MOVLW XX, the PC will roll over to location 00h and begin executing user code.

The STATUS register page preselect bits are cleared upon a Reset, which means that page 0 is preselected.

Therefore, upon a Reset, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

# 4.7 Stack

The PIC12F510/16F506 devices have a two-deep, 12-bit wide hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of Stack 1 into Stack 2 and then PUSH the current PC value, incremented by one, into Stack Level 1. If more than two sequential CALLs are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of Stack Level 1 into the PC and then copy Stack Level 2 contents into Stack Level 1. If more than two sequential RETLWS are executed, the stack will be filled with the address previously stored in Stack Level 2.

- **Note 1:** The W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

- 2: There are no Status bits to indicate stack overflows or stack underflow conditions.

- 3: There are no instruction mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL and RETLW instructions.

#### 10.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- · WDT Time-out Reset during normal operation

- · WDT Time-out Reset during Sleep

- Wake-up from Sleep Reset on pin change

- Wake-up from Sleep Reset on comparator change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up from Sleep Reset on pin change or wake-up from Sleep Reset on comparator change. The exceptions are TO, PD, CWUF and RBWUF/GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 10-4 for a full description of Reset states of all registers.

| Register | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change, Wake-up on<br>Comparator Change |

|----------|---------|--------------------------|-------------------------------------------------------------------------------------|

| W        | —       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                                                            |

| INDF     | 00h     | xxxx xxxx                | <u>uuuu</u> uuuu                                                                    |

| TMR0     | 01h     | xxxx xxxx                | uuuu uuuu                                                                           |

| PCL      | 02h     | 1111 1111                | 1111 1111                                                                           |

| STATUS   | 03h     | 0001 1xxx                | qq0q quuu <sup>(2)</sup>                                                            |

| FSR      | 04h     | 110x xxxx                | 11uu uuuu                                                                           |

| OSCCAL   | 05h     | 1111 111-                | uuuu uuu-                                                                           |

| GPIO     | 06h     | xx xxxx                  | uu uuuu                                                                             |

| CM1CON0  | 07h     | 1111 1111                | uuuu uuuu                                                                           |

| ADCON0   | 08h     | 1111 1100                | uull 1100                                                                           |

| ADRES    | 09h     | xxxx xxxx                | uuuu uuuu                                                                           |

| OPTION   |         | 1111 1111                | 1111 1111                                                                           |

| TRISIO   |         | 11 1111                  | 11 1111                                                                             |

#### TABLE 10-3: RESET CONDITIONS FOR REGISTERS – PIC12F510

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 10-5 for Reset value for specific conditions.

#### 10.12 In-Circuit Serial Programming™ (ICSP™)

The PIC12F510/16F506 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the GP1/RB1 and GP0/RB0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1/RB1 becomes the programming clock and GP0/RB0 becomes the programming data. Both GP1/RB1 and GP0/RB0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is supplied to the device. Depending on the command and if the command was a Load or a Read, 14 bits of program data are then supplied to or from the device. For complete details of serial programming, please refer to the PIC12F510/16F506 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 10-15.

#### FIGURE 10-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                        |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is skipped.<br>If bit 'b' is '1', then the next instruction fetched during the current instruction execution, is discarded and a NOP is executed instead, making this a two-cycle instruction. |

| CLRW             | Clear W                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                           |

| Operands:        | None                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The W register is cleared. Zero bit (Z) is set.                        |

| CALL             | Subroutine Call                                                                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                                                                                                     |

| Operation:       | $(PC) + 1 \rightarrow$ Top-of-Stack;<br>k $\rightarrow$ PC<7:0>;<br>(STATUS <6:5>) $\rightarrow$ PC<10:9>;<br>0 $\rightarrow$ PC<8>                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                  |

| Description:     | Subroutine call. First, return<br>address (PC + 1) is PUSHed onto<br>the stack. The eight-bit immediate<br>address is loaded into PC<br>bits <7:0>. The upper bits<br>PC<10:9> are loaded from<br>STATUS <6:5>, PC<8> is cleared.<br>CALL is a two-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRWDT                                                                                                                                                                                                  |

| Operands:        | None                                                                                                                                                                                                                     |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT;} \\ 0 \rightarrow \underline{\text{WDT}} \text{ prescaler (if assigned);} \\ 1 \rightarrow \underline{\text{TO};} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                                                                   |

| Description:     | The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits $\overline{TO}$ and $\overline{PD}$ are set.                                    |

| CLRF             | Clear f                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [label]CLRF f                                                          |

| Operands:        | $0 \leq f \leq 31$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.         |

| COMF             | Complement f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                |

| Operation:       | $(\overline{f})  ightarrow (dest)$                                                                                                                              |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                |

| Operation:       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                            |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is placed back in register<br>'f'. |

| MOVWF            | Move W to f                                    |

|------------------|------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                       |

| Operands:        | $0 \le f \le 31$                               |

| Operation:       | $(W) \rightarrow (f)$                          |

| Status Affected: | None                                           |

| Description:     | Move data from the W register to register 'f'. |

| MOVF             | Move f                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                     |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>moved to destination 'd'. If 'd' is '0',<br>destination is the W register. If 'd'<br>is '1', the destination is file<br>register 'f'. 'd' = 1 is useful as a<br>test of a file register, since Status<br>flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                                    |

| Operands:        | $0 \le k \le 255$                                                                                           |

| Operation:       | $k \rightarrow (W)$                                                                                         |

| Status Affected: | None                                                                                                        |

| Description:     | The eight-bit literal 'k' is loaded<br>into the W register. The "don't<br>cares" will be assembled as '0's. |

| OPTION           | Load OPTION Register                                              |

|------------------|-------------------------------------------------------------------|

| Syntax:          | [ label ] Option                                                  |

| Operands:        | None                                                              |

| Operation:       | $(W) \rightarrow Option$                                          |

| Status Affected: | None                                                              |

| Description:     | The content of the W register is loaded into the OPTION register. |

| TRIS             | Load TRIS Register                                                                 |

|------------------|------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                            |

| Operands:        | f = 6                                                                              |

| Operation:       | $(W) \to TRIS \text{ register f}$                                                  |

| Status Affected: | None                                                                               |

| Description:     | TRIS register 'f' (f = 6 or 7) is<br>loaded with the contents of the W<br>register |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                              |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                       |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                          |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |  |  |  |  |  |

| Status Affected: | Z                                                                                                                 |  |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

#### 12.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

### 12.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 12.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

#### TABLE 13-1: COMPARATOR SPECIFICATIONS

| Sym   | Characteristics              | Min   | Тур | Max       | Units | Comments       |

|-------|------------------------------|-------|-----|-----------|-------|----------------|

| Vos   | Input Offset Voltage         | —     | ±3  | ±10       | mV    | (Vdd - 1.5V)/2 |

| Vсм   | Input Common Mode Voltage    | 0     | _   | Vdd - 1.5 | V     |                |

| CMRR  | Common Mode Rejection Ratio  | +55*  | _   | —         | dB    |                |

| TRT   | Response Time <sup>(1)</sup> | —     | 150 | 400*      | ns    | Internal       |

| VIVRF | Internal Voltage Reference   | 0.550 | 0.6 | 0.650     | V     |                |

These parameters are characterized but not tested. \*

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD - 1.5V.

#### TABLE 13-2: COMPARATOR VOLTAGE REFERENCE (CVREF) SPECIFICATIONS

| Sym                                                  | Characteristics              | Min | Тур     | Max   | Units | Comments             |  |

|------------------------------------------------------|------------------------------|-----|---------|-------|-------|----------------------|--|

| CVRES                                                | Resolution                   | _   | VDD/24* | _     | LSb   | Low Range (VRR = 1)  |  |

|                                                      |                              | —   | VDD/32  | —     | LSb   | High Range (VRR = 0) |  |

|                                                      | Absolute Accuracy            | _   |         | ±1/2* | LSb   | Low Range (VRR = 1)  |  |

|                                                      |                              | —   |         | ±1/2* | LSb   | High Range (VRR = 0) |  |

|                                                      | Unit Resistor Value (R)      | _   | 2K*     | _     | Ω     |                      |  |

|                                                      |                              | —   |         |       |       |                      |  |

|                                                      | Settling Time <sup>(1)</sup> | _   |         | 10*   | μs    |                      |  |

| * These parameters are characterized but not tested. |                              |     |         |       |       |                      |  |

These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

#### TABLE 13-3: A/D CONVERTER CHARACTERISTICS (PIC16F506/PIC12F510)

| Param<br>No. | Sym  | Characteristic                                    | Min  | Тур†                      | Мах            | Units | Conditions                               |

|--------------|------|---------------------------------------------------|------|---------------------------|----------------|-------|------------------------------------------|

| A01          | Nr   | Resolution                                        |      |                           | 8 bits         | bit   |                                          |

| A03          | EIL  | Integral Error                                    | _    | —                         | ± 1.5          | LSb   | VDD = 5.0V                               |

| A04          | Edl  | Differential Error                                | _    | —                         | -1 < EDL ≤ 1.5 | LSb   | No missing codes to<br>8 bits VDD = 5.0V |

| A05          | EFS  | Full-scale Range                                  | 2    | —                         | 5.5*           | V     | Vdd                                      |

| A06          | EOFF | Offset Error                                      | _    | —                         | ± 1.5          | LSb   | VDD = 5.0V                               |

| A07          | Egn  | Gain Error                                        | -0.5 | —                         | +1.75          | LSb   | VDD = 5.0V                               |

| A10          |      | Monotonicity                                      | _    | guaranteed <sup>(1)</sup> | _              |       | $Vss \leq Vain \leq Vdd$                 |

| A25          | VAIN | Analog Input Voltage                              | Vss  | —                         | Vdd            | V     |                                          |

| A30          | Zain | Recommended Impedance<br>of Analog Voltage Source | _    | —                         | 10             | kΩ    |                                          |

These parameters are characterized but not tested.

† Data in the "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only are not tested.

Note 1: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

## 15.2 Package Marking Information (Cont'd)

14-Lead SOIC (3.90 mm)

8-Lead MSOP

14-Lead TSSOP (4.4 mm)

Example

Example

Example

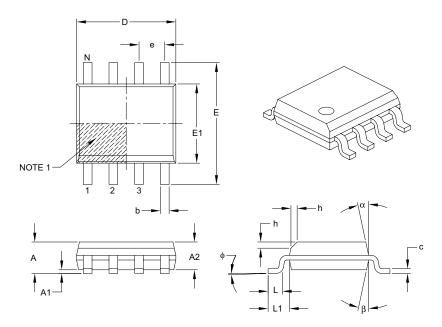

### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        | MILLIMETERS |          |      |  |  |

|--------------------------|--------------|-------------|----------|------|--|--|

| Dime                     | nsion Limits | MIN         | MAX      |      |  |  |

| Number of Pins           | N            | 8           |          |      |  |  |

| Pitch                    | е            |             | 1.27 BSC |      |  |  |

| Overall Height           | A            | -           | -        | 1.75 |  |  |

| Molded Package Thickness | A2           | 1.25 – –    |          |      |  |  |

| Standoff §               | A1           | 0.10 – 0.25 |          |      |  |  |

| Overall Width            | E            | 6.00 BSC    |          |      |  |  |

| Molded Package Width     | E1           | 3.90 BSC    |          |      |  |  |

| Overall Length           | D            | 4.90 BSC    |          |      |  |  |

| Chamfer (optional)       | h            | 0.25 – 0.50 |          |      |  |  |

| Foot Length              | L            | 0.40 – 1.27 |          |      |  |  |

| Footprint                | L1           | 1.04 REF    |          |      |  |  |

| Foot Angle               | ¢            | 0° – 8°     |          |      |  |  |

| Lead Thickness           | С            | 0.17 – 0.25 |          |      |  |  |

| Lead Width               | b            | 0.31 – 0.51 |          |      |  |  |

| Mold Draft Angle Top     | α            | 5° – 15°    |          |      |  |  |

| Mold Draft Angle Bottom  | β            | 5° – 15°    |          |      |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

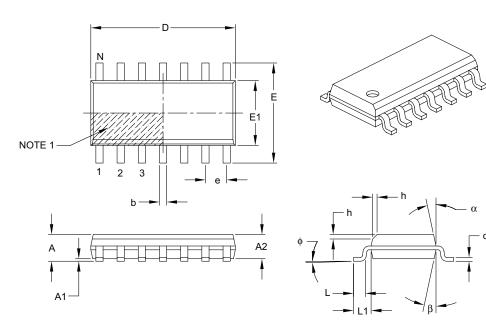

### 14-Lead Plastic Small Outline (SL) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |  |  |

|--------------------------|------------------|-------------|----------|------|--|--|

|                          | Dimension Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins           | N                | 14          |          |      |  |  |

| Pitch                    | e                |             | 1.27 BSC |      |  |  |

| Overall Height           | A                | -           | -        | 1.75 |  |  |

| Molded Package Thickness | A2               | 1.25        | -        | -    |  |  |

| Standoff §               | A1               | 0.10 – 0.25 |          |      |  |  |

| Overall Width            | E                | 6.00 BSC    |          |      |  |  |

| Molded Package Width     | E1               | 3.90 BSC    |          |      |  |  |

| Overall Length           | D                | 8.65 BSC    |          |      |  |  |

| Chamfer (optional)       | h                | 0.25 – 0.50 |          |      |  |  |

| Foot Length              | L                | 0.40        | —        | 1.27 |  |  |

| Footprint                | L1               | 1.04 REF    |          |      |  |  |

| Foot Angle               | φ                | 0°          | -        | 8°   |  |  |

| Lead Thickness           | С                | 0.17 – 0.25 |          |      |  |  |

| Lead Width               | b                | 0.31        | _        | 0.51 |  |  |

| Mold Draft Angle Top     | α                | 5° – 15°    |          |      |  |  |

| Mold Draft Angle Bottom  | β                | 5° – 15°    |          |      |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-065B