Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173°, 4.40mm Width)Supplier Device Package14-TSSOPPurchase URLhttps://www.ex.fl.com/product-detail/microchip-technology/pic16f506-e-st | Details                    |                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size8-BitSpeed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                   | Product Status             | Active                                                                   |

| Speed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                 | Core Processor             | PIC                                                                      |

| Connectivity-PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                           | Core Size                  | 8-Bit                                                                    |

| PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K × 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 × 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                        | Speed                      | 20MHz                                                                    |

| Number of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                           | Connectivity               | -                                                                        |

| Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                          | Peripherals                | POR, WDT                                                                 |

| Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                            | Number of I/O              | 11                                                                       |

| EEPROM Size-RAM Size67 × 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                    | Program Memory Size        | 1.5KB (1K x 12)                                                          |

| RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                | Program Memory Type        | FLASH                                                                    |

| Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                              | EEPROM Size                | -                                                                        |

| Data ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                                                                 | RAM Size                   | 67 x 8                                                                   |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                                                                                        | Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     14-TSSOP (0.173", 4.40mm Width)       Supplier Device Package     14-TSSOP                                                                                                                                                                                                                                                                                                      | Data Converters            | A/D 4x8b                                                                 |

| Mounting Type     Surface Mount       Package / Case     14-TSSOP (0.173", 4.40mm Width)       Supplier Device Package     14-TSSOP                                                                                                                                                                                                                                                                                                                                                         | Oscillator Type            | Internal                                                                 |

| Package / Case     14-TSSOP (0.173", 4.40mm Width)       Supplier Device Package     14-TSSOP                                                                                                                                                                                                                                                                                                                                                                                               | Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Supplier Device Package 14-TSSOP                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Mounting Type              | Surface Mount                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic16f506-e-st                                                                                                                                                                                                                                                                                                                                                                                                       | Supplier Device Package    | 14-TSSOP                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f506-e-st |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Міскоснір PIC12F510/16F506

## 8/14-Pin, 8-Bit Flash Microcontroller

#### **Devices Included In This Data Sheet:**

- PIC16F506

- PIC12F510

#### High-Performance RISC CPU:

- · Only 33 Single-Word Instructions to Learn

- All Single-Cycle Instructions except for Program Branches, which are Two-Cycle

- 12-Bit Wide Instructions

- Two-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- · 8-Bit Wide Data Path

- 10 Special Function Hardware Registers (PIC12F510)

- 13 Special Function Hardware Registers (PIC16F506)

- · Operating Speed:

- DC 8 MHz Crystal Oscillator (PIC12F510)

- DC 500 ns instruction cycle (PIC12F510)

- DC 20 MHz Crystal Oscillator (PIC16F506)

- DC 200 ns instruction cycle (PIC16F506)

#### **Special Microcontroller Features:**

- 4 or 8 MHz Selectable Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debugging (ICD) Support

- Power-on Reset (POR)

- Device Reset Timer (DRT):

- Short DRT (1.125 ms, typical) for INTOSC, EXTRC and EC

- DRT (18 ms, typical) for HS, XT and LP

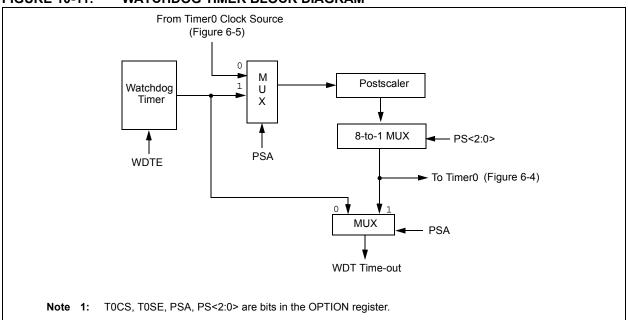

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

- · Selectable Internal Weak Pull-Ups on I/O Pins

- · Power-Saving Sleep mode

- Wake-up from Sleep on Pin Change

- · Wake-up from Sleep on Comparator Change

- · Selectable Oscillator Options:

- INTOSC: 4/8 MHz precision Internal oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- LP: Power-saving, low-frequency crystal

- HS: High-speed crystal/resonator (PIC16F506 only)

- EC: High-speed external clock input (PIC16F506 only)

- Analog-to-Digital (A/D) Converter:

- 8-bit resolution

- 4-input channels (1 channel is dedicated to conversion of the internal 0.6V absolute voltage reference)

- High Current Sink/Source for Direct LED Drive

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

#### Low-Power Features/CMOS Technology:

- Operating Current:

- < 175 μA @ 2V, 4 MHz, typical

- Standby Current:

- 100 nA @ 2V, typical

- · Low-Power, High-Speed Flash Technology:

- 100,000 cycle Flash endurance

- > 40-year retention

- Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V

- Wide Temperature Range:

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

#### Peripheral Features (PIC12F510):

- 6 I/O Pins:

- 5 I/O pins with individual direction control

- 1 input only pin

- 1 Analog Comparator with Absolute Reference

#### Peripheral Features (PIC16F506):

- 12 I/O Pins:

- 11 I/O pins with individual direction control

- 1 input only pin

- 2 Analog Comparators with Absolute Reference and Programmable Reference

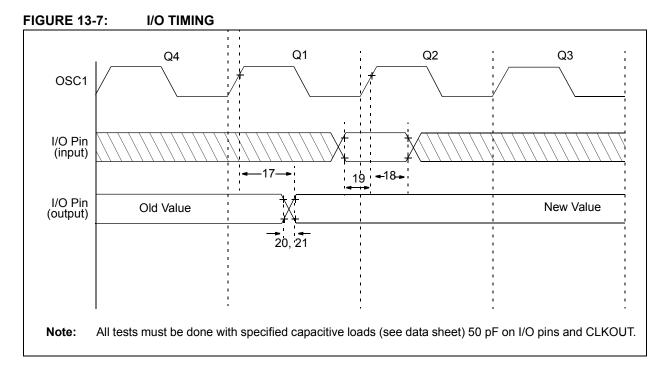

## 3.1 Clocking Scheme/Instruction Cycle

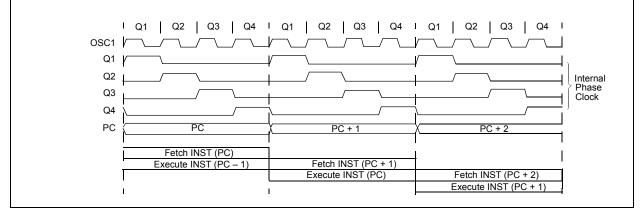

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-3 and Example 3-1.

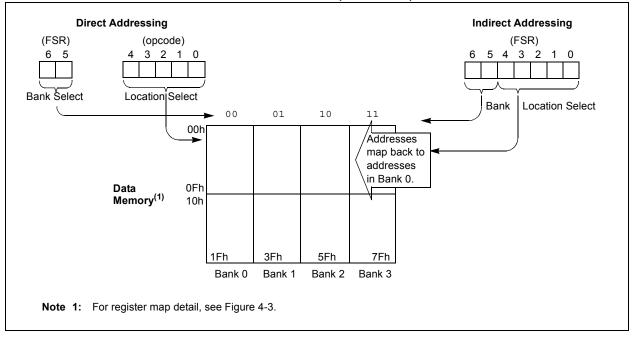

#### 3.2 Instruction Flow/Pipelining

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

#### 4.4 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, that contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<7:0> bits.

- Note 1: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin (i.e., note that TRIS overrides Option control of GPPU/RBPU and GPWU/RBWU).

- **2:** If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

#### REGISTER 4-3: OPTION\_REG: OPTION REGISTER (PIC12F510)

| W-1   | W-1  | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|------|------|------|-----|-----|-----|-------|

| GPWU  | GPPU | TOCS | TOSE | PSA | PS2 | PS1 | PS0   |

| bit 7 |      |      |      |     |     |     | bit 0 |

| Legend:    |                                                                                                            |                                                             |                                                                           |                                    |                    |  |

|------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------|--------------------|--|

| R = Reada  | ble bit W = V                                                                                              | Writable bit                                                | U                                                                         | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value | at POR '1' =                                                                                               | Bit is set                                                  | '0'                                                                       | = Bit is cleared                   | x = Bit is unknown |  |

| bit 7      | <b>GPWU:</b> Enable Wake-u<br>1 = Disabled<br>0 = Enabled                                                  | p On Pin Chang                                              | e bit (GP0, GP                                                            | 1, GP3)                            |                    |  |

| bit 6      | <b>GPPU:</b> Enable Weak Pu<br>1 = Disabled<br>0 = Enabled                                                 | ull-Ups bit (GP0,                                           | GP1, GP3)                                                                 |                                    |                    |  |

| bit 5      | <b>TOCS:</b> Timer0 Clock So<br>1 = Transition on TOCI<br>0 = Internal instruction                         | KI pin                                                      | KOUT)                                                                     |                                    |                    |  |

| bit 4      | <b>T0SE:</b> Timer0 Source E<br>1 = Increment on high<br>0 = Increment on low-1                            | -to-low transition                                          |                                                                           |                                    |                    |  |

| bit 3      | <ul> <li>PSA: Prescaler Assignr</li> <li>1 = Prescaler assigner</li> <li>0 = Prescaler assigner</li> </ul> | d to the WDT                                                |                                                                           |                                    |                    |  |

| bit 2-0    | PS<2:0>: Prescaler Rat                                                                                     | e Select bits                                               |                                                                           |                                    |                    |  |

|            | Bit Value                                                                                                  | Timer0 Rate                                                 | WDT Rate                                                                  |                                    |                    |  |

|            | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                       | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 |                                    |                    |  |

| W-1           | W-1                                                             | W-1                                                                                                                                                                       | W-1                                                            | W-1               | W-1             | W-1             | W-1   |

|---------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------|-----------------|-----------------|-------|

| RBWU          | RBPU                                                            | TOCS                                                                                                                                                                      | TOSE                                                           | PSA               | PS2             | PS1             | PS0   |

| bit 7         |                                                                 |                                                                                                                                                                           |                                                                |                   |                 |                 | bit ( |

|               |                                                                 |                                                                                                                                                                           |                                                                |                   |                 |                 |       |

| Legend:       |                                                                 |                                                                                                                                                                           |                                                                |                   |                 |                 |       |

| R = Readabl   | le bit                                                          | W = Writable                                                                                                                                                              | bit                                                            | U = Unimpler      | nented bit, rea | d as '0'        |       |

| -n = Value at | t POR                                                           | '1' = Bit is set                                                                                                                                                          |                                                                | '0' = Bit is cle  | ared            | x = Bit is unkr | nown  |

| bit 7         | <b>RBWU:</b> Enable V<br>1 = Disabled<br>0 = Enabled            | Vake-up On Pin (                                                                                                                                                          | Change bit (RB0                                                | ), RB1, RB3, RB4) |                 |                 |       |

| bit 6         | <b>RBPU:</b> Enable W<br>1 = Disabled<br>0 = Enabled            | /eak Pull-Ups bit                                                                                                                                                         | (RB0, RB1, RB                                                  | 3, RB4)           |                 |                 |       |

| bit 5         | <b>TOCS:</b> Timer0 CI<br>1 = Transition o<br>0 = Internal inst |                                                                                                                                                                           |                                                                |                   |                 |                 |       |

| bit 4         | <b>TOSE:</b> Timer0 Sc<br>1 = Increment c<br>0 = Increment c    | Ũ                                                                                                                                                                         | nsition on T0CK                                                | •                 |                 |                 |       |

| bit 3         | PSA: Prescaler A<br>1 = Prescaler a<br>0 = Prescaler a          | ssigned to the W                                                                                                                                                          |                                                                |                   |                 |                 |       |

| bit 2-0       | PS<2:0>: Presca                                                 | ler Rate Select b                                                                                                                                                         | its                                                            |                   |                 |                 |       |

|               | Bit V                                                           | alue Timer0                                                                                                                                                               | Rate WDT R                                                     | ate               |                 |                 |       |

|               | 0<br>0<br>0<br>1<br>1<br>1<br>1                                 | D0         1:2           D1         1:4           L0         1:8           L1         1:13           D01         1:30           D11         1:6           L1         1:12 | 1 : 2<br>1 : 4<br>6 1 : 8<br>2 1 : 16<br>4 1 : 32<br>28 1 : 64 |                   |                 |                 |       |

#### REGISTER 4-4: OPTION\_REG: OPTION REGISTER (PIC16F506)

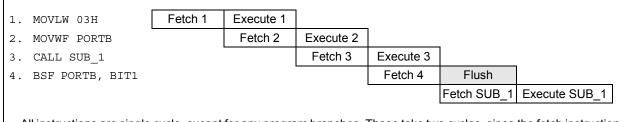

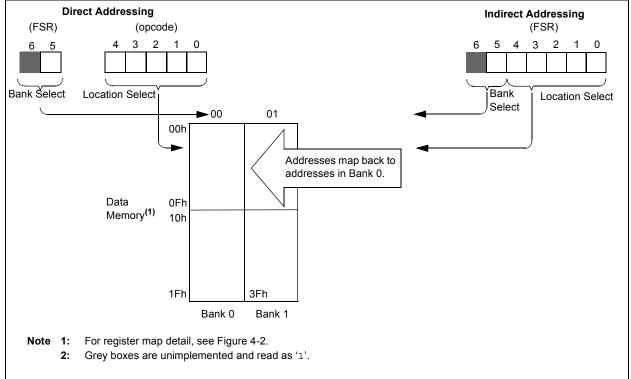

## 4.8 Indirect Data Addressing: INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### 4.8.1 INDIRECT ADDRESSING EXAMPLE

- · Register file 07 contains the value 10h

- · Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-1.

#### EXAMPLE 4-1:

#### -1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT   | MOVLW<br>MOVWF<br>CLRF<br>INCF<br>BTFSC<br>GOTO | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear INDF register<br>;inc pointer<br>;all done?<br>;NO, clear next |

|--------|-------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|

| CONTIN | UE                                              |                                               |                                                                                                         |

|        | :                                               |                                               | ;YES, continue                                                                                          |

|        | :                                               |                                               |                                                                                                         |

|        |                                                 |                                               |                                                                                                         |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16F506** – Uses FSR<6:5>. Selects from Bank 0 to Bank 3. FSR<7> is unimplemented, read as '1'.

**PIC12F510** – Uses FSR<5>. Selects from Bank 0 to Bank 1. FSR<7:6> are unimplemented, read as '11'.

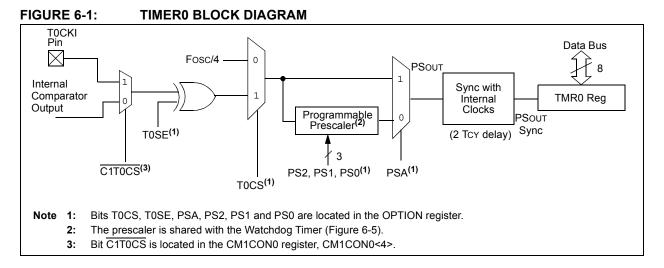

#### 6.0 TMR0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select:

- Edge select for external clock

- External clock from either the T0CKI pin or from the output of the comparator

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

There are two types of Counter mode. The first Counter mode uses the T0CKI pin to increment Timer0. It is selected by setting the T0CKI bit (OPTION<5>), setting the  $\overline{C1T0CS}$  bit (CM1CON0<4>) and setting the  $\overline{C1OUTEN}$  bit (CM1CON0<6>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 With An External Clock".

The second Counter mode uses the output of the comparator to increment Timer0. It can be entered in two different ways. The first way is selected by setting the TOCS bit (OPTION<5>), and clearing the C1TOCS bit (CM1CON0<4>) (C1OUTEN [CM1CON0<6>] does not affect this mode of operation). This enables an internal connection between the comparator and the Timer0.

The second way is selected by setting the T0CS bit (OPTION<5>), setting the C1T0CS bit (CM1CON0) and clearing the C10UTEN bit (CM1CON0<6>). This allows the output of the comparator onto the T0CKI pin, while keeping the T0CKI input active. Therefore, any comparator change on the COUT pin is fed back into the T0CKI input. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input as discussed in Section 6.1 "Using Timer0 With An External Clock".

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 6.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

| R-1        | R/W-1                                                                                                                 | R/W-1                       | R/W-1           | R/W-1                     | R/W-1           | R/W-1           | R/W-1 |

|------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|---------------------------|-----------------|-----------------|-------|

| C10U       | T C1OUTEN                                                                                                             | C1POL                       | C1T0CS          | C10N                      | C1NREF          | C1PREF          | C1WU  |

| bit 7      |                                                                                                                       |                             |                 |                           |                 |                 | bit ( |

|            |                                                                                                                       |                             |                 |                           |                 |                 |       |

| Legend:    |                                                                                                                       |                             |                 |                           |                 |                 |       |

| R = Reada  |                                                                                                                       | W = Writable                |                 |                           | mented bit, rea |                 |       |

| -n = Value | at POR                                                                                                                | '1' = Bit is set            | t               | '0' = Bit is cle          | eared           | x = Bit is unkn | own   |

| bit 7      | C1OUT: Com                                                                                                            | parator Output              | t bit           |                           |                 |                 |       |

|            | 1 = VIN + > VII                                                                                                       | -                           |                 |                           |                 |                 |       |

|            | 0 = VIN + < VII                                                                                                       |                             |                 | (4) (2)                   |                 |                 |       |

| bit 6      |                                                                                                                       | Comparator Ou               |                 |                           |                 |                 |       |

|            |                                                                                                                       | comparator is comparator is |                 |                           | pin             |                 |       |

| bit 5      | •                                                                                                                     | parator Output              | •               | •                         |                 |                 |       |

| DIUD       |                                                                                                                       | comparator is               | •               |                           |                 |                 |       |

|            |                                                                                                                       | comparator is               |                 |                           |                 |                 |       |

| bit 4      | C1T0CS: Cor                                                                                                           | nparator TMR                | Clock Source    | e bit <sup>(2)</sup>      |                 |                 |       |

|            | 1 = TMR0 clo                                                                                                          | ck source sele              | cted by T0CS    | control bit               |                 |                 |       |

|            | 0 = Compara                                                                                                           | tor output used             | d as TMR0 clo   | ck source                 |                 |                 |       |

| bit 3      |                                                                                                                       | arator Enable               | bit             |                           |                 |                 |       |

|            | 1 = Compara                                                                                                           |                             |                 |                           |                 |                 |       |

|            | 0 = Compara                                                                                                           |                             |                 | <b>2 1 1 1 1 (2)</b>      |                 |                 |       |

| bit 2      | 1 = C1IN- pin                                                                                                         | mparator Nega               | ative Reference | e Select bit(-)           |                 |                 |       |

|            | 0 = 0.6V inter                                                                                                        |                             |                 |                           |                 |                 |       |

| bit 1      |                                                                                                                       | mparator Posit              | ive Reference   | Select bit <sup>(2)</sup> |                 |                 |       |

|            | 1 = C1IN+ pin                                                                                                         |                             |                 |                           |                 |                 |       |

|            | 0 = C1IN- pin                                                                                                         |                             |                 |                           |                 |                 |       |

| bit 0      |                                                                                                                       | barator Wake-u              |                 |                           |                 |                 |       |

|            | <ol> <li>= Wake-up On Comparator Change is disabled</li> <li>= Wake-up On Comparator Change is enabled</li> </ol>     |                             |                 |                           |                 |                 |       |

|            | •                                                                                                                     | •                           | •               | nabled                    |                 |                 |       |

| Note 1:    | Overrides T0CS b                                                                                                      |                             |                 |                           |                 |                 |       |

| 2:         | Vhen comparator is turned on, these control bits assert themselves. Otherwise, the other registers hav<br>precedence. |                             |                 |                           |                 |                 |       |

#### REGISTER 7-2: CM1CON0: COMPARATOR C1 CONTROL REGISTER (PIC16F506)

#### 9.1.6 ANALOG CONVERSION RESULT REGISTER

The ADRES register contains the results of the last conversion. These results are present during the sampling period of the next analog conversion process. After the sampling period is over, ADRES is cleared (= 0). A 'leading one' is then right shifted into the ADRES to serve as an internal conversion complete bit. As each bit weight, starting with the MSB, is converted, the leading one is shifted right and the converted bit is stuffed into ADRES. After a total of 9 right

shifts of the 'leading one' have taken place, the conversion is complete; the 'leading one' has been shifted out and the GO/DONE bit is cleared.

If the GO/DONE bit is cleared in software during a conversion, the conversion stops. The data in ADRES is the partial conversion result. This data is valid for the bit weights that have been converted. The position of the 'leading one' determines the number of bits that have been converted. The bits that were not converted before the GO/DONE was cleared are unrecoverable.

#### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER (PIC12F510)

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|---------|-------|

| ANS1  | ANS0  | ADCS1 | ADCS0 | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |       |       |       |       |       |         | bit 0 |

| Legend:            |                                                    |                                                                                                                                                                  |                                                                                                          |                                                                                                                       |  |  |

|--------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| R = Read           | able bit                                           | W = Writable bit                                                                                                                                                 | U = Unimplemented bit                                                                                    | , read as '0'                                                                                                         |  |  |

| -n = Value         | e at POR                                           | '1' = Bit is set                                                                                                                                                 | '0' = Bit is cleared                                                                                     | x = Bit is unknown                                                                                                    |  |  |

| bit 7-6            | 00 = No<br>01 = AN<br>10 = AN                      | <b>0&gt;:</b> ADC Analog Input Pin S<br>pins configured for analog in<br>2 configured as an analog ir<br>2 and AN0 configured as an<br>2, AN1 and AN0 configured | nput<br>iput<br>alog inputs                                                                              |                                                                                                                       |  |  |

| bit 5-4            | ADCS<<br>00 = FO<br>01 = FO<br>10 = FO<br>11 = IN  | sc/8<br>sc/4                                                                                                                                                     | s Select bits                                                                                            |                                                                                                                       |  |  |

| bit 3-2            | 00 = Ch<br>01 = Ch<br>10 = Ch                      | <b>0&gt;:</b> ADC Channel Select bits<br>annel AN0<br>annel AN1<br>annel AN2<br>V absolute voltage reference                                                     |                                                                                                          |                                                                                                                       |  |  |

| bit 1              | 1 = AD0<br>auto<br>0 = AD0                         | omatically cleared by hardwa                                                                                                                                     | Setting this bit starts an Al<br>are when the ADC is done con<br>in progress. Manually clearin           | DC conversion cycle. This bit<br>verting.<br>Ig this bit while a conversion is                                        |  |  |

| bit 0              | 1 = AD0                                            | ADC Enable bit<br>C module is operating<br>C module is shut-off and con                                                                                          | sumes no power                                                                                           |                                                                                                                       |  |  |

| Note 1:<br>2:      | less of the pir<br>input to the co<br>that the ADC | n function previously defined omparator and the ADC will b                                                                                                       | . The only exception to this is<br>be active at the same time. It is<br>nput does not affect their appli | forced into Analog mode, regard-<br>the comparator, where the analog<br>the users responsibility to ensur-<br>cation. |  |  |

| 3:                 |                                                    | s default to 11 after any Res                                                                                                                                    |                                                                                                          |                                                                                                                       |  |  |

| <u></u> <i>A</i> . |                                                    | hit is clear the GO/DONE hit                                                                                                                                     | cannot ha sat                                                                                            |                                                                                                                       |  |  |

4: If the ADON bit is clear, the GO/DONE bit cannot be set.

#### 10.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- · WDT Time-out Reset during normal operation

- · WDT Time-out Reset during Sleep

- Wake-up from Sleep Reset on pin change

- Wake-up from Sleep Reset on comparator change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up from Sleep Reset on pin change or wake-up from Sleep Reset on comparator change. The exceptions are TO, PD, CWUF and RBWUF/GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 10-4 for a full description of Reset states of all registers.

| Register | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change, Wake-up on<br>Comparator Change |

|----------|---------|--------------------------|-------------------------------------------------------------------------------------|

| W        | —       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                                                            |

| INDF     | 00h     | xxxx xxxx                | <u>uuuu</u> uuuu                                                                    |

| TMR0     | 01h     | xxxx xxxx                | uuuu uuuu                                                                           |

| PCL      | 02h     | 1111 1111                | 1111 1111                                                                           |

| STATUS   | 03h     | 0001 1xxx                | qq0q quuu <sup>(2)</sup>                                                            |

| FSR      | 04h     | 110x xxxx                | 11uu uuuu                                                                           |

| OSCCAL   | 05h     | 1111 111-                | uuuu uuu-                                                                           |

| GPIO     | 06h     | xx xxxx                  | uu uuuu                                                                             |

| CM1CON0  | 07h     | 1111 1111                | uuuu uuuu                                                                           |

| ADCON0   | 08h     | 1111 1100                | uull 1100                                                                           |

| ADRES    | 09h     | xxxx xxxx                | uuuu uuuu                                                                           |

| OPTION   |         | 1111 1111                | 1111 1111                                                                           |

| TRISIO   |         | 11 1111                  | 11 1111                                                                             |

#### TABLE 10-3: RESET CONDITIONS FOR REGISTERS – PIC12F510

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 10-5 for Reset value for specific conditions.

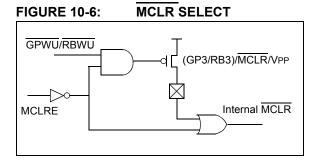

#### 10.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external MCLR function. When programmed, the MCLR function is tied to the internal VDD and the pin is assigned to be a I/O. See Figure 10-6.

#### 10.4 Power-on Reset (POR)

The PIC12F510/16F506 devices incorporate an onchip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. The POR is active regardless of the state of the MCLR enable bit. An internal weak pull-up resistor is implemented using a transistor (refer to Table 13-3 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create an external Power-on Reset. A maximum rise time for VDD is specified. See **Section 13.0 "Electrical Characteristics"** for details.

When the devices start normal operation (exit the Reset condition), device operating parameters (volt-age, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 10-7.

The Power-on Reset circuit and the Device Reset Timer (see Section 10.5 "Device Reset Timer (DRT)") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR, internal or external, to be high. After the time-out period, it will reset the Reset latch and thus end the on-chip Reset signal.

A power-up example where  $\overline{\text{MCLR}}$  is held low is shown in Figure 10-8. VDD is allowed to rise and stabilize before bringing  $\overline{\text{MCLR}}$  high. The chip will actually come out of Reset TDRT msec after  $\overline{\text{MCLR}}$  goes high.

In Figure 10-9, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be (GP3/RB3). The VDD is stable before the Start-up timer times out and there is no problem in getting a proper Reset. However, Figure 10-10 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 10-9).

| Note: | When the devices start normal operation (exit the Reset condition), device operat- |

|-------|------------------------------------------------------------------------------------|

|       | ing parameters (voltage, frequency,                                                |

|       | temperature, etc.) must be met to ensure                                           |

|       | operation. If these conditions are not met,                                        |

|       | the device must be held in Reset until the                                         |

|       | operating conditions are met.                                                      |

For additional information, refer to Application Notes AN522, *"Power-Up Considerations"* (DS00522) and AN607, *"Power-up Trouble Shooting"* (DS00607).

TABLE 10-7: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION <sup>(1)</sup> | GPWU  | GPPU  | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup> | RBWU  | RBPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer. - = unimplemented, read as '0', u = unchanged.

Note 1: PIC12F510 only.

2: PIC16F506 only.

| TRIS             | Load TRIS Register                                                                 |

|------------------|------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                            |

| Operands:        | f = 6                                                                              |

| Operation:       | $(W) \to TRIS \text{ register f}$                                                  |

| Status Affected: | None                                                                               |

| Description:     | TRIS register 'f' (f = 6 or 7) is<br>loaded with the contents of the W<br>register |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                              |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                          |

| Operands:        | $0 \le k \le 255$                                                                                                 |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |

| Status Affected: | Z                                                                                                                 |

| Description:     | The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| DC Characteristics |              |                                                                 |       | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |             |          |                                                                                                                    |  |  |

|--------------------|--------------|-----------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|--------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym          | Characteristic                                                  | Min   | Typ <sup>(1)</sup>                                                                                                                    | Max         | Units    | Conditions                                                                                                         |  |  |

| D001               | Vdd          | Supply Voltage                                                  | 2.0   |                                                                                                                                       | 5.5         | V        | See Figure 14-1                                                                                                    |  |  |

| D002               | Vdr          | RAM Data Retention Voltage <sup>(2)</sup>                       | _     | 1.5*                                                                                                                                  |             | V        | Device in Sleep mode                                                                                               |  |  |

| D003               | VPOR         | VDD Start Voltage to ensure<br>Power-on Reset                   | —     | Vss                                                                                                                                   |             | V        | See Section 10.4 "Power-on<br>Reset (POR)" for details                                                             |  |  |

| D004               | SVDD         | VDD Rise Rate to ensure<br>Power-on Reset                       | 0.05* | _                                                                                                                                     |             | V/ms     | See Section 10.4 "Power-on<br>Reset (POR)" for details                                                             |  |  |

| D010               | IDD          | Supply Current <sup>(3,4)</sup>                                 |       | 175<br>0.625                                                                                                                          | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, VDD = 2.0V<br>Fosc = 4 MHz, VDD = 5.0V                                                               |  |  |

|                    |              |                                                                 | _     | 250<br>1.0                                                                                                                            | 450<br>1.5  | μA<br>mA | Fosc = 8 MHz, Vdd = 2.0V<br>Fosc = 8 MHz, Vdd = 5.0V                                                               |  |  |

|                    |              |                                                                 |       | 1.4                                                                                                                                   | 2.0         | mA       | Fosc = 20 MHz, VDD = 5.0V                                                                                          |  |  |

|                    |              |                                                                 | _     | 11<br>38                                                                                                                              | 16<br>54    | μΑ<br>μΑ | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                                                             |  |  |

| D020               | IPD          | Power-down Current <sup>(5)</sup>                               | _     | 0.1<br>0.35                                                                                                                           | 9.0<br>15.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                                                           |  |  |

| D022               | Iwdt         | WDT Current <sup>(5)</sup>                                      | _     | 1.0<br>7.0                                                                                                                            | 18<br>22    | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                                                           |  |  |

| D023               | ICMP         | Comparator Current <sup>(5)</sup>                               | _     | 15<br>55                                                                                                                              | 25<br>75    | μΑ<br>μΑ | VDD = 2.0V (per comparator)<br>VDD = 5.0V (per comparator)                                                         |  |  |

| D022               | ICVREF       | CVREF Current <sup>(5)</sup>                                    | _     | 30<br>75                                                                                                                              | 65<br>135   | μΑ<br>μΑ | VDD = 2.0V (high range)<br>VDD = 5.0V (high range)                                                                 |  |  |

| D023               | IFVR         | Internal 0.6V Fixed Voltage<br>Reference Current <sup>(5)</sup> | _     | 85<br>175                                                                                                                             | 130<br>220  | μΑ<br>μΑ | VDD = 2.0V (0.6V reference and<br>1 comparator enabled)<br>VDD = 5.0V (0.6V reference and<br>1 comparator enabled) |  |  |

| D024               | $\Delta$ IAD | A/D Conversion Current <sup>(5)</sup>                           | _     | 120                                                                                                                                   | 150         | μA       | 2.0V                                                                                                               |  |  |

|                    |              |                                                                 | _     | 200                                                                                                                                   | 250         | μA       | 5.0V                                                                                                               |  |  |

#### 13.2 DC Characteristics: PIC12F510/16F506 (Extended)

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- 4: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- **5:** For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

- **6:** Does not include current through REXT. The current through the resistor can be estimated by the formula: I = VDD/2REXT (mA) with REXT in kΩ.

#### TABLE 13-5: CALIBRATED INTERNAL RC FREQUENCIES

| AC CH        | ARACT | ERISTICS                                               | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial),} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array} $ |                      |                      | 5°C (industrial),    |       |                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                                         | Freq.<br>Tolerance                                                                                                                                                                                                                                                 | Min                  | Typ <sup>(1)</sup>   | Max*                 | Units | Conditions                                                                                                                                                                                                                                                                                                                                                                      |

| F10          | Fosc  | Internal Calibrated INTOSC<br>Frequency <sup>(1)</sup> | ±1%<br>±2%<br>±5%                                                                                                                                                                                                                                                  | 7.92<br>7.84<br>7.60 | 8.00<br>8.00<br>8.00 | 8.08<br>8.16<br>8.40 | MHz   | $ \begin{array}{l} \mbox{VdD} = 3.5 \mbox{V TA} = 25 \mbox{°C} \\ 2.5 \mbox{V } \leq \mbox{VdD} \leq 5.5 \mbox{V} \\ 0^{\circ} \mbox{C} \leq \mbox{Ta} \leq +85 \mbox{°C} \\ 2.0 \mbox{V} \leq \mbox{VdD} \leq 5.5 \mbox{V} \\ -40 \mbox{°C} \leq \mbox{Ta} \leq +85 \mbox{°C} (\mbox{Ind.}) \\ -40 \mbox{°C} \leq \mbox{Ta} \leq +125 \mbox{°C} (\mbox{Ext.}) \\ \end{array} $ |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| VDD (Volts)   | Temperature (°C) | Min | Тур  | Max  | Units |

|---------------|------------------|-----|------|------|-------|

| RB0 (GP0)/RB1 | (GP1)            |     |      |      |       |

| 2.0           | -40              | 73K | 105K | 186K | Ω     |

|               | 25               | 73K | 113K | 187K | Ω     |

|               | 85               | 82K | 123K | 190K | Ω     |

|               | 125              | 86K | 132k | 190K | Ω     |

| 5.5           | -40              | 15K | 21K  | 33K  | Ω     |

|               | 25               | 15K | 22K  | 34K  | Ω     |

|               | 85               | 19K | 26k  | 35K  | Ω     |

|               | 125              | 23K | 29K  | 35K  | Ω     |

| RB3 (GP3)     |                  |     |      |      |       |

| 2.0           | -40              | 63K | 81K  | 96K  | Ω     |

|               | 25               | 77K | 93K  | 116K | Ω     |

|               | 85               | 82K | 96k  | 116K | Ω     |

|               | 125              | 86K | 100K | 119K | Ω     |

| 5.5           | -40              | 16K | 20k  | 22K  | Ω     |

|               | 25               | 16K | 21K  | 23K  | Ω     |

|               | 85               | 24K | 25k  | 28K  | Ω     |

|               | 125              | 26K | 27K  | 29K  | Ω     |

#### TABLE 13-9: PULL-UP RESISTOR RANGES

NOTES:

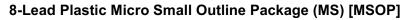

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        | MILLIMETERS |          |      |  |

|--------------------------|--------------|-------------|----------|------|--|

| Dimer                    | nsion Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N            |             | 8        |      |  |

| Pitch                    | е            | 0.65 BSC    |          |      |  |

| Overall Height           | A            | -           | -        | 1.10 |  |

| Molded Package Thickness | A2           | 0.75        | 0.85     | 0.95 |  |

| Standoff                 | A1           | 0.00        | -        | 0.15 |  |

| Overall Width            | E            |             | 4.90 BSC |      |  |

| Molded Package Width     | E1           | 3.00 BSC    |          |      |  |

| Overall Length           | D            | 3.00 BSC    |          |      |  |

| Foot Length              | L            | 0.40        | 0.60     | 0.80 |  |

| Footprint                | L1           | 0.95 REF    |          |      |  |

| Foot Angle               | φ            | 0°          | -        | 8°   |  |

| Lead Thickness           | С            | 0.08        | -        | 0.23 |  |

| Lead Width               | b            | 0.22        | -        | 0.40 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111B

### **Т**

| Timer0                                         |        |

|------------------------------------------------|--------|

| Timer0                                         |        |

| Timer0 (TMR0) Module                           | 39     |

| TMR0 with External Clock                       |        |

| Timing Diagrams and Specifications             | 91     |

| Timing Parameter Symbology and Load Conditions | 91     |

| TRIS Registers                                 | 27     |

| w                                              |        |

| Wake-up from Sleep                             | 69     |

| Watchdog Timer (WDT)                           | 55, 66 |

| Period                                         |        |

|                                                |        |

| Programming Considerations                     |        |

| Programming Considerations<br>WWW Address      |        |

| 5 5                                            | 108    |

| WWW Address                                    | 108    |