# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 67 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 16-QFN (3x3)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f506-i-mg |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table of Contents

| 1.0   | General Description                                  | 5     |

|-------|------------------------------------------------------|-------|

| 2.0   | PIC12F510/16F506 Device Varieties                    | 7     |

| 3.0   | Architectural Overview                               | 9     |

| 4.0   | Memory Organization                                  | 15    |

| 5.0   | I/O Port                                             | 27    |

| 6.0   | TMR0 Module and TMR0 Register                        | 39    |

| 7.0   | Comparator(s)                                        | 43    |

| 8.0   | Comparator Voltage Reference Module (PIC16F506 only) | 49    |

| 9.0   | Analog-to-Digital (A/D) Converter                    | 51    |

| 10.0  | Special Features Of The CPU                          | 55    |

|       | Instruction Set Summary                              |       |

| 12.0  | Development Support                                  | 79    |

| 13.0  | Electrical Characteristics                           | 83    |

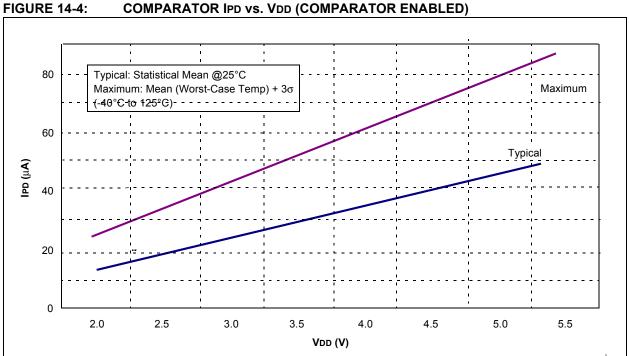

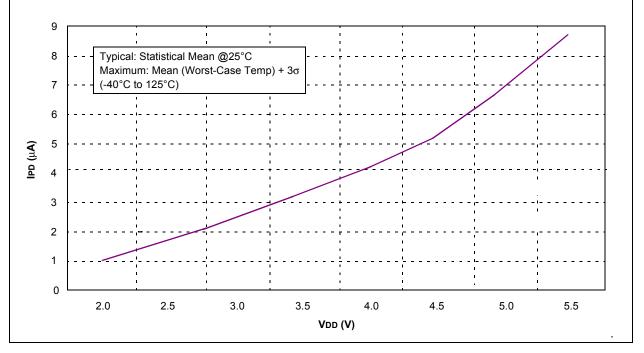

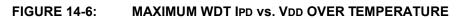

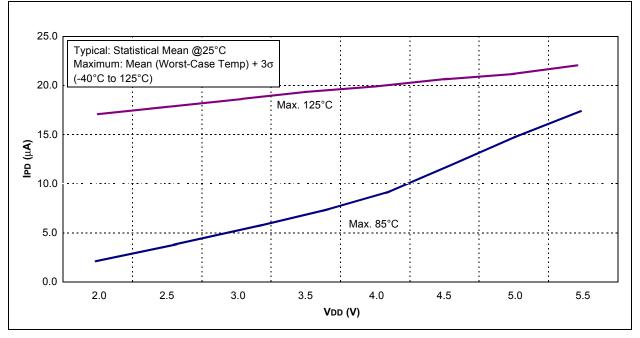

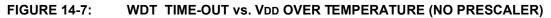

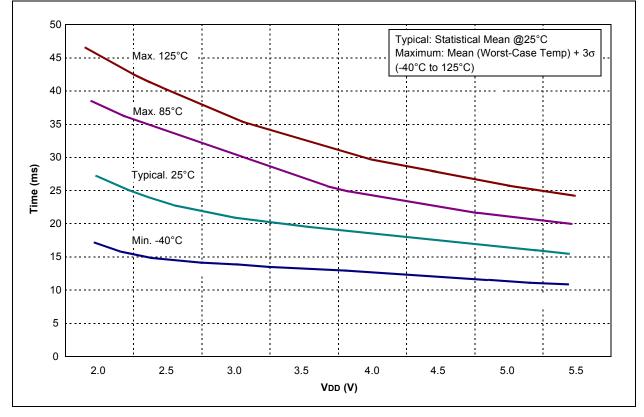

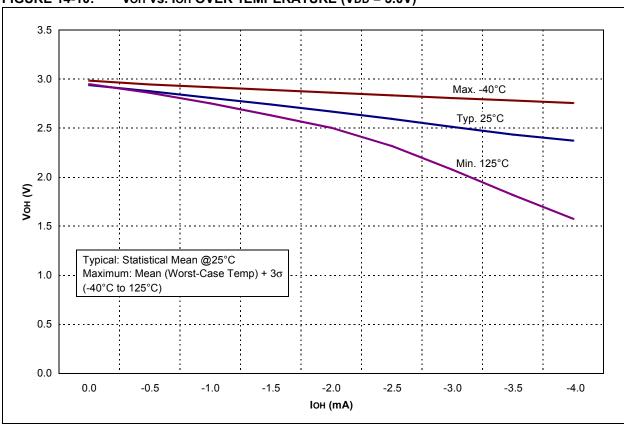

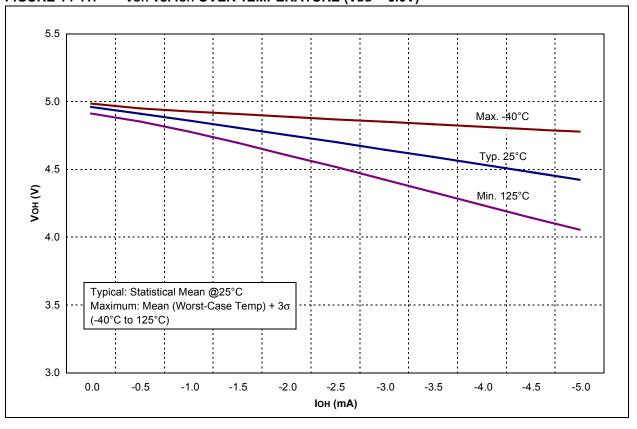

| 14.0  | DC and AC Characteristics Graphs and Charts          | 97    |

| 15.0  | Packaging                                            | . 105 |

| Index |                                                      | . 117 |

| The N | ficrochip Web Site                                   | . 119 |

| Custo | mer Change Notification Service                      | . 119 |

|       | mer Support                                          |       |

| Read  | er Response                                          | . 120 |

| Produ | Ict Identification System                            | . 121 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

NOTES:

| Name                  | Function | Input Type | Output<br>Type | Description                                                                                                                |

|-----------------------|----------|------------|----------------|----------------------------------------------------------------------------------------------------------------------------|

| RB0/AN0/C1IN+/ICSPDAT | RB0      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | AN0      | AN         | —              | ADC channel input.                                                                                                         |

|                       | C1IN+    | AN         | —              | Comparator 1 input.                                                                                                        |

|                       | ICSPDAT  | ST         | CMOS           | In-Circuit Serial Programming data pin.                                                                                    |

| RB1/AN1/C1IN-/ICSPCLK | RB1      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | AN1      | AN         |                | ADC channel input.                                                                                                         |

|                       | C1IN-    | AN         |                | Comparator 1 input.                                                                                                        |

|                       | ICSPCLK  | ST         | _              | In-Circuit Serial Programming clock pin.                                                                                   |

| RB2/AN2/C1OUT         | RB2      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | AN2      | AN         |                | ADC channel input.                                                                                                         |

|                       | C10UT    | _          | CMOS           | Comparator 1 output.                                                                                                       |

| RB3/MCLR/Vpp          | RB3      | TTL        | _              | Standard TTL input. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.             |

|                       | MCLR     | ST         | —              | MCLR input – weak pull-up always enabled in this mode.                                                                     |

|                       | Vpp      | HV         |                | Programming voltage input.                                                                                                 |

| RB4/OSC2/CLKOUT       | RB4      | TTL        | CMOS           | Bidirectional I/O port. Can be software pro-<br>grammed for internal weak pull-up and wake-up<br>from Sleep on pin change. |

|                       | OSC2     | _          | XTAL           | XTAL oscillator output pin.                                                                                                |

|                       | CLKOUT   | _          | CMOS           | EXTRC/INTOSC CLKOUT pin (Fosc/4).                                                                                          |

| RB5/OSC1/CLKIN        | RB5      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | OSC1     | XTAL       | _              | XTAL oscillator input pin.                                                                                                 |

|                       | CLKIN    | ST         | _              | EXTRC/EC Schmitt Trigger input.                                                                                            |

| RC0/C2IN+             | RC0      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2IN+    | AN         | _              | Comparator 2 input.                                                                                                        |

| RC1/C2IN-             | RC1      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2IN-    | AN         | _              | Comparator 2 input.                                                                                                        |

| RC2/CVREF             | RC2      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | CVREF    |            | AN             | Programmable Voltage Reference output.                                                                                     |

| RC3                   | RC3      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

| RC4/C2OUT             | RC4      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | C2OUT    |            | CMOS           | Comparator 2 output.                                                                                                       |

| RC5/T0CKI             | RC5      | TTL        | CMOS           | Bidirectional I/O port.                                                                                                    |

|                       | T0CKI    | ST         | _              | Timer0 clock input.                                                                                                        |

| Vdd                   | Vdd      | Р          |                | Positive supply for logic and I/O pins.                                                                                    |

| Vss                   | Vss      | Р          | _              | Ground reference for logic and I/O pins.                                                                                   |

TABLE 3-3: PIN DESCRIPTIONS – PIC16F506

**Legend:** I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input, AN = Analog Voltage, HV = High Voltage

## 4.0 MEMORY ORGANIZATION

The PIC12F510/16F506 memories are organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using STATUS register bit PA0. For the PIC12F510 and PIC16F506, with data memory register files of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Select Register (FSR).

## 4.1 Program Memory Organization for the PIC12F510/16F506

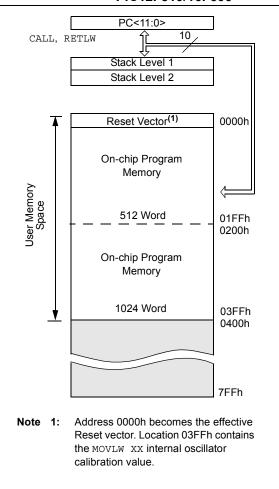

The PIC12F510/16F506 devices have a 10-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space.

Only the first 1K x 12 (0000h-03FFh) are physically implemented (see Figure 4-1). Accessing a location above these boundaries will cause a wraparound within the 1K x 12 space. The effective Reset vector is a 0000h (see Figure 4-1). Location 03FFh contains the internal clock oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-1:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC12F510/16F506

| Address            | Name    | Bit 7                                | Bit 6                                                              | Bit 5        | Bit 4        | Bit 3        | Bit 2     | Bit 1   | Bit 0 | Value on<br>Power-on<br>Reset |  |

|--------------------|---------|--------------------------------------|--------------------------------------------------------------------|--------------|--------------|--------------|-----------|---------|-------|-------------------------------|--|

| N/A                | TRIS    | I/O Control Registers (TRISB, TRISC) |                                                                    |              |              |              |           |         |       |                               |  |

| N/A                | OPTION  | Contains co                          | Contains control bits to configure Timer0 and Timer0/WDT Prescaler |              |              |              |           |         |       |                               |  |

| 00h                | INDF    | Uses conte                           | nts of FSR to                                                      | address dat  | a memory (no | t a physical | register) |         |       | xxxx xxxx                     |  |

| 01h                | TMR0    | Timer0 Mod                           | l'imer0 Module Register                                            |              |              |              |           |         |       |                               |  |

| 02h <sup>(1)</sup> | PCL     | Low Order                            | 8 bits of PC                                                       |              |              |              |           |         |       | 1111 1111                     |  |

| 03h                | STATUS  | RBWUF                                | CWUF                                                               | PA0          | TO           | PD           | Z         | DC      | С     | 0001 1xxx                     |  |

| 04h                | FSR     | Indirect Dat                         | a Memory Ad                                                        | dress Pointe | er           |              |           |         |       | 100x xxxx                     |  |

| 05h                | OSCCAL  | CAL6                                 | CAL5                                                               | CAL4         | CAL3         | CAL2         | CAL1      | CAL0    | —     | 1111 111-                     |  |

| 06h                | PORTB   | _                                    | _                                                                  | RB5          | RB4          | RB3          | RB2       | RB1     | RB0   | xx xxxx                       |  |

| 07h                | PORTC   | —                                    | _                                                                  | RC5          | RC4          | RC3          | RC2       | RC1     | RC0   | xx xxxx                       |  |

| 08h                | CM1CON0 | C10UT                                | C10UTEN                                                            | C1POL        | C1T0CS       | C10N         | C1NREF    | C1PREF  | C1WU  | 1111 1111                     |  |

| 09h                | ADCON0  | ANS1                                 | ANS0                                                               | ADCS1        | ADCS0        | CHS1         | CHS0      | GO/DONE | ADON  | 1111 1100                     |  |

| 0Ah                | ADRES   | ADC Conve                            | ersion Result                                                      |              |              |              |           |         |       | xxxx xxxx                     |  |

| 0Bh                | CM2CON0 | C2OUT                                | C2OUTEN                                                            | C2POL        | C2PREF2      | C2ON         | C2NREF    | C2PREF1 | C2WU  | 1111 1111                     |  |

| 0Ch                | VRCON   | VREN                                 | VROE                                                               | VRR          | (2)          | VR3          | VR2       | VR1     | VR0   | 0011 1111                     |  |

#### TABLE 4-2: SPECIAL FUNCTION REGISTER SUMMARY – PIC16F506

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0' (if applicable). Shaded cells = unimplemented or unused.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 "Program Counter" for an explanation of how to access these bits.

2: Unimplemented bit VRCON<4> read as '1'.

## 4.3 STATUS Register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see **Section 11.0 "Instruction Set Summary"**.

| REGISTER 4-2: | STATUS: STATUS REGISTER (PIC16F506) |

|---------------|-------------------------------------|

|---------------|-------------------------------------|

| R/W-0           | R/W-0                                                                                                             | R/W-0                                 | R-1                             | R-1                | R/W-x               | R/W-x             | R/W-x |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------|--------------------|---------------------|-------------------|-------|--|--|--|--|--|

| RBWUF           | CWUF                                                                                                              | PA0                                   | TO                              | PD                 | Z                   | DC                | С     |  |  |  |  |  |

| bit 7           |                                                                                                                   |                                       |                                 |                    | ·                   |                   | bit   |  |  |  |  |  |

|                 |                                                                                                                   |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

| Legend:         |                                                                                                                   |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

| R = Readable    | bit                                                                                                               | W = Writable b                        | it                              | U = Unimpler       | mented bit, read as | s '0'             |       |  |  |  |  |  |

| -n = Value at F | POR                                                                                                               | '1' = Bit is set                      |                                 | '0' = Bit is cle   | ared                | x = Bit is unkno  | wn    |  |  |  |  |  |

| bit 7           | <b>RBWUF</b> : POR                                                                                                | TP Dooot bit                          |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | 1 = Reset due                                                                                                     | to wake-up from<br>er-up or other Res |                                 | hange              |                     |                   |       |  |  |  |  |  |

| bit 6           | •                                                                                                                 | arator Reset bit                      |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | •                                                                                                                 | to wake-up from                       | Sleep on com                    | parator change     |                     |                   |       |  |  |  |  |  |

|                 | 0 = After powe                                                                                                    | er-up or other Res                    | set                             | -                  |                     |                   |       |  |  |  |  |  |

| bit 5           | -                                                                                                                 | Page Preselect I                      | oit                             |                    |                     |                   |       |  |  |  |  |  |

|                 | 0 (                                                                                                               | 1 = Page 1 (200h-3FFh)                |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | 0 = Page 0 (000h-1FFh)<br>Each page is 512 bytes.                                                                 |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | Using the PA0 bit as a general purpose read/write bit in devices which do not use it for program page preselect i |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | not recommended, since this may affect upward compatibility with future products.                                 |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

| bit 4           | <b>TO</b> : Time-Out                                                                                              |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | 1 = After power-up, CLRWDT instruction, or SLEEP instruction                                                      |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 |                                                                                                                   | ne-out occurred                       |                                 |                    |                     |                   |       |  |  |  |  |  |

| bit 3           | PD: Power-Do                                                                                                      |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | 1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                      |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

| bit 2           | <b>Z</b> : Zero bit                                                                                               | on of the Sheer                       | instruction                     |                    |                     |                   |       |  |  |  |  |  |

|                 |                                                                                                                   | of an arithmetic                      | or logic operatio               | on is zero         |                     |                   |       |  |  |  |  |  |

|                 |                                                                                                                   | of an arithmetic of                   | • •                             |                    |                     |                   |       |  |  |  |  |  |

| bit 1           | DC: Digit Carry/Borrow bit (for ADDWF and SUBWF instructions)                                                     |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | ADDWF:                                                                                                            |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | 1 = A carry from the 4th low-order bit of the result occurred                                                     |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | 0 = A carry from the 4th low-order bit of the result did not occur                                                |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | <u>SUBWF :</u><br>1 = A borrow from the 4th low-order bit of the result did not occur                             |                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 |                                                                                                                   | rom the 4th low-o                     |                                 |                    |                     |                   |       |  |  |  |  |  |

| bit 0           | C: Carry/Borro                                                                                                    | w bit (for ADDWF,                     | SUBWF and RR                    | F, RLF instruction | ons)                |                   |       |  |  |  |  |  |

|                 | ADDWF:                                                                                                            |                                       | UBWF:                           | -                  | RRF or RLF:         |                   |       |  |  |  |  |  |

|                 | 1 = A carry oc<br>0 = A carry did                                                                                 |                                       | = A borrow did<br>= A borrow oc |                    | Load bit with LSb   | or MSb, respectiv | ely   |  |  |  |  |  |

|                 | 0 – A carry uit                                                                                                   |                                       |                                 | ouncu              |                     |                   |       |  |  |  |  |  |

### 5.5 I/O Programming Considerations

#### 5.5.1 BIDIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. For example, the BCF and BSF instructions read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit 5 of PORTB/GPIO will cause all eight bits of PORTB/GPIO to be read into the CPU, bit 5 to be set and the PORTB/GPIO value to be written to the output latches. If another bit of PORTB/ GPIO is used as a bidirectional I/O pin (say bit '0') and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit '0' is switched into Output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential Read-Modify-Write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired OR", "wired AND"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT (e.g., PIC16F506)

|                         |                    | -                    |  |  |  |  |  |  |  |

|-------------------------|--------------------|----------------------|--|--|--|--|--|--|--|

| ;Initial PORTB Settings |                    |                      |  |  |  |  |  |  |  |

| ;PORTB<5:3> Inputs      |                    |                      |  |  |  |  |  |  |  |

| ;PORTB<2:0> Outputs     |                    |                      |  |  |  |  |  |  |  |

| ;                       |                    |                      |  |  |  |  |  |  |  |

| ;                       | PORTB latch        | PORTB pins           |  |  |  |  |  |  |  |

| ;                       |                    |                      |  |  |  |  |  |  |  |

| BCF PORTB, 5            | ;01 -ppp           | 11 pppp              |  |  |  |  |  |  |  |

| BCF PORTB, 4            | ;10 -ppp           | 11 pppp              |  |  |  |  |  |  |  |

| MOVLW 007h;             |                    |                      |  |  |  |  |  |  |  |

| TRIS PORTB              | ;10 -ppp           | 11 pppp              |  |  |  |  |  |  |  |

| ;                       |                    |                      |  |  |  |  |  |  |  |

| Note: The user          | may have expecte   | ed the pin values to |  |  |  |  |  |  |  |

|                         |                    | •                    |  |  |  |  |  |  |  |

|                         |                    | BCF caused RB5 to    |  |  |  |  |  |  |  |

| be latched              | d as the pin value | (High).              |  |  |  |  |  |  |  |

|                         |                    |                      |  |  |  |  |  |  |  |

## 5.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle. Whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-14). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes the file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-14: SUCCESSIVE I/O OPERATION (PIC16F506)

|                         | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4               | Q1   Q2   Q3   Q4 ;          | Q1 Q2 Q3 Q4 | ;                                                                                      |

|-------------------------|-------------------|---------------------------------|------------------------------|-------------|----------------------------------------------------------------------------------------|

| Instruction             | PC PC             | X PC + 1                        | X PC + 2                     | X PC + 3    | This example shows a write to PORTB followed by a read from PORTB.                     |

| Fetched                 | MOVWF PORTB       | MOVF PORTB, W                   | NOP                          | NOP         | Data setup time = (0.25 TCY – TPD)                                                     |

| RB<5:0>                 |                   | ı ı<br>• • • •                  | /                            |             | where: TCY = instruction cycle                                                         |

| 110 10.02               | l                 | <u> </u>                        | <u> </u>                     |             | TPD = propagation delay                                                                |

| Instruction<br>Executed |                   | Port pin<br>written here        | Port pin<br>sampled here     |             | Therefore, at higher clock frequencies, a write followed by a read may be problematic. |

|                         |                   | MOVWF PORTB<br>(Write to PORTB) | MOVF PORTB,W<br>(Read PORTB) | NOP         |                                                                                        |

| 1                       |                   |                                 |                              |             |                                                                                        |

|                         |                   |                                 |                              |             |                                                                                        |

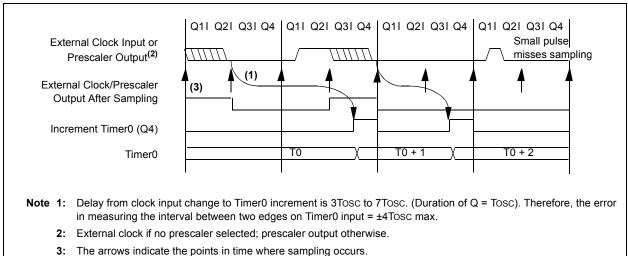

#### 6.1 Using Timer0 With An External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of an external clock with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for TOCKI or the comparator output to be high for at least 2Tosc (and a small RC delay of 2Tt0H) and low for at least 2Tosc (and a small RC delay of 2Tt0H). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI or the comparator output to have a period of at least 4Tosc (and a small RC delay of 4Tt0H) divided by the prescaler value. The only requirement on TOCKI or the comparator output high and low time is that they do not violate the minimum pulse width requirement of Tt0H. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

## 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

## 6.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see Figure 10-12). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|

|       | Timer0 module or the WDT, but not both. |  |  |  |  |  |  |  |

|       | Thus, a prescaler assignment for the    |  |  |  |  |  |  |  |

|       | Timer0 module means that there is no    |  |  |  |  |  |  |  |

|       | prescaler for the WDT and vice-versa.   |  |  |  |  |  |  |  |

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

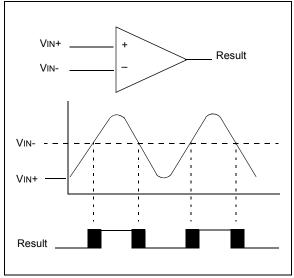

## 7.1 Comparator Operation

A single comparator is shown in Figure 7-3 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. The shaded area of the output of the comparator in Figure 7-3 represent the uncertainty due to input offsets and response time. See Table 13-1 for Common Mode Voltage.

FIGURE 7-3: SINGLE COMPARATOR

## 7.2 Comparator Reference

An internal reference signal may be used depending on the comparator operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-3). Please see **Section 8.0 "Comparator Voltage Reference Module (PIC16F506 only)"** for internal reference specifications.

#### 7.3 Comparator Response Time

Response time is the minimum time after selecting a new reference voltage or input source before the comparator output is to have a valid level. If the comparator inputs are changed, a delay must be used to allow the comparator to settle to its new state. Please see Table 13-1 for comparator response time specifications.

#### 7.4 Comparator Output

The comparator output is read through the CM1CON0 or CM2CON0 register. This bit is read-only. The comparator output may also be used externally, see Figure 7-3.

| Note: | Analog levels on any pin that is defined as   |

|-------|-----------------------------------------------|

|       | a digital input may cause the input buffer to |

|       | consume more current than is specified.       |

### 7.5 Comparator Wake-up Flag

The Comparator Wake-up Flag is set whenever all of the following conditions are met:

- <u>C1WU</u> = 0 (CM1CON0<0>) or C2WU = 0 (CM2CON0<0>)

- CM1CON0 or CM2CON0 has been read to latch the last known state of the C1OUT and C2OUT bit (MOVF CM1CON0, W)

- · Device is in Sleep

- The output of a comparator has changed state

The wake-up flag may be cleared in software or by another device Reset.

## 7.6 Comparator Operation During Sleep

When the comparator is enabled it is active. To minimize power consumption while in Sleep mode, turn off the comparator before entering Sleep.

## 7.7 Effects of Reset

A Power-on Reset (POR) forces the CM2CON0 register to its Reset state. This forces the Comparator input pins to analog Reset mode. Device current is minimized when analog inputs are present at Reset time.

## 7.8 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

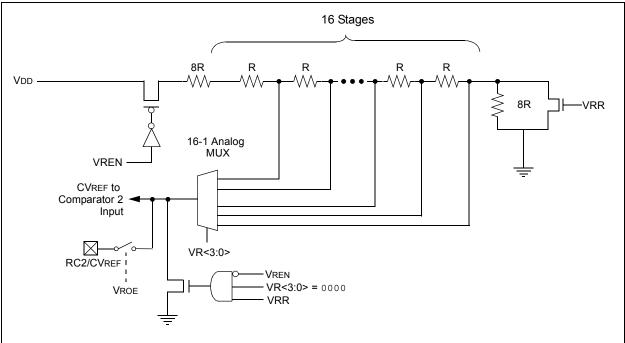

#### FIGURE 8-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

#### TABLE 8-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Add | Name                   | Bit 7 | Bit 6   | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1   | Bit 0 | Value on<br>POR | Value on all other Resets |

|-----|------------------------|-------|---------|-------|---------|-------|--------|---------|-------|-----------------|---------------------------|

| 0Ch | VRCON                  | VREN  | VROE    | VRR   | _       | VR3   | VR2    | VR1     | VR0   | 001- 1111       | 001- 1111                 |

| 08h | CM1CON0 <sup>(1)</sup> | C10UT | C10UTEN | C1POL | C1T0CS  | C10N  | C1NREF | C1PREF  | C1WU  | 1111 1111       | uuuu uuuu                 |

| 0Bh | CM2CON0 <sup>(1)</sup> | C2OUT | C2OUTEN | C2POL | C2PREF2 | C2ON  | C2NREF | C2PREF1 | C2WU  | 1111 1111       | uuuu uuuu                 |

$\label{eq:Legend: Legend: Legend: u = unchanged, - = unimplemented, read as `0`.$

Note 1: PIC16F506 only.

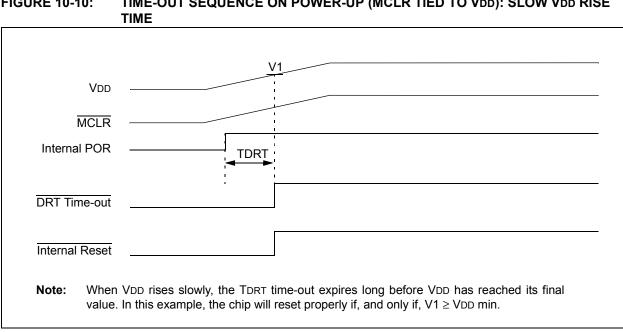

TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE FIGURE 10-10:

### 10.12 In-Circuit Serial Programming™ (ICSP™)

The PIC12F510/16F506 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the GP1/RB1 and GP0/RB0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1/RB1 becomes the programming clock and GP0/RB0 becomes the programming data. Both GP1/RB1 and GP0/RB0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is supplied to the device. Depending on the command and if the command was a Load or a Read, 14 bits of program data are then supplied to or from the device. For complete details of serial programming, please refer to the PIC12F510/16F506 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 10-15.

#### FIGURE 10-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| Mnem    | onic, | Description                                       | Cycles           | 12-1   | Bit Opc | ode  | Status   | Notes   |

|---------|-------|---------------------------------------------------|------------------|--------|---------|------|----------|---------|

| Opera   | ands  | Description                                       | Cycles           | MSb    |         | LSb  | Affected | Notes   |

| ADDWF   | f, d  | Add W and f                                       | 1                | 0001   | 11df    | ffff | C, DC, Z | 1, 2, 4 |

| ANDWF   | f, d  | AND W with f                                      | 1                | 0001   | 01df    | ffff | Z        | 2, 4    |

| CLRF    | f     | Clear f                                           | 1                | 0000   | 011f    | ffff | Z        | 4       |

| CLRW    | -     | Clear W                                           | 1                | 0000   | 0100    | 0000 | Z        |         |

| COMF    | f, d  | Complement f                                      | 1                | 0010   | 01df    | ffff | Z        |         |

| DECF    | f, d  | Decrement f                                       | 1                | 0000   | 11df    | ffff | Z        | 2, 4    |

| DECFSZ  | f, d  | Decrement f, Skip if 0                            | 1 <sup>(2)</sup> | 0010   | 11df    | ffff | None     | 2, 4    |

| INCF    | f, d  | Increment f                                       | 1                | 0010   | 10df    | ffff | Z        | 2, 4    |

| INCFSZ  | f, d  | Increment f, Skip if 0                            | 1 <sup>(2)</sup> | 0011   | 11df    | ffff | None     | 2, 4    |

| IORWF   | f, d  | Inclusive OR W with f                             | 1                | 0001   | 00df    | ffff | Z        | 2, 4    |

| MOVF    | f, d  | Move f                                            | 1                | 0010   | 00df    | ffff | Z        | 2, 4    |

| MOVWF   | f     | Move W to f                                       | 1                | 0000   | 001f    | ffff | None     | 1, 4    |

| NOP     | _     | No Operation                                      | 1                | 0000   | 0000    | 0000 | None     |         |

| RLF     | f, d  | Rotate left f through Carry                       | 1                | 0011   | 01df    | ffff | С        | 2, 4    |

| RRF     | f, d  | Rotate right f through Carry                      | 1                | 0011   | 00df    | ffff | С        | 2, 4    |

| SUBWF   | f, d  | Subtract W from f                                 | 1                | 0000   | 10df    | ffff | C, DC, Z | 1, 2, 4 |

| SWAPF   | f, d  | Swap f                                            | 1                | 0011   | 10df    | ffff | None     | 2, 4    |

| XORWF   | f, d  | Exclusive OR W with f                             | 1                | 0001   | 10df    | ffff | Z        | 2, 4    |

|         | ·     | BIT-ORIENTED FILE REGISTE                         | R OPER           | ATIONS | ;       |      | I        |         |

| BCF     | f, b  | Bit Clear f                                       | 1                | 0100   | bbbf    | ffff | None     | 2, 4    |

| BSF     | f, b  | Bit Set f                                         | 1                | 0101   | bbbf    | ffff | None     | 2, 4    |

| BTFSC   | f, b  | Bit Test f, Skip if Clear                         | 1 <sup>(2)</sup> | 0110   | bbbf    | ffff | None     | ,       |

| BTFSS   | f, b  | Bit Test f, Skip if Set                           | 1 <sup>(2)</sup> | 0111   | bbbf    | ffff | None     |         |

|         | ,     | LITERAL AND CONTROL C                             | PERATIO          | ONS    |         |      |          | 1       |

| ANDLW   | k     | AND literal with W                                | 1                | 1110   | kkkk    | kkkk | Z        |         |

| CALL    | k     | Call Subroutine                                   | 2                | 1001   | kkkk    | kkkk | None     | 1       |

| CLRWDT  | _     | Clear Watchdog Timer                              | 1                | 0000   | 0000    | 0100 | TO, PD   |         |

| GOTO    | k     | Unconditional branch                              | 2                | 101k   | kkkk    | kkkk | None     |         |

| IORLW   | k     | Inclusive OR literal with W                       | 1                | 1101   | kkkk    | kkkk | Z        |         |

| MOVLW   | k     | Move literal to W                                 | 1                | 1100   | kkkk    | kkkk | None     |         |

| OPTION  | _     | Load OPTION register                              | 1                | 0000   | 0000    | 0010 | None     |         |

| RETLW   | k     | Return, place literal in W                        | 2                | 1000   | kkkk    | kkkk | None     |         |

| SLEEP   | _     | Go into Standby mode                              | 1                | 0000   | 0000    | 0011 | TO, PD   |         |

| TRIS    | f     | Load TRIS register                                | 1                | 0000   | 0000    | Offf | None     | 3       |

| XORLW   | k     | Exclusive OR literal to W                         | 1                | 1111   | kkkk    | kkkk | Z        | -       |

| Note 1: |       | bit of the Program Counter will be forced to a 'o | ' by any i       |        |         |      |          | cept fo |

#### TABLE 11-2: INSTRUCTION SET SUMMARY

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 6, causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

4: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

FIGURE 14-11: VOH vs. IOH OVER TEMPERATURE (VDD = 5.0V)

FIGURE 14-10: VOH vs. IOH OVER TEMPERATURE (VDD = 3.0V)

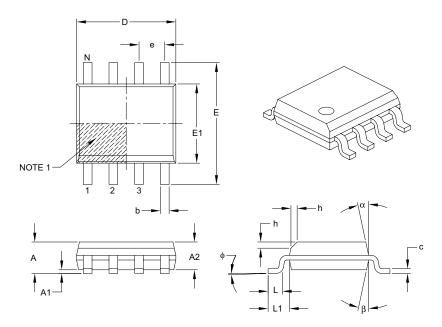

### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        |          | MILLIMETERS | 6    |

|--------------------------|--------------|----------|-------------|------|

| Dime                     | nsion Limits | MIN      | NOM         | MAX  |

| Number of Pins           | N            | 8        |             |      |

| Pitch                    | е            | 1.27 BSC |             |      |

| Overall Height           | A            | -        | -           | 1.75 |

| Molded Package Thickness | A2           | 1.25     | -           | -    |

| Standoff §               | A1           | 0.10     | -           | 0.25 |

| Overall Width            | E            | 6.00 BSC |             |      |

| Molded Package Width     | E1           | 3.90 BSC |             |      |

| Overall Length           | D            | 4.90 BSC |             |      |

| Chamfer (optional)       | h            | 0.25     | -           | 0.50 |

| Foot Length              | L            | 0.40     | -           | 1.27 |

| Footprint                | L1           | 1.04 REF |             |      |

| Foot Angle               | ¢            | 0°       | -           | 8°   |

| Lead Thickness           | С            | 0.17     | -           | 0.25 |

| Lead Width               | b            | 0.31     | -           | 0.51 |

| Mold Draft Angle Top     | α            | 5°       | -           | 15°  |

| Mold Draft Angle Bottom  | β            | 5°       | -           | 15°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

## INDEX

| Α               |    |

|-----------------|----|

| ALU             | 9  |

| Assembler       |    |

| MPASM Assembler | 80 |

## В

| Block Diagram                |    |

|------------------------------|----|

| Comparator for the PIC12F510 |    |

| Comparator for the PIC16F506 |    |

| On-Chip Reset Circuit        | 64 |

| Timer0                       |    |

| TMR0/WDT Prescaler           |    |

| Watchdog Timer               | 67 |

| Brown-Out Protection Circuit | 68 |

## С

| C Compilers                          |        |

|--------------------------------------|--------|

| MPLAB C18                            | 80     |

| MPLAB C30                            | 80     |

| Carry                                | 9      |

| Clocking Scheme                      |        |

| Code Protection                      | 55, 69 |

| Configuration Bits                   |        |

| Configuration Word (PIC12F510)       | 56     |

| Configuration Word (PIC16F506)       |        |

| Customer Change Notification Service |        |

| Customer Notification Service        | 108    |

| Customer Support                     | 108    |

## D

| DC                                        | 88 |

|-------------------------------------------|----|

| DC Characteristics (Extended)             | 87 |

| DC Characteristics (Industrial)           | 86 |

| DC Characteristics (Industrial, Extended) | 88 |

| Development Support                       | 79 |

| Digit Carry                               | 9  |

|                                           |    |

### Ε

| rata3 |

|-------|

| ala   |

## F

Family of Devices PIC12F510/16F506......5 FSR.......24

#### I

| I/O Interfacing                |        |

|--------------------------------|--------|

| I/O Ports                      |        |

| I/O Programming Considerations |        |

| ID Locations                   | 55, 69 |

| INDF                           |        |

| Indirect Data Addressing       |        |

| Instruction Cycle              | 14     |

| Instruction Flow/Pipelining    |        |

| Instruction Set Summary        | 72     |

| Internet Address               | 108    |

| L                              |        |

| Loading of PC                  |        |

## Μ

| Memory Organization 15                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Memory 16                                                                                                                                                                                                                                                                                |

| Program Memory (PIC12F510/16F506) 15                                                                                                                                                                                                                                                          |

| Microchip Internet Web Site 108                                                                                                                                                                                                                                                               |

| MPLAB ASM30 Assembler, Linker, Librarian 80                                                                                                                                                                                                                                                   |

| MPLAB ICD 2 In-Circuit Debugger 81                                                                                                                                                                                                                                                            |

| MPLAB ICE 2000 High-Performance Universal                                                                                                                                                                                                                                                     |

| In-Circuit Emulator                                                                                                                                                                                                                                                                           |

| MPLAB ICE 4000 High-Performance Universal                                                                                                                                                                                                                                                     |

| In-Circuit Emulator                                                                                                                                                                                                                                                                           |

| MPLAB Integrated Development Environment Software 79                                                                                                                                                                                                                                          |

| MPLAB PM3 Device Programmer 81                                                                                                                                                                                                                                                                |

| MPLINK Object Linker/MPLIB Object Librarian 80                                                                                                                                                                                                                                                |

| 0                                                                                                                                                                                                                                                                                             |

| -                                                                                                                                                                                                                                                                                             |

| OPTION Register                                                                                                                                                                                                                                                                               |

| OSC Selection                                                                                                                                                                                                                                                                                 |

| OSCCAL Register                                                                                                                                                                                                                                                                               |

| Oscillator Configurations 58                                                                                                                                                                                                                                                                  |

| Oscillator Types                                                                                                                                                                                                                                                                              |

| HS58                                                                                                                                                                                                                                                                                          |

| LP 58                                                                                                                                                                                                                                                                                         |

| RC                                                                                                                                                                                                                                                                                            |

| XT58                                                                                                                                                                                                                                                                                          |

| Р                                                                                                                                                                                                                                                                                             |

| -                                                                                                                                                                                                                                                                                             |

| PIC12F510/16F506 Device Varieties7                                                                                                                                                                                                                                                            |

| PICSTART Plus Development Programmer82                                                                                                                                                                                                                                                        |

| POR                                                                                                                                                                                                                                                                                           |

| Device Reset Timer (DRT) 55, 66                                                                                                                                                                                                                                                               |

| PD                                                                                                                                                                                                                                                                                            |

| Power-on Reset (POR)55                                                                                                                                                                                                                                                                        |

| <del>TO</del>                                                                                                                                                                                                                                                                                 |

| PORTB                                                                                                                                                                                                                                                                                         |

| Power-down Mode                                                                                                                                                                                                                                                                               |

| Prescaler                                                                                                                                                                                                                                                                                     |

| Program Counter                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                               |

| Q                                                                                                                                                                                                                                                                                             |

| Q cycles                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                               |

| R                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                               |

| R                                                                                                                                                                                                                                                                                             |

| R Oscillator                                                                                                                                                                                                                                                                                  |

| R C Oscillator                                                                                                                                                                                                                                                                                |

| R C Oscillator                                                                                                                                                                                                                                                                                |

| R<br>RC Oscillator                                                                                                                                                                                                                                                                            |

| R         59           Reader Response         109           Read-Modify-Write         37           Register File Map         16           PIC12F510         16           PIC16F506         16                                                                                                |

| R         59           Reader Response         109           Read-Modify-Write         37           Register File Map         16           PIC12F510         16           PIC16F506         16           Registers         16                                                                 |

| RRC Oscillator                                                                                                                                                                                                                                                                                |

| R         59           Reader Response         109           Read-Modify-Write         37           Register File Map         16           PIC12F510         16           PIC16F506         16           Registers         5           Special Function         17           Reset         55 |

| RRC Oscillator                                                                                                                                                                                                                                                                                |

| R         59           Reader Response         109           Read-Modify-Write         37           Register File Map         16           PIC12F510         16           PIC16F506         16           Registers         5           Special Function         17           Reset         55 |

| R         RC Oscillator                                                                                                                                                                                                                                                                       |

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device    | X /XX XXX<br>     <br>Temperature Package Pattern<br>Range                                                 | Examples:<br>a) PIC16F506-E/P 301 = Extended Temp., PDIP<br>package, QTP pattern #301<br>b) PIC16F506-I/SN = Industrial Temp., SOIC                                                           |

|-----------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:               | PIC16F506<br>PIC12F510<br>PIC16F506T <sup>(1)</sup><br>PIC12F510T <sup>(2)</sup><br>VDD range 2.0V to 5.5V | package<br>c) PIC16F506T-E/P = Extended Temp., PDIP<br>package, Tape and Reel                                                                                                                 |

| Temperature<br>Range: | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)  |                                                                                                                                                                                               |

| Package:              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                       | Note 1:       T = in tape and reel SOIC and TSSOP packages only         2:       T = in tape and reel SOIC and MSOP packages only.         3:       PIC12F510 only.         4:       Pb-free. |

| Pattern:              | QTP, SQTP Code or Special Requirements<br>(blank otherwise)                                                |                                                                                                                                                                                               |