# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

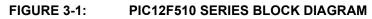

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 11                                                                      |

| Program Memory Size        | 1.5KB (1K x 12)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 67 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 14-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f506-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

NOTES:

| REGISTER 4-2: | STATUS: STATUS REGISTER (PIC16F506) |

|---------------|-------------------------------------|

|---------------|-------------------------------------|

| R/W-0           | R/W-0                                         | R/W-0                                                                                                              | R-1                             | R-1                | R/W-x               | R/W-x             | R/W-x |  |  |  |  |  |

|-----------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|---------------------|-------------------|-------|--|--|--|--|--|

| RBWUF           | CWUF                                          | PA0                                                                                                                | TO                              | PD                 | Z                   | DC                | С     |  |  |  |  |  |

| bit 7           |                                               |                                                                                                                    |                                 |                    | ·                   | •                 | bit   |  |  |  |  |  |

|                 |                                               |                                                                                                                    |                                 |                    |                     |                   |       |  |  |  |  |  |

| Legend:         |                                               |                                                                                                                    |                                 |                    |                     |                   |       |  |  |  |  |  |

| R = Readable    | bit                                           | W = Writable b                                                                                                     | it                              | U = Unimpler       | mented bit, read as | s '0'             |       |  |  |  |  |  |

| -n = Value at F | POR                                           | '1' = Bit is set                                                                                                   |                                 | '0' = Bit is cle   | ared                | x = Bit is unkno  | wn    |  |  |  |  |  |

| bit 7           | <b>RBWUF</b> : POR                            | TP Dooot bit                                                                                                       |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | 1 = Reset due                                 | to wake-up from<br>er-up or other Res                                                                              |                                 | hange              |                     |                   |       |  |  |  |  |  |

| bit 6           | •                                             | arator Reset bit                                                                                                   |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | •                                             | to wake-up from                                                                                                    | Sleep on com                    | parator change     |                     |                   |       |  |  |  |  |  |

|                 | 0 = After powe                                | er-up or other Res                                                                                                 | set                             | -                  |                     |                   |       |  |  |  |  |  |

| bit 5           | -                                             | Page Preselect I                                                                                                   | oit                             |                    |                     |                   |       |  |  |  |  |  |

|                 | 0 (                                           | 1 = Page 1 (200h-3FFh)<br>0 = Page 0 (000h-1FFh)                                                                   |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | <b>U</b> (                                    | Each page is 512 bytes.                                                                                            |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 |                                               | Using the PA0 bit as a general purpose read/write bit in devices which do not use it for program page preselect is |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | not recommen                                  | ided, since this m                                                                                                 | ay affect upwa                  | rd compatibility   | with future produc  | ts.               |       |  |  |  |  |  |

| bit 4           | <b>TO</b> : Time-Out                          |                                                                                                                    |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 |                                               | er-up, CLRWDT ins                                                                                                  | struction, or SL                | EEP instruction    |                     |                   |       |  |  |  |  |  |

|                 |                                               | ne-out occurred                                                                                                    |                                 |                    |                     |                   |       |  |  |  |  |  |

| bit 3           | PD: Power-Do                                  |                                                                                                                    |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | •                                             | er-up or by the CL<br>ion of the SLEEP                                                                             |                                 | on                 |                     |                   |       |  |  |  |  |  |

| bit 2           | <b>Z</b> : Zero bit                           | on of the Sheer                                                                                                    | instruction                     |                    |                     |                   |       |  |  |  |  |  |

|                 |                                               | of an arithmetic                                                                                                   | or logic operatio               | on is zero         |                     |                   |       |  |  |  |  |  |

|                 |                                               | of an arithmetic of                                                                                                | • •                             |                    |                     |                   |       |  |  |  |  |  |

| bit 1           | DC: Digit Carr                                | DC: Digit Carry/Borrow bit (for ADDWF and SUBWF instructions)                                                      |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | ADDWF:                                        |                                                                                                                    |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 |                                               | 1 = A carry from the 4th low-order bit of the result occurred                                                      |                                 |                    |                     |                   |       |  |  |  |  |  |

|                 | ,                                             | m the 4th low-ord                                                                                                  | der bit of the re               | sult did not occu  | ır                  |                   |       |  |  |  |  |  |

|                 | $\frac{\text{SUBWF}}{1 = A \text{ borrow f}}$ | rom the 4th low-c                                                                                                  | order bit of the                | result did not oc  | cur                 |                   |       |  |  |  |  |  |

|                 |                                               | rom the 4th low-o                                                                                                  |                                 |                    |                     |                   |       |  |  |  |  |  |

| bit 0           | C: Carry/Borro                                | w bit (for ADDWF,                                                                                                  | SUBWF and RR                    | F, RLF instruction | ons)                |                   |       |  |  |  |  |  |

|                 | ADDWF:                                        |                                                                                                                    | UBWF:                           | -                  | RRF or RLF:         |                   |       |  |  |  |  |  |

|                 | 1 = A carry oc                                |                                                                                                                    | = A borrow did<br>= A borrow oc |                    | Load bit with LSb   | or MSb, respectiv | ely   |  |  |  |  |  |

|                 | 0 - A carry uit                               | 0 = A carry did not occur 0 = A borrow occurred                                                                    |                                 |                    |                     |                   |       |  |  |  |  |  |

| W-1                               | W-1                                                             | W-1                                                                                                                                                                        | W-1                                                            | W-1               | W-1             | W-1      | W-1   |

|-----------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------|-----------------|----------|-------|

| RBWU                              | RBPU                                                            | TOCS                                                                                                                                                                       | TOSE                                                           | PSA               | PS2             | PS1      | PS0   |

| bit 7                             |                                                                 |                                                                                                                                                                            |                                                                |                   |                 |          | bit ( |

|                                   |                                                                 |                                                                                                                                                                            |                                                                |                   |                 |          |       |

| Legend:                           |                                                                 |                                                                                                                                                                            |                                                                |                   |                 |          |       |

| R = Readabl                       | le bit                                                          | W = Writable                                                                                                                                                               | bit                                                            | U = Unimpler      | nented bit, rea | d as '0' |       |

| n = Value at POR '1' = Bit is set |                                                                 |                                                                                                                                                                            | '0' = Bit is cle                                               | ared              | x = Bit is unkr | nown     |       |

| bit 7                             | <b>RBWU:</b> Enable V<br>1 = Disabled<br>0 = Enabled            | Vake-up On Pin (                                                                                                                                                           | Change bit (RB0                                                | ), RB1, RB3, RB4) |                 |          |       |

| bit 6                             | <b>RBPU:</b> Enable W<br>1 = Disabled<br>0 = Enabled            | /eak Pull-Ups bit                                                                                                                                                          | (RB0, RB1, RB                                                  | 3, RB4)           |                 |          |       |

| bit 5                             | <b>TOCS:</b> Timer0 CI<br>1 = Transition o<br>0 = Internal inst |                                                                                                                                                                            |                                                                |                   |                 |          |       |

| bit 4                             | <b>TOSE:</b> Timer0 Sc<br>1 = Increment c<br>0 = Increment c    | Ũ                                                                                                                                                                          | nsition on T0CK                                                | •                 |                 |          |       |

| bit 3                             | PSA: Prescaler A<br>1 = Prescaler a<br>0 = Prescaler a          | ssigned to the W                                                                                                                                                           |                                                                |                   |                 |          |       |

| bit 2-0                           | PS<2:0>: Presca                                                 | ler Rate Select b                                                                                                                                                          | its                                                            |                   |                 |          |       |

|                                   | Bit V                                                           | alue Timer0                                                                                                                                                                | Rate WDT R                                                     | ate               |                 |          |       |

|                                   | 0<br>0<br>0<br>1<br>1<br>1<br>1                                 | D0         1:2           D1         1:4           L0         1:8           L1         1:13           D01         1:30           D11         1:6           L01         1:12 | 1 : 2<br>1 : 4<br>6 1 : 8<br>2 1 : 16<br>4 1 : 32<br>28 1 : 64 |                   |                 |          |       |

#### REGISTER 4-4: OPTION\_REG: OPTION REGISTER (PIC16F506)

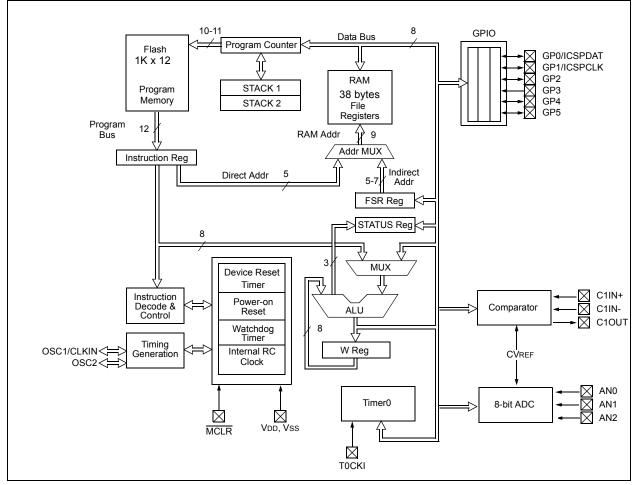

### 4.6 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The Program Counter (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4-4).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-4).

Instructions where the PCL is the destination or modify PCL instructions include MOVWF PC, ADDWF PC and BSF PC, 5.

Note: Because PC<8> is cleared in the CALL instruction or any modify PCL instruction, all subroutine calls or computed jumps are limited to the first 256 locations of any program memory page (512 words long).

#### FIGURE 4-4: LOADING OF PC BRANCH INSTRUCTIONS

### 4.6.1 EFFECTS OF RESET

The PC is set upon a Reset, which means that the PC addresses the last location in the last page (i.e., the oscillator calibration instruction). After executing MOVLW XX, the PC will roll over to location 00h and begin executing user code.

The STATUS register page preselect bits are cleared upon a Reset, which means that page 0 is preselected.

Therefore, upon a Reset, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

### 4.7 Stack

The PIC12F510/16F506 devices have a two-deep, 12-bit wide hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of Stack 1 into Stack 2 and then PUSH the current PC value, incremented by one, into Stack Level 1. If more than two sequential CALLs are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of Stack Level 1 into the PC and then copy Stack Level 2 contents into Stack Level 1. If more than two sequential RETLWS are executed, the stack will be filled with the address previously stored in Stack Level 2.

- **Note 1:** The W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

- 2: There are no Status bits to indicate stack overflows or stack underflow conditions.

- 3: There are no instruction mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL and RETLW instructions.

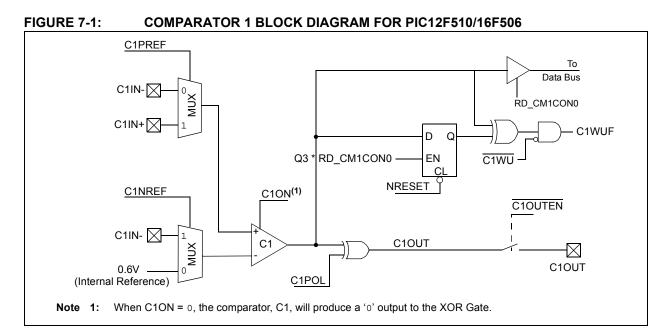

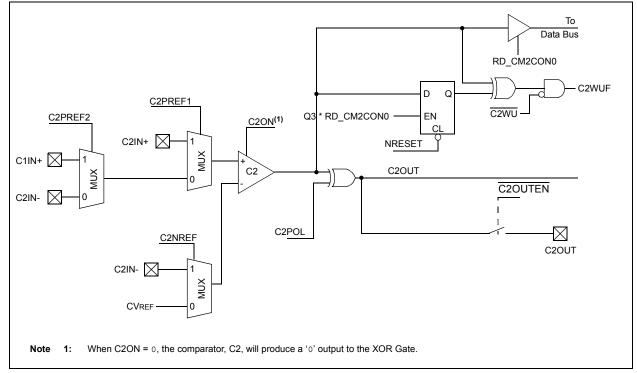

| TABLE 7-1: | REGISTERS ASSOCIATED WITH COMPARATOR MODULE |

|------------|---------------------------------------------|

|            |                                             |

| Add | Name                    | Bit 7 | Bit 6   | Bit 5      | Bit 4                | Bit 3 | Bit 2   | Bit 1   | Bit 0 | Value on<br>POR | Value on<br>All Other<br>Resets |

|-----|-------------------------|-------|---------|------------|----------------------|-------|---------|---------|-------|-----------------|---------------------------------|

| 03h | STATUS                  | GPWUF | CWUF    | PA0        | TO                   | PD    | Z       | DC      | С     | 0001 1xxx       | qq0q quuu                       |

| 07h | CM1CON0 <sup>(1)</sup>  | C1OUT | C10UTEN | C1POL      | C1T0CS               | C10N  | C1NREF  | C1PREF  | C1WU  | 1111 1111       | uuuu uuuu                       |

| 08h | CM1CON0 <sup>(2)</sup>  | C1OUT | C10UTEN | C1POL      | C1T0CS               | C10N  | C1NREF  | C1PREF  | C1WU  | 1111 1111       | uuuu uuuu                       |

| 0Bh | CM2CON0 <sup>(2)</sup>  | C2OUT | C2OUTEN | C2POL      | C2PREF2              | C2ON  | C2NREF  | C2PREF1 | C2WU  | 1111 1111       | uuuu uuuu                       |

| N/A | TRISB <sup>(2)</sup>    | _     | _       | I/O Contro | l Register           |       | 11 1111 | 11 1111 |       |                 |                                 |

| N/A | TRISC <sup>(2)</sup>    | —     | _       | I/O Contro | I/O Control Register |       |         |         |       |                 | 11 1111                         |

| N/A | TRISGPIO <sup>(1)</sup> | —     | _       | I/O Contro | l Register           |       |         |         |       | 11 1111         | 11 1111                         |

Legend: x = Unknown, u = Unchanged, - = Unimplemented, read as '0', q = Depends on condition.

Note 1: PIC12F510 only.

2: PIC16F506 only.

#### 9.1.5 SLEEP

This ADC does not have a dedicated ADC clock, and therefore, no conversion in Sleep is possible. If a conversion is underway and a Sleep command is executed, the GO/DONE and ADON bit will be cleared. This will stop any conversion in process and powerdown the ADC module to conserve power. Due to the nature of the conversion process, the ADRES may contain a partial conversion. At least 1 bit must have been converted prior to Sleep to have partial conversion data in ADRES. The ADCS and CHS bits are reset to their default condition; ANS<1:0> = 11 and CHS<1:0> = 11.

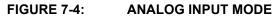

- For accurate conversions, TAD must meet the following:

- + 500 ns < TAD < 50  $\mu s$

- TAD = 1/(FOSC/divisor)

Shaded areas indicate TAD out of range for accurate conversions. If analog input is desired at these frequencies, use INTOSC/4 for the ADC clock source.

| Source | ADCS<br><1:0> | Divisor | 20 <sup>(1)</sup><br>MHz | 16 <sup>(1)</sup><br>MHz | 8 MHz | 4 MHz | 1 MHz | 500<br>kHz | 350<br>kHz | 200<br>kHz | 100<br>kHz | 32 kHz |

|--------|---------------|---------|--------------------------|--------------------------|-------|-------|-------|------------|------------|------------|------------|--------|

| INTOSC | 11            | 4       | _                        | _                        | .5 μs | 1 μs  | _     | _          | _          | _          | —          | _      |

| FOSC   | 10            | 4       | .2 μs                    | .25 μs                   | .5 μs | 1 μs  | 4 μs  | 8 µs       | 11 μs      | 20 µs      | 40 µs      | 125 μs |

| FOSC   | 01            | 8       | .4 μs                    | .5 μs                    | 1 μs  | 2 μs  | 8 µs  | 16 μs      | 23 µs      | 40 µs      | 80 µs      | 250 μs |

| FOSC   | 00            | 16      | .8 μs                    | 1 μs                     | 2 μs  | 4 μs  | 16 µs | 32 µs      | 46 µs      | 80 µs      | 160 μs     | 500 μs |

TABLE 9-2: TAD FOR ADCS SETTINGS WITH VARIOUS OSCILLATORS

**Note 1:** When operating with external oscillator frequencies of 16 MHz or higher, better ADC performance will result from selection of a suitable Fosc divisor value from Table 9-2 than from use of the INTOSC/4 option for the ADC clock.

#### TABLE 9-3:EFFECTS OF SLEEP ON ADCON0

|                   | ANS1      | ANS0      | ADCS1 | ADCS0 | CHS1 | CHS0 | GO/DONE | ADON |

|-------------------|-----------|-----------|-------|-------|------|------|---------|------|

| Entering<br>Sleep | Unchanged | Unchanged | 1     | 1     | 1    | 1    | 0       | 0    |

| Wake or<br>Reset  | 1         | 1         | 1     | 1     | 1    | 1    | 0       | 0    |

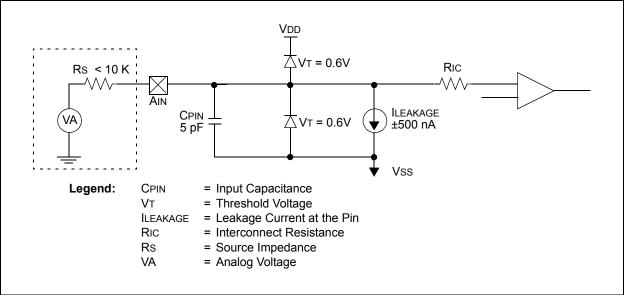

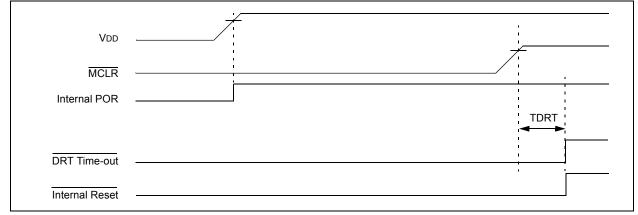

### FIGURE 10-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

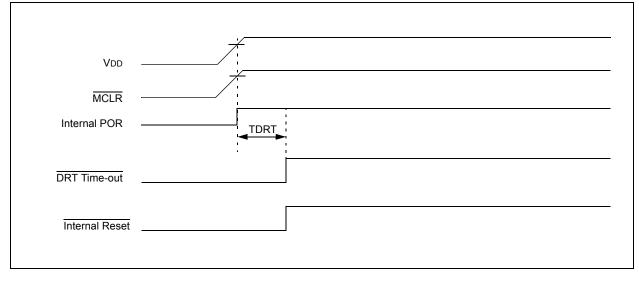

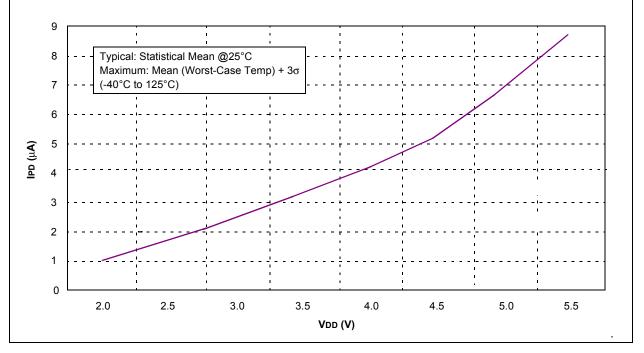

#### 10.5 Device Reset Timer (DRT)

On the PIC12F510/16F506 devices, the DRT runs any time the device is powered up. DRT runs from Reset and varies based on oscillator selection and Reset type (see Table 10-6).

The DRT operates from a free running on-chip oscillator that is separate from INTOSC. The processor is kept in Reset as long as the DRT is active. The DRT delay allows VDD to rise above VDD minimum and for the oscillator to stabilize.

Oscillator circuits, based on crystals or ceramic resonators, require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the devices in a Reset for a set period, as stated in Table 10-6, after MCLR has reached a logic high (VIH MCLR) level. Programming (GP3/RB3)/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases. This allows savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the (GP3/RB3)/MCLR/ VPP pin as a general purpose input.

The DRT delays will vary from chip-to-chip due to VDD, temperature and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out from Sleep. This is particularly important for applications using the WDT to wake from Sleep mode automatically.

Reset sources are POR, MCLR, WDT time-out, Wakeup on Pin Change and Wake-up on Comparator Change. See Section 10.9.2 "Wake-up from Sleep Reset", Notes 1, 2 and 3.

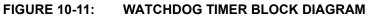

### 10.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator that does not require any external components. This RC oscillator is separate from the external RC oscillator of the (GP5/RB5)/OSC1/CLKIN pin and the internal 4/8 MHz oscillator. This means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or Sleep, a WDT Reset or wake-up Reset generates a device Reset.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset.

The WDT can be permanently disabled by programming the configuration WDTE as a '0' (see **Section 10.1 "Configuration Bits"**). Refer to the PIC12F510/16F506 Programming Specifications to determine how to access the Configuration Word.

#### TABLE 10-6:TYPICAL DRT PERIODS

| Oscillator<br>Configuration | POR Reset | Subsequent<br>Resets |

|-----------------------------|-----------|----------------------|

| LP                          | 18 ms     | 18 ms                |

| хт                          | 18 ms     | 18 ms                |

| HS <sup>(1)</sup>           | 18 ms     | 18 ms                |

| EC <sup>(1)</sup>           | 1.125 ms  | 10 µs                |

| INTOSC                      | 1.125 ms  | 10 µs                |

| EXTRC                       | 1.125 ms  | 10 µs                |

Note 1: PIC16F506 only

Note: It is the responsibility of the application designer to ensure the use of the 1.125 ms nominal DRT will result in acceptable operation. Refer to Electrical Specifications for VDD rise time and stability requirements for this mode of operation.

#### 10.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). If a longer time-out period is desired, a prescaler with a divisor ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst-case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 10.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device Reset.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum Sleep time before a WDT wake-up Reset.

TABLE 10-7: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION <sup>(1)</sup> | GPWU  | GPPU  | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup> | RBWU  | RBPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer. - = unimplemented, read as '0', u = unchanged.

Note 1: PIC12F510 only.

2: PIC16F506 only.

### 10.7 Time-out Sequence, Power-down and <u>Wake-up</u> from Sleep Status Bits (TO, PD, GPWUF/RBWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  and (GPWUF/RBWUF) bits in the STATUS register can be tested to determine if a Reset condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) Reset.

# TABLE 10-8: TO/PD/(GPWUF/RBWUF) STATUS AFTER RESET

| CWUF | GPWUF/<br>RBWUF | то | PD | Reset Caused By                               |

|------|-----------------|----|----|-----------------------------------------------|

| 0    | 0               | 0  | 0  | WDT wake-up from<br>Sleep                     |

| 0    | 0               | 0  | u  | WDT time-out (not<br>from Sleep)              |

| 0    | 0               | 1  | 0  | MCLR wake-up from Sleep                       |

| 0    | 0               | 1  | 1  | Power-up                                      |

| 0    | 0               | u  | u  | MCLR not during<br>Sleep                      |

| 0    | 1               | 1  | 0  | Wake-up from Sleep on pin change              |

| 1    | 0               | 1  | 0  | Wake-up from Sleep<br>on comparator<br>change |

Legend: u = unchanged

### 10.8 Reset on Brown-out

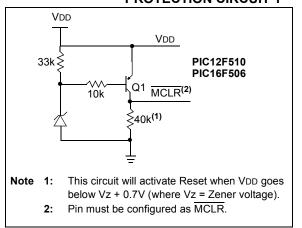

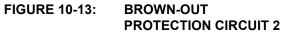

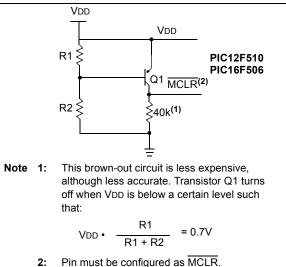

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset PIC12F510/16F506 devices when a brownout occurs, external brown-out protection circuits may be built, as shown in Figure 10-12 and Figure 10-13.

#### FIGURE 10-12: BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 10-14: BROWN-OUT PROTECTION CIRCUIT 3

| DC Cha       | aracteris    | tics                                                            |       |                    |             |          | ns (unless otherwise specified)<br>TA $\leq$ +125°C (extended)                                                     |

|--------------|--------------|-----------------------------------------------------------------|-------|--------------------|-------------|----------|--------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym          | Characteristic                                                  | Min   | Typ <sup>(1)</sup> | Max         | Units    | Conditions                                                                                                         |

| D001         | Vdd          | Supply Voltage                                                  | 2.0   |                    | 5.5         | V        | See Figure 14-1                                                                                                    |

| D002         | Vdr          | RAM Data Retention Voltage <sup>(2)</sup>                       | _     | 1.5*               |             | V        | Device in Sleep mode                                                                                               |

| D003         | VPOR         | VDD Start Voltage to ensure<br>Power-on Reset                   | —     | Vss                |             | V        | See Section 10.4 "Power-on<br>Reset (POR)" for details                                                             |

| D004         | SVDD         | VDD Rise Rate to ensure<br>Power-on Reset                       | 0.05* | _                  |             | V/ms     | See Section 10.4 "Power-on<br>Reset (POR)" for details                                                             |

| D010         | IDD          | Supply Current <sup>(3,4)</sup>                                 |       | 175<br>0.625       | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, VDD = 2.0V<br>Fosc = 4 MHz, VDD = 5.0V                                                               |

|              |              |                                                                 | _     | 250<br>1.0         | 450<br>1.5  | μA<br>mA | Fosc = 8 MHz, Vdd = 2.0V<br>Fosc = 8 MHz, Vdd = 5.0V                                                               |

|              |              |                                                                 | _     | 1.4                | 2.0         | mA       | Fosc = 20 MHz, VDD = 5.0V                                                                                          |

|              |              |                                                                 | _     | 11<br>38           | 16<br>54    | μΑ<br>μΑ | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                                                             |

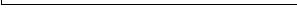

| D020         | IPD          | Power-down Current <sup>(5)</sup>                               | _     | 0.1<br>0.35        | 9.0<br>15.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                                                           |

| D022         | Iwdt         | WDT Current <sup>(5)</sup>                                      | _     | 1.0<br>7.0         | 18<br>22    | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                                                           |

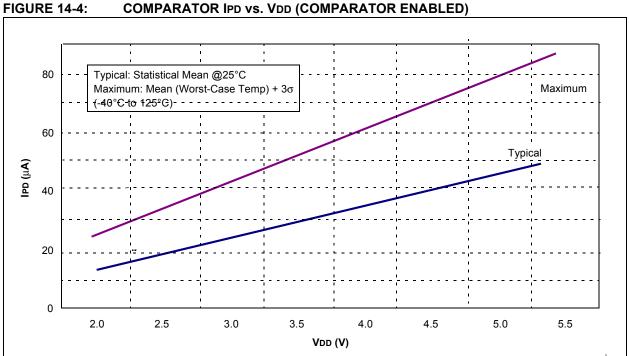

| D023         | ICMP         | Comparator Current <sup>(5)</sup>                               | _     | 15<br>55           | 25<br>75    | μΑ<br>μΑ | VDD = 2.0V (per comparator)<br>VDD = 5.0V (per comparator)                                                         |

| D022         | ICVREF       | CVREF Current <sup>(5)</sup>                                    | _     | 30<br>75           | 65<br>135   | μΑ<br>μΑ | VDD = 2.0V (high range)<br>VDD = 5.0V (high range)                                                                 |

| D023         | IFVR         | Internal 0.6V Fixed Voltage<br>Reference Current <sup>(5)</sup> | _     | 85<br>175          | 130<br>220  | μΑ<br>μΑ | VDD = 2.0V (0.6V reference and<br>1 comparator enabled)<br>VDD = 5.0V (0.6V reference and<br>1 comparator enabled) |

| D024         | $\Delta$ IAD | A/D Conversion Current <sup>(5)</sup>                           | _     | 120                | 150         | μA       | 2.0V                                                                                                               |

|              |              |                                                                 | _     | 200                | 250         | μA       | 5.0V                                                                                                               |

#### 13.2 DC Characteristics: PIC12F510/16F506 (Extended)

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- 4: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- **5:** For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

- **6:** Does not include current through REXT. The current through the resistor can be estimated by the formula: I = VDD/2REXT (mA) with REXT in kΩ.

#### FIGURE 14-14: DEVICE RESET TIMER (HS, XT AND LP) vs. VDD

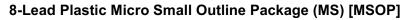

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |              | MILLIMETERS |      |      |

|--------------------------|--------------|-------------|------|------|

| Dimer                    | nsion Limits | MIN         | NOM  | MAX  |

| Number of Pins           | N            | 8           |      |      |

| Pitch                    | е            | 0.65 BSC    |      |      |

| Overall Height           | A            | -           | -    | 1.10 |

| Molded Package Thickness | A2           | 0.75        | 0.85 | 0.95 |

| Standoff                 | A1           | 0.00        | -    | 0.15 |

| Overall Width            | E            | 4.90 BSC    |      |      |

| Molded Package Width     | E1           | 3.00 BSC    |      |      |

| Overall Length           | D            | 3.00 BSC    |      |      |

| Foot Length              | L            | 0.40        | 0.60 | 0.80 |

| Footprint                | L1           | 0.95 REF    |      |      |

| Foot Angle               | φ            | 0°          | -    | 8°   |

| Lead Thickness           | С            | 0.08        | -    | 0.23 |

| Lead Width               | b            | 0.22        | -    | 0.40 |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111B

### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:   | Technical Publications Manager                                                           | Total Pages Sent                                  |  |  |  |

|-------|------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|

| RE:   | Reader Response                                                                          |                                                   |  |  |  |

| From  | Name                                                                                     |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

|       | Address                                                                                  |                                                   |  |  |  |

|       | City / State / ZIP / Country                                                             |                                                   |  |  |  |

|       | Telephone: ()                                                                            | FAX: ()                                           |  |  |  |

| Appli | cation (optional):                                                                       |                                                   |  |  |  |

| Woul  | d you like a reply?YN                                                                    |                                                   |  |  |  |

| Devic | e: PIC12F510/16F506                                                                      | Literature Number: DS41268D                       |  |  |  |

| Ques  | tions:                                                                                   |                                                   |  |  |  |

| 1. V  | 1. What are the best features of this document?                                          |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

| 2. H  | 2. How does this document meet your hardware and software development needs?             |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

| _     |                                                                                          |                                                   |  |  |  |

| 3. D  | Do you find the organization of this document easy to follow? If not, why?               |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

| 4. V  | Vhat additions to the document do y                                                      | ou think would enhance the structure and subject? |  |  |  |

| _     |                                                                                          |                                                   |  |  |  |

| _     |                                                                                          |                                                   |  |  |  |

| 5. V  | What deletions from the document could be made without affecting the overall usefulness? |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

| 6. Is | 5. Is there any incorrect or misleading information (what and where)?                    |                                                   |  |  |  |

| _     |                                                                                          |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

| 7. H  | . How would you improve this document?                                                   |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |

|       |                                                                                          |                                                   |  |  |  |