# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

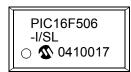

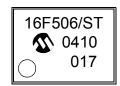

| 201010                     |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 67 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f506-i-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Міскоснір PIC12F510/16F506

# 8/14-Pin, 8-Bit Flash Microcontroller

# **Devices Included In This Data Sheet:**

- PIC16F506

- PIC12F510

# High-Performance RISC CPU:

- · Only 33 Single-Word Instructions to Learn

- All Single-Cycle Instructions except for Program Branches, which are Two-Cycle

- 12-Bit Wide Instructions

- Two-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- · 8-Bit Wide Data Path

- 10 Special Function Hardware Registers (PIC12F510)

- 13 Special Function Hardware Registers (PIC16F506)

- · Operating Speed:

- DC 8 MHz Crystal Oscillator (PIC12F510)

- DC 500 ns instruction cycle (PIC12F510)

- DC 20 MHz Crystal Oscillator (PIC16F506)

- DC 200 ns instruction cycle (PIC16F506)

### **Special Microcontroller Features:**

- 4 or 8 MHz Selectable Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debugging (ICD) Support

- Power-on Reset (POR)

- Device Reset Timer (DRT):

- Short DRT (1.125 ms, typical) for INTOSC, EXTRC and EC

- DRT (18 ms, typical) for HS, XT and LP

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

- · Selectable Internal Weak Pull-Ups on I/O Pins

- · Power-Saving Sleep mode

- Wake-up from Sleep on Pin Change

- · Wake-up from Sleep on Comparator Change

- · Selectable Oscillator Options:

- INTOSC: 4/8 MHz precision Internal oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- LP: Power-saving, low-frequency crystal

- HS: High-speed crystal/resonator (PIC16F506 only)

- EC: High-speed external clock input (PIC16F506 only)

- Analog-to-Digital (A/D) Converter:

- 8-bit resolution

- 4-input channels (1 channel is dedicated to conversion of the internal 0.6V absolute voltage reference)

- High Current Sink/Source for Direct LED Drive

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

### Low-Power Features/CMOS Technology:

- Operating Current:

- < 175 μA @ 2V, 4 MHz, typical

- Standby Current:

- 100 nA @ 2V, typical

- · Low-Power, High-Speed Flash Technology:

- 100,000 cycle Flash endurance

- > 40-year retention

- Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V

- Wide Temperature Range:

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

# Peripheral Features (PIC12F510):

- 6 I/O Pins:

- 5 I/O pins with individual direction control

- 1 input only pin

- 1 Analog Comparator with Absolute Reference

### Peripheral Features (PIC16F506):

- 12 I/O Pins:

- 11 I/O pins with individual direction control

- 1 input only pin

- 2 Analog Comparators with Absolute Reference and Programmable Reference

NOTES:

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12F510/16F506 devices can be attributed to a number of architectural features commonly found in RISC microprocessors. The PIC12F510/16F506 devices use a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architectures where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide, making it possible to have all single-word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (200 ns @ 20 MHz, 1 µs @ 4 MHz) except for program branches.

Table 3-1 lists program memory (Flash) and data memory (RAM) for the PIC12F510/16F506 devices.

| TABLE 3-1: PIC12F510/16F506 MEMORY |

|------------------------------------|

|------------------------------------|

| Device    | Men       | nory   |

|-----------|-----------|--------|

| Device    | Program   | Data   |

| PIC12F510 | 1024 x 12 | 38 x 8 |

| PIC16F506 | 1024 x 12 | 67 x 8 |

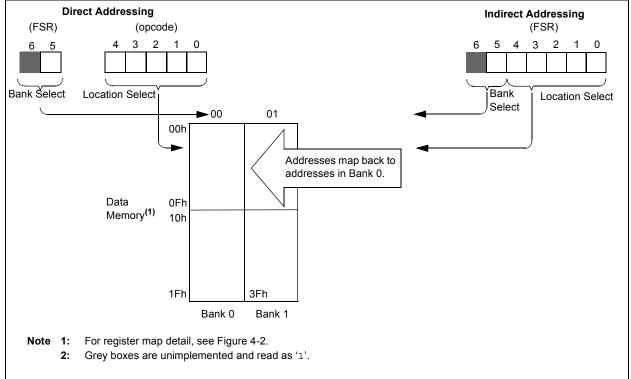

The PIC12F510/16F506 devices can directly or indirectly address its register files and data memory. All Special Function Registers (SFRs), including the PC, are mapped in the data memory. The PIC12F510/ 16F506 devices have a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any addressing mode. This symmetrical nature and lack of "special optimal situations" make programming with the PIC12F510/16F506 devices simple, yet efficient. In addition, the learning curve is reduced significantly.

The PIC12F510/16F506 devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file. The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, one operand is typically the W (working) register. The other operand is either a file register or an immediate constant. In single-operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC) and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1 for PIC12F510 with the corresponding device pins described in Table 3-2. A simplified block diagram for PIC16F506 is shown in Figure 3-2 with the corresponding device pins described in Table 3-3.

| REGISTER 4-2: | STATUS: STATUS REGISTER (PIC16F506) |

|---------------|-------------------------------------|

|---------------|-------------------------------------|

| R/W-0           | R/W-0                                         | R/W-0                                  | R-1                             | R-1                 | R/W-x               | R/W-x              | R/W-x         |

|-----------------|-----------------------------------------------|----------------------------------------|---------------------------------|---------------------|---------------------|--------------------|---------------|

| RBWUF           | CWUF                                          | PA0                                    | TO                              | PD                  | Z                   | DC                 | С             |

| bit 7           |                                               |                                        |                                 |                     | ·                   | •                  | bit           |

|                 |                                               |                                        |                                 |                     |                     |                    |               |

| Legend:         |                                               |                                        |                                 |                     |                     |                    |               |

| R = Readable    | bit                                           | W = Writable b                         | it                              | U = Unimpler        | mented bit, read as | s '0'              |               |

| -n = Value at F | POR                                           | '1' = Bit is set                       |                                 | '0' = Bit is cle    | ared                | x = Bit is unkno   | wn            |

| bit 7           | <b>RBWUF</b> : POR                            | TP Dooot bit                           |                                 |                     |                     |                    |               |

|                 | 1 = Reset due                                 | to wake-up from<br>er-up or other Res  |                                 | hange               |                     |                    |               |

| bit 6           | •                                             | arator Reset bit                       |                                 |                     |                     |                    |               |

|                 | •                                             | to wake-up from                        | Sleep on com                    | parator change      |                     |                    |               |

|                 | 0 = After powe                                | er-up or other Res                     | set                             | -                   |                     |                    |               |

| bit 5           | -                                             | Page Preselect I                       | oit                             |                     |                     |                    |               |

|                 | 1 = Page 1 (20                                | ,                                      |                                 |                     |                     |                    |               |

|                 | 0 = Page 0 (00<br>Each page is 5              | ,                                      |                                 |                     |                     |                    |               |

|                 |                                               |                                        | purpose read/v                  | vrite bit in device | es which do not us  | e it for program p | age preselect |

|                 | not recommen                                  | ided, since this m                     | ay affect upwa                  | rd compatibility    | with future produc  | ts.                |               |

| bit 4           | <b>TO</b> : Time-Out                          |                                        |                                 |                     |                     |                    |               |

|                 |                                               | er-up, CLRWDT ins                      | struction, or SL                | EEP instruction     |                     |                    |               |

|                 |                                               | ne-out occurred                        |                                 |                     |                     |                    |               |

| bit 3           | PD: Power-Do                                  |                                        |                                 |                     |                     |                    |               |

|                 | •                                             | er-up or by the CL<br>ion of the SLEEP |                                 | on                  |                     |                    |               |

| bit 2           | <b>Z</b> : Zero bit                           | on of the Sheer                        | instruction                     |                     |                     |                    |               |

|                 |                                               | of an arithmetic                       | or logic operatio               | on is zero          |                     |                    |               |

|                 |                                               | of an arithmetic of                    | • •                             |                     |                     |                    |               |

| bit 1           | DC: Digit Carr                                | y/Borrow bit (for a                    | ADDWF and SUE                   | WF instructions     | )                   |                    |               |

|                 | ADDWF:                                        |                                        |                                 |                     |                     |                    |               |

|                 |                                               | m the 4th low-ord                      |                                 |                     |                     |                    |               |

|                 | ,                                             | m the 4th low-ord                      | der bit of the re               | sult did not occu   | ır                  |                    |               |

|                 | $\frac{\text{SUBWF}}{1 = A \text{ borrow f}}$ | rom the 4th low-c                      | order bit of the                | result did not oc   | cur                 |                    |               |

|                 |                                               | rom the 4th low-o                      |                                 |                     |                     |                    |               |

| bit 0           | C: Carry/Borro                                | w bit (for ADDWF,                      | SUBWF and RR                    | F, RLF instruction  | ons)                |                    |               |

|                 | ADDWF:                                        |                                        | UBWF:                           | -                   | RRF or RLF:         |                    |               |

|                 | 1 = A carry oc<br>0 = A carry did             |                                        | = A borrow did<br>= A borrow oc |                     | Load bit with LSb   | or MSb, respectiv  | ely           |

|                 | 0 - A carry uit                               |                                        |                                 | ouncu               |                     |                    |               |

# 4.8 Indirect Data Addressing: INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

## 4.8.1 INDIRECT ADDRESSING EXAMPLE

- · Register file 07 contains the value 10h

- · Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-1.

# EXAMPLE 4-1:

#### -1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT   | MOVLW<br>MOVWF<br>CLRF<br>INCF<br>BTFSC<br>GOTO | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear INDF register<br>;inc pointer<br>;all done?<br>;NO, clear next |

|--------|-------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|

| CONTIN | UE                                              |                                               |                                                                                                         |

|        | :                                               |                                               | ;YES, continue                                                                                          |

|        | :                                               |                                               |                                                                                                         |

|        |                                                 |                                               |                                                                                                         |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16F506** – Uses FSR<6:5>. Selects from Bank 0 to Bank 3. FSR<7> is unimplemented, read as '1'.

**PIC12F510** – Uses FSR<5>. Selects from Bank 0 to Bank 1. FSR<7:6> are unimplemented, read as '11'.

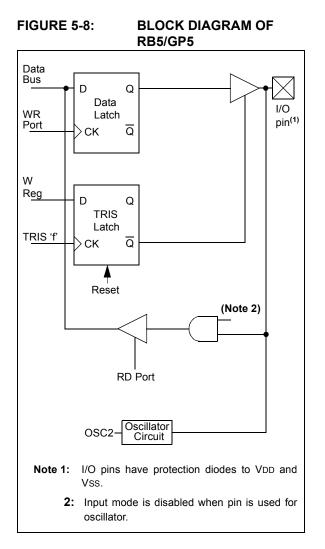

#### FIGURE 5-9: **BLOCK DIAGRAM OF** RC0/RC1 Data Bus D Q Data I/O WR Latch pin<sup>(1)</sup> P<u>ort</u> Q СК W Reg D Q TRIS Latch TRIS 'f' CK Q Reset Comp Pin Enable

RD Port

Vss.

COMP2

Note 1: I/O pins have protection diodes to VDD and

# TABLE 5-1: SUMMARY OF PORT REGISTERS

| Address | Name                    | Bit 7 | Bit 6 | Bit 5     | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|-------|-------|-----------|------------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | TRISGPIO <sup>(1)</sup> |       |       | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | TRISB <sup>(2)</sup>    | _     | —     | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | TRISC <sup>(2)</sup>    | _     | _     | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | OPTION <sup>(1)</sup>   | GPWU  | GPPU  | TOCS      | TOSE       | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup>   | RBWU  | RBPU  | TOCS      | TOSE       | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| 03h     | STATUS <sup>(1)</sup>   | GPWUF | CWUF  | PA0       | TO         | PD    | Z     | DC    | С     | 0001 1xxx                     | qq0q quuu <b>(3)</b>            |

| 03h     | STATUS <sup>(2)</sup>   | RBWUF | CWUF  | PA0       | TO         | PD    | Z     | DC    | С     | 0001 1xxx                     | qq0q quuu <sup>(3)</sup>        |

| 06h     | GPIO <sup>(1)</sup>     | _     | _     | GP5       | GP4        | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                         |

| 06h     | PORTB <sup>(2)</sup>    | —     | —     | RB5       | RB4        | RB3   | RB2   | RB1   | RB0   | xx xxxx                       | uu uuuu                         |

| 07h     | PORTC <sup>(2)</sup>    | _     |       | RC5       | RC4        | RC3   | RC2   | RC1   | RC0   | xx xxxx                       | uu uuuu                         |

$\label{eq:logend: Legend: Legend: -= unimplemented read as `0', x = unknown, u = unchanged, q = depends on condition.$

Note 1: PIC12F510 only.

2: PIC16F506 only.

3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

# TABLE 5-2: I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC16F506)

| Priority | RB0       | RB1       | RB2   | RB3        | RB4         | RB5        |

|----------|-----------|-----------|-------|------------|-------------|------------|

| 1        | AN0/C1IN+ | AN1/C1IN- | AN2   | Input/MCLR | OSC2/CLKOUT | OSC1/CLKIN |

| 2        | TRISB     | TRISB     | C10UT | —          | TRISB       | TRISB      |

| 3        | _         |           | TRISB | _          | _           |            |

# TABLE 5-3: I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC16F506)

| Priority | RC0   | RC1   | RC2   | RC3   | RC4   | RC5   |

|----------|-------|-------|-------|-------|-------|-------|

| 1        | C2IN+ | C2IN- | CVREF | TRISC | C2OUT | TOCKI |

| 2        | TRISC | TRISC | TRISC |       | TRISC | TRISC |

# TABLE 5-4:I/O PIN FUNCTION ORDER OF PRECEDENCE (PIC12F510)

| Priority | GP0       | GP1       | GP2    | GP3        | GP4    | GP5        |

|----------|-----------|-----------|--------|------------|--------|------------|

| 1        | AN0/C1IN+ | AN1/C1IN- | AN2    | Input/MCLR | OSC2   | OSC1/CLKIN |

| 2        | TRISIO    | TRISIO    | C10UT  | _          | TRISIO | TRISIO     |

| 3        | _         | —         | TOCKI  | _          | _      | _          |

| 4        |           | —         | TRISIO | —          | _      | _          |

| TABLE 5-6: RE  | EQUIREMENTS FOR DIGITAL PIN OPERATION (PIC16F506 PORTB)(1), (2) |       |       |          |          |     |     |     |          |          |  |  |  |

|----------------|-----------------------------------------------------------------|-------|-------|----------|----------|-----|-----|-----|----------|----------|--|--|--|

|                | RB0                                                             | RB0   | RB0   | RB1      | RB1      | RB2 | RB2 | RB3 | RB4      | RB5      |  |  |  |

| CM1CON0        |                                                                 |       |       |          |          |     |     |     |          |          |  |  |  |

| C10N           | —                                                               | 0     | 1     | 0        | 1        | 0   | 1   |     | —        | _        |  |  |  |

| C1PREF         | _                                                               | _     | 0     |          |          |     | _   |     |          |          |  |  |  |

| C1NREF         | —                                                               | _     | _     | —        | 0        |     | _   | _   | —        |          |  |  |  |

| C1T0CS         | —                                                               | _     |       | _        | —        |     | _   |     | —        | _        |  |  |  |

| C1OUTEN        | —                                                               | _     |       | _        | —        | —   | 1   | —   | _        | _        |  |  |  |

| CM2CON0        |                                                                 |       |       |          |          |     |     |     |          |          |  |  |  |

| C2ON           | 1                                                               | —     | —     | —        | —        | _   | _   |     | —        | _        |  |  |  |

| C2PREF1        | 0                                                               | _     | _     | _        | _        |     | _   | _   | —        |          |  |  |  |

| C2PREF2        | 1                                                               | —     | _     | _        | —        | _   | —   | _   | —        | _        |  |  |  |

| C2NREF         | —                                                               | _     | —     | _        | —        |     | _   | _   | —        | _        |  |  |  |

| C2OUTEN        | —                                                               | _     | _     | _        | _        | _   | _   | _   | -        | _        |  |  |  |

| OPTION         |                                                                 |       |       |          |          |     |     |     |          |          |  |  |  |

| TOCS           | —                                                               |       |       |          |          | _   |     |     | —        |          |  |  |  |

| ADCON0         |                                                                 |       |       |          |          |     |     |     |          |          |  |  |  |

| ANS<1:0>       | 00, 01                                                          | 00,01 | 00,01 | 00,01,10 | 00,01,10 | 00  | 00  | _   | —        |          |  |  |  |

| CONFIG         |                                                                 |       |       |          |          |     |     |     |          |          |  |  |  |

| MCLRE          | —                                                               | _     | —     | —        | —        |     | _   | 0   | —        | _        |  |  |  |

| INTOSC         | —                                                               | _     | —     | _        | —        |     | _   | _   | —        | _        |  |  |  |

| LP             | _                                                               | _     | _     | _        | _        |     | _   | _   | Disabled | Disabled |  |  |  |

| EXTRC          |                                                                 | —     | _     | _        | —        | _   | —   | _   | —        | Disabled |  |  |  |

| ХТ             |                                                                 |       |       |          |          |     | —   | —   | Disabled | Disabled |  |  |  |

| EC             |                                                                 | —     | —     | —        | —        | _   | —   | —   | —        | Disabled |  |  |  |

| HS             |                                                                 | —     |       | —        | —        | _   | —   | —   | Disabled | Disabled |  |  |  |

| INTOSC CLKOUT  |                                                                 | —     | —     | —        | —        | _   | —   | —   |          | Disabled |  |  |  |

| EXTRC CLOCKOUT | —                                                               | —     |       | —        |          | _   |     |     | Disabled | Disabled |  |  |  |

# TABLE 5-6: REQUIREMENTS FOR DIGITAL PIN OPERATION (PIC16F506 PORTB)<sup>(1), (2)</sup>

**Note 1:** Multiple column entries for a pin demonstrate the different permutations to arrive at digital functionality for the pin.

2: Shaded cells indicate the bit status does not affect the pins digital functionality.

# TABLE 5-7: REQUIREMENTS FOR DIGITAL PIN OPERATION (PIC16F506 PORTC)<sup>(1), (2)</sup>

|                  |             |             |          |            |           | •         |             |             | ,           |            |

|------------------|-------------|-------------|----------|------------|-----------|-----------|-------------|-------------|-------------|------------|

|                  | RC0         | RC0         | RC1      | RC1        | RC2       | RC3       | RC4         | RC4         | RC5         | RC5        |

| CM2CON0          |             |             |          |            |           |           |             |             |             |            |

| C2ON             | 0           | 1           | 0        | 1          |           |           | 0           | 1           |             |            |

| C2PREF1          |             | 0           |          |            | _         |           |             |             | _           |            |

| C2PREF2          | —           | 0           | —        |            | —         | —         | —           | —           | —           | —          |

| C2NREF           | —           | —           | —        | 0          | —         | —         | —           | —           | —           | —          |

| C2OUTEN          |             | —           | _        | _          | _         | _         | _           | 1           | _           |            |

| VRCON0           |             |             | •        |            |           |           |             |             |             |            |

| VROE             |             |             |          |            | 0         |           |             |             | _           |            |

| OPTION           | •           | -           | •        | •          |           |           |             |             |             |            |

| TOCS             | —           | —           | —        |            | _         | —         | _           | —           | 0           | —          |

| Note 1: Multiple | column entr | ies for a r | in demon | strata tha | different | normutati | one to arri | ve at digit | al function | nality for |

**Note 1:** Multiple column entries for a pin demonstrate the different permutations to arrive at digital functionality for the pin.

2: Shaded cells indicate the bit status does not affect the pins digital functionality.

#### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| PC<br>(Program<br>Counter)<br>Instruction<br>Fetch | Q1 Q2 Q3 Q4<br>( | <u>Х РС </u> | ( PC + 1                          | PC + 2                 | Y PC + 3                      | PC + 4                 | Q1 Q2 Q3 Q4<br>( <u>PC+5</u> )<br>MOVF TMR0,W | Q1 Q2 Q3 Q4;<br>X PC + 6              |

|----------------------------------------------------|------------------|--------------|-----------------------------------|------------------------|-------------------------------|------------------------|-----------------------------------------------|---------------------------------------|

| Timer0<br>Instruction<br>Executed                  | ()               | Τ0 + 1 )     | T0 + 2)<br>Write TMR0<br>executed | Read TMR0<br>reads NT0 | NT0<br>Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | NT0 + 1)                                      | NT0 + 2<br>Read TMR0<br>reads NT0 + 2 |

#### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

| (Program<br>Counter)    | ( PC - 1    |            | ↓ Q1 Q2 Q3 Q4<br>X PC + 1 | PC + 2                 | PC + 3      | PC + 4                 | PC+5        | ( PC + 6 )                                                                                                          |

|-------------------------|-------------|------------|---------------------------|------------------------|-------------|------------------------|-------------|---------------------------------------------------------------------------------------------------------------------|

| Instruction<br>Fetch    | ,<br>!<br>! | MOVWF TMR0 | MOVF TMR0,W               | MOVF TMR0,W            | MOVF TMR0,W | MOVF TMR0,W            | MOVF TMR0,W | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| Timer0                  | χ           | T0 + 1     |                           | ,<br>,<br>,            | NT0         |                        |             | NT0 + 1                                                                                                             |

| Instruction<br>Executed | 1<br>1<br>1 |            |                           |                        | Read TMR0   |                        | Read TMR0   |                                                                                                                     |

|                         | 1           | •          | Write TMR0<br>executed    | Read TMR0<br>reads NT0 | reads NT0   | Read TMR0<br>reads NT0 |             | Read TMR0<br>reads NT0 + 2                                                                                          |

#### TABLE 6-1: **REGISTERS ASSOCIATED WITH TIMER0**

| Addr | Name                    | Bit 7      | Bit 6                                  | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|------|-------------------------|------------|----------------------------------------|-----------|-------------|-------|--------|--------|-----------|-------------------------------|---------------------------------|

| 01h  | TMR0                    | Timer0 – 8 | Fimer0 – 8-bit Real-Time Clock/Counter |           |             |       |        |        | XXXX XXXX | uuuu uuuu                     |                                 |

| 07h  | CM1CON0 <sup>(2)</sup>  | C10UT      | C10UTEN                                | C1POL     | C1T0CS      | C10N  | C1NREF | C1PREF | C1WU      | 1111 1111                     | uuuu uuuu                       |

| 08h  | CM1CON0 <sup>(3)</sup>  | C10UT      | C10UTEN                                | C1POL     | C1T0CS      | C10N  | C1NREF | C1PREF | C1WU      | 1111 1111                     | uuuu uuuu                       |

| N/A  | OPTION                  | GPWU       | GPPU                                   | TOCS      | T0SE        | PSA   | PS2    | PS1    | PS0       | 1111 1111                     | 1111 1111                       |

| N/A  | TRISGPIO <sup>(1)</sup> | _          | _                                      | I/O Contr | ol Register |       |        |        |           | 1111                          | 11 1111                         |

**Shaded cells not used by Timer0**, - = unimplemented, x = unknown, u = unchanged. **Note 1:** The TRIS of the TOCKI pin is overridden when TOCS = 1. Legend:

2: For PIC12F510.

3: For PIC16F506.

| R-1        | R/W-1                                                                                                                  | R/W-1                       | R/W-1           | R/W-1                     | R/W-1           | R/W-1           | R/W-1 |

|------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|---------------------------|-----------------|-----------------|-------|

| C10U       | T C1OUTEN                                                                                                              | C1POL                       | C1T0CS          | C10N                      | C1NREF          | C1PREF          | C1WU  |

| bit 7      |                                                                                                                        |                             |                 |                           |                 |                 | bit ( |

|            |                                                                                                                        |                             |                 |                           |                 |                 |       |

| Legend:    |                                                                                                                        |                             |                 |                           |                 |                 |       |

| R = Reada  |                                                                                                                        | W = Writable                |                 |                           | mented bit, rea |                 |       |

| -n = Value | at POR                                                                                                                 | '1' = Bit is set            | t               | '0' = Bit is cle          | eared           | x = Bit is unkn | own   |

| bit 7      | C1OUT: Com                                                                                                             | parator Output              | t bit           |                           |                 |                 |       |

|            | 1 = VIN + > VII                                                                                                        | -                           |                 |                           |                 |                 |       |

|            | 0 = VIN + < VII                                                                                                        |                             |                 | (4) (2)                   |                 |                 |       |

| bit 6      |                                                                                                                        | Comparator Ou               |                 |                           |                 |                 |       |

|            |                                                                                                                        | comparator is comparator is |                 |                           | pin             |                 |       |

| bit 5      | •                                                                                                                      | parator Output              | •               | •                         |                 |                 |       |

| DIUD       |                                                                                                                        | comparator is               | •               |                           |                 |                 |       |

|            |                                                                                                                        | comparator is               |                 |                           |                 |                 |       |

| bit 4      | C1T0CS: Cor                                                                                                            | nparator TMR                | Clock Source    | e bit <sup>(2)</sup>      |                 |                 |       |

|            | 1 = TMR0 clo                                                                                                           | ck source sele              | cted by T0CS    | control bit               |                 |                 |       |

|            | 0 = Compara                                                                                                            | tor output used             | d as TMR0 clo   | ck source                 |                 |                 |       |

| bit 3      |                                                                                                                        | arator Enable               | bit             |                           |                 |                 |       |

|            | 1 = Compara                                                                                                            |                             |                 |                           |                 |                 |       |

|            | 0 = Compara                                                                                                            |                             |                 | <b>2 1 1 1 1 (2)</b>      |                 |                 |       |

| bit 2      | 1 = C1IN- pin                                                                                                          | mparator Nega               | ative Reference | e Select bit(-)           |                 |                 |       |

|            | 0 = 0.6V inter                                                                                                         |                             |                 |                           |                 |                 |       |

| bit 1      |                                                                                                                        |                             | ive Reference   | Select bit <sup>(2)</sup> |                 |                 |       |

|            | <b>C1PREF:</b> Comparator Positive Reference Select bit <sup>(2)</sup><br>1 = C1IN+ pin                                |                             |                 |                           |                 |                 |       |

|            | 0 = C1IN- pin                                                                                                          |                             |                 |                           |                 |                 |       |

| bit 0      | C1WU: Comparator Wake-up On Change Enable bit <sup>(2)</sup>                                                           |                             |                 |                           |                 |                 |       |

|            | <ol> <li>Wake-up On Comparator Change is disabled</li> <li>Wake-up On Comparator Change is enabled</li> </ol>          |                             |                 |                           |                 |                 |       |

|            | •                                                                                                                      | •                           | •               | nabled                    |                 |                 |       |

| Note 1:    | Overrides T0CS b                                                                                                       |                             |                 |                           |                 |                 |       |

| 2:         | When comparator is turned on, these control bits assert themselves. Otherwise, the other registers have<br>precedence. |                             |                 |                           |                 |                 |       |

# REGISTER 7-2: CM1CON0: COMPARATOR C1 CONTROL REGISTER (PIC16F506)

# 9.0 ANALOG-TO-DIGITAL (A/D) CONVERTER

The A/D Converter allows conversion of an analog signal into an 8-bit digital signal.

# 9.1 Clock Divisors

The ADC has 4 clock source settings ADCS<1:0>. There are 3 divisor values 16, 8 and 4. The fourth setting is INTOSC with a divisor of 4. These settings will allow a proper conversion when using an external oscillator at speeds from 20 MHz to 350 kHz. Using an external oscillator at a frequency below 350 kHz (TAD > 50  $\mu$ s) requires the ADC oscillator setting to be INTOSC/4 for valid ADC results.

The ADC requires 13 TAD periods to complete a conversion. The divisor values do not affect the number of TAD periods required to perform a conversion. The divisor values determine the length of the TAD period.

When the ADCS<1:0> bits are changed while an ADC conversion is in process, the new ADC clock source will not be selected until the next conversion is started. This clock source selection will be lost when the device enters Sleep.

## 9.1.1 VOLTAGE REFERENCE

There is no external voltage reference for the ADC. The ADC reference voltage will always be VDD.

# 9.1.2 ANALOG MODE SELECTION

The ANS<1:0> bits are used to configure pins for analog input. Upon any Reset, ANS<1:0> defaults to 11. This configures pins ANO, AN1 and AN2 as analog inputs. Pins configured as analog inputs are not available for digital output. Users should not change the ANS bits while a conversion is in process. ANS bits are active regardless of the condition of ADON.

### 9.1.3 ADC CHANNEL SELECTION

The CHS bits are used to select the analog channel to be sampled by the ADC. The CHS<1:0> bits can be changed at any time without adversely effecting a conversion. To acquire an analog signal the CHS<1:0> selection must match one of the pin(s) selected by the ANS<1:0> bits. When the ADC is on (ADON = 1) and a channel is selected that is also being used by the comparator, then both the comparator and the ADC will see the analog voltage on the pin.

Note: It is the users responsibility to ensure that use of the ADC and comparator simultaneously on the same pin, does not adversely affect the signal being monitored or adversely effect device operation. When the CHS<1:0> bits are changed during an ADC conversion, the new channel will not be selected until the current conversion is completed. This allows the current conversion to complete with valid results. All channel selection information will be lost when the device enters Sleep.

| <b>TABLE 9-1</b> : | CHANNEL SELECT (ADCS) |

|--------------------|-----------------------|

|                    | BITS AFTER AN EVENT   |

| Event                 | ADCS<1:0> |

|-----------------------|-----------|

| MCLR                  | 11        |

| Conversion completed  | CS<1:0>   |

| Conversion terminated | CS<1:0>   |

| Power-on              | 11        |

| Wake from Sleep       | 11        |

# 9.1.4 THE GO/DONE BIT

The GO/DONE bit is used to determine the status of a conversion, to start a conversion and to manually halt a conversion in process. Setting the GO/DONE bit starts a conversion. When the conversion is complete, the ADC module clears the GO/DONE bit. A conversion can be terminated by manually clearing the GO/DONE bit while a conversion is in process. Manual termination of a conversion may result in a partially converted result in ADRES.

The GO/DONE bit is cleared when the device enters Sleep, stopping the current conversion. The ADC does not have a dedicated oscillator, it runs off of the instruction clock. Therefore, no conversion can occur in sleep.

The GO/DONE bit cannot be set when ADON is clear.

<sup>© 2007</sup> Microchip Technology Inc.

#### 9.1.6 ANALOG CONVERSION RESULT REGISTER

The ADRES register contains the results of the last conversion. These results are present during the sampling period of the next analog conversion process. After the sampling period is over, ADRES is cleared (= 0). A 'leading one' is then right shifted into the ADRES to serve as an internal conversion complete bit. As each bit weight, starting with the MSB, is converted, the leading one is shifted right and the converted bit is stuffed into ADRES. After a total of 9 right

shifts of the 'leading one' have taken place, the conversion is complete; the 'leading one' has been shifted out and the GO/DONE bit is cleared.

If the GO/DONE bit is cleared in software during a conversion, the conversion stops. The data in ADRES is the partial conversion result. This data is valid for the bit weights that have been converted. The position of the 'leading one' determines the number of bits that have been converted. The bits that were not converted before the GO/DONE was cleared are unrecoverable.

## REGISTER 9-1: ADCON0: A/D CONTROL REGISTER (PIC12F510)

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|---------|-------|

| ANS1  | ANS0  | ADCS1 | ADCS0 | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |       |       |       |       |       |         | bit 0 |

| Legend:            |                                                    |                                                                                                                                                                  |                                                                                                          |                                                                                                                       |  |

|--------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| R = Readable bit   |                                                    | W = Writable bit                                                                                                                                                 | U = Unimplemented bit, read as '0'                                                                       |                                                                                                                       |  |

| -n = Value         | e at POR                                           | '1' = Bit is set                                                                                                                                                 | '0' = Bit is cleared                                                                                     | x = Bit is unknown                                                                                                    |  |

| bit 7-6            | 00 = No<br>01 = AN<br>10 = AN                      | <b>0&gt;:</b> ADC Analog Input Pin S<br>pins configured for analog in<br>2 configured as an analog ir<br>2 and AN0 configured as an<br>2, AN1 and AN0 configured | nput<br>iput<br>alog inputs                                                                              |                                                                                                                       |  |

| bit 5-4            | ADCS<<br>00 = FO<br>01 = FO<br>10 = FO<br>11 = IN  | sc/8<br>sc/4                                                                                                                                                     | s Select bits                                                                                            |                                                                                                                       |  |

| bit 3-2            | 00 = Ch<br>01 = Ch<br>10 = Ch                      | <b>0&gt;:</b> ADC Channel Select bits<br>annel AN0<br>annel AN1<br>annel AN2<br>V absolute voltage reference                                                     |                                                                                                          |                                                                                                                       |  |

| bit 1              | 1 = AD0<br>auto<br>0 = AD0                         | omatically cleared by hardwa                                                                                                                                     | Setting this bit starts an Al<br>are when the ADC is done con<br>in progress. Manually clearin           | DC conversion cycle. This bit<br>verting.<br>Ig this bit while a conversion is                                        |  |

| bit 0              | 1 = AD0                                            | ADC Enable bit<br>C module is operating<br>C module is shut-off and con                                                                                          | sumes no power                                                                                           |                                                                                                                       |  |

| Note 1:<br>2:      | less of the pir<br>input to the co<br>that the ADC | n function previously defined omparator and the ADC will b                                                                                                       | . The only exception to this is<br>be active at the same time. It is<br>nput does not affect their appli | forced into Analog mode, regard-<br>the comparator, where the analog<br>the users responsibility to ensur-<br>cation. |  |

| 3:                 |                                                    | s default to 11 after any Res                                                                                                                                    |                                                                                                          |                                                                                                                       |  |

| <u></u> <i>A</i> . |                                                    | hit is clear the GO/DONE hit                                                                                                                                     | cannot ha sat                                                                                            |                                                                                                                       |  |

4: If the ADON bit is clear, the GO/DONE bit cannot be set.

## 10.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- · WDT Time-out Reset during normal operation

- · WDT Time-out Reset during Sleep

- Wake-up from Sleep Reset on pin change

- Wake-up from Sleep Reset on comparator change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up from Sleep Reset on pin change or wake-up from Sleep Reset on comparator change. The exceptions are TO, PD, CWUF and RBWUF/GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 10-4 for a full description of Reset states of all registers.

| Register | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change, Wake-up on<br>Comparator Change |

|----------|---------|--------------------------|-------------------------------------------------------------------------------------|

| W        | —       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                                                            |

| INDF     | 00h     | xxxx xxxx                | <u>uuuu</u> uuuu                                                                    |

| TMR0     | 01h     | xxxx xxxx                | uuuu uuuu                                                                           |

| PCL      | 02h     | 1111 1111                | 1111 1111                                                                           |

| STATUS   | 03h     | 0001 1xxx                | qq0q quuu <sup>(2)</sup>                                                            |

| FSR      | 04h     | 110x xxxx                | 11uu uuuu                                                                           |

| OSCCAL   | 05h     | 1111 111-                | uuuu uuu-                                                                           |

| GPIO     | 06h     | xx xxxx                  | uu uuuu                                                                             |

| CM1CON0  | 07h     | 1111 1111                | uuuu uuuu                                                                           |

| ADCON0   | 08h     | 1111 1100                | uull 1100                                                                           |

| ADRES    | 09h     | xxxx xxxx                | uuuu uuuu                                                                           |

| OPTION   |         | 1111 1111                | 1111 1111                                                                           |

| TRISIO   |         | 11 1111                  | 11 1111                                                                             |

### TABLE 10-3: RESET CONDITIONS FOR REGISTERS – PIC12F510

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 10-5 for Reset value for specific conditions.

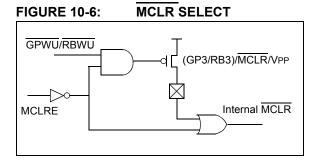

## 10.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external MCLR function. When programmed, the MCLR function is tied to the internal VDD and the pin is assigned to be a I/O. See Figure 10-6.

# 10.4 Power-on Reset (POR)

The PIC12F510/16F506 devices incorporate an onchip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. The POR is active regardless of the state of the MCLR enable bit. An internal weak pull-up resistor is implemented using a transistor (refer to Table 13-3 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create an external Power-on Reset. A maximum rise time for VDD is specified. See **Section 13.0 "Electrical Characteristics"** for details.

When the devices start normal operation (exit the Reset condition), device operating parameters (volt-age, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 10-7.

The Power-on Reset circuit and the Device Reset Timer (see Section 10.5 "Device Reset Timer (DRT)") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR, internal or external, to be high. After the time-out period, it will reset the Reset latch and thus end the on-chip Reset signal.

A power-up example where  $\overline{\text{MCLR}}$  is held low is shown in Figure 10-8. VDD is allowed to rise and stabilize before bringing  $\overline{\text{MCLR}}$  high. The chip will actually come out of Reset TDRT msec after  $\overline{\text{MCLR}}$  goes high.

In Figure 10-9, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be (GP3/RB3). The VDD is stable before the Start-up timer times out and there is no problem in getting a proper Reset. However, Figure 10-10 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 10-9).

| Note: | When the devices start normal operation (exit the Reset condition), device operat- |

|-------|------------------------------------------------------------------------------------|

|       | ing parameters (voltage, frequency,                                                |

|       | temperature, etc.) must be met to ensure                                           |

|       | operation. If these conditions are not met,                                        |

|       | the device must be held in Reset until the                                         |

|       | operating conditions are met.                                                      |

For additional information, refer to Application Notes AN522, *"Power-Up Considerations"* (DS00522) and AN607, *"Power-up Trouble Shooting"* (DS00607).

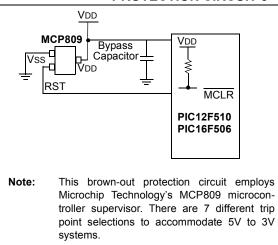

# 10.7 Time-out Sequence, Power-down and <u>Wake-up</u> from Sleep Status Bits (TO, PD, GPWUF/RBWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  and (GPWUF/RBWUF) bits in the STATUS register can be tested to determine if a Reset condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) Reset.

# TABLE 10-8: TO/PD/(GPWUF/RBWUF) STATUS AFTER RESET

| CWUF | GPWUF/<br>RBWUF | то | PD | Reset Caused By                               |

|------|-----------------|----|----|-----------------------------------------------|

| 0    | 0               | 0  | 0  | WDT wake-up from<br>Sleep                     |

| 0    | 0               | 0  | u  | WDT time-out (not<br>from Sleep)              |

| 0    | 0               | 1  | 0  | MCLR wake-up from Sleep                       |

| 0    | 0               | 1  | 1  | Power-up                                      |

| 0    | 0               | u  | u  | MCLR not during<br>Sleep                      |

| 0    | 1               | 1  | 0  | Wake-up from Sleep on pin change              |

| 1    | 0               | 1  | 0  | Wake-up from Sleep<br>on comparator<br>change |

Legend: u = unchanged

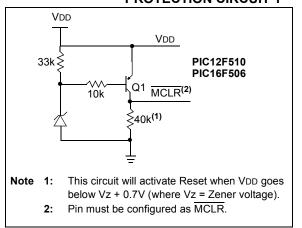

# 10.8 Reset on Brown-out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

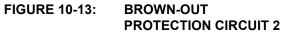

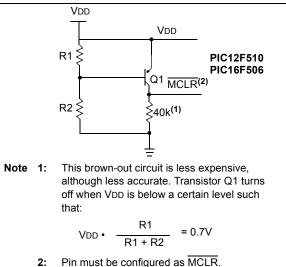

To reset PIC12F510/16F506 devices when a brownout occurs, external brown-out protection circuits may be built, as shown in Figure 10-12 and Figure 10-13.

## FIGURE 10-12: BROWN-OUT PROTECTION CIRCUIT 1

### FIGURE 10-14: BROWN-OUT PROTECTION CIRCUIT 3

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                  |

| Operation:       | $(f) - 1 \rightarrow (dest)$                                                                                                                      |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is 'o',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                           |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                               |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                |

| Operation:       | (f) – 1 $\rightarrow$ d; skip if result = 0                                                                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '0', the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '0', then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a<br>two-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                         |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                      |  |  |  |  |

| Operands:        | $0 \le k \le 511$                                                                                                                                                                            |  |  |  |  |

| Operation:       | $k \rightarrow PC<8:0>;$<br>STATUS <6:5> $\rightarrow PC<10:9>$                                                                                                                              |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                         |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS <6:5>. GOTO is a two-<br>cycle instruction. |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |  |  |  |

| Operation:       | (W) .OR. (k) $\rightarrow$ (W)                                                                                            |  |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |  |  |  |  |  |

| DC Characteristics |              | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |       |                    |             |          |                                                                                                                    |

|--------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-------------|----------|--------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym          | Characteristic                                                                                                                        | Min   | Typ <sup>(1)</sup> | Max         | Units    | Conditions                                                                                                         |

| D001               | Vdd          | Supply Voltage                                                                                                                        | 2.0   |                    | 5.5         | V        | See Figure 14-1                                                                                                    |

| D002               | Vdr          | RAM Data Retention Voltage <sup>(2)</sup>                                                                                             | _     | 1.5*               |             | V        | Device in Sleep mode                                                                                               |

| D003               | VPOR         | VDD Start Voltage to ensure<br>Power-on Reset                                                                                         | —     | Vss                |             | V        | See Section 10.4 "Power-on<br>Reset (POR)" for details                                                             |

| D004               | SVDD         | VDD Rise Rate to ensure<br>Power-on Reset                                                                                             | 0.05* | _                  |             | V/ms     | See Section 10.4 "Power-on<br>Reset (POR)" for details                                                             |

| D010               | IDD          | Supply Current <sup>(3,4)</sup>                                                                                                       |       | 175<br>0.625       | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, VDD = 2.0V<br>Fosc = 4 MHz, VDD = 5.0V                                                               |

|                    |              |                                                                                                                                       | _     | 250<br>1.0         | 450<br>1.5  | μA<br>mA | Fosc = 8 MHz, Vdd = 2.0V<br>Fosc = 8 MHz, Vdd = 5.0V                                                               |

|                    |              |                                                                                                                                       |       | 1.4                | 2.0         | mA       | Fosc = 20 MHz, VDD = 5.0V                                                                                          |