# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 67 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (3x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f506t-i-mg |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 4.0 MEMORY ORGANIZATION

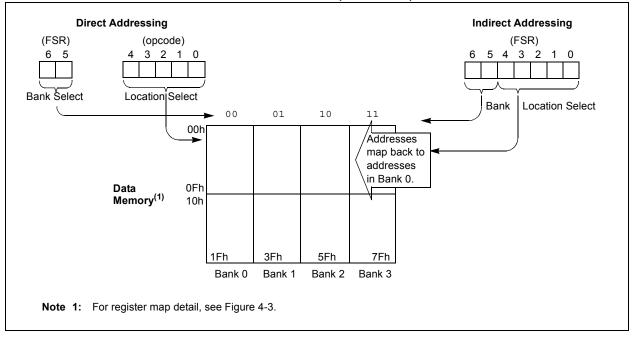

The PIC12F510/16F506 memories are organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using STATUS register bit PA0. For the PIC12F510 and PIC16F506, with data memory register files of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Select Register (FSR).

## 4.1 Program Memory Organization for the PIC12F510/16F506

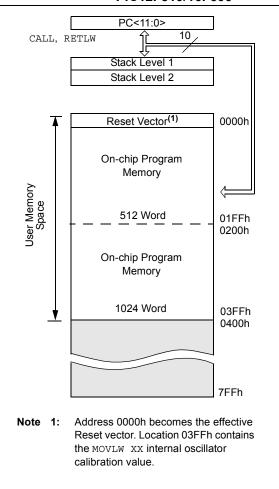

The PIC12F510/16F506 devices have a 10-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space.

Only the first 1K x 12 (0000h-03FFh) are physically implemented (see Figure 4-1). Accessing a location above these boundaries will cause a wraparound within the 1K x 12 space. The effective Reset vector is a 0000h (see Figure 4-1). Location 03FFh contains the internal clock oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-1:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC12F510/16F506

#### 4.4 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, that contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<7:0> bits.

- Note 1: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin (i.e., note that TRIS overrides Option control of GPPU/RBPU and GPWU/RBWU).

- **2:** If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

#### REGISTER 4-3: OPTION\_REG: OPTION REGISTER (PIC12F510)

| W-1   | W-1  | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|------|------|------|-----|-----|-----|-------|

| GPWU  | GPPU | TOCS | TOSE | PSA | PS2 | PS1 | PS0   |

| bit 7 |      |      |      |     |     |     | bit 0 |

| Legend:    |                                                                                                            |                                                             |                                                                           |                                    |                    |  |

|------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------|--------------------|--|

| R = Reada  | ble bit W = V                                                                                              | W = Writable bit                                            |                                                                           | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value | n = Value at POR (1' = Bit is set                                                                          |                                                             |                                                                           | = Bit is cleared                   | x = Bit is unknown |  |

| bit 7      | <b>GPWU:</b> Enable Wake-u<br>1 = Disabled<br>0 = Enabled                                                  | p On Pin Chang                                              | e bit (GP0, GP                                                            | 1, GP3)                            |                    |  |

| bit 6      | <b>GPPU:</b> Enable Weak Pu<br>1 = Disabled<br>0 = Enabled                                                 | ull-Ups bit (GP0,                                           | GP1, GP3)                                                                 |                                    |                    |  |

| bit 5      | <b>TOCS:</b> Timer0 Clock So<br>1 = Transition on TOCI<br>0 = Internal instruction                         | KI pin                                                      | KOUT)                                                                     |                                    |                    |  |

| bit 4      | <b>T0SE:</b> Timer0 Source E<br>1 = Increment on high<br>0 = Increment on low-1                            | -to-low transition                                          |                                                                           |                                    |                    |  |

| bit 3      | <ul> <li>PSA: Prescaler Assignr</li> <li>1 = Prescaler assigner</li> <li>0 = Prescaler assigner</li> </ul> | d to the WDT                                                |                                                                           |                                    |                    |  |

| bit 2-0    | PS<2:0>: Prescaler Rat                                                                                     | e Select bits                                               |                                                                           |                                    |                    |  |

|            | Bit Value                                                                                                  | Timer0 Rate                                                 | WDT Rate                                                                  |                                    |                    |  |

|            | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                       | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 |                                    |                    |  |

## 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

| Note: | On the PIC12F510, I/O PORTB is refer- |

|-------|---------------------------------------|

|       | enced as GPIO. On the PIC16F506, I/O  |

|       | PORTB is referenced as PORTB.         |

#### 5.1 PORTB/GPIO

PORTB/GPIO is an 8-bit I/O register. Only the loworder 6 bits are used (RB/GP<5:0>). Bits 7 and 6 are unimplemented and read as '0's. Please note that RB3/ GP3 is an input only pin. The Configuration Word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during a port read. Pins RB0/GP0, RB1/GP1, RB3/GP3 and RB4 (PIC16F506 only) can be configured with weak pull-up and also for wake-up on change. The wake-up on change and weak <u>pull-up</u> functions are not pin selectable. If RB3/GP3/MCLR is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

### 5.2 PORTC (PIC16F506 Only)

PORTC is an 8-bit I/O register. Only the low-order 6 bits are used (RC<5:0>). Bits 7 and 6 are unimplemented and read as '0's.

### 5.3 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exception is RB3/GP3, which are input only, and the TOCKI pin, which may be controlled by the OPTION register. See Register 4-3.

| Note: | A read of the port reads the pins, not the<br>output data latches. That is, if an output<br>driver on a pin is enabled and driven high |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|

|       | but the external system is holding it low, a<br>read of the port will indicate that the pin is<br>low.                                 |

**Note:** The TRIS registers are write-only and are set (output drivers disabled) upon Reset.

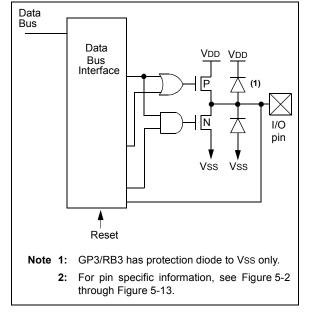

#### 5.4 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except RB3/GP3 which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except RB3/GP3) can be programmed individually as input or output.

FIGURE 5-1:

#### PIC12F510/16F506 EQUIVALENT CIRCUIT FOR PIN DRIVE<sup>(2)</sup>

NOTES:

### 7.0 COMPARATOR(S)

The PIC12F510 contains one analog comparator module. The PIC16F506 contains two comparators and a comparator voltage reference.

### REGISTER 7-1: CM1CON0: COMPARATOR C1 CONTROL REGISTER (PIC12F510)

| C1OUT         C1OUTEN         C1POL         C1TOCS         C1ON         C1NREF         C1PREF         C1WU           bit 7         bit 7 | R-1   | R/W-1   | R/W-1 | R/W-1  | R/W-1 | R/W-1  | R/W-1  | R/W-1 |

|------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|--------|-------|--------|--------|-------|

| bit 7 bi                                                                                                                                 | C10UT | C10UTEN | C1POL | C1T0CS | C10N  | C1NREF | C1PREF | C1WU  |

|                                                                                                                                          | bit 7 |         |       |        |       |        |        | bit 0 |

| Legend:                                                                                                                                                                                     |                                                                                                                                                                          |                                                                                    |                                  |                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------|--------------------|--|

| R = Readable bit                                                                                                                                                                            |                                                                                                                                                                          | W = Writable bit                                                                   | U = Unimplemented bit,           | read as '0'        |  |

| -n = Value                                                                                                                                                                                  | at POR                                                                                                                                                                   | '1' = Bit is set                                                                   | '0' = Bit is cleared             | x = Bit is unknown |  |

| bit 7                                                                                                                                                                                       | <b>C1OUT:</b><br>1 = VIN+<br>0 = VIN+                                                                                                                                    |                                                                                    |                                  |                    |  |

| bit 6<br><b>C10UTEN:</b> Comparator Output Enable bit <sup>(1), (2)</sup><br>1 = Output of comparator is NOT placed on the C1OUT pin<br>0 = Output of comparator is placed in the C1OUT pin |                                                                                                                                                                          |                                                                                    |                                  |                    |  |

| bit 5                                                                                                                                                                                       |                                                                                                                                                                          |                                                                                    |                                  |                    |  |

| bit 4                                                                                                                                                                                       | <b>C1TOCS</b> : Comparator TMR0 Clock Source bit <sup>(2)</sup><br>1 = TMR0 clock source selected by T0CS control bit<br>0 = Comparator output used as TMR0 clock source |                                                                                    |                                  |                    |  |

| bit 3                                                                                                                                                                                       | 1 = Com                                                                                                                                                                  | Comparator Enable bit<br>parator is on<br>parator is off                           |                                  |                    |  |

| bit 2                                                                                                                                                                                       | 1 = C1IN                                                                                                                                                                 | Comparator Negative Refe<br>- pin<br>internal reference                            | erence Select bit <sup>(2)</sup> |                    |  |

| bit 1                                                                                                                                                                                       | C1PREF<br>1 = C1IN<br>0 = C1IN                                                                                                                                           | •                                                                                  | rence Select bit <sup>(2)</sup>  |                    |  |

| bit 0                                                                                                                                                                                       | 1 = Wak                                                                                                                                                                  | Comparator Wake-up On Ch<br>e-up On Comparator Change<br>e-up On Comparator Change | e is disabled                    |                    |  |

| Note 1:<br>2:                                                                                                                                                                               | 0.0000000                                                                                                                                                                | CS bit for TRIS control of RI rator is turned on, these con                        |                                  |                    |  |

|            |                                                                         | <b>-</b>                                                                |                  |                  | <b>-</b>         | <b>B</b> 4        |              |

|------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------|------------------|------------------|-------------------|--------------|

| R-1        | R/W-1                                                                   | R/W-1                                                                   | R/W-1            | R/W-1            | R/W-1            | R/W-1             | R/W-1        |

| C2OU       | T C2OUTEN                                                               | C2POL                                                                   | C2PREF2          | C2ON             | C2NREF           | C2PREF1           | C2WU         |

| bit 7      |                                                                         |                                                                         |                  |                  |                  |                   | bit 0        |

|            |                                                                         |                                                                         |                  |                  |                  |                   |              |

| Legend:    |                                                                         |                                                                         |                  |                  |                  |                   |              |

| R = Reada  | able bit                                                                | W = Writable                                                            | bit              | U = Unimpler     | mented bit, read | d as '0'          |              |

| -n = Value | e at POR                                                                | '1' = Bit is set                                                        | t                | '0' = Bit is cle | ared             | x = Bit is unkn   | own          |

|            |                                                                         |                                                                         |                  |                  |                  |                   |              |

| bit 7      | C2OUT: Com                                                              | parator Output                                                          | t bit            |                  |                  |                   |              |

|            | 1 = VIN + > VII                                                         | -                                                                       |                  |                  |                  |                   |              |

|            | 0 = VIN + < VII                                                         | -                                                                       |                  |                  |                  |                   |              |

| bit 6      |                                                                         |                                                                         | tput Enable bit  |                  |                  |                   |              |

|            |                                                                         |                                                                         | NOT placed o     |                  | pin              |                   |              |

|            | •                                                                       | •                                                                       | placed in the (  | C2001 pin        |                  |                   |              |

| bit 5      |                                                                         | C2POL: Comparator Output Polarity bit <sup>(2)</sup>                    |                  |                  |                  |                   |              |

|            | 1 = Output of comparator not inverted                                   |                                                                         |                  |                  |                  |                   |              |

| L:1 4      | •                                                                       | 0 = Output of comparator inverted                                       |                  |                  |                  |                   |              |

| bit 4      |                                                                         | <b>C2PREF2:</b> Comparator Positive Reference Select bit <sup>(2)</sup> |                  |                  |                  |                   |              |

|            | 1 = C IIN + pir<br>0 = C2IN- pin                                        | 1 = C1IN + pin                                                          |                  |                  |                  |                   |              |

| bit 3      | •                                                                       | <b>C2ON:</b> Comparator Enable bit                                      |                  |                  |                  |                   |              |

| bit 0      | 1 = Comparator is on                                                    |                                                                         |                  |                  |                  |                   |              |

|            | 0 = Comparator is off                                                   |                                                                         |                  |                  |                  |                   |              |

| bit 2      |                                                                         |                                                                         |                  |                  |                  |                   |              |

|            | 1 = C2IN-pin                                                            |                                                                         |                  |                  |                  |                   |              |

|            | 0 = CVREF                                                               |                                                                         |                  |                  |                  |                   |              |

| bit 1      | <b>C2PREF1:</b> Comparator Positive Reference Select bit <sup>(2)</sup> |                                                                         |                  |                  |                  |                   |              |

|            | 1 = C2IN+pin                                                            |                                                                         |                  |                  |                  |                   |              |

|            | 0 = C2PREF2                                                             | 0 = C2PREF2 controls analog input selection                             |                  |                  |                  |                   |              |

| bit 0      | C2WU: Comparator Wake-up on Change Enable bit <sup>(2)</sup>            |                                                                         |                  |                  |                  |                   |              |

|            |                                                                         |                                                                         | r change is dis  |                  |                  |                   |              |

|            | •                                                                       | -                                                                       | r change is en   | abled.           |                  |                   |              |

| Note 1:    | Overrides TOCS b                                                        |                                                                         |                  |                  |                  |                   |              |

| 2:         | When comparator precedence.                                             | is turned on, tl                                                        | nese control bit | ts assert them   | selves. Otherw   | ise, the other re | gisters have |

### REGISTER 7-3: CM2CON0: COMPARATOR C2 CONTROL REGISTER (PIC16F506)

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                  |

| Operation:       | $(f) - 1 \rightarrow (dest)$                                                                                                                      |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                               |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                               |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                    |

| Operation:       | (f) – 1 $\rightarrow$ d; skip if result = 0                                                                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '0', the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '0', then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a<br>two-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                      |

| Operands:        | $0 \le k \le 511$                                                                                                                                                                            |

| Operation:       | $k \rightarrow PC<8:0>;$<br>STATUS <6:5> $\rightarrow PC<10:9>$                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                         |

| Description:     | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS <6:5>. GOTO is a two-<br>cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |  |  |

| Operation:       | (W) .OR. (k) $\rightarrow$ (W)                                                                                            |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |  |  |  |  |

## 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- · Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART® Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

### 12.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

#### 12.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

### 12.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 12.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

## **13.0 ELECTRICAL CHARACTERISTICS**

#### Absolute Maximum Ratings†

| Ambient temperature under bias                                                                            | 40°C to +125°C                      |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------|

| Storage temperature                                                                                       | 65°C to +150°C                      |

| Voltage on VDD with respect to Vss                                                                        | 0 to +7.0V                          |

| Voltage on MCLR with respect to Vss                                                                       | 0 to +14V                           |

| Voltage on all other pins with respect to Vss                                                             | 0.3V to (VDD + 0.3V)                |

| Total power dissipation <sup>(1)</sup>                                                                    | 700 mW                              |

| Max. current out of Vss pin                                                                               | 200 mA                              |

| Max. current into Vod pin                                                                                 | 150 mA                              |

| Input clamp current, lικ (Vι < 0 or Vι > VDD)                                                             | ±20 mA                              |

| Output clamp current, Ioκ (Vo < 0 or Vo > VDD)                                                            | ±20 mA                              |

| Max. output current sunk by any I/O pin                                                                   | 25 mA                               |

| Max. output current sourced by any I/O pin                                                                | 25 mA                               |

| Max. output current sourced by I/O port                                                                   | 100 mA                              |

| Max. output current sunk by I/O port                                                                      | 100 mA                              |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD | -VOH) x IOH} + $\Sigma$ (VOL x IOL) |

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 13.1 DC Characteristics: PIC12F510/16F506 (Industrial)

| DC Characteristics |              |                                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature } 40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \end{array}$ |                    |             |          |                                                                                                     |  |

|--------------------|--------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|----------|-----------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Sym          | Characteristic                                                  | Min                                                                                                                                                                                          | Typ <sup>(1)</sup> | Max         | Units    | Conditions                                                                                          |  |

| D001               | Vdd          | Supply Voltage                                                  | 2.0                                                                                                                                                                                          |                    | 5.5         | V        | See Figure 14-1                                                                                     |  |

| D002               | Vdr          | RAM Data Retention Voltage <sup>(2)</sup>                       | _                                                                                                                                                                                            | 1.5*               |             | V        | Device in Sleep mode                                                                                |  |

| D003               | VPOR         | VDD Start Voltage to ensure<br>Power-on Reset                   | —                                                                                                                                                                                            | Vss                |             | V        | See Section 10.4 "Power-on<br>Reset (POR)" for details                                              |  |

| D004               | SVDD         | VDD Rise Rate to ensure<br>Power-on Reset                       | 0.05*                                                                                                                                                                                        | —                  |             | V/ms     | See Section 10.4 "Power-on<br>Reset (POR)" for details                                              |  |

| D010               | IDD          | Supply Current <sup>(3,4)</sup>                                 | _                                                                                                                                                                                            | 175<br>0.625       | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, VDD = 2.0V<br>Fosc = 4 MHz, VDD = 5.0V                                                |  |

|                    |              |                                                                 | _                                                                                                                                                                                            | 250<br>1.0         | 450<br>1.5  | μA<br>mA | Fosc = 8 MHz, Vdd = 2.0V<br>Fosc = 8 MHz, Vdd = 5.0V                                                |  |

|                    |              |                                                                 |                                                                                                                                                                                              | 1.4                | 2.0         | mA       | Fosc = 20 MHz, VDD = 5.0V                                                                           |  |

|                    |              |                                                                 | _                                                                                                                                                                                            | 11<br>38           | 15<br>52    | μΑ<br>μΑ | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                                              |  |

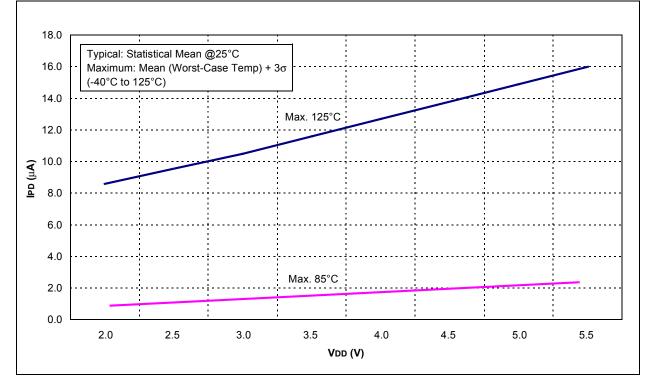

| D020               | IPD          | Power-down Current <sup>(5)</sup>                               | _                                                                                                                                                                                            | 0.1<br>0.35        | 1.2<br>2.4  | μA<br>μA | VDD = 2.0V<br>VDD = 5.0V                                                                            |  |

| D022               | Iwdt         | WDT Current <sup>(5)</sup>                                      | _                                                                                                                                                                                            | 1.0<br>7.0         | 3.0<br>16.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                                            |  |

| D023               | ICMP         | Comparator Current <sup>(5)</sup>                               | _                                                                                                                                                                                            | 15<br>55           | 22<br>67    | μΑ<br>μΑ | VDD = 2.0V (per comparator)<br>VDD = 5.0V (per comparator)                                          |  |

| D022               | ICVREF       | CVREF Current <sup>(5)</sup>                                    | _                                                                                                                                                                                            | 30<br>75           | 60<br>125   | μΑ<br>μΑ | VDD = 2.0V (high range)<br>VDD = 5.0V (high range)                                                  |  |

| D023               | IFVR         | Internal 0.6V Fixed Voltage<br>Reference Current <sup>(5)</sup> |                                                                                                                                                                                              | 85<br>175          | 120<br>205  | μΑ<br>μΑ | $V_{DD}$ = 2.0V (0.6V reference and<br>1 comparator enabled)<br>$V_{DD}$ = 5.0V (0.6V reference and |  |

|                    |              |                                                                 |                                                                                                                                                                                              |                    |             |          | 1 comparator enabled)                                                                               |  |

| D024               | $\Delta$ IAD | A/D Conversion Current <sup>(5)</sup>                           | —                                                                                                                                                                                            | 120                | 150         | μA       | 2.0V                                                                                                |  |

|                    |              |                                                                 | —                                                                                                                                                                                            | 200                | 250         | μA       | 5.0V                                                                                                |  |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

**3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

4: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

**5:** For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

**6:** Does not include current through REXT. The current through the resistor can be estimated by the formula: I = VDD/2REXT (mA) with REXT in kΩ.

#### TABLE 13-7: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER

|              |      |                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified} \\ \mbox{Operating Temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |                  |            |          |                                                  |  |

|--------------|------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|----------|--------------------------------------------------|--|

| Param<br>No. | Sym  | Characteristic                                   | Min Typ <sup>(1)</sup> Max Units Conditions                                                                                                                                                                                                                   |                  |            |          | Conditions                                       |  |

| 30           | ТмсL | MCLR Pulse Width (low)                           | 2000*                                                                                                                                                                                                                                                         | _                | _          | ns       | VDD = 5.0V                                       |  |

| 31           | Twdt | Watchdog Timer Time-out Period<br>(No Prescaler) | 9*<br>9*                                                                                                                                                                                                                                                      | 18*<br>18*       | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |

| 32           | Tdrt | Device Reset Timer Period                        |                                                                                                                                                                                                                                                               |                  |            |          |                                                  |  |

|              |      | Standard                                         | 9*<br>9*                                                                                                                                                                                                                                                      | 18*<br>18*       | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |

|              |      | Short                                            | 0.5*<br>0.5*                                                                                                                                                                                                                                                  | 1.125*<br>1.125* | 2*<br>2.5* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |

| 34           | Tioz | I/O high-impedance from MCLR low                 | _                                                                                                                                                                                                                                                             | _                | 2000*      | ns       |                                                  |  |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

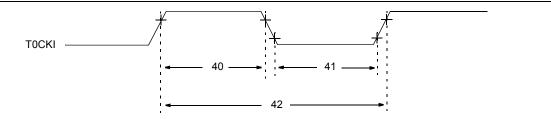

#### FIGURE 13-9: TIMER0 CLOCK TIMINGS

\*

#### TABLE 13-8: TIMER0 CLOCK REQUIREMENTS

|             |                    |                        | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |                   |                    |     |       |                                                                |

|-------------|--------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|-----|-------|----------------------------------------------------------------|

| Parm<br>No. | Svm Characteristic |                        |                                                                                                                                                                                        | Min               | Typ <sup>(1)</sup> | Max | Units | Conditions                                                     |

| 40          | Tt0H               | T0CKI High Pulse Width | No Prescaler                                                                                                                                                                           | 0.5 TCY + 20*     | _                  | _   | ns    |                                                                |

|             |                    |                        | With Prescaler                                                                                                                                                                         | 10*               | —                  | _   | ns    |                                                                |

| 41          | Tt0L               | T0CKI Low Pulse Width  | No Prescaler                                                                                                                                                                           | 0.5 TCY + 20*     | —                  |     | ns    |                                                                |

|             |                    |                        | With Prescaler                                                                                                                                                                         | 10*               | —                  |     | ns    |                                                                |

| 42          | Tt0P               | T0CKI Period           |                                                                                                                                                                                        | 20 or Tcy + 40* N | —                  | _   | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| VDD (Volts)   | Temperature (°C) | Min | Тур  | Max  | Units |

|---------------|------------------|-----|------|------|-------|

| RB0 (GP0)/RB1 | (GP1)            |     |      |      |       |

| 2.0           | -40              | 73K | 105K | 186K | Ω     |

|               | 25               | 73K | 113K | 187K | Ω     |

|               | 85               | 82K | 123K | 190K | Ω     |

|               | 125              | 86K | 132k | 190K | Ω     |

| 5.5           | -40              | 15K | 21K  | 33K  | Ω     |

|               | 25               | 15K | 22K  | 34K  | Ω     |

|               | 85               | 19K | 26k  | 35K  | Ω     |

|               | 125              | 23K | 29K  | 35K  | Ω     |

| RB3 (GP3)     |                  |     |      |      |       |

| 2.0           | -40              | 63K | 81K  | 96K  | Ω     |

|               | 25               | 77K | 93K  | 116K | Ω     |

|               | 85               | 82K | 96k  | 116K | Ω     |

|               | 125              | 86K | 100K | 119K | Ω     |

| 5.5           | -40              | 16K | 20k  | 22K  | Ω     |

|               | 25               | 16K | 21K  | 23K  | Ω     |

|               | 85               | 24K | 25k  | 28K  | Ω     |

|               | 125              | 26K | 27K  | 29K  | Ω     |

### TABLE 13-9: PULL-UP RESISTOR RANGES

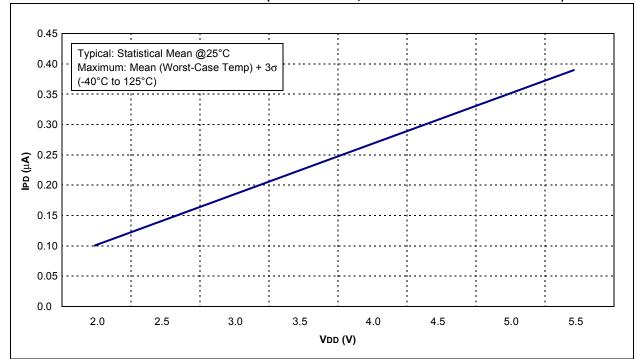

### FIGURE 14-2: TYPICAL IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

### 15.2 Package Marking Information (Cont'd)

14-Lead SOIC (3.90 mm)

8-Lead MSOP

14-Lead TSSOP (4.4 mm)

Example

Example

Example

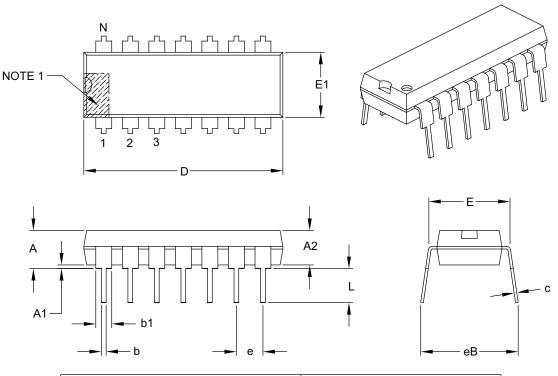

### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units     | INCHES |          |      |  |

|----------------------------|-----------|--------|----------|------|--|

| Dimensio                   | on Limits | MIN    | NOM      | MAX  |  |

| Number of Pins             | N         |        | 14       |      |  |

| Pitch                      | е         |        | .100 BSC |      |  |

| Top to Seating Plane       | Α         | -      | -        | .210 |  |

| Molded Package Thickness   | A2        | .115   | .130     | .195 |  |

| Base to Seating Plane      | A1        | .015   | -        | -    |  |

| Shoulder to Shoulder Width | E         | .290   | .310     | .325 |  |

| Molded Package Width       | E1        | .240   | .250     | .280 |  |

| Overall Length             | D         | .735   | .750     | .775 |  |

| Tip to Seating Plane       | L         | .115   | .130     | .150 |  |

| Lead Thickness             | С         | .008   | .010     | .015 |  |

| Upper Lead Width           | b1        | .045   | .060     | .070 |  |

| Lower Lead Width           | b         | .014   | .018     | .022 |  |

| Overall Row Spacing §      | eB        | _      | _        | .430 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

NOTES:

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com