Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                              |

| Data Converters            | A/D 20x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-QFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32jg1b200f128gm32-b0 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2 Power

The EFM32JG1 has an Energy Management Unit (EMU) and efficient integrated regulators to generate internal supply voltages. Only a single external supply voltage is required, from which all internal voltages are created. An optional integrated dc-dc buck regulator can be utilized to further reduce the current consumption. The dc-dc regulator requires one external inductor and one external capacitor.

AVDD and VREGVDD need to be 1.85 V or higher for the MCU to operate across all conditions; however the rest of the system will operate down to 1.62 V, including the digital supply and I/O. This means that the device is fully compatible with 1.8 V components. Running from a sufficiently high supply, the device can use the dc-dc to regulate voltage not only for itself, but also for other PCB components, supplying up to a total of 200 mA.

#### 3.2.1 Energy Management Unit (EMU)

The Energy Management Unit manages transitions of energy modes in the device. Each energy mode defines which peripherals and features are available and the amount of current the device consumes. The EMU can also be used to turn off the power to unused RAM blocks, and it contains control registers for the DC-DC regulator and the Voltage Monitor (VMON). The VMON is used to monitor multiple supply voltages. It has multiple channels which can be programmed individually by the user to determine if a sensed supply has fallen below a chosen threshold.

### 3.2.2 DC-DC Converter

The DC-DC buck converter covers a wide range of load currents and provides up to 90% efficiency in energy modes EM0, EM1, EM2 and EM3, and can supply up to 200 mA to the device and surrounding PCB components. Protection features include programmable current limiting, short-circuit protection, and dead-time protection. The DC-DC converter may also enter bypass mode when the input voltage is too low for efficient operation. In bypass mode, the DC-DC input supply is internally connected directly to its output through a low resistance switch. Bypass mode also supports in-rush current limiting to prevent input supply voltage droops due to excessive output current transients.

#### 3.3 General Purpose Input/Output (GPIO)

EFM32JG1 has up to 32 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

#### 3.4 Clocking

#### 3.4.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFM32JG1. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

#### 3.4.2 Internal and External Oscillators

The EFM32JG1 supports two crystal oscillators and fully integrates four RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 38 to 40 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system, when crystal accuracy is not required. The HFRCO employs fast startup at minimal energy consumption combined with a wide frequency range.

- An integrated auxilliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC and the Serial Wire debug port with a wide frequency range.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

#### 3.5 Counters/Timers and PWM

#### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER\_0 only.

#### 3.5.2 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes.

#### 3.5.3 Low Energy Timer (LETIMER)

The unique LETIMER is a 16-bit timer that is available in energy mode EM2 Deep Sleep in addition to EM1 Sleep and EM0 Active. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. The LETIMER is connected to the Real Time Counter and Calendar (RTCC), and can be configured to start counting on compare matches from the RTCC.

#### 3.5.4 Ultra Low Power Wake-up Timer (CRYOTIMER)

The CRYOTIMER is a 32-bit counter that is capable of running in all energy modes. It can be clocked by either the 32.768 kHz crystal oscillator (LFXO), the 32.768 kHz RC oscillator (LFRCO), or the 1 kHz RC oscillator (ULFRCO). It can provide periodic Wakeup events and PRS signals which can be used to wake up peripherals from any energy mode. The CRYOTIMER provides a wide range of interrupt periods, facilitating flexible ultra-low energy operation.

#### 3.5.5 Pulse Counter (PCNT)

The Pulse Counter (PCNT) peripheral can be used for counting pulses on a single input or to decode quadrature encoded inputs. The clock for PCNT is selectable from either an external source on pin PCTNn\_S0IN or from an internal timing reference, selectable from among any of the internal oscillators, except the AUXHFRCO. The module may operate in energy mode EM0 Active, EM1 Sleep, EM2 Deep Sleep, and EM3 Stop.

#### 3.5.6 Watchdog Timer (WDOG)

The watchdog timer can act both as an independent watchdog or as a watchdog synchronous with the CPU clock. It has windowed monitoring capabilities, and can generate a reset or different interrupts depending on the failure mode of the system. The watchdog can also monitor autonomous systems driven by PRS.

#### 3.6 Communications and Other Digital Peripherals

## 3.6.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The Universal Synchronous/Asynchronous Receiver/Transmitter is a flexible serial I/O module. It supports full duplex asynchronous UART communication with hardware flow control as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with devices supporting:

- ISO7816 SmartCards

- IrDA

- 1<sup>2</sup>S

# 4.1.2 Operating Conditions

When assigning supply sources, the following requirements must be observed:

- VREGVDD must be the highest voltage in the system

- VREGVDD = AVDD

- DVDD ≤ AVDD

- IOVDD ≤ AVDD

# 4.1.2.1 General Operating Conditions

| Parameter                                                     | Symbol               | Test Condition                                           | Min  | Тур | Max                  | Unit |

|---------------------------------------------------------------|----------------------|----------------------------------------------------------|------|-----|----------------------|------|

| Operating temperature range                                   | T <sub>OP</sub>      | -G temperature grade, Ambient Temperature                | -40  | 25  | 85                   | °C   |

|                                                               |                      | -I temperature grade, Junction<br>Temperature            | -40  | 25  | 125                  | °C   |

| AVDD Supply voltage <sup>1</sup>                              | V <sub>AVDD</sub>    |                                                          | 1.85 | 3.3 | 3.8                  | V    |

| VREGVDD Operating supply                                      | V <sub>VREGVDD</sub> | DCDC in regulation                                       | 2.4  | 3.3 | 3.8                  | V    |

| voltage <sup>1 2</sup>                                        |                      | DCDC in bypass, 50mA load                                | 1.85 | 3.3 | 3.8                  | V    |

|                                                               |                      | DCDC not in use. DVDD external-<br>ly shorted to VREGVDD | 1.85 | 3.3 | 3.8                  | V    |

| VREGVDD Current                                               | I <sub>VREGVDD</sub> | DCDC in bypass, T <sub>amb</sub> ≤ 85 °C                 | _    | _   | 200                  | mA   |

|                                                               |                      | DCDC in bypass, T <sub>amb</sub> > 85 °C                 | _    | _   | 100                  | mA   |

| DVDD Operating supply volt-<br>age                            | V <sub>DVDD</sub>    |                                                          | 1.62 | _   | V <sub>VREGVDD</sub> | V    |

| IOVDD Operating supply voltage                                | VIOVDD               |                                                          | 1.62 | -   | V <sub>VREGVDD</sub> | V    |

| Difference between AVDD<br>and VREGVDD, ABS(AVDD-<br>VREGVDD) | dV <sub>DD</sub>     |                                                          |      | _   | 0.1                  | V    |

| HFCLK frequency                                               | f <sub>CORE</sub>    | 0 wait-states (MODE = WS0) <sup>3</sup>                  | _    | _   | 26                   | MHz  |

|                                                               |                      | 1 wait-states (MODE = WS1) <sup>3</sup>                  | _    | _   | 40                   | MHz  |

## Table 4.2. General Operating Conditions

# Note:

1. VREGVDD must be tied to AVDD. Both VREGVDD and AVDD minimum voltages must be satisfied for the part to operate.

2. The minimum voltage required in bypass mode is calculated using R<sub>BYP</sub> from the DCDC specification table. Requirements for other loads can be calculated as V<sub>DVDD\_min</sub>+I<sub>LOAD</sub> \* R<sub>BYP\_max</sub>

3. In MSC\_READCTRL register

## 4.1.3 Thermal Characteristics

| Parameter          | Symbol              | Test Condition                                      | Min | Тур  | Max | Unit |

|--------------------|---------------------|-----------------------------------------------------|-----|------|-----|------|

| Thermal Resistance | THETA <sub>JA</sub> | QFN32 Package, 2-Layer PCB,<br>Air velocity = 0 m/s | —   | 79   | _   | °C/W |

|                    |                     | QFN32 Package, 2-Layer PCB,<br>Air velocity = 1 m/s | _   | 62.2 | _   | °C/W |

|                    |                     | QFN32 Package, 2-Layer PCB,<br>Air velocity = 2 m/s | _   | 54.1 | _   | °C/W |

|                    |                     | QFN32 Package, 4-Layer PCB,<br>Air velocity = 0 m/s | _   | 32   | _   | °C/W |

|                    |                     | QFN32 Package, 4-Layer PCB,<br>Air velocity = 1 m/s | _   | 28.1 | _   | °C/W |

|                    |                     | QFN32 Package, 4-Layer PCB,<br>Air velocity = 2 m/s | _   | 26.9 | _   | °C/W |

|                    |                     | QFN48 Package, 2-Layer PCB,<br>Air velocity = 0 m/s | _   | 64.5 |     | °C/W |

|                    |                     | QFN48 Package, 2-Layer PCB,<br>Air velocity = 1 m/s | _   | 51.6 | _   | °C/W |

|                    |                     | QFN48 Package, 2-Layer PCB,<br>Air velocity = 2 m/s | -   | 47.7 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 0 m/s | _   | 26.2 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 1 m/s | -   | 23.1 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 2 m/s | -   | 22.1 | _   | °C/W |

## Table 4.3. Thermal Characteristics

#### 4.1.5.2 Current Consumption 3.3 V using DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = IOVDD = 3.3 V, DVDD = 1.8 V DC-DC output.  $T_{OP}$  = 25 °C. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at  $T_{OP}$  = 25 °C. See Figure 5.2 EFM32JG1 Typical Application Circuit Using the DC-DC Converter on page 48.

| Parameter                                                                            | Symbol              | Test Condition                                                   | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0<br>Active mode with all peripherals disabled, DCDC in Low | I <sub>ACTIVE</sub> | 38.4 MHz crystal, CPU running while loop from flash <sup>2</sup> | _   | 86   | _   | µA/MHz |

| Noise DCM mode <sup>1</sup> .                                                        |                     | 38 MHz HFRCO, CPU running<br>Prime from flash                    | _   | 63   | _   | µA/MHz |

|                                                                                      |                     | 38 MHz HFRCO, CPU running while loop from flash                  | _   | 71   | _   | µA/MHz |

|                                                                                      |                     | 38 MHz HFRCO, CPU running<br>CoreMark from flash                 | _   | 78   | _   | µA/MHz |

|                                                                                      |                     | 26 MHz HFRCO, CPU running while loop from flash                  | _   | 76   | _   | µA/MHz |

| Current consumption in EM0<br>Active mode with all periph-                           | -                   | 38.4 MHz crystal, CPU running while loop from flash <sup>2</sup> | _   | 96   | _   | µA/MHz |

| erals disabled, DCDC in Low Noise CCM mode <sup>3</sup> .                            |                     | 38 MHz HFRCO, CPU running<br>Prime from flash                    | _   | 75   | _   | µA/MHz |

|                                                                                      | -                   | 38 MHz HFRCO, CPU running while loop from flash                  | _   | 81   | _   | µA/MHz |

|                                                                                      |                     | 38 MHz HFRCO, CPU running<br>CoreMark from flash                 | _   | 88   |     | µA/MHz |

|                                                                                      |                     | 26 MHz HFRCO, CPU running while loop from flash                  | _   | 94   | _   | µA/MHz |

| Current consumption in EM1                                                           | I <sub>EM1</sub>    | 38.4 MHz crystal <sup>2</sup>                                    | _   | 47   | _   | µA/MHz |

| Sleep mode with all peripher-<br>als disabled, DCDC in Low                           |                     | 38 MHz HFRCO                                                     | _   | 32   | _   | µA/MHz |

| Noise DCM mode <sup>1</sup> .                                                        |                     | 26 MHz HFRCO                                                     | _   | 38   | _   | µA/MHz |

| Current consumption in EM1                                                           | -                   | 38.4 MHz crystal <sup>2</sup>                                    | _   | 59   | _   | µA/MHz |

| Sleep mode with all peripher-<br>als disabled, DCDC in Low                           |                     | 38 MHz HFRCO                                                     | _   | 45   | _   | µA/MHz |

| Noise CCM mode <sup>3</sup> .                                                        |                     | 26 MHz HFRCO                                                     | _   | 58   | _   | µA/MHz |

| Current consumption in EM2<br>Deep Sleep mode. DCDC in                               | I <sub>EM2</sub>    | Full RAM retention and RTCC running from LFXO                    | _   | 2.5  | _   | μA     |

| Low Power mode <sup>4</sup> .                                                        |                     | 4 kB RAM retention and RTCC running from LFRCO                   | _   | 2.2  | _   | μA     |

| Current consumption in EM3<br>Stop mode                                              | I <sub>EM3</sub>    | Full RAM retention and CRYO-<br>TIMER running from ULFRCO        | _   | 2.1  | _   | μΑ     |

| Current consumption in EM4H Hibernate mode                                           | I <sub>EM4</sub>    | 128 byte RAM retention, RTCC running from LFXO                   | _   | 0.86 | _   | μA     |

|                                                                                      |                     | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO       | _   | 0.58 | _   | μA     |

|                                                                                      |                     | 128 byte RAM retention, no RTCC                                  | _   | 0.58 | _   | μA     |

## Table 4.6. Current Consumption 3.3V with DC-DC

#### 4.1.5.3 Current Consumption 1.85 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 1.85 V.  $T_{OP}$  = 25 °C. EMU\_PWRCFG\_PWRCG=NODCDC. EMU\_DCDCCTRL\_DCDCMODE=BYPASS. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at  $T_{OP}$  = 25 °C. See Figure 5.1 EFM32JG1 Typical Application Circuit, Direct Supply, No DC-DC Converter on page 48.

#### Table 4.7. Current Consumption 1.85V without DC/DC

| Parameter                                                                    | Symbol            | Test Condition                                                   | Min | Тур  | Мах | Unit   |

|------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0<br>Active mode with all periph-<br>erals disabled | IACTIVE           | 38.4 MHz crystal, CPU running while loop from flash <sup>1</sup> | _   | 127  |     | µA/MHz |

|                                                                              |                   | 38 MHz HFRCO, CPU running<br>Prime from flash                    | —   | 88   |     | µA/MHz |

|                                                                              |                   | 38 MHz HFRCO, CPU running while loop from flash                  | —   | 100  |     | µA/MHz |

|                                                                              |                   | 38 MHz HFRCO, CPU running<br>CoreMark from flash                 | _   | 112  |     | µA/MH: |

|                                                                              |                   | 26 MHz HFRCO, CPU running while loop from flash                  | —   | 102  | _   | µA/MH: |

|                                                                              |                   | 1 MHz HFRCO, CPU running while loop from flash                   | _   | 220  | _   | µA/MH: |

| Current consumption in EM1                                                   | I <sub>EM1</sub>  | 38.4 MHz crystal <sup>1</sup>                                    | —   | 61   |     | µA/MH: |

| Sleep mode with all peripherals disabled                                     |                   | 38 MHz HFRCO                                                     | _   | 35   |     | µA/MH  |

|                                                                              |                   | 26 MHz HFRCO                                                     | _   | 37   | _   | µA/MH  |

|                                                                              |                   | 1 MHz HFRCO                                                      | _   | 154  |     | µA/MH  |

| Current consumption in EM2<br>Deep Sleep mode                                | I <sub>EM2</sub>  | Full RAM retention and RTCC running from LFXO                    | _   | 3.2  | _   | μA     |

|                                                                              |                   | 4 kB RAM retention and RTCC running from LFRCO                   | _   | 2.8  |     | μA     |

| Current consumption in EM3<br>Stop mode                                      | I <sub>EM3</sub>  | Full RAM retention and CRYO-<br>TIMER running from ULFRCO        | _   | 2.7  | _   | μA     |

| Current consumption in<br>EM4H Hibernate mode                                | I <sub>EM4</sub>  | 128 byte RAM retention, RTCC running from LFXO                   | _   | 1    |     | μA     |

|                                                                              |                   | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO       | —   | 0.62 |     | μA     |

|                                                                              |                   | 128 byte RAM retention, no RTCC                                  | _   | 0.62 | _   | μA     |

| Current consumption in EM4S Shutoff mode                                     | I <sub>EM4S</sub> | No RAM retention, no RTCC                                        | _   | 0.02 | _   | μΑ     |

# 4.1.8 Oscillators

# 4.1.8.1 LFXO

# Table 4.10. LFXO

| Parameter                                                | Symbol               | Test Condition                                                                  | Min | Тур    | Max | Unit |

|----------------------------------------------------------|----------------------|---------------------------------------------------------------------------------|-----|--------|-----|------|

| Crystal frequency                                        | f <sub>LFXO</sub>    |                                                                                 |     | 32.768 | _   | kHz  |

| Supported crystal equivalent series resistance (ESR)     | ESR <sub>LFXO</sub>  |                                                                                 |     |        | 70  | kΩ   |

| Supported range of crystal load capacitance <sup>1</sup> | C <sub>LFXO_CL</sub> |                                                                                 | 6   | _      | 18  | pF   |

| On-chip tuning cap range <sup>2</sup>                    | C <sub>LFXO_T</sub>  | On each of LFXTAL_N and LFXTAL_P pins                                           | 8   | _      | 40  | pF   |

| On-chip tuning cap step size                             | SS <sub>LFXO</sub>   |                                                                                 | _   | 0.25   | _   | pF   |

| Current consumption after startup <sup>3</sup>           | I <sub>LFXO</sub>    | ESR = 70 kΩ, C <sub>L</sub> = 7 pF, GAIN <sup>4</sup> = 3, AGC <sup>4</sup> = 1 |     | 273    | _   | nA   |

| Start- up time                                           | t <sub>LFXO</sub>    | ESR=70 kΩ, C <sub>L</sub> = 7 pF, GAIN <sup>4</sup> =<br>2                      |     | 308    | _   | ms   |

## Note:

1. Total load capacitance as seen by the crystal

2. The effective load capacitance seen by the crystal will be C<sub>LFXO\_T</sub> /2. This is because each XTAL pin has a tuning cap and the two caps will be seen in series by the crystal.

3. Block is supplied by AVDD if ANASW = 0, or DVDD if ANASW=1 in EMU\_PWRCTRL register

4. In CMU\_LFXOCTRL register

## Table 4.18. ADC

| Parameter                                                                                      | Symbol                  | Test Condition                                                         | Min               | Тур | Max                | Unit |

|------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------|-------------------|-----|--------------------|------|

| Resolution                                                                                     | VRESOLUTION             |                                                                        | 6                 |     | 12                 | Bits |

| Input voltage range                                                                            | VADCIN                  | Single ended                                                           | 0                 | _   | 2*V <sub>REF</sub> | V    |

|                                                                                                |                         | Differential                                                           | -V <sub>REF</sub> | _   | V <sub>REF</sub>   | V    |

| Input range of external refer-<br>ence voltage, single ended<br>and differential               | Vadcrefin_p             |                                                                        | 1                 | _   | V <sub>AVDD</sub>  | V    |

| Power supply rejection <sup>1</sup>                                                            | PSRR <sub>ADC</sub>     | At DC                                                                  | _                 | 80  | _                  | dB   |

| Analog input common mode rejection ratio                                                       | CMRR <sub>ADC</sub>     | At DC                                                                  | _                 | 80  | _                  | dB   |

| Current from all supplies, us-                                                                 | I <sub>ADC_CONTI-</sub> | 1 Msps / 16 MHz ADCCLK,                                                | _                 | 301 | 350                | μA   |

| ing internal reference buffer.<br>Continous operation. WAR-<br>MUPMODE <sup>2</sup> = KEEPADC- | NOUS_LP                 | BIASPROG = 0, GPBIASACC = 1                                            |                   |     |                    |      |

| WARM                                                                                           |                         | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 1 <sup>3</sup> | _                 | 149 | _                  | μA   |

|                                                                                                |                         | 62.5 ksps / 1 MHz ADCCLK,                                              | _                 | 91  | _                  | μA   |

|                                                                                                |                         | BIASPROG = 15, GPBIASACC = 1 <sup>3</sup>                              |                   |     |                    |      |

| Current from all supplies, us-                                                                 | uffer.<br>WAR-          | 35 ksps / 16 MHz ADCCLK,                                               | _                 | 51  | _                  | μA   |

| ing internal reference buffer.<br>Duty-cycled operation. WAR-<br>MUPMODE <sup>2</sup> = NORMAL |                         | BIASPROG = 0, GPBIASACC = 1                                            |                   |     |                    |      |

|                                                                                                |                         | 5 ksps / 16 MHz ADCCLK                                                 | _                 | 9   | _                  | μA   |

|                                                                                                |                         | BIASPROG = 0, GPBIASACC = 1                                            |                   |     |                    |      |

| Current from all supplies, us-                                                                 | IADC_STAND-             | 125 ksps / 16 MHz ADCCLK,                                              | _                 | 117 | _                  | μA   |

| ing internal reference buffer.<br>Duty-cycled operation.<br>AWARMUPMODE <sup>2</sup> = KEEP-   | BY_LP                   | BIASPROG = 0, GPBIASACC = 1                                            |                   |     |                    |      |

| INSTANDBY or KEEPIN-<br>SLOWACC                                                                |                         | 35 ksps / 16 MHz ADCCLK,                                               | _                 | 79  | _                  | μA   |

|                                                                                                |                         | BIASPROG = 0, GPBIASACC = 1                                            |                   |     |                    |      |

| Current from all supplies, us-                                                                 | IADC_CONTI-             | 1 Msps / 16 MHz ADCCLK,                                                | _                 | 345 | _                  | μA   |

| ing internal reference buffer.<br>Continous operation. WAR-<br>MUPMODE <sup>2</sup> = KEEPADC- | NOUS_HP                 | BIASPROG = 0, GPBIASACC = 0                                            |                   |     |                    |      |

| WARM                                                                                           |                         | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 0 <sup>3</sup> | _                 | 191 | -                  | μA   |

|                                                                                                |                         | 62.5 ksps / 1 MHz ADCCLK,                                              | _                 | 132 | _                  | μA   |

|                                                                                                |                         | BIASPROG = 15, GPBIASACC = 0 <sup>3</sup>                              |                   |     |                    |      |

| Parameter                                                                                      | Symbol                    | Test Condition                                                       | Min | Тур   | Мах | Unit   |

|------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------|-----|-------|-----|--------|

| Current from all supplies, us-                                                                 | IADC_NORMAL_HP            | 35 ksps / 16 MHz ADCCLK,                                             | _   | 102   | _   | μA     |

| ing internal reference buffer.<br>Duty-cycled operation. WAR-<br>MUPMODE <sup>2</sup> = NORMAL |                           | BIASPROG = 0, GPBIASACC = 0                                          |     |       |     |        |

|                                                                                                |                           | 5 ksps / 16 MHz ADCCLK                                               | _   | 17    | _   | μA     |

|                                                                                                |                           | $\begin{array}{l} BIASPROG = 0, \ GPBIASACC = 0\\ 3 \end{array}$     |     |       |     |        |

| Current from all supplies, us-                                                                 | IADC_STAND-               | 125 ksps / 16 MHz ADCCLK,                                            | _   | 162   | _   | μA     |

| ing internal reference buffer.<br>Duty-cycled operation.<br>AWARMUPMODE <sup>2</sup> = KEEP-   | BY_HP                     | BIASPROG = 0, GPBIASACC = 0                                          |     |       |     |        |

| INSTANDBY or KEEPIN-<br>SLOWACC                                                                |                           | 35 ksps / 16 MHz ADCCLK,                                             | —   | 123   | _   | μA     |

|                                                                                                |                           | BIASPROG = 0, GPBIASACC = 0                                          |     |       |     |        |

| Current from HFPERCLK                                                                          | I <sub>ADC_CLK</sub>      | HFPERCLK = 16 MHz                                                    |     | 140   |     | μA     |

| ADC Clock Frequency                                                                            | f <sub>ADCCLK</sub>       |                                                                      | _   | _     | 16  | MHz    |

| Throughput rate                                                                                | <b>f</b> ADCRATE          |                                                                      | —   | —     | 1   | Msps   |

| Conversion time <sup>4</sup>                                                                   | t <sub>ADCCONV</sub>      | 6 bit                                                                | —   | 7     | _   | cycles |

|                                                                                                |                           | 8 bit                                                                | —   | 9     | _   | cycles |

|                                                                                                |                           | 12 bit                                                               |     | 13    |     | cycles |

| Startup time of reference generator and ADC core                                               | t <sub>ADCSTART</sub>     | WARMUPMODE <sup>2</sup> = NORMAL                                     | —   | —     | 5   | μs     |

|                                                                                                |                           | WARMUPMODE <sup>2</sup> = KEEPIN-<br>STANDBY                         | —   | _     | 2   | μs     |

|                                                                                                |                           | WARMUPMODE <sup>2</sup> = KEEPINSLO-<br>WACC                         | _   | _     | 1   | μs     |

| SNDR at 1Msps and f <sub>in</sub> =<br>10kHz                                                   | SNDR <sub>ADC</sub>       | Internal reference, 2.5 V full-scale, differential (-1.25, 1.25)     | 58  | 67    | —   | dB     |

|                                                                                                |                           | vrefp_in = 1.25 V direct mode with<br>2.5 V full-scale, differential | —   | 68    | —   | dB     |

| Spurious-Free Dynamic<br>Range (SFDR)                                                          | SFDR <sub>ADC</sub>       | 1 MSamples/s, 10 kHz full-scale<br>sine wave                         | _   | 75    |     | dB     |

| Input referred ADC noise,<br>rms                                                               | V <sub>REF_NOISE</sub>    | Including quantization noise and distortion                          |     | 380   |     | μV     |

| Offset Error                                                                                   | V <sub>ADCOFFSETERR</sub> |                                                                      | -3  | 0.25  | 3   | LSB    |

| Gain error in ADC                                                                              | V <sub>ADC_GAIN</sub>     | Using internal reference                                             | _   | -0.2  | 5   | %      |

|                                                                                                |                           | Using external reference                                             | —   | -1    | —   | %      |

| Differential non-linearity<br>(DNL)                                                            | DNL <sub>ADC</sub>        | 12 bit resolution, No Missing Co-<br>des                             | -1  | _     | 2   | LSB    |

| Integral non-linearity (INL),<br>End point method                                              | INL <sub>ADC</sub>        | 12 bit resolution                                                    | -6  | _     | 6   | LSB    |

| Temperature Sensor Slope                                                                       | V <sub>TS_SLOPE</sub>     |                                                                      | —   | -1.84 |     | mV/°C  |

| Parameter                     | Symbol                 | Test Condition                                             | Min | Тур  | Мах  | Unit |

|-------------------------------|------------------------|------------------------------------------------------------|-----|------|------|------|

| Comparator delay <sup>4</sup> | t <sub>ACMPDELAY</sub> | $BIASPROG^2 = 1$ , $FULLBIAS^2 = 0$                        | —   | 30   | _    | μs   |

|                               |                        | BIASPROG <sup>2</sup> = 0x10, FULLBIAS <sup>2</sup><br>= 0 | _   | 3.7  |      | μs   |

|                               |                        | BIASPROG <sup>2</sup> = 0x20, FULLBIAS <sup>2</sup><br>= 1 | _   | 35   |      | ns   |

| Offset voltage                | VACMPOFFSET            | BIASPROG <sup>2</sup> =0x10, FULLBIAS <sup>2</sup><br>= 1  | -35 | _    | 35   | mV   |

| Reference Voltage             | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | 1   | 1.25 | 1.47 | V    |

|                               |                        | Internal 2.5 V reference                                   | 2   | 2.5  | 2.8  | V    |

| Capacitive Sense Internal     | R <sub>CSRES</sub>     | CSRESSEL <sup>5</sup> = 0                                  |     | inf  | _    | kΩ   |

| Resistance                    |                        | CSRESSEL <sup>5</sup> = 1                                  |     | 15   | _    | kΩ   |

|                               |                        | CSRESSEL <sup>5</sup> = 2                                  | _   | 27   | _    | kΩ   |

|                               |                        | CSRESSEL <sup>5</sup> = 3                                  |     | 39   |      | kΩ   |

|                               |                        | CSRESSEL <sup>5</sup> = 4                                  |     | 51   | _    | kΩ   |

|                               |                        | CSRESSEL <sup>5</sup> = 5                                  | —   | 102  | —    | kΩ   |

|                               |                        | CSRESSEL <sup>5</sup> = 6                                  | —   | 164  | _    | kΩ   |

|                               |                        | CSRESSEL <sup>5</sup> = 7                                  | _   | 239  | _    | kΩ   |

## Note:

1. ACMPVDD is a supply chosen by the setting in ACMPn\_CTRL\_PWRSEL and may be IOVDD, AVDD or DVDD

2. In ACMPn\_CTRL register

3. In ACMPn\_HYSTERESIS register

- 4. ±100 mV differential drive

- 5. In ACMPn\_INPUTSEL register

The total ACMP current is the sum of the contributions from the ACMP and its internal voltage reference as given as:

## $I_{ACMPTOTAL} = I_{ACMP} + I_{ACMPREF}$

$\mathbf{I}_{\text{ACMPREF}}$  is zero if an external voltage reference is used.

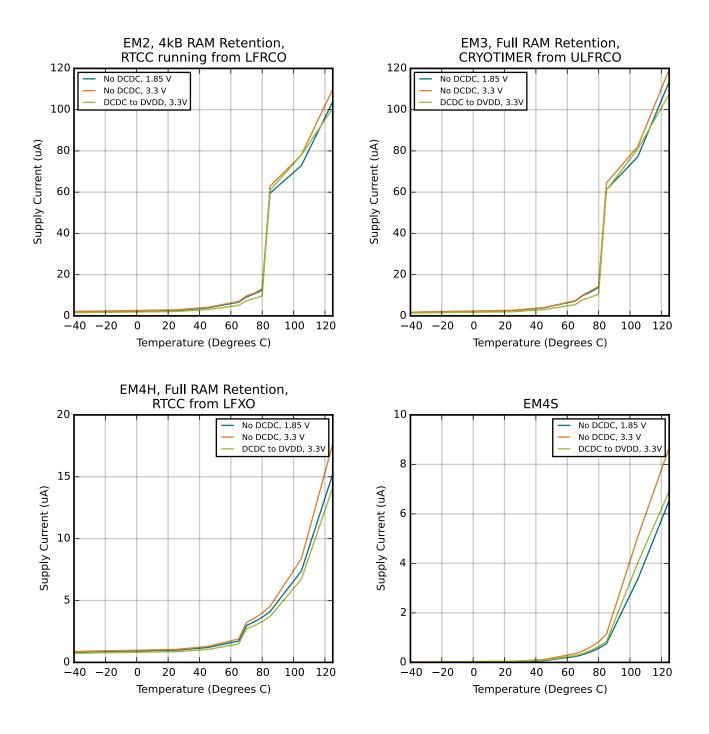

Figure 4.5. EM2, EM3, EM4H and EM4S Typical Supply Current

| QFN      | 48 Pin# and Name |                | Pin Alternate Functi                                                                                                                                                                                                                                                  | onality / Description                                                                                                                                                                                                     |                                                                                                           |

|----------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog         | Timers                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                             | Other                                                                                                     |

| 4        | PF3              | BUSAY<br>BUSBX | TIM0_CC0 #27<br>TIM0_CC1 #26<br>TIM0_CC2 #25<br>TIM0_CDTI0 #24<br>TIM0_CDTI1 #23<br>TIM0_CDTI2 #22<br>TIM1_CC0 #27<br>TIM1_CC1 #26<br>TIM1_CC2 #25<br>TIM1_CC3 #24 LE-<br>TIM0_OUT0 #27 LE-<br>TIM0_OUT1 #26<br>PCNT0_S0IN #27<br>PCNT0_S1IN #26                      | US0_TX #27 US0_RX<br>#26 US0_CLK #25<br>US0_CS #24 US0_CTS<br>#23 US0_RTS #22<br>US1_TX #27 US1_RX<br>#26 US1_CLK #25<br>US1_CS #24 US1_CTS<br>#23 US1_RTS #22<br>LEU0_TX #27 LEU0_RX<br>#26 I2C0_SDA #27<br>I2C0_SCL #26 | CMU_CLK1 #6<br>PRS_CH0 #3 PRS_CH1<br>#2 PRS_CH2 #1<br>PRS_CH3 #0 ACMP0_O<br>#27 ACMP1_O #27<br>DBG_TDI #0 |

| 5        | PF4              | BUSAX<br>BUSBY | TIM0_CC0 #28<br>TIM0_CC1 #27<br>TIM0_CC2 #26<br>TIM0_CDTI0 #25<br>TIM0_CDTI1 #24<br>TIM0_CDTI2 #23<br>TIM1_CC0 #28<br>TIM1_CC1 #27<br>TIM1_CC2 #26<br>TIM1_CC3 #25 LE-<br>TIM0_OUT0 #28 LE-<br>TIM0_OUT0 #28 LE-<br>TIM0_OUT1 #27<br>PCNT0_S0IN #28<br>PCNT0_S1IN #27 | US0_TX #28 US0_RX<br>#27 US0_CLK #26<br>US0_CS #25 US0_CTS<br>#24 US0_RTS #23<br>US1_TX #28 US1_RX<br>#27 US1_CLK #26<br>US1_CS #25 US1_CTS<br>#24 US1_RTS #23<br>LEU0_TX #28 LEU0_RX<br>#27 I2C0_SDA #28<br>I2C0_SCL #27 | PRS_CH0 #4 PRS_CH1<br>#3 PRS_CH2 #2<br>PRS_CH3 #1 ACMP0_O<br>#28 ACMP1_O #28                              |

| 6        | PF5              | BUSAY<br>BUSBX | TIM0_CC0 #29<br>TIM0_CC1 #28<br>TIM0_CC2 #27<br>TIM0_CDTI0 #26<br>TIM0_CDTI1 #25<br>TIM0_CDTI2 #24<br>TIM1_CC0 #29<br>TIM1_CC1 #28<br>TIM1_CC2 #27<br>TIM1_CC3 #26 LE-<br>TIM0_OUT0 #29 LE-<br>TIM0_OUT1 #28<br>PCNT0_S0IN #29<br>PCNT0_S1IN #28                      | US0_TX #29 US0_RX<br>#28 US0_CLK #27<br>US0_CS #26 US0_CTS<br>#25 US0_RTS #24<br>US1_TX #29 US1_RX<br>#28 US1_CLK #27<br>US1_CS #26 US1_CTS<br>#25 US1_RTS #24<br>LEU0_TX #29 LEU0_RX<br>#28 I2C0_SDA #29<br>I2C0_SCL #28 | PRS_CH0 #5 PRS_CH1<br>#4 PRS_CH2 #3<br>PRS_CH3 #2 ACMP0_O<br>#29 ACMP1_O #29                              |

| 7        | PF6              | BUSAX<br>BUSBY | TIM0_CC0 #30<br>TIM0_CC1 #29<br>TIM0_CC2 #28<br>TIM0_CDTI0 #27<br>TIM0_CDTI1 #26<br>TIM0_CDTI2 #25<br>TIM1_CC0 #30<br>TIM1_CC1 #29<br>TIM1_CC2 #28<br>TIM1_CC3 #27 LE-<br>TIM0_OUT0 #30 LE-<br>TIM0_OUT0 #30 LE-<br>TIM0_OUT1 #29<br>PCNT0_S0IN #30<br>PCNT0_S1IN #29 | US0_TX #30 US0_RX<br>#29 US0_CLK #28<br>US0_CS #27 US0_CTS<br>#26 US0_RTS #25<br>US1_TX #30 US1_RX<br>#29 US1_CLK #28<br>US1_CS #27 US1_CTS<br>#26 US1_RTS #25<br>LEU0_TX #30 LEU0_RX<br>#29 I2C0_SDA #30<br>I2C0_SCL #29 | CMU_CLK1 #7<br>PRS_CH0 #6 PRS_CH1<br>#5 PRS_CH2 #4<br>PRS_CH3 #3 ACMP0_O<br>#30 ACMP1_O #30               |

| QFN      | 48 Pin# and Name |                | Pin Alternate Functi                                                                                                                                                                                                                                                  | onality / Description                                                                                                                                                                                                     |                                                                                                                       |

|----------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog         | Timers                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                             | Other                                                                                                                 |

| 46       | PC9              | BUSAY<br>BUSBX | TIM0_CC0 #14<br>TIM0_CC1 #13<br>TIM0_CC2 #12<br>TIM0_CDTI0 #11<br>TIM0_CDTI1 #10<br>TIM0_CDTI2 #9<br>TIM1_CC0 #14<br>TIM1_CC1 #13<br>TIM1_CC2 #12<br>TIM1_CC3 #11 LE-<br>TIM0_OUT0 #14 LE-<br>TIM0_OUT1 #13<br>PCNT0_S0IN #14<br>PCNT0_S1IN #13                       | US0_TX #14 US0_RX<br>#13 US0_CLK #12<br>US0_CS #11 US0_CTS<br>#10 US0_RTS #9<br>US1_TX #14 US1_RX<br>#13 US1_CLK #12<br>US1_CS #11 US1_CTS<br>#10 US1_RTS #9<br>LEU0_TX #14 LEU0_RX<br>#13 I2C0_SDA #14<br>I2C0_SCL #13   | PRS_CH0 #11<br>PRS_CH9 #14<br>PRS_CH10 #3<br>PRS_CH11 #2<br>ACMP0_O #14<br>ACMP1_O #14                                |

| 47       | PC10             | BUSAX<br>BUSBY | TIM0_CC0 #15<br>TIM0_CC1 #14<br>TIM0_CC2 #13<br>TIM0_CDTI0 #12<br>TIM0_CDT11 #11<br>TIM0_CDT12 #10<br>TIM1_CC0 #15<br>TIM1_CC1 #14<br>TIM1_CC2 #13<br>TIM1_CC3 #12 LE-<br>TIM0_OUT0 #15 LE-<br>TIM0_OUT1 #14<br>PCNT0_S0IN #15<br>PCNT0_S1IN #14                      | US0_TX #15 US0_RX<br>#14 US0_CLK #13<br>US0_CS #12 US0_CTS<br>#11 US0_RTS #10<br>US1_TX #15 US1_RX<br>#14 US1_CLK #13<br>US1_CS #12 US1_CTS<br>#11 US1_RTS #10<br>LEU0_TX #15 LEU0_RX<br>#14 I2C0_SDA #15<br>I2C0_SCL #14 | CMU_CLK1 #3<br>PRS_CH0 #12<br>PRS_CH9 #15<br>PRS_CH10 #4<br>PRS_CH11 #3<br>ACMP0_O #15<br>ACMP1_O #15<br>GPIO_EM4WU12 |

| 48       | PC11             | BUSAY<br>BUSBX | TIM0_CC0 #16<br>TIM0_CC1 #15<br>TIM0_CC2 #14<br>TIM0_CDTI0 #13<br>TIM0_CDT11 #12<br>TIM0_CDT12 #11<br>TIM1_CC0 #16<br>TIM1_CC1 #15<br>TIM1_CC2 #14<br>TIM1_CC3 #13 LE-<br>TIM0_OUT0 #16 LE-<br>TIM0_OUT0 #16 LE-<br>TIM0_OUT1 #15<br>PCNT0_S0IN #16<br>PCNT0_S1IN #15 | US0_TX #16 US0_RX<br>#15 US0_CLK #14<br>US0_CS #13 US0_CTS<br>#12 US0_RTS #11<br>US1_TX #16 US1_RX<br>#15 US1_CLK #14<br>US1_CS #13 US1_CTS<br>#12 US1_RTS #11<br>LEU0_TX #16 LEU0_RX<br>#15 I2C0_SDA #16<br>I2C0_SCL #15 | CMU_CLK0 #3<br>PRS_CH0 #13<br>PRS_CH9 #16<br>PRS_CH10 #5<br>PRS_CH11 #4<br>ACMP0_O #16<br>ACMP1_O #16<br>DBG_SWO #3   |

| QFN      | 32 Pin# and Name |                             | Pin Alternate Functi                                                                                                                                                                                                                                                  | onality / Description                                                                                                                                                                                                     |                                                                                                                 |

|----------|------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog                      | Timers                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                             | Other                                                                                                           |

| 15       | PD14             | BUSCX<br>BUSDY              | TIM0_CC0 #22<br>TIM0_CC1 #21<br>TIM0_CC2 #20<br>TIM0_CDTI0 #19<br>TIM0_CDTI1 #18<br>TIM0_CDT12 #17<br>TIM1_CC0 #22<br>TIM1_CC1 #21<br>TIM1_CC3 #19 LE-<br>TIM0_OUT0 #22 LE-<br>TIM0_OUT0 #22 LE-<br>TIM0_OUT1 #21<br>PCNT0_S0IN #22<br>PCNT0_S1IN #21                 | US0_TX #22 US0_RX<br>#21 US0_CLK #20<br>US0_CS #19 US0_CTS<br>#18 US0_RTS #17<br>US1_TX #22 US1_RX<br>#21 US1_CLK #20<br>US1_CS #19 US1_CTS<br>#18 US1_RTS #17<br>LEU0_TX #22 LEU0_RX<br>#21 I2C0_SDA #22<br>I2C0_SCL #21 | CMU_CLK0 #5<br>PRS_CH3 #13<br>PRS_CH4 #5 PRS_CH5<br>#4 PRS_CH6 #16<br>ACMP0_0 #22<br>ACMP1_0 #22<br>GPIO_EM4WU4 |

| 16       | PD15             | BUSCY<br>BUSDX              | TIM0_CC0 #23<br>TIM0_CC1 #22<br>TIM0_CC2 #21<br>TIM0_CDTI0 #20<br>TIM0_CDTI1 #19<br>TIM0_CDT12 #18<br>TIM1_CC0 #23<br>TIM1_CC1 #22<br>TIM1_CC2 #21<br>TIM1_CC3 #20 LE-<br>TIM0_OUT0 #23 LE-<br>TIM0_OUT0 #23 LE-<br>TIM0_OUT1 #22<br>PCNT0_S0IN #23<br>PCNT0_S1IN #22 | US0_TX #23 US0_RX<br>#22 US0_CLK #21<br>US0_CS #20 US0_CTS<br>#19 US0_RTS #18<br>US1_TX #23 US1_RX<br>#22 US1_CLK #21<br>US1_CS #20 US1_CTS<br>#19 US1_RTS #18<br>LEU0_TX #23 LEU0_RX<br>#22 I2C0_SDA #23<br>I2C0_SCL #22 | CMU_CLK1 #5<br>PRS_CH3 #14<br>PRS_CH4 #6 PRS_CH5<br>#5 PRS_CH6 #17<br>ACMP0_O #23<br>ACMP1_O #23<br>DBG_SWO #2  |

| 17       | PA0              | ADC0_EXTN<br>BUSCX<br>BUSDY | TIM0_CC0 #0<br>TIM0_CC1 #31<br>TIM0_CC2 #30<br>TIM0_CDTI0 #29<br>TIM0_CDTI1 #28<br>TIM0_CDTI2 #27<br>TIM1_CC0 #0<br>TIM1_CC1 #31<br>TIM1_CC2 #30<br>TIM1_CC3 #29 LE-<br>TIM0_OUT0 #0 LE-<br>TIM0_OUT0 #0 LE-<br>TIM0_OUT1 #31<br>PCNT0_S0IN #0<br>PCNT0_S1IN #31      | US0_TX #0 US0_RX<br>#31 US0_CLK #30<br>US0_CS #29 US0_CTS<br>#28 US0_RTS #27<br>US1_TX #0 US1_RX<br>#31 US1_CLK #30<br>US1_CS #29 US1_CTS<br>#28 US1_RTS #27<br>LEU0_TX #0 LEU0_RX<br>#31 I2C0_SDA #0<br>I2C0_SCL #31     | CMU_CLK1 #0<br>PRS_CH6 #0 PRS_CH7<br>#10 PRS_CH8 #9<br>PRS_CH9 #8 ACMP0_O<br>#0 ACMP1_O #0                      |

| 18       | PA1              | ADC0_EXTP<br>BUSCY<br>BUSDX | TIM0_CC0 #1<br>TIM0_CC1 #0<br>TIM0_CC2 #31<br>TIM0_CDTI0 #30<br>TIM0_CDTI1 #29<br>TIM0_CDTI2 #28<br>TIM1_CC0 #1<br>TIM1_CC1 #0<br>TIM1_CC2 #31<br>TIM1_CC3 #30 LE-<br>TIM0_OUT0 #1 LE-<br>TIM0_OUT0 #1 LE-<br>TIM0_OUT1 #0<br>PCNT0_S0IN #1<br>PCNT0_S1IN #0          | US0_TX #1 US0_RX #0<br>US0_CLK #31 US0_CS<br>#30 US0_CTS #29<br>US0_RTS #28 US1_TX<br>#1 US1_RX #0<br>US1_CLK #31 US1_CS<br>#30 US1_CTS #29<br>US1_RTS #28 LEU0_TX<br>#1 LEU0_RX #0<br>I2C0_SDA #1 I2C0_SCL<br>#0         | CMU_CLK0 #0<br>PRS_CH6 #1 PRS_CH7<br>#0 PRS_CH8 #10<br>PRS_CH9 #9 ACMP0_O<br>#1 ACMP1_O #1                      |

## 6.2.1 EFM32JG1 QFN32 without DC-DC GPIO Overview

The GPIO pins are organized as 16-bit ports indicated by letters (A, B, C...), and the individual pins on each port are indicated by a number from 15 down to 0.

| Port   | Pin<br>15    | Pin<br>14    | Pin<br>13    | Pin<br>12    | Pin<br>11    | Pin<br>10    | Pin 9       | Pin 8       | Pin 7       | Pin 6 | Pin 5 | Pin 4       | Pin 3       | Pin 2       | Pin 1       | Pin 0       |

|--------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------|-------|-------|-------------|-------------|-------------|-------------|-------------|

| Port A | -            | -            | -            | -            | -            | -            | -           | -           | -           | -     | -     | -           | -           | -           | PA1         | PA0         |

| Port B | PB15         | PB14         | PB13<br>(5V) | PB12<br>(5V) | PB11<br>(5V) | -            | -           | -           | -           | -     | -     | -           | -           | -           | -           | -           |

| Port C | -            | -            | -            | -            | PC11<br>(5V) | PC10<br>(5V) | PC9<br>(5V) | PC8<br>(5V) | PC7<br>(5V) | -     | -     | -           | -           | -           | -           | -           |

| Port D | PD15<br>(5V) | PD14<br>(5V) | PD13<br>(5V) | PD12<br>(5V) | PD11<br>(5V) | PD10<br>(5V) | PD9<br>(5V) | -           | -           | -     | -     | -           | -           | -           | -           | -           |

| Port F | -            | -            | -            | -            | -            | -            | -           | -           | -           | -     | -     | PF4<br>(5V) | PF3<br>(5V) | PF2<br>(5V) | PF1<br>(5V) | PF0<br>(5V) |

## Table 6.4. QFN32 without DC-DC GPIO Pinout

Note:

1. GPIO with 5V tolerance are indicated by (5V).

2. The pins PB13, PB12, PB11, PD15, PD14, and PD13 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hardware compatibility, do not use these pins with 5V domains.

## 6.4 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |                                        |                                        |                                           | LOCA                                      | ATION                                       |                                              |                                          |                                          |                                                                                                                                                                                  |

|---------------|----------------------------------------|----------------------------------------|-------------------------------------------|-------------------------------------------|---------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                                  | 4 - 7                                  | 8 - 11                                    | 12 - 15                                   | 16 - 19                                     | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                                                                                                                                                      |

| ACMP0_O       | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3   | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12 | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10 | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Analog comparator<br>ACMP0, digital out-<br>put.                                                                                                                                 |

| ACMP1_O       | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3   | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12 | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10 | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Analog comparator<br>ACMP1, digital out-<br>put.                                                                                                                                 |

| ADC0_EXTN     | 0: PA0                                 |                                        |                                           |                                           |                                             |                                              |                                          |                                          | Analog to digital<br>converter ADC0 ex-<br>ternal reference in-<br>put negative pin                                                                                              |

| ADC0_EXTP     | 0: PA1                                 |                                        |                                           |                                           |                                             |                                              |                                          |                                          | Analog to digital<br>converter ADC0 ex-<br>ternal reference in-<br>put positive pin                                                                                              |

| BOOT_RX       | 0: PF1                                 |                                        |                                           |                                           |                                             |                                              |                                          |                                          | Bootloader RX                                                                                                                                                                    |

| BOOT_TX       | 0: PF0                                 |                                        |                                           |                                           |                                             |                                              |                                          |                                          | Bootloader TX                                                                                                                                                                    |

| CMU_CLK0      | 0: PA1<br>1: PB15<br>2: PC6<br>3: PC11 | 4: PD9<br>5: PD14<br>6: PF2<br>7: PF7  |                                           |                                           |                                             |                                              |                                          |                                          | Clock Management<br>Unit, clock output<br>number 0.                                                                                                                              |

| CMU_CLK1      | 0: PA0<br>1: PB14<br>2: PC7<br>3: PC10 | 4: PD10<br>5: PD15<br>6: PF3<br>7: PF6 |                                           |                                           |                                             |                                              |                                          |                                          | Clock Management<br>Unit, clock output<br>number 1.                                                                                                                              |

| DBG_SWCLKTCK  | 0: PF0                                 |                                        |                                           |                                           |                                             |                                              |                                          |                                          | Debug-interface<br>Serial Wire clock<br>input and JTAG<br>Test Clock.<br>Note that this func-<br>tion is enabled to<br>the pin out of reset,<br>and has a built-in<br>pull down. |

#### Table 6.7. Alternate functionality overview

| Alternate     |                                      |                                         |                                           | LOC                                        | TION                                        |                                              |                                          |                                          |                                                                                                                                     |

|---------------|--------------------------------------|-----------------------------------------|-------------------------------------------|--------------------------------------------|---------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                                | 4 - 7                                   | 8 - 11                                    | 12 - 15                                    | 16 - 19                                     | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                                                                                                         |

| GPIO_EM4WU12  | 0: PC10                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Pin can be used to<br>wake the system<br>up from EM4                                                                                |

| I2C0_SCL      | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | I2C0 Serial Clock<br>Line input / output.                                                                                           |

| I2C0_SDA      | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | I2C0 Serial Data in-<br>put / output.                                                                                               |

| LETIM0_OUT0   | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Low Energy Timer<br>LETIM0, output<br>channel 0.                                                                                    |

| LETIM0_OUT1   | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | Low Energy Timer<br>LETIM0, output<br>channel 1.                                                                                    |

| LEU0_RX       | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | LEUART0 Receive input.                                                                                                              |

| LEU0_TX       | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | LEUART0 Transmit<br>output. Also used<br>as receive input in<br>half duplex commu-<br>nication.                                     |

| LFXTAL_N      | 0: PB14                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Low Frequency<br>Crystal (typically<br>32.768 kHz) nega-<br>tive pin. Also used<br>as an optional ex-<br>ternal clock input<br>pin. |

| LFXTAL_P      | 0: PB15                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Low Frequency<br>Crystal (typically<br>32.768 kHz) posi-<br>tive pin.                                                               |

| PCNT0_S0IN    | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Pulse Counter<br>PCNT0 input num-<br>ber 0.                                                                                         |

| PCNT0_S1IN    | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | Pulse Counter<br>PCNT0 input num-<br>ber 1.                                                                                         |

| PRS_CH0       | 0: PF0<br>1: PF1<br>2: PF2<br>3: PF3 | 4: PF4<br>5: PF5<br>6: PF6<br>7: PF7    | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11                       |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 0.                                                                                    |

| Port    | Bus   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7  | CH6  | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

|---------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|-----|-----|

| APORT1X | BUSAX |      |      |      |      |      |      |      |      |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | PC6  |      |      |      |      |     |     |

| APORT1Y | BUSAY |      |      |      |      |      |      |      |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | PC9 |     | PC7  |      |      |      |      |      |     |     |

| APORT2X | BUSBX |      |      |      |      |      |      |      |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | PC9 |     | PC7  |      |      |      |      |      |     |     |

| APORT2Y | BUSBY |      |      |      |      |      |      |      |      |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | 90d  |      |      |      |      |     |     |

| APORT3X | BUSCX |      | PB14 |      | PB12 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     |     |

| APORT3Y | BUSCY | PB15 |      | PB13 |      | PB11 |      |      |      |      |      |      |      |      |      |      |      |      |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

| APORT4X | BUSDX | PB15 |      | PB13 |      | PB11 |      |      |      |      |      |      |      |      |      |      |      |      |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

| APORT4Y | BUSDY |      | PB14 |      | PB12 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     |     |

# Table 6.9. ACMP1 Bus and Pin Mapping

# 9. Revision History

## 9.1 Revision 1.1

## 2016-Oct-26

- System Overview Sections: Minor wording and typographical error fixes.

- Electrical Characteristics: Minor wording and typographical error fixes.

- "HFRCO and AUXHFRCO" table in Electrical Characteristics: f\_HFRCO symbol changed to f\_HFRCO\_ACC.

- Pinout tables: APORT channel details removed from "Analog" column. This information is now found in the APORT client map sections.

- Updated APORT client map sections.

## 9.2 Revision 1.0

## 2016-Jul-22

- Electrical Characteristics: Minimum and maximum value statement changed to cover full operating temperature range.

- Finalized Specification Tables. Tables with condition/min/typ/max or footnote changes include:

- Absolute Maximum Ratings

- · General Operating Conditions

- DC-DC Converter

- LFRCO

- HFRCO and AUXHFRCO

- ADC

- IDAC

- Updated Typical Performance Graphs.

- · Added note for 5V tolerance to pinout GPIO Overview sections.

- · Updated OPN decoder with latest revision.

- · Updated Package Marking text with latest descriptions.

#### 9.3 Revision 0.95

2016-04-11

- · All OPNs changed to rev C0.

- · Electrical specification tables updated with latest characterization data and production test limits.