Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                   |

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 20                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                               |

| Data Converters            | A/D 20x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-QFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32jg1b200f256gm32-b0r |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2 Power

The EFM32JG1 has an Energy Management Unit (EMU) and efficient integrated regulators to generate internal supply voltages. Only a single external supply voltage is required, from which all internal voltages are created. An optional integrated dc-dc buck regulator can be utilized to further reduce the current consumption. The dc-dc regulator requires one external inductor and one external capacitor.

AVDD and VREGVDD need to be 1.85 V or higher for the MCU to operate across all conditions; however the rest of the system will operate down to 1.62 V, including the digital supply and I/O. This means that the device is fully compatible with 1.8 V components. Running from a sufficiently high supply, the device can use the dc-dc to regulate voltage not only for itself, but also for other PCB components, supplying up to a total of 200 mA.

### 3.2.1 Energy Management Unit (EMU)

The Energy Management Unit manages transitions of energy modes in the device. Each energy mode defines which peripherals and features are available and the amount of current the device consumes. The EMU can also be used to turn off the power to unused RAM blocks, and it contains control registers for the DC-DC regulator and the Voltage Monitor (VMON). The VMON is used to monitor multiple supply voltages. It has multiple channels which can be programmed individually by the user to determine if a sensed supply has fallen below a chosen threshold.

### 3.2.2 DC-DC Converter

The DC-DC buck converter covers a wide range of load currents and provides up to 90% efficiency in energy modes EM0, EM1, EM2 and EM3, and can supply up to 200 mA to the device and surrounding PCB components. Protection features include programmable current limiting, short-circuit protection, and dead-time protection. The DC-DC converter may also enter bypass mode when the input voltage is too low for efficient operation. In bypass mode, the DC-DC input supply is internally connected directly to its output through a low resistance switch. Bypass mode also supports in-rush current limiting to prevent input supply voltage droops due to excessive output current transients.

### 3.3 General Purpose Input/Output (GPIO)

EFM32JG1 has up to 32 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

### 3.4 Clocking

### 3.4.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFM32JG1. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

### 3.4.2 Internal and External Oscillators

The EFM32JG1 supports two crystal oscillators and fully integrates four RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 38 to 40 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system, when crystal accuracy is not required. The HFRCO employs fast startup at minimal energy consumption combined with a wide frequency range.

- An integrated auxilliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC and the Serial Wire debug port with a wide frequency range.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

## 4.1.3 Thermal Characteristics

| Parameter          | Symbol              | Test Condition                                      | Min | Тур  | Max | Unit |

|--------------------|---------------------|-----------------------------------------------------|-----|------|-----|------|

| Thermal Resistance | THETA <sub>JA</sub> | QFN32 Package, 2-Layer PCB,<br>Air velocity = 0 m/s | —   | 79   | _   | °C/W |

|                    |                     | QFN32 Package, 2-Layer PCB,<br>Air velocity = 1 m/s | _   | 62.2 | _   | °C/W |

|                    |                     | QFN32 Package, 2-Layer PCB,<br>Air velocity = 2 m/s | _   | 54.1 | _   | °C/W |

|                    |                     | QFN32 Package, 4-Layer PCB,<br>Air velocity = 0 m/s | _   | 32   | _   | °C/W |

|                    |                     | QFN32 Package, 4-Layer PCB,<br>Air velocity = 1 m/s | _   | 28.1 | _   | °C/W |

|                    |                     | QFN32 Package, 4-Layer PCB,<br>Air velocity = 2 m/s | _   | 26.9 | _   | °C/W |

|                    |                     | QFN48 Package, 2-Layer PCB,<br>Air velocity = 0 m/s | _   | 64.5 |     | °C/W |

|                    |                     | QFN48 Package, 2-Layer PCB,<br>Air velocity = 1 m/s | _   | 51.6 | _   | °C/W |

|                    |                     | QFN48 Package, 2-Layer PCB,<br>Air velocity = 2 m/s | _   | 47.7 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 0 m/s | _   | 26.2 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 1 m/s | -   | 23.1 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 2 m/s | -   | 22.1 | _   | °C/W |

## Table 4.3. Thermal Characteristics

| Parameter                          | Symbol                                     | Test Condition                                                              | Min | Тур | Max | Unit |

|------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|------|

| Max load current                   | I <sub>LOAD_MAX</sub>                      | Low noise (LN) mode, Heavy<br>Drive <sup>4</sup> , T <sub>amb</sub> ≤ 85 °C | _   | —   | 200 | mA   |

|                                    |                                            | Low noise (LN) mode, Heavy<br>Drive <sup>4</sup> , T <sub>amb</sub> > 85 °C | _   | _   | 100 | mA   |

|                                    |                                            | Low noise (LN) mode, Medium Drive <sup>4</sup>                              | _   | _   | 100 | mA   |

|                                    | Low noise (LN) mode,<br>Drive <sup>4</sup> | Low noise (LN) mode, Light Drive <sup>4</sup>                               | _   | _   | 50  | mA   |

|                                    |                                            | Low power (LP) mode,<br>LPCMPBIAS <sup>3</sup> = 0                          | _   | _   | 75  | μA   |

|                                    |                                            | Low power (LP) mode,<br>LPCMPBIAS <sup>3</sup> = 3                          | _   |     | 10  | mA   |

| DCDC nominal output ca-<br>pacitor | C <sub>DCDC</sub>                          | 25% tolerance                                                               | 1   | 1   | 1   | μF   |

| DCDC nominal output induc-<br>tor  | L <sub>DCDC</sub>                          | 20% tolerance                                                               | 4.7 | 4.7 | 4.7 | μH   |

| Resistance in Bypass mode          | R <sub>BYP</sub>                           |                                                                             | _   | 1.2 | 2.5 | Ω    |

#### Note:

1. Due to internal dropout, the DC-DC output will never be able to reach its input voltage, V<sub>VREGVDD</sub>

2. LP mode controller is a hysteretic controller that maintains the output voltage within the specified limits

3. In EMU\_DCDCMISCCTRL register

4. Drive levels are defined by configuration of the PFETCNT and NFETCNT registers. Light Drive: PFETCNT=NFETCNT=3; Medium Drive: PFETCNT=NFETCNT=7; Heavy Drive: PFETCNT=15.

## Table 4.11. HFXO

| Parameter                                                | Symbol               | Test Condition                                  | Min | Тур  | Max | Unit |

|----------------------------------------------------------|----------------------|-------------------------------------------------|-----|------|-----|------|

| Crystal Frequency                                        | f <sub>HFXO</sub>    |                                                 | 38  | 38.4 | 40  | MHz  |

| Supported crystal equivalent series resistance (ESR)     | ESR <sub>HFXO</sub>  | Crystal frequency 38.4 MHz                      | —   | _    | 60  | Ω    |

| Supported range of crystal load capacitance <sup>1</sup> | C <sub>HFXO_CL</sub> |                                                 | 6   | _    | 12  | pF   |

| On-chip tuning cap range <sup>2</sup>                    | C <sub>HFXO_T</sub>  | On each of HFXTAL_N and HFXTAL_P pins           | 9   | 20   | 25  | pF   |

| On-chip tuning capacitance step                          | SS <sub>HFXO</sub>   |                                                 | _   | 0.04 |     | pF   |

| Startup time                                             | t <sub>HFXO</sub>    | 38.4 MHz, ESR = 50 Ω, C <sub>L</sub> = 10<br>pF | —   | 300  | _   | μs   |

| Frequency Tolerance for the crystal                      | FT <sub>HFXO</sub>   | 38.4 MHz, ESR = 50 Ω, CL = 10<br>pF             | -40 | —    | 40  | ppm  |

Note:

1. Total load capacitance as seen by the crystal

The effective load capacitance seen by the crystal will be C<sub>HFXO\_T</sub> /2. This is because each XTAL pin has a tuning cap and the two caps will be seen in series by the crystal.

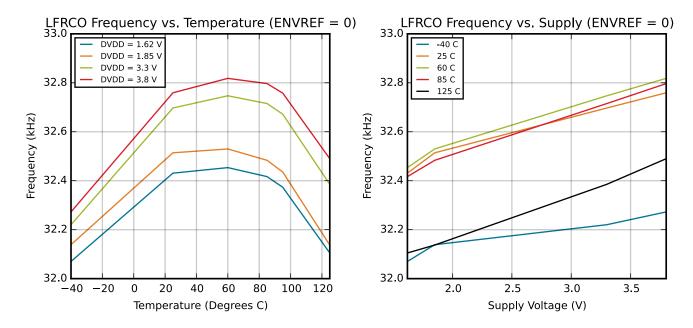

## 4.1.8.3 LFRCO

## Table 4.12. LFRCO

| Parameter                        | Symbol             | Test Condition                                              | Min    | Тур    | Max    | Unit |

|----------------------------------|--------------------|-------------------------------------------------------------|--------|--------|--------|------|

| Oscillation frequency            | f <sub>LFRCO</sub> | ENVREF = 1 in<br>CMU_LFRCOCTRL, T <sub>AMB</sub> ≤ 85<br>°C | 30.474 | 32.768 | 34.243 | kHz  |

|                                  |                    | ENVREF = 1 in<br>CMU_LFRCOCTRL, T <sub>AMB</sub> > 85<br>°C | 30.474 | _      | 39.7   | kHz  |

|                                  |                    | ENVREF = 0 in<br>CMU_LFRCOCTRL                              | 30.474 | 32.768 | 33.915 | kHz  |

| Startup time                     | t <sub>LFRCO</sub> |                                                             | _      | 500    | _      | μs   |

| Current consumption <sup>1</sup> | I <sub>LFRCO</sub> | ENVREF = 1 in<br>CMU_LFRCOCTRL                              | _      | 342    |        | nA   |

|                                  |                    | ENVREF = 0 in<br>CMU_LFRCOCTRL                              | _      | 494    | _      | nA   |

#### Note:

1. Block is supplied by AVDD if ANASW = 0, or DVDD if ANASW=1 in EMU\_PWRCTRL register

## 4.1.8.4 HFRCO and AUXHFRCO

| Parameter                           | Symbol                 | Test Condition                                                 | Min  | Тур | Max | Unit  |

|-------------------------------------|------------------------|----------------------------------------------------------------|------|-----|-----|-------|

| Frequency Accuracy                  | f <sub>HFRCO_ACC</sub> | Any frequency band, across sup-<br>ply voltage and temperature | -2.5 | _   | 2.5 | %     |

| Start-up time                       | t <sub>HFRCO</sub>     | f <sub>HFRCO</sub> ≥ 19 MHz                                    | —    | 300 | _   | ns    |

|                                     |                        | 4 < f <sub>HFRCO</sub> < 19 MHz                                | _    | 1   | _   | μs    |

|                                     |                        | f <sub>HFRCO</sub> ≤ 4 MHz                                     | —    | 2.5 | _   | μs    |

| Current consumption on all supplies | I <sub>HFRCO</sub>     | f <sub>HFRCO</sub> = 38 MHz                                    | _    | 204 | 228 | μA    |

| supplies                            |                        | f <sub>HFRCO</sub> = 32 MHz                                    |      | 171 | 190 | μA    |

|                                     |                        | f <sub>HFRCO</sub> = 26 MHz                                    |      | 147 | 164 | μA    |

|                                     |                        | f <sub>HFRCO</sub> = 19 MHz                                    | _    | 126 | 138 | μA    |

|                                     |                        | f <sub>HFRCO</sub> = 16 MHz                                    |      | 110 | 120 | μA    |

|                                     |                        | f <sub>HFRCO</sub> = 13 MHz                                    |      | 100 | 110 | μA    |

|                                     |                        | f <sub>HFRCO</sub> = 7 MHz                                     | _    | 81  | 91  | μA    |

|                                     |                        | f <sub>HFRCO</sub> = 4 MHz                                     |      | 33  | 35  | μA    |

|                                     |                        | f <sub>HFRCO</sub> = 2 MHz                                     |      | 31  | 35  | μA    |

|                                     |                        | f <sub>HFRCO</sub> = 1 MHz                                     |      | 30  | 35  | μA    |

| Step size                           | SS <sub>HFRCO</sub>    | Coarse (% of period)                                           | _    | 0.8 |     | %     |

|                                     |                        | Fine (% of period)                                             | —    | 0.1 | —   | %     |

| Period Jitter                       | PJ <sub>HFRCO</sub>    |                                                                | _    | 0.2 | _   | % RMS |

### Table 4.13. HFRCO and AUXHFRCO

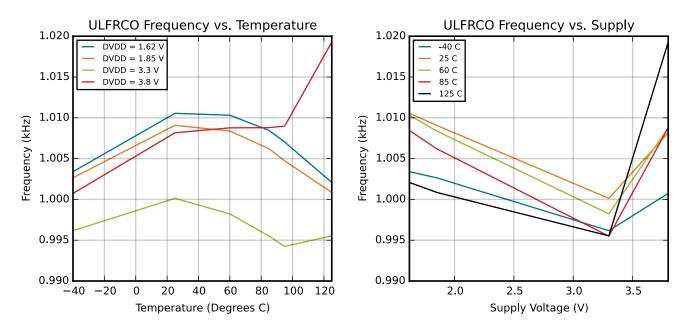

## 4.1.8.5 ULFRCO

## Table 4.14. ULFRCO

| Parameter             | Symbol              | Test Condition | Min  | Тур | Max  | Unit |

|-----------------------|---------------------|----------------|------|-----|------|------|

| Oscillation frequency | f <sub>ULFRCO</sub> |                | 0.95 | 1   | 1.07 | kHz  |

## 4.1.9 Flash Memory Characteristics

| Parameter                                      | Symbol               | Test Condition            | Min   | Тур | Max | Unit   |

|------------------------------------------------|----------------------|---------------------------|-------|-----|-----|--------|

| Flash erase cycles before failure              | EC <sub>FLASH</sub>  |                           | 10000 | _   | _   | cycles |

| Flash data retention                           | RET <sub>FLASH</sub> | T <sub>AMB</sub> ≤ 85 °C  | 10    | _   | _   | years  |

|                                                |                      | T <sub>AMB</sub> ≤ 125 °C | 10    | _   | _   | years  |

| Word (32-bit) programming time                 | t <sub>W_PROG</sub>  |                           | 20    | 26  | 40  | μs     |

| Page erase time                                | t <sub>PERASE</sub>  |                           | 20    | 27  | 40  | ms     |

| Mass erase time                                | t <sub>MERASE</sub>  |                           | 20    | 27  | 40  | ms     |

| Device erase time <sup>2</sup>                 | t <sub>DERASE</sub>  | T <sub>AMB</sub> ≤ 85 °C  | _     | 60  | 74  | ms     |

|                                                |                      | T <sub>AMB</sub> ≤ 125 °C | —     | 60  | 78  | ms     |

| Page erase current <sup>3</sup>                | I <sub>ERASE</sub>   |                           | _     | _   | 3   | mA     |

| Mass or Device erase cur-<br>rent <sup>3</sup> |                      |                           | -     | —   | 5   | mA     |

| Write current <sup>3</sup>                     | I <sub>WRITE</sub>   |                           | —     | _   | 3   | mA     |

## Table 4.15. Flash Memory Characteristics<sup>1</sup>

Note:

1. Flash data retention information is published in the Quarterly Quality and Reliability Report.

2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW)

3. Measured at 25°C

## Table 4.16. GPIO

| Parameter                                                                | Symbol                 | Test Condition                                                       | Min       | Тур                                                                                                                                                                           | Max       | Unit |

|--------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|

| Input low voltage                                                        | V <sub>IOIL</sub>      |                                                                      | —         | _                                                                                                                                                                             | IOVDD*0.3 | V    |

| Input high voltage                                                       | V <sub>IOIH</sub>      |                                                                      | IOVDD*0.7 | _                                                                                                                                                                             | _         | V    |

| Output high voltage relative                                             | V <sub>IOOH</sub>      | Sourcing 3 mA, IOVDD ≥ 3 V,                                          | IOVDD*0.8 | _                                                                                                                                                                             | _         | V    |

| to IOVDD                                                                 |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                                    |           |                                                                                                                                                                               |           |      |

|                                                                          |                        | Sourcing 1.2 mA, IOVDD $\ge$ 1.62 V,                                 | IOVDD*0.6 | 10.7 — — $10.8$ — — $10.6$ — — $10.8$ — — $10.8$ — — $10.8$ — — $10.8$ — — $10.6$ — — $10.6$ — — $10.6$ — — $10.6$ — — $10.7$ IOVDD*0 $1000000000000000000000000000000000000$ | _         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                                    |           |                                                                                                                                                                               |           |      |

|                                                                          |                        | Sourcing 20 mA, IOVDD $\ge$ 3 V,                                     | IOVDD*0.8 | _                                                                                                                                                                             | _         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                                  |           |                                                                                                                                                                               |           |      |

|                                                                          |                        | Sourcing 8 mA, IOVDD ≥ 1.62 V,                                       | IOVDD*0.6 | _                                                                                                                                                                             | _         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                                  |           |                                                                                                                                                                               |           |      |

| Output low voltage relative to                                           | V <sub>IOOL</sub>      | Sinking 3 mA, IOVDD ≥ 3 V,                                           | _         | _                                                                                                                                                                             | IOVDD*0.2 | V    |

| IOVDD                                                                    |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                                    |           |                                                                                                                                                                               |           |      |

|                                                                          |                        | Sinking 1.2 mA, IOVDD ≥ 1.62 V,                                      | _         | _                                                                                                                                                                             | IOVDD*0.4 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                                    |           |                                                                                                                                                                               |           |      |

|                                                                          |                        | Sinking 20 mA, IOVDD $\ge$ 3 V,                                      | _         | _                                                                                                                                                                             | IOVDD*0.2 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                                  |           |                                                                                                                                                                               |           |      |

|                                                                          |                        | Sinking 8 mA, IOVDD ≥ 1.62 V,                                        | _         | _                                                                                                                                                                             | IOVDD*0.4 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                                  |           |                                                                                                                                                                               |           |      |

| Input leakage current                                                    | I <sub>IOLEAK</sub>    | All GPIO except LFXO pins, GPIO<br>≤ IOVDD, T <sub>amb</sub> ≤ 85 °C | _         | 0.1                                                                                                                                                                           | 30        | nA   |

|                                                                          |                        | LFXO Pins, GPIO ≤ IOVDD, T <sub>amb</sub><br>≤ 85 °C                 | _         | 0.1                                                                                                                                                                           | 50        | nA   |

|                                                                          |                        | All GPIO except LFXO pins, GPIO<br>≤ IOVDD, T <sub>AMB</sub> > 85 °C | _         | _                                                                                                                                                                             | 110       | nA   |

|                                                                          |                        | LFXO Pins, GPIO ≤ IOVDD, T <sub>AMB</sub><br>> 85 °C                 | _         |                                                                                                                                                                               | 250       | nA   |

| Input leakage current on 5VTOL pads above IOVDD                          | I <sub>5VTOLLEAK</sub> | IOVDD < GPIO ≤ IOVDD + 2 V                                           | _         | 3.3                                                                                                                                                                           | 15        | μA   |

| I/O pin pull-up resistor                                                 | R <sub>PU</sub>        |                                                                      | 30        | 43                                                                                                                                                                            | 65        | kΩ   |

| I/O pin pull-down resistor                                               | R <sub>PD</sub>        |                                                                      | 30        | 43                                                                                                                                                                            | 65        | kΩ   |

| Pulse width of pulses re-<br>moved by the glitch suppres-<br>sion filter | tioglitch              |                                                                      | 20        | 25                                                                                                                                                                            | 35        | ns   |

| Parameter                                                                                      | Symbol                    | Test Condition                                                       | Min | Тур   | Мах | Unit   |

|------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------|-----|-------|-----|--------|

| Current from all supplies, us-                                                                 | IADC_NORMAL_HP            | 35 ksps / 16 MHz ADCCLK,                                             | _   | 102   | _   | μA     |

| ing internal reference buffer.<br>Duty-cycled operation. WAR-<br>MUPMODE <sup>2</sup> = NORMAL |                           | BIASPROG = 0, GPBIASACC = 0                                          |     |       |     |        |

|                                                                                                |                           | 5 ksps / 16 MHz ADCCLK                                               | _   | 17    | _   | μA     |

|                                                                                                |                           | $\begin{array}{l} BIASPROG = 0, \ GPBIASACC = 0\\ 3 \end{array}$     |     |       |     |        |

| Current from all supplies, us-                                                                 | IADC_STAND-               | 125 ksps / 16 MHz ADCCLK,                                            | _   | 162   | _   | μA     |

| ing internal reference buffer.<br>Duty-cycled operation.<br>AWARMUPMODE <sup>2</sup> = KEEP-   | BY_HP                     | BIASPROG = 0, GPBIASACC = 0                                          |     |       |     |        |

| INSTANDBY or KEEPIN-<br>SLOWACC                                                                |                           | 35 ksps / 16 MHz ADCCLK,                                             | —   | 123   | _   | μA     |

| SLOWAGG                                                                                        |                           | BIASPROG = 0, GPBIASACC = 0                                          |     |       |     |        |

| Current from HFPERCLK                                                                          | I <sub>ADC_CLK</sub>      | HFPERCLK = 16 MHz                                                    |     | 140   |     | μA     |

| ADC Clock Frequency                                                                            | f <sub>ADCCLK</sub>       |                                                                      | _   | _     | 16  | MHz    |

| Throughput rate                                                                                | <b>f</b> ADCRATE          |                                                                      | —   | —     | 1   | Msps   |

| Conversion time <sup>4</sup>                                                                   | t <sub>ADCCONV</sub>      | 6 bit                                                                | —   | 7     | _   | cycles |

|                                                                                                |                           | 8 bit                                                                | —   | 9     | _   | cycles |

|                                                                                                |                           | 12 bit                                                               |     | 13    |     | cycles |

| Startup time of reference generator and ADC core                                               | tadcstart                 | WARMUPMODE <sup>2</sup> = NORMAL                                     | —   | —     | 5   | μs     |

|                                                                                                |                           | WARMUPMODE <sup>2</sup> = KEEPIN-<br>STANDBY                         | —   | _     | 2   | μs     |

|                                                                                                |                           | WARMUPMODE <sup>2</sup> = KEEPINSLO-<br>WACC                         | _   | _     | 1   | μs     |

| SNDR at 1Msps and f <sub>in</sub> =<br>10kHz                                                   | SNDR <sub>ADC</sub>       | Internal reference, 2.5 V full-scale, differential (-1.25, 1.25)     | 58  | 67    | —   | dB     |

|                                                                                                |                           | vrefp_in = 1.25 V direct mode with<br>2.5 V full-scale, differential | —   | 68    | —   | dB     |

| Spurious-Free Dynamic<br>Range (SFDR)                                                          | SFDR <sub>ADC</sub>       | 1 MSamples/s, 10 kHz full-scale<br>sine wave                         | _   | 75    | _   | dB     |

| Input referred ADC noise,<br>rms                                                               | V <sub>REF_NOISE</sub>    | Including quantization noise and distortion                          |     | 380   |     | μV     |

| Offset Error                                                                                   | V <sub>ADCOFFSETERR</sub> |                                                                      | -3  | 0.25  | 3   | LSB    |

| Gain error in ADC                                                                              | V <sub>ADC_GAIN</sub>     | Using internal reference                                             | _   | -0.2  | 5   | %      |

|                                                                                                |                           | Using external reference                                             | —   | -1    |     | %      |

| Differential non-linearity<br>(DNL)                                                            | DNL <sub>ADC</sub>        | 12 bit resolution, No Missing Co-<br>des                             | -1  | _     | 2   | LSB    |

| Integral non-linearity (INL),<br>End point method                                              | INL <sub>ADC</sub>        | 12 bit resolution                                                    | -6  | _     | 6   | LSB    |

| Temperature Sensor Slope                                                                       | V <sub>TS_SLOPE</sub>     |                                                                      | —   | -1.84 |     | mV/°C  |

# 4.1.14 Analog Comparator (ACMP)

## Table 4.20. ACMP

| Parameter                                             | Symbol               | Test Condition                                                      | Min   | Тур | Max                         | Unit |

|-------------------------------------------------------|----------------------|---------------------------------------------------------------------|-------|-----|-----------------------------|------|

| Input voltage range                                   | V <sub>ACMPIN</sub>  | ACMPVDD =<br>ACMPn_CTRL_PWRSEL <sup>1</sup>                         | 0     | _   | V <sub>ACMPVDD</sub>        | V    |

| Supply Voltage                                        | V <sub>ACMPVDD</sub> | BIASPROG <sup>2</sup> $\leq$ 0x10 or FULL-<br>BIAS <sup>2</sup> = 0 | 1.85  | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                       |                      | $0x10 < BIASPROG^2 \le 0x20$ and FULLBIAS <sup>2</sup> = 1          | 2.1   | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Active current not including                          | I <sub>ACMP</sub>    | $BIASPROG^2 = 1$ , $FULLBIAS^2 = 0$                                 | _     | 50  | _                           | nA   |

| voltage reference                                     |                      | $BIASPROG^{2} = 0x10, FULLBIAS^{2} = 0$                             | _     | 306 | -                           | nA   |

|                                                       |                      | $BIASPROG^{2} = 0x20, FULLBIAS^{2}$ $= 1$                           | _     | 74  | 95                          | μA   |

| Current consumption of inter-<br>al voltage reference | I <sub>ACMPREF</sub> | VLP selected as input using 2.5 V<br>Reference / 4 (0.625 V)        | _     | 50  | _                           | nA   |

|                                                       |                      | VLP selected as input using VDD                                     | _     | 20  |                             | nA   |

|                                                       |                      | VBDIV selected as input using 1.25 V reference / 1                  | _     | 4.1 | _                           | μA   |

|                                                       |                      | VADIV selected as input using VDD/1                                 | _     | 2.4 | _                           | μA   |

| Hysteresis ( $V_{CM}$ = 1.25 V,                       | VACMPHYST            | HYSTSEL <sup>3</sup> = HYST0                                        | -1.75 | 0   | 1.75                        | mV   |

| $BIASPROG^2 = 0x10, FULL-$<br>$BIAS^2 = 1)$           |                      | HYSTSEL <sup>3</sup> = HYST1                                        | 10    | 18  | 26                          | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST2                                        | 21    | 32  | 46                          | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST3                                        | 27    | 44  | 63                          | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST4                                        | 32    | 55  | 80                          | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST5                                        | 38    | 65  | 100                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST6                                        | 43    | 77  | 121                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST7                                        | 47    | 86  | 148                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST8                                        | -4    | 0   | 4                           | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST9                                        | -27   | -18 | -10                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST10                                       | -47   | -32 | -18                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST11                                       | -64   | -43 | -27                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST12                                       | -78   | -54 | -32                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST13                                       | -93   | -64 | -37                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST14                                       | -113  | -74 | -42                         | mV   |

|                                                       |                      | HYSTSEL <sup>3</sup> = HYST15                                       | -135  | -85 | -47                         | mV   |

## 4.1.15 I2C

### I2C Standard-mode (Sm)

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Max  | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | —   | 100  | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 4.7 |     |      | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 4   | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU,DAT</sub> |                | 250 |     | _    | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD,DAT</sub> |                | 100 | _   | 3450 | ns   |

| Repeated START condition set-up time             | t <sub>SU,STA</sub> |                | 4.7 |     |      | μs   |

| (Repeated) START condition hold time             | t <sub>HD,STA</sub> |                | 4   |     |      | μs   |

| STOP condition set-up time                       | t <sub>SU,STO</sub> |                | 4   | _   | _    | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 4.7 | _   |      | μs   |

## Table 4.21. I2C Standard-mode (Sm)<sup>1</sup>

Note:

1. For CLHR set to 0 in the I2Cn\_CTRL register

2. For the minimum HFPERCLK frequency required in Standard-mode, refer to the I2C chapter in the reference manual

3. The maximum SDA hold time (t<sub>HD,DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>)

Figure 4.18. LFRCO Typical Performance at 32.768 kHz

Figure 4.19. ULFRCO Typical Performance at 1 kHz

| QFN      | 48 Pin# and Name |                             | Pin Alternate Functionality / Description                                                                                                                                                                                                                             |                                                                                                                                                                                                                           |                                                                                                                |  |  |  |  |  |  |

|----------|------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin<br># | Pin Name         | Analog                      | Timers                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                             | Other                                                                                                          |  |  |  |  |  |  |

| 24       | PD15             | BUSCY<br>BUSDX              | TIM0_CC0 #23<br>TIM0_CC1 #22<br>TIM0_CC2 #21<br>TIM0_CDTI0 #20<br>TIM0_CDTI1 #19<br>TIM0_CDTI2 #18<br>TIM1_CC0 #23<br>TIM1_CC1 #22<br>TIM1_CC2 #21<br>TIM1_CC3 #20 LE-<br>TIM0_OUT0 #23 LE-<br>TIM0_OUT0 #23 LE-<br>TIM0_OUT1 #22<br>PCNT0_S0IN #23<br>PCNT0_S1IN #22 | US0_TX #23 US0_RX<br>#22 US0_CLK #21<br>US0_CS #20 US0_CTS<br>#19 US0_RTS #18<br>US1_TX #23 US1_RX<br>#22 US1_CLK #21<br>US1_CS #20 US1_CTS<br>#19 US1_RTS #18<br>LEU0_TX #23 LEU0_RX<br>#22 I2C0_SDA #23<br>I2C0_SCL #22 | CMU_CLK1 #5<br>PRS_CH3 #14<br>PRS_CH4 #6 PRS_CH5<br>#5 PRS_CH6 #17<br>ACMP0_0 #23<br>ACMP1_0 #23<br>DBG_SWO #2 |  |  |  |  |  |  |

| 25       | PA0              | ADC0_EXTN<br>BUSCX<br>BUSDY | TIM0_CC0 #0<br>TIM0_CC1 #31<br>TIM0_CC2 #30<br>TIM0_CDT10 #29<br>TIM0_CDT11 #28<br>TIM0_CDT12 #27<br>TIM1_CC0 #0<br>TIM1_CC1 #31<br>TIM1_CC2 #30<br>TIM1_CC3 #29 LE-<br>TIM0_OUT0 #0 LE-<br>TIM0_OUT1 #31<br>PCNT0_S0IN #0<br>PCNT0_S1IN #31                          | US0_TX #0 US0_RX<br>#31 US0_CLK #30<br>US0_CS #29 US0_CTS<br>#28 US0_RTS #27<br>US1_TX #0 US1_RX<br>#31 US1_CLK #30<br>US1_CS #29 US1_CTS<br>#28 US1_RTS #27<br>LEU0_TX #0 LEU0_RX<br>#31 I2C0_SDA #0<br>I2C0_SCL #31     | CMU_CLK1 #0<br>PRS_CH6 #0 PRS_CH7<br>#10 PRS_CH8 #9<br>PRS_CH9 #8 ACMP0_O<br>#0 ACMP1_O #0                     |  |  |  |  |  |  |

| 26       | PA1              | ADC0_EXTP<br>BUSCY<br>BUSDX | TIM0_CC0 #1<br>TIM0_CC1 #0<br>TIM0_CC2 #31<br>TIM0_CDTI0 #30<br>TIM0_CDTI1 #29<br>TIM0_CDTI2 #28<br>TIM1_CC0 #1<br>TIM1_CC1 #0<br>TIM1_CC2 #31<br>TIM1_CC3 #30 LE-<br>TIM0_OUT0 #1 LE-<br>TIM0_OUT0 #1 LE-<br>TIM0_OUT1 #0<br>PCNT0_S0IN #1<br>PCNT0_S1IN #0          | US0_TX #1 US0_RX #0<br>US0_CLK #31 US0_CS<br>#30 US0_CTS #29<br>US0_RTS #28 US1_TX<br>#1 US1_RX #0<br>US1_CLK #31 US1_CS<br>#30 US1_CTS #29<br>US1_RTS #28 LEU0_TX<br>#1 LEU0_RX #0<br>I2C0_SDA #1 I2C0_SCL<br>#0         | CMU_CLK0 #0<br>PRS_CH6 #1 PRS_CH7<br>#0 PRS_CH8 #10<br>PRS_CH9 #9 ACMP0_O<br>#1 ACMP1_O #1                     |  |  |  |  |  |  |

| 27       | PA2              | BUSCX<br>BUSDY              | TIM0_CC0 #2<br>TIM0_CC1 #1<br>TIM0_CC2 #0<br>TIM0_CDTI0 #31<br>TIM0_CDT11 #30<br>TIM0_CDT12 #29<br>TIM1_CC0 #2<br>TIM1_CC1 #1<br>TIM1_CC2 #0<br>TIM1_CC3 #31 LE-<br>TIM0_OUT0 #2 LE-<br>TIM0_OUT0 #2 LE-<br>TIM0_OUT1 #1<br>PCNT0_S0IN #2<br>PCNT0_S1IN #1            | US0_TX #2 US0_RX #1<br>US0_CLK #0 US0_CS<br>#31 US0_CTS #30<br>US0_RTS #29 US1_TX<br>#2 US1_RX #1<br>US1_CLK #0 US1_CS<br>#31 US1_CTS #30<br>US1_RTS #29 LEU0_TX<br>#2 LEU0_RX #1<br>I2C0_SDA #2 I2C0_SCL<br>#1           | PRS_CH6 #2 PRS_CH7<br>#1 PRS_CH8 #0<br>PRS_CH9 #10<br>ACMP0_O #2<br>ACMP1_O #2                                 |  |  |  |  |  |  |

### 6.2.1 EFM32JG1 QFN32 without DC-DC GPIO Overview

The GPIO pins are organized as 16-bit ports indicated by letters (A, B, C...), and the individual pins on each port are indicated by a number from 15 down to 0.

| Port   | Pin<br>15    | Pin<br>14    | Pin<br>13    | Pin<br>12    | Pin<br>11    | Pin<br>10    | Pin 9       | Pin 8       | Pin 7       | Pin 6 | Pin 5 | Pin 4       | Pin 3       | Pin 2       | Pin 1       | Pin 0       |

|--------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------|-------|-------|-------------|-------------|-------------|-------------|-------------|

| Port A | -            | -            | -            | -            | -            | -            | -           | -           | -           | -     | -     | -           | -           | -           | PA1         | PA0         |

| Port B | PB15         | PB14         | PB13<br>(5V) | PB12<br>(5V) | PB11<br>(5V) | -            | -           | -           | -           | -     | -     | -           | -           | -           | -           | -           |

| Port C | -            | -            | -            | -            | PC11<br>(5V) | PC10<br>(5V) | PC9<br>(5V) | PC8<br>(5V) | PC7<br>(5V) | -     | -     | -           | -           | -           | -           | -           |

| Port D | PD15<br>(5V) | PD14<br>(5V) | PD13<br>(5V) | PD12<br>(5V) | PD11<br>(5V) | PD10<br>(5V) | PD9<br>(5V) | -           | -           | -     | -     | -           | -           | -           | -           | -           |

| Port F | -            | -            | -            | -            | -            | -            | -           | -           | -           | -     | -     | PF4<br>(5V) | PF3<br>(5V) | PF2<br>(5V) | PF1<br>(5V) | PF0<br>(5V) |

## Table 6.4. QFN32 without DC-DC GPIO Pinout

Note:

1. GPIO with 5V tolerance are indicated by (5V).

2. The pins PB13, PB12, PB11, PD15, PD14, and PD13 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hardware compatibility, do not use these pins with 5V domains.

### 6.3.1 EFM32JG1 QFN32 with DC-DC GPIO Overview

The GPIO pins are organized as 16-bit ports indicated by letters (A, B, C...), and the individual pins on each port are indicated by a number from 15 down to 0.

| Port   | Pin<br>15    | Pin<br>14    | Pin<br>13    | Pin<br>12    | Pin<br>11    | Pin<br>10    | Pin 9       | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3       | Pin 2       | Pin 1       | Pin 0       |

|--------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------|-------|-------|-------|-------|-------------|-------------|-------------|-------------|

| Port A | -            | -            | -            | -            | -            | -            | -           | -     | -     | -     | -     | -     | -           | -           | PA1         | PA0         |

| Port B | PB15         | PB14         | PB13<br>(5V) | PB12<br>(5V) | PB11<br>(5V) | -            | -           | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port C | -            | -            | -            | -            | PC11<br>(5V) | PC10<br>(5V) | -           | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port D | PD15<br>(5V) | PD14<br>(5V) | PD13<br>(5V) | PD12<br>(5V) | PD11<br>(5V) | PD10<br>(5V) | PD9<br>(5V) | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port F | -            | -            | -            | -            | -            | -            | -           | -     | -     | -     | -     | -     | PF3<br>(5V) | PF2<br>(5V) | PF1<br>(5V) | PF0<br>(5V) |

### Table 6.6. QFN32 with DC-DC GPIO Pinout

Note:

1. GPIO with 5V tolerance are indicated by (5V).

2. The pins PB13, PB12, PB11, PD15, PD14, and PD13 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hardware compatibility, do not use these pins with 5V domains.

| Alternate     |                                         |                                          |                                           | LOC                                         | ATION                                        |                                              |                                          |                                          |                                                              |

|---------------|-----------------------------------------|------------------------------------------|-------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|--------------------------------------------------------------|

| Functionality | 0 - 3                                   | 4 - 7                                    | 8 - 11                                    | 12 - 15                                     | 16 - 19                                      | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                                  |

| TIM0_CC2      | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5    | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14 | 8: PB15<br>9: PC6<br>10: PC7<br>11: PC8   | 12: PC9<br>13: PC10<br>14: PC11<br>15: PD9  | 16: PD10<br>17: PD11<br>18: PD12<br>19: PD13 | 20: PD14<br>21: PD15<br>22: PF0<br>23: PF1   | 24: PF2<br>25: PF3<br>26: PF4<br>27: PF5 | 28: PF6<br>29: PF7<br>30: PA0<br>31: PA1 | Timer 0 Capture<br>Compare input /<br>output channel 2.      |

| TIM0_CDTI0    | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11   | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15 | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11<br>14: PD9<br>15: PD10 | 16: PD11<br>17: PD12<br>18: PD13<br>19: PD14 | 20: PD15<br>21: PF0<br>22: PF1<br>23: PF2    | 24: PF3<br>25: PF4<br>26: PF5<br>27: PF6 | 28: PF7<br>29: PA0<br>30: PA1<br>31: PA2 | Timer 0 Compli-<br>mentary Dead Time<br>Insertion channel 0. |

| TIM0_CDTI1    | 0: PA4<br>1: PA5<br>2: PB11<br>3: PB12  | 4: PB13<br>5: PB14<br>6: PB15<br>7: PC6  | 8: PC7<br>9: PC8<br>10: PC9<br>11: PC10   | 12: PC11<br>13: PD9<br>14: PD10<br>15: PD11 | 16: PD12<br>17: PD13<br>18: PD14<br>19: PD15 | 20: PF0<br>21: PF1<br>22: PF2<br>23: PF3     | 24: PF4<br>25: PF5<br>26: PF6<br>27: PF7 | 28: PA0<br>29: PA1<br>30: PA2<br>31: PA3 | Timer 0 Compli-<br>mentary Dead Time<br>Insertion channel 1. |

| TIM0_CDTI2    | 0: PA5<br>1: PB11<br>2: PB12<br>3: PB13 | 4: PB14<br>5: PB15<br>6: PC6<br>7: PC7   | 8: PC8<br>9: PC9<br>10: PC10<br>11: PC11  | 12: PD9<br>13: PD10<br>14: PD11<br>15: PD12 | 16: PD13<br>17: PD14<br>18: PD15<br>19: PF0  | 20: PF1<br>21: PF2<br>22: PF3<br>23: PF4     | 24: PF5<br>25: PF6<br>26: PF7<br>27: PA0 | 28: PA1<br>29: PA2<br>30: PA3<br>31: PA4 | Timer 0 Compli-<br>mentary Dead Time<br>Insertion channel 2. |

| TIM1_CC0      | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3    | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12   | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10   | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11  | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Timer 1 Capture<br>Compare input /<br>output channel 0.      |

| TIM1_CC1      | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4    | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13  | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11  | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12  | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | Timer 1 Capture<br>Compare input /<br>output channel 1.      |

| TIM1_CC2      | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5    | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14 | 8: PB15<br>9: PC6<br>10: PC7<br>11: PC8   | 12: PC9<br>13: PC10<br>14: PC11<br>15: PD9  | 16: PD10<br>17: PD11<br>18: PD12<br>19: PD13 | 20: PD14<br>21: PD15<br>22: PF0<br>23: PF1   | 24: PF2<br>25: PF3<br>26: PF4<br>27: PF5 | 28: PF6<br>29: PF7<br>30: PA0<br>31: PA1 | Timer 1 Capture<br>Compare input /<br>output channel 2.      |

| TIM1_CC3      | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11   | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15 | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11<br>14: PD9<br>15: PD10 | 16: PD11<br>17: PD12<br>18: PD13<br>19: PD14 | 20: PD15<br>21: PF0<br>22: PF1<br>23: PF2    | 24: PF3<br>25: PF4<br>26: PF5<br>27: PF6 | 28: PF7<br>29: PA0<br>30: PA1<br>31: PA2 | Timer 1 Capture<br>Compare input /<br>output channel 3.      |

| US0_CLK       | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5    | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14 | 8: PB15<br>9: PC6<br>10: PC7<br>11: PC8   | 12: PC9<br>13: PC10<br>14: PC11<br>15: PD9  | 16: PD10<br>17: PD11<br>18: PD12<br>19: PD13 | 20: PD14<br>21: PD15<br>22: PF0<br>23: PF1   | 24: PF2<br>25: PF3<br>26: PF4<br>27: PF5 | 28: PF6<br>29: PF7<br>30: PA0<br>31: PA1 | USART0 clock in-<br>put / output.                            |

| US0_CS        | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11   | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15 | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11<br>14: PD9<br>15: PD10 | 16: PD11<br>17: PD12<br>18: PD13<br>19: PD14 | 20: PD15<br>21: PF0<br>22: PF1<br>23: PF2    | 24: PF3<br>25: PF4<br>26: PF5<br>27: PF6 | 28: PF7<br>29: PA0<br>30: PA1<br>31: PA2 | USART0 chip se-<br>lect input / output.                      |

| US0_CTS       | 0: PA4<br>1: PA5<br>2: PB11<br>3: PB12  | 4: PB13<br>5: PB14<br>6: PB15<br>7: PC6  | 8: PC7<br>9: PC8<br>10: PC9<br>11: PC10   | 12: PC11<br>13: PD9<br>14: PD10<br>15: PD11 | 16: PD12<br>17: PD13<br>18: PD14<br>19: PD15 | 20: PF0<br>21: PF1<br>22: PF2<br>23: PF3     | 24: PF4<br>25: PF5<br>26: PF6<br>27: PF7 | 28: PA0<br>29: PA1<br>30: PA2<br>31: PA3 | USART0 Clear To<br>Send hardware<br>flow control input.      |

| US0_RTS       | 0: PA5<br>1: PB11<br>2: PB12<br>3: PB13 | 4: PB14<br>5: PB15<br>6: PC6<br>7: PC7   | 8: PC8<br>9: PC9<br>10: PC10<br>11: PC11  | 12: PD9<br>13: PD10<br>14: PD11<br>15: PD12 | 16: PD13<br>17: PD14<br>18: PD15<br>19: PF0  | 20: PF1<br>21: PF2<br>22: PF3<br>23: PF4     | 24: PF5<br>25: PF6<br>26: PF7<br>27: PA0 | 28: PA1<br>29: PA2<br>30: PA3<br>31: PA4 | USART0 Request<br>To Send hardware<br>flow control output.   |

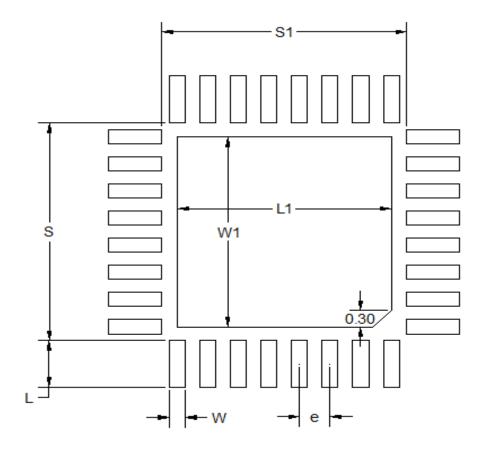

| Dimension | Min      | Tvn  | Мах  |  |  |  |  |

|-----------|----------|------|------|--|--|--|--|

|           |          | Тур  |      |  |  |  |  |

| A         | 0.80     | 0.85 | 0.90 |  |  |  |  |

| A1        | 0.00     | 0.02 | 0.05 |  |  |  |  |

| A3        | 0.20 REF |      |      |  |  |  |  |

| b         | 0.18     | 0.25 | 0.30 |  |  |  |  |

| D/E       | 4.90     | 5.00 | 5.10 |  |  |  |  |

| D2/E2     | 3.40     | 3.50 | 3.60 |  |  |  |  |

| E         | 0.50 BSC |      |      |  |  |  |  |

| L         | 0.30     | 0.40 | 0.50 |  |  |  |  |

| К         | 0.20     |      |      |  |  |  |  |

| R         | 0.09     |      | 0.14 |  |  |  |  |

| ааа       | 0.15     |      |      |  |  |  |  |

| bbb       |          | 0.10 |      |  |  |  |  |

| ссс       | 0.10     |      |      |  |  |  |  |

| ddd       | 0.05     |      |      |  |  |  |  |

| eee       | 0.08     |      |      |  |  |  |  |

| fff       |          | 0.10 |      |  |  |  |  |

| Noto:     | 1        |      |      |  |  |  |  |

### Table 8.1. QFN32 Package Dimensions

## Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MO-220, Variation VKKD-4.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 8.2 QFN32 PCB Land Pattern

Figure 8.2. QFN32 PCB Land Pattern Drawing

### Table 8.2. QFN32 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| S1        | 4.01 |

| S         | 4.01 |

| L1        | 3.50 |

| W1        | 3.50 |

| e         | 0.50 |

| W         | 0.26 |

| L         | 0.86 |

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

5. The stencil thickness should be 0.125 mm (5 mils).

6. The ratio of stencil aperture to land pad size can be 1:1 for all perimeter pads.

7. A 3x3 array of 0.85 mm square openings on a 1.00 mm pitch can be used for the center ground pad.

8. A No-Clean, Type-3 solder paste is recommended.

9. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

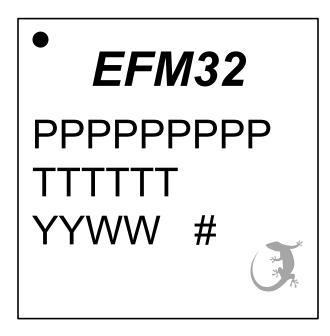

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

- # Reserved for future use. Current value is 0.

## 9.7 Revision 0.1

Initial release.