## Microchip Technology - PIC18F2220-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2220-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

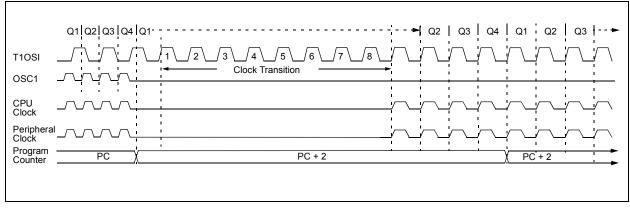

## 2.7.2 OSCILLATOR TRANSITIONS

The PIC18F2X20/4X20 devices contain circuitry to prevent clocking "glitches" when switching between clock sources. A short pause in the system clock occurs during the clock switch. The length of this pause is between 8 and 9 clock periods of the new clock source. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes"**.

### 2.8 Effects of Power-Managed Modes on the Various Clock Sources

When the device executes a SLEEP instruction, the system is switched to one of the power-managed modes, depending on the state of the IDLEN and SCS1:SCS0 bits of the OSCCON register. See **Section 3.0 "Power-Managed Modes"** for details.

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the system clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the system clock source. The INTRC output can be used directly to provide the system clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 23.2 "Watchdog Timer (WDT)" through Section 23.4 "Fail-Safe Clock Monitor"). The INTOSC output at 8 MHz may be used directly to clock the system or may be divided down first. The INTOSC output is disabled if the system clock is provided directly from the INTRC output. If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a system clock source (i.e., MSSP slave, PSP, INTx pins, A/D conversions and others).

## 2.9 Power-up Delays

Power-up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see Section 4.1 "Power-on Reset (POR)" through Section 4.5 "Brown-out Reset (BOR)".

The first timer is the Power-up Timer (PWRT) which provides a fixed delay on power-up (parameter 33, Table 26-10), if enabled, in Configuration Register 2L. The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms, following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of 5 to 10  $\mu s,$  following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| OSC Mode       | OSC1 Pin                                                 | OSC2 Pin                                                 |

|----------------|----------------------------------------------------------|----------------------------------------------------------|

| RC, INTIO1     | Floating, external resistor should pull high             | At logic low (clock/4 output)                            |

| RCIO, INTIO2   | Floating, external resistor should pull high             | Configured as PORTA, bit 6                               |

| ECIO           | Floating, pulled by external clock                       | Configured as PORTA, bit 6                               |

| EC             | Floating, pulled by external clock                       | At logic low (clock/4 output)                            |

| LP, XT, and HS | Feedback inverter disabled at<br>quiescent voltage level | Feedback inverter disabled at<br>quiescent voltage level |

#### TABLE 2-3: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-1 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

## 3.4 Run Modes

If the IDLEN bit is clear when a SLEEP instruction is executed, the CPU and peripherals are both clocked from the source selected using the SCS1:SCS0 bits. While these operating modes may not afford the power conservation of Idle or Sleep modes, they do allow the device to continue executing instructions by using a lower frequency clock source. RC\_RUN mode also offers the possibility of executing code at a frequency greater than the primary clock.

Wake-up from a power-managed Run mode can be triggered by an interrupt, or any Reset, to return to full-power operation. As the CPU is executing code in Run modes, several additional exits from Run modes are possible. They include exit to Sleep mode, exit to a corresponding Idle mode, and exit by executing a RESET instruction. While the device is in any of the power-managed Run modes, a WDT time-out will result in a WDT Reset.

#### 3.4.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal full-power execution mode. If the SLEEP instruction is never executed, the microcontroller operates in this mode (a SLEEP instruction is executed to enter all other power-managed modes). All other power-managed modes exit to PRI\_RUN mode when an interrupt or WDT time-out occur.

There is no entry to PRI\_RUN mode. The OSTS bit is set. The IOFS bit may be set if the internal oscillator block is the primary clock source (see Section 2.7.1 "Oscillator Control Register").

#### 3.4.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of lower power consumption while still using a high-accuracy clock source.

SEC\_RUN mode is entered by clearing the IDLEN bit, setting SCS1:SCS0 = 01 and executing a SLEEP instruction. The system clock source is switched to the Timer1 oscillator (see Figure 3-9), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when trying to set the SCS0 bit, the write to SCS0 will not occur. If the Timer1 oscillator is enabled, but not yet running, system clocks will be delayed until the oscillator has started; in such situations, initial oscillator operation is far from stable and unpredictable operation may result.

When a wake-up event occurs, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 3-6). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

Firmware can force an exit from SEC\_RUN mode. By clearing the T1OSCEN bit (T1CON<3>), an exit from SEC\_RUN back to normal full-power operation is triggered. The Timer1 oscillator will continue to run and provide the system clock even though the T1OSCEN bit is cleared. The primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 3-6). When the clock switch is cleared, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up.

## FIGURE 3-9: TIMING TRANSITION FOR ENTRY TO SEC\_RUN MODE

#### 4.1 Power-on Reset (POR)

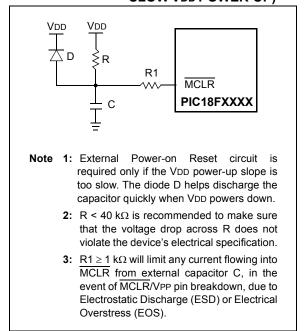

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, just tie the MCLR pin through a resistor (1k to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

FIGURE 4-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

### 4.2 Power-up Timer (PWRT)

The Power-up Timer (PWRT) of the PIC18F2X20/4X20 devices is an 11-bit counter, which uses the INTRC source as the clock input. This yields a count of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter #33 for details.

The PWRT is enabled by clearing Configuration bit, PWRTEN.

## 4.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most power-managed modes.

#### 4.4 PLL Lock Time-out

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 4.5 Brown-out Reset (BOR)

A Configuration bit, BOREN, can disable (if clear/ programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below VBOR (parameter D005) for greater than TBOR (parameter #35), the brown-out situation will reset the chip. A Reset may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR. If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay TPWRT (parameter #33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay. Enabling BOR Reset does not automatically enable the PWRT.

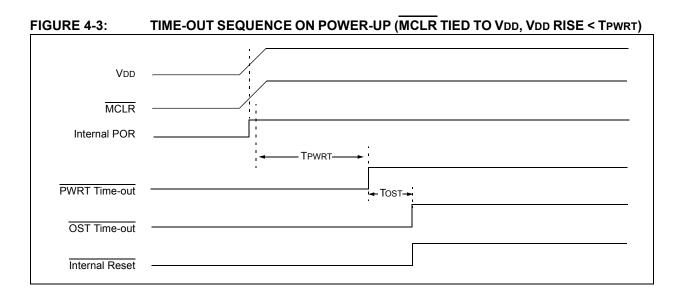

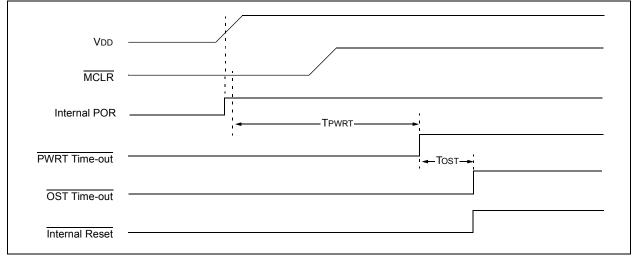

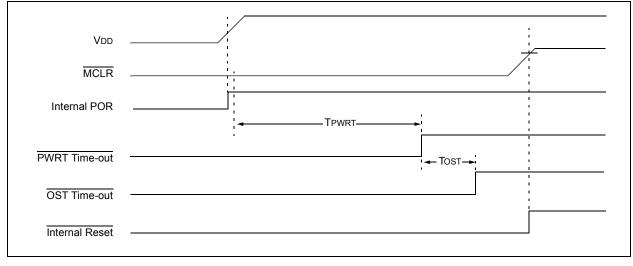

### 4.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, after the POR pulse has cleared, PWRT time-out is invoked (if enabled). Then, the OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

Table 4-2 shows the Reset conditions for some Special Function Registers, while Table 4-3 shows the Reset conditions for all the registers.

#### FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

#### FIGURE 4-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

NOTES:

| TABLE 5-2              |                     | JUIER               |                         | MARY (P    |              | .0/2320/4/     | 220/4320)                   |         | 1                    |                     |

|------------------------|---------------------|---------------------|-------------------------|------------|--------------|----------------|-----------------------------|---------|----------------------|---------------------|

| File Name              | Bit 7               | Bit 6               | Bit 5                   | Bit 4      | Bit 3        | Bit 2          | Bit 1                       | Bit 0   | Value on<br>POR, BOR | Details on<br>page: |

| OSCCON                 | IDLEN               | IRCF2               | IRCF1                   | IRCF0      | OSTS         | IOFS           | SCS1                        | SCS0    | 0000 q000            | 27, 47              |

| LVDCON                 | —                   |                     | IRVST                   | LVDEN      | LVDL3        | LVDL2          | LVDL1                       | LVDL0   | 00 0101              | 47, 233             |

| WDTCON                 | —                   |                     |                         | —          | _            |                | —                           | SWDTEN  | 0                    | 47, 247             |

| RCON                   | IPEN                | _                   | _                       | RI         | TO           | PD             | POR                         | BOR     | 01 11q0              | 45, 69, 98          |

| TMR1H                  | Timer1 Regis        | XXXX XXXX           | 47, 125                 |            |              |                |                             |         |                      |                     |

| TMR1L                  | Timer1 Regis        | ster Low Byte       |                         |            |              |                |                             |         | XXXX XXXX            | 47, 125             |

| T1CON                  | RD16                | T1RUN               | T1CKPS1                 | T1CKPS0    | T1OSCEN      | T1SYNC         | TMR1CS                      | TMR10N  | 0000 0000            | 47, 121             |

| TMR2                   | Timer2 Regis        | 0000 0000           | 47, 127                 |            |              |                |                             |         |                      |                     |

| PR2                    | Timer2 Perio        | 1111 1111           | 47, 127                 |            |              |                |                             |         |                      |                     |

| T2CON                  | —                   | TOUTPS3             | TOUTPS2                 | TOUTPS1    | TOUTPS0      | TMR2ON         | T2CKPS1                     | T2CKPS0 | -000 0000            | 47, 127             |

| SSPBUF                 | MSSP Recei          | ve Buffer/Trar      | nsmit Register          | -          |              |                |                             |         | XXXX XXXX            | 47, 156,<br>164     |

| SSPADD                 | MSSP Addre          | ss Register ir      | I <sup>2</sup> C™ Slave | mode. MSSP | Baud Rate Re | eload Register | r in I <sup>2</sup> C Maste | r mode. | 0000 0000            | 47, 164             |

| SSPSTAT                | SMP                 | CKE                 | D/Ā                     | Р          | S            | R/W            | UA                          | BF      | 0000 0000            | 47, 156,<br>165     |

| SSPCON1                | WCOL                | SSPOV               | SSPEN                   | СКР        | SSPM3        | SSPM2          | SSPM1                       | SSPM0   | 0000 0000            | 47, 157,<br>166     |

| SSPCON2                | GCEN                | ACKSTAT             | ACKDT                   | ACKEN      | RCEN         | PEN            | RSEN                        | SEN     | 0000 0000            | 47, 167             |

| ADRESH                 | A/D Result R        | egister High E      | Byte                    | •          | •            |                | •                           | •       | XXXX XXXX            | 48, 220             |

| ADRESL                 | A/D Result R        | egister Low B       | yte                     |            |              |                |                             |         | XXXX XXXX            | 48, 220             |

| ADCON0                 | _                   | _                   | CHS3                    | CHS2       | CHS1         | CHS0           | GO/DONE                     | ADON    | 00 0000              | 48, 211             |

| ADCON1                 | —                   | _                   | VCFG1                   | VCFG0      | PCFG3        | PCFG2          | PCFG1                       | PCFG0   | 00 0qqq              | 48, 212             |

| ADCON2                 | ADFM                | -                   | ACQT2                   | ACQT1      | ACQT0        | ADCS2          | ADCS1                       | ADCS0   | 0-00 0000            | 48, 213             |

| CCPR1H                 | Capture/Com         | pare/PWM R          | egister 1 High          | n Byte     | •            |                | •                           | •       | XXXX XXXX            | 48, 134             |

| CCPR1L                 | Capture/Com         | npare/PWM R         | egister 1 Low           | Byte       |              |                |                             |         | XXXX XXXX            | 48, 134             |

| CCP1CON                | P1M1 <sup>(5)</sup> | P1M0 <sup>(5)</sup> | DC1B1                   | DC1B0      | CCP1M3       | CCP1M2         | CCP1M1                      | CCP1M0  | 0000 0000            | 48, 133,<br>141     |

| CCPR2H                 | Capture/Com         | npare/PWM R         | egister 2 High          | Byte       |              |                |                             |         | XXXX XXXX            | 48, 134             |

| CCPR2L                 | Capture/Com         | npare/PWM R         | egister 2 Low           | Byte       |              |                |                             |         | XXXX XXXX            | 48, 134             |

| CCP2CON                | —                   |                     | DC2B1                   | DC2B0      | CCP2M3       | CCP2M2         | CCP2M1                      | CCP2M0  | 00 0000              | 48, 133             |

| PWM1CON <sup>(5)</sup> | PRSEN               | PDC6                | PDC5                    | PDC4       | PDC3         | PDC2           | PDC1                        | PDC0    | 0000 0000            | 48, 149             |

| ECCPAS <sup>(5)</sup>  | ECCPASE             | ECCPAS2             | ECCPAS1                 | ECCPAS0    | PSSAC1       | PSSAC0         | PSSBD1                      | PSSBD0  | 0000 0000            | 48, 150             |

| CVRCON                 | CVREN               | CVROE               | CVRR                    | —          | CVR3         | CVR2           | CVR1                        | CVR0    | 000- 0000            | 48, 227             |

| CMCON                  | C2OUT               | C1OUT               | C2INV                   | C1INV      | CIS          | CM2            | CM1                         | CM0     | 0000 0111            | 48, 221             |

| TMR3H                  | Timer3 Regis        | ster High Byte      |                         |            |              |                |                             |         | XXXX XXXX            | 48, 131             |

| TMR3L                  | Timer3 Regis        | ster Low Byte       |                         |            | -            |                |                             |         | XXXX XXXX            | 48, 131             |

| T3CON                  | RD16                | T3CCP2              | T3CKPS1                 | T3CKPS0    | T3CCP1       | T3SYNC         | TMR3CS                      | TMR3ON  | 0000 0000            | 48, 129             |

| SPBRG                  | USART Bau           | d Rate Genera       | ator                    |            |              |                |                             |         | 0000 0000            | 48, 198             |

| RCREG                  | USART Rece          | eive Register       |                         |            |              |                |                             |         | 0000 0000            | 48, 204,<br>203     |

| TXREG                  | USART Tran          | smit Register       |                         |            |              |                |                             |         | 0000 0000            | 48, 202,<br>203     |

| TXSTA                  | CSRC                | TX9                 | TXEN                    | SYNC       | _            | BRGH           | TRMT                        | TX9D    | 0000 -010            | 48, 196             |

| RCSTA                  | SPEN                | RX9                 | SREN                    | CREN       | ADDEN        | FERR           | OERR                        | RX9D    | 0000 000x            | 48, 197             |

#### TABLE 5-2:REGISTER FILE SUMMARY (PIC18F2220/2320/4220/4320) (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO, ECIO and INTIO2 (with port function on RA6) Oscillator mode only and read as '0' in all other oscillator modes.

2: RA7 and associated bits are configured as port pins in INTIO2 Oscillator mode only and read as '0' in all other modes.

3: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

4: If PBADEN = 0, PORTB<4:0> are configured as digital inputs and read unknown and if PBADEN = 1, PORTB<4:0> are configured as analog inputs and read as '0' following a Reset.

5: These registers and/or bits are not implemented on the PIC18F2X20 devices and read as 0x00.

6: The RE3 port bit is available as an input only pin only in 40-pin devices when Master Clear functionality is disabled (CONFIG3H<7>= 0).

### 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 9-6: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|-------|--------|--------|--------|

| PSPIE <sup>(1)</sup> | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7                |       |       |       |       |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>BEDIE:</b> Derallel Slave Dort Bood/Mrite Interrupt Enable hit(1)             |

|-------|----------------------------------------------------------------------------------|

| DIL 7 | <b>PSPIE:</b> Parallel Slave Port Read/Write Interrupt Enable bit <sup>(1)</sup> |

|       | 1 = Enables the PSP read/write interrupt                                         |

|       | 0 = Disables the PSP read/write interrupt                                        |

| bit 6 | ADIE: A/D Converter Interrupt Enable bit                                         |

|       | 1 = Enables the A/D interrupt                                                    |

|       | 0 = Disables the A/D interrupt                                                   |

| bit 5 | RCIE: USART Receive Interrupt Enable bit                                         |

|       | 1 = Enables the USART receive interrupt                                          |

|       | 0 = Disables the USART receive interrupt                                         |

| bit 4 | TXIE: USART Transmit Interrupt Enable bit                                        |

|       | 1 = Enables the USART transmit interrupt                                         |

|       | 0 = Disables the USART transmit interrupt                                        |

| bit 3 | SSPIE: Master Synchronous Serial Port Interrupt Enable bit                       |

|       | 1 = Enables the MSSP interrupt                                                   |

|       | 0 = Disables the MSSP interrupt                                                  |

| bit 2 | CCP1IE: CCP1 Interrupt Enable bit                                                |

|       | 1 = Enables the CCP1 interrupt                                                   |

|       | 0 = Disables the CCP1 interrupt                                                  |

| bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit                                   |

|       | 1 = Enables the TMR2 to PR2 match interrupt                                      |

|       | 0 = Disables the TMR2 to PR2 match interrupt                                     |

| bit 0 | TMR1IE: TMR1 Overflow Interrupt Enable bit                                       |

|       | 1 = Enables the TMR1 overflow interrupt                                          |

|       | 0 = Disables the TMR1 overflow interrupt                                         |

|       |                                                                                  |

**Note 1:** This bit is reserved on PIC18F2X20 devices; always maintain this bit clear.

| Name                   | Bit#  | Buffer | Function                                                                                                                                  |

|------------------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                | bit 0 | TTL    | Input/output or analog input.                                                                                                             |

| RA1/AN1                | bit 1 | TTL    | Input/output or analog input.                                                                                                             |

| RA2/AN2/VREF-/CVREF    | bit 2 | TTL    | Input/output, analog input, VREF- or comparator VREF output.                                                                              |

| RA3/AN3/VREF+          | bit 3 | TTL    | Input/output, analog input or VREF+.                                                                                                      |

| RA4/T0CKI/C1OUT        | bit 4 | ST     | Input/output, external clock input for Timer0 or Comparator 1 output. Output is open-drain type.                                          |

| RA5/AN4/SS/LVDIN/C2OUT | bit 5 | TTL    | Input/output, analog input, slave select input for Master<br>Synchronous Serial Port, Low-Voltage Detect input or<br>Comparator 2 output. |

| OSC2/CLKO/RA6          | bit 6 | TTL    | OSC2, clock output or I/O pin.                                                                                                            |

| OSC1/CLKI/RA7          | bit 7 | TTL    | OSC1, clock input or I/O pin.                                                                                                             |

#### TABLE 10-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7                 | Bit 6                 | Bit 5     | Bit 4                   | Bit 3      | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------|-----------------------|-----------|-------------------------|------------|-------|-------|-------|----------------------|---------------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5       | RA5 RA4 RA3 RA2 RA1 RA0 |            |       |       |       |                      | uu0u 0000                       |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA Data | a Latch Reg             | gister     |       |       |       | XXXX XXXX            | uuuu uuuu                       |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA D   | ata Directio            | n Register |       |       |       | 1111 1111            | 1111 1111                       |

| ADCON1 | —                     | —                     | VCFG1     | VCFG0                   | PCFG3      | PCFG2 | PCFG1 | PCFG0 | 00 0000              | 00 0000                         |

| CMCON  | C2OUT                 | C10UT                 | C2INV     | C1INV                   | CIS        | CM2   | CM1   | CM0   | 0000 0111            | 0000 0111                       |

| CVRCON | CVREN                 | CVROE                 | CVRR      |                         | CVR3       | CVR2  | CVR1  | CVR0  | 000- 0000            | 000- 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA7:RA6 and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

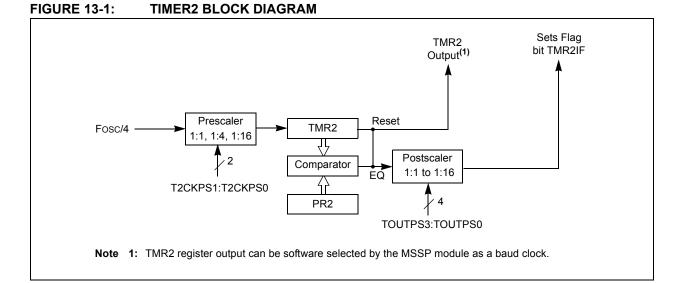

#### 13.2 Timer2 Interrupt

The Timer2 module has an 8-bit Period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

#### 13.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate the shift clock.

| Name   | Bit 7                | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------|---------------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL     | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF  | RBIF    | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF          | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE          | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP          | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP  | TMR1IP  | 1111 1111            | 1111 1111                       |

| TMR2   | Timer2 Mod           | dule Register | r       |         |         |        |         |         | 0000 0000            | 0000 0000                       |

| T2CON  | _                    | TOUTPS3       | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| PR2    | Timer2 Per           | iod Register  |         |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| OSCCON | IDLEN                | IRCF2         | IRCF1   | IRCF0   | OSTS    | IOFS   | SCS1    | SCS0    | 0000 qq00            | 0000 qq00                       |

$\label{eq:logarder} \mbox{Legend:} \quad x \mbox{=} unknown, u \mbox{=} unchanged, \mbox{-} \mbox{=} unimplemented, read as `0'. Shaded cells are not used by the Timer2 module.$

**Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

## 15.0 CAPTURE/COMPARE/PWM (CCP) MODULES

The standard CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. Table 15-1 shows the timer resources required for each of the CCP module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the Special Event Trigger. Therefore, operation of a CCP module is described with respect to CCP1 except where noted. Table 15-2 shows the interaction of the CCP modules. Note: In 28-pin devices, both CCP1 and CCP2 function as standard CCP modules. In 40-pin devices, CCP1 is implemented as an Enhanced CCP module, offering additional capabilities in PWM mode. Capture and Compare modes are identical in all modules regardless of the device.

> Please see Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module" for a discussion of the enhanced PWM capabilities of the CCP1 module.

#### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

| U-0          | U-0                                                                               | R/W-0                                                                                     | R/W-0          | R/W-0            | R/W-0           | R/W-0            | R/W-0          |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|------------------|-----------------|------------------|----------------|--|--|--|--|--|--|

| _            | _                                                                                 | DCxB1                                                                                     | DCxB0          | CCPxM3           | CCPxM2          | CCPxM1           | CCPxM0         |  |  |  |  |  |  |

| bit 7        |                                                                                   |                                                                                           |                |                  |                 |                  | bit 0          |  |  |  |  |  |  |

| Legend:      |                                                                                   |                                                                                           |                |                  |                 |                  |                |  |  |  |  |  |  |

| R = Readal   | ble bit                                                                           | W = Writable                                                                              | bit            | U = Unimpler     | mented bit, rea | d as '0'         |                |  |  |  |  |  |  |

| -n = Value a | Value at POR'1' = Bit is set'0' = Bit is cleared                                  |                                                                                           | ared           | x = Bit is unk   | nown            |                  |                |  |  |  |  |  |  |

| bit 7-6      | Unimplemen                                                                        | ited: Read as '                                                                           | 0'             |                  |                 |                  |                |  |  |  |  |  |  |

| bit 5-4      | -                                                                                 | B0: PWM Duty                                                                              |                | nd Bit 0 for CCI | Px Module       |                  |                |  |  |  |  |  |  |

|              |                                                                                   |                                                                                           | (bit 1 and bit | 0) of the 10-bit | PWM duty cyc    | le. The eight M  | Sbs of the dut |  |  |  |  |  |  |

| bit 3-0      | ,                                                                                 | PxM0: CCPx M                                                                              | lode Select b  | its              |                 |                  |                |  |  |  |  |  |  |

|              | 0001 = Rese                                                                       |                                                                                           |                |                  | ,               |                  |                |  |  |  |  |  |  |

|              | 0011 = Rese                                                                       |                                                                                           |                | -                | F DIT IS SET)   |                  |                |  |  |  |  |  |  |

|              | 0100 = Capture mode: every falling edge<br>0101 = Capture mode: every rising edge |                                                                                           |                |                  |                 |                  |                |  |  |  |  |  |  |

|              |                                                                                   |                                                                                           |                |                  |                 |                  |                |  |  |  |  |  |  |

|              |                                                                                   | 0110 = Capture mode: every 4th rising edge<br>0111 = Capture mode: every 16th rising edge |                |                  |                 |                  |                |  |  |  |  |  |  |

|              |                                                                                   | pare mode: init                                                                           |                |                  | pare match, for | ce CCPx pin hi   | gh (CCPxIF bi  |  |  |  |  |  |  |

|              | 1001 = Com<br>is se                                                               | ,<br>pare mode: init<br>t)                                                                | ialize CCPx p  | in high; on com  | pare match, fo  | rce CCPx pin lo  | ow (CCPxIF bi  |  |  |  |  |  |  |

|              |                                                                                   | pare mode: ger<br>ates as a port p                                                        |                | •                | compare match   | n (CCPxIF bit is | set, CCPx pi   |  |  |  |  |  |  |

|              | 1011 = Com<br>11xx = PWN                                                          | pare mode: trig<br>/ mode                                                                 | ger special e  | vent (CCPxIF b   | oit is set)     |                  |                |  |  |  |  |  |  |

## 16.4.4 PROGRAMMABLE DEAD-BAND DELAY

In half-bridge applications, where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shootthrough current*) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead band delay is available to avoid shootthrough current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 16-4 for illustration. The lower seven bits of the PWM1CON register (Register 16-2) set the delay period in terms of microcontroller instruction cycles (TCY or 4 TOSC).

#### 16.4.5 ENHANCED PWM AUTO-SHUTDOWN

When the ECCP is programmed for any of the enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the enhanced PWM output pins into a defined shutdown state when a shutdown event occurs. A shutdown event can be caused by either of the two comparator modules or the INT0 pin (or any combination of these three sources). The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a digital signal on the INT0 pin can also trigger a shutdown. The autoshutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCPAS2:ECCPAS0 bits (ECCPAS<6:4>).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits (ECCPAS<3:0>). Each pin pair (P1A/P1C and P1B/ P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCPASE bit (ECCPAS<7>) is also set to hold the enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|------------------------------------|-------|----------------|-------|------------------|------------------|-----------------|-------|

| R = Readable I                     |       | W = Writable I |       | U = Unimpler     | nented bit, read | read as '0'     |       |

| Legend:                            |       |                |       |                  |                  |                 |       |

| bit 7                              |       |                |       |                  |                  |                 | bit 0 |

| PRSEN                              | PDC6  | PDC5           | PDC4  | PDC3             | PDC2             | PDC1            | PDC0  |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

### REGISTER 16-2: PWM1CON: PWM CONFIGURATION REGISTER

|         | the PWM restarts automatically                                                 |

|---------|--------------------------------------------------------------------------------|

|         | 0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM |

| bit 6-0 | PDC6:PDC0: PWM Delay Count bits                                                |

Delay time, in number of Fosc/4 (4 \* Tosc) cycles, between the scheduled time when a PWM signal should transition to active and the actual time it transitions active.

1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away;

#### 17.4.3.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit, BF (SSPSTAT<0>), is set or bit, SSPOV (SSPCON1<6>), is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPCON1<4>). See **Section 17.4.4** "Clock **Stretching**" for more detail.

#### 17.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see Section 17.4.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the RC3/ SCK/SCL pin should be enabled by setting bit, CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 17-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, the RC3/SCK/SCL pin must be enabled by setting bit, CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

NOTES:

After Instruction

If Carry PC If Carry PC

= = =

| ANDWF                       | AND W with f                                                                                                                                                                                     |                                                                                        | BC                | Branch if                                                                                                                                | Carry                  |                 |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|--|

| Syntax:                     | [label] ANDWF                                                                                                                                                                                    | f [,d [,a]]                                                                            | Syntax:           | [ <i>label</i> ] B                                                                                                                       | C n                    |                 |  |

| Operands: $0 \le f \le 255$ |                                                                                                                                                                                                  | Operands:                                                                              | -128 ≤ n ≤        | $-128 \le n \le 127$                                                                                                                     |                        |                 |  |

|                             | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                           |                                                                                        | Operation:        | if Carry bi<br>(PC) + 2 -                                                                                                                | t is '1',<br>⊦ 2n → PC |                 |  |

| Operation:                  | (W) .AND. (f) $\rightarrow$ dest                                                                                                                                                                 |                                                                                        | Status Affected   | t: None                                                                                                                                  |                        |                 |  |

| Status Affected:            | N, Z                                                                                                                                                                                             |                                                                                        | Encoding:         | 1110                                                                                                                                     | 0010 nn                | nn nnnn         |  |

| Encoding:                   | 0001 01da f                                                                                                                                                                                      | fff ffff                                                                               | Description:      | If the Car                                                                                                                               | y bit is '1', th       | nen the         |  |

| Description:                | The contents of W are<br>register 'f'. If 'd' is '0',<br>stored in W. If 'd' is '1<br>stored back in registe<br>If 'a' is '0', the Access<br>selected. If 'a' is '1', t<br>not be overridden (de | the result is<br>, the result is<br>er 'f' (default).<br>s Bank will be<br>he BSR will |                   | program will brar<br>The 2's complem<br>added to the PC<br>have incremente<br>instruction, the n<br>PC + 2 + 2n. Thi<br>then a two-cycle |                        |                 |  |

| Words:                      | 1                                                                                                                                                                                                |                                                                                        | Words:            | 1                                                                                                                                        |                        |                 |  |

| Cycles:                     | 1                                                                                                                                                                                                |                                                                                        | Cycles:           | 1(2)                                                                                                                                     |                        |                 |  |

| Q Cycle Activity:           |                                                                                                                                                                                                  |                                                                                        | Q Cycle Activity: |                                                                                                                                          |                        |                 |  |

| Q1                          | Q2 Q3                                                                                                                                                                                            | Q4                                                                                     | If Jump:          |                                                                                                                                          |                        |                 |  |

| Decode                      | Read Process                                                                                                                                                                                     | Write to                                                                               | Q1                | Q2                                                                                                                                       | Q3                     | Q4              |  |

|                             | register 'f' Data                                                                                                                                                                                | destination                                                                            | Decode            | Read literal<br>'n'                                                                                                                      | Process<br>Data        | Write to PC     |  |

| Example:                    | ANDWF REG, W                                                                                                                                                                                     |                                                                                        | No<br>operation   | No<br>operation                                                                                                                          | No<br>operation        | No<br>operation |  |

| Before Instru               |                                                                                                                                                                                                  |                                                                                        | If No Jump:       |                                                                                                                                          |                        |                 |  |

| W<br>REG                    | = 0x17<br>= 0xC2                                                                                                                                                                                 |                                                                                        | Q1                | Q2                                                                                                                                       | Q3                     | Q4              |  |

| After Instruction           |                                                                                                                                                                                                  |                                                                                        | Decode            | Read literal<br>'n'                                                                                                                      | Process<br>Data        | No<br>operation |  |

| W<br>REG                    | = 0x02<br>= 0xC2                                                                                                                                                                                 |                                                                                        |                   | '                                                                                                                                        | Dulu                   | operation       |  |

| KEG                         | - 0x02                                                                                                                                                                                           |                                                                                        | Example:          | HERE                                                                                                                                     | BC JUME                |                 |  |

|                             |                                                                                                                                                                                                  | Before Instruction<br>PC = address (HERE)                                              |                   |                                                                                                                                          |                        |                 |  |

1; address (JUMP) 0; address (HERE + 2)

| BRA                                          | <b>x</b>                                                        | Unconditi                                                                                                | ional Branci            | h                                                          | BS                                                          | F                                    | Bit Set f            |                                                                                                                       |                               |  |

|----------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------|--|

| Synt                                         | tax:                                                            | [ <i>label</i> ] B                                                                                       | RA n                    |                                                            | Sy                                                          | Syntax: [ <i>label</i> ] BSF f,b[,a] |                      |                                                                                                                       |                               |  |

| Ope                                          | rands:                                                          | $-1024 \le n \le 1023$                                                                                   |                         |                                                            | Ор                                                          | erands:                              | $0 \leq f \leq 255$  |                                                                                                                       |                               |  |

| Ope                                          | Dperation: $(PC) + 2 + 2n \rightarrow PC$                       |                                                                                                          |                         |                                                            | $0 \le b \le 7$                                             |                                      |                      |                                                                                                                       |                               |  |

| Status Affected: None                        |                                                                 | On                                                                                                       | oration:                | a ∈ [0,1]<br>1 → f <b></b>                                 |                                                             |                                      |                      |                                                                                                                       |                               |  |

| Enco                                         | oding:                                                          | 1101 Onnn nnnn nnnn                                                                                      |                         | -                                                          | Operation:<br>Status Affected:<br>Encoding:<br>Description: |                                      | None                 |                                                                                                                       |                               |  |

| Des                                          | cription:                                                       | Add the 2's complement number<br>'2n' to the PC. Since the PC will<br>have incremented to fetch the next |                         |                                                            |                                                             |                                      | En                   | bbba ff:<br>gister 'f' is se                                                                                          | ff ffff<br>et. If 'a' is '0', |  |

|                                              |                                                                 | instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>two-cycle instruction.     |                         |                                                            |                                                             |                                      |                      | Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then<br>the bank will be selected as per the |                               |  |

| Wor                                          | ds:                                                             | 1                                                                                                        |                         |                                                            |                                                             |                                      | BSR value            | <b>)</b> .                                                                                                            |                               |  |

| Cycl                                         | es:                                                             | 2                                                                                                        |                         |                                                            |                                                             | ords:                                | 1                    |                                                                                                                       |                               |  |

| QC                                           | Cycle Activity:                                                 | :                                                                                                        |                         |                                                            | Cy                                                          | cles:                                | 1                    |                                                                                                                       |                               |  |

|                                              | Q1                                                              | Q2                                                                                                       | Q3                      | Q4                                                         | Q                                                           | Cycle Activity                       | :                    |                                                                                                                       |                               |  |

|                                              | Decode                                                          | Read literal                                                                                             | Process                 | Write to PC                                                |                                                             | Q1                                   | Q2                   | Q3                                                                                                                    | Q4                            |  |

|                                              | No<br>operation                                                 | ʻn'<br>No<br>operation                                                                                   | Data<br>No<br>operation | No<br>operation                                            |                                                             | Decode                               | Read<br>register 'f' | Process<br>Data                                                                                                       | Write<br>register 'f'         |  |

|                                              |                                                                 |                                                                                                          |                         |                                                            | Exa                                                         | ample:                               | BSF F                | LAG_REG, 7                                                                                                            |                               |  |

| Example: HERE BRA Jump<br>Before Instruction |                                                                 |                                                                                                          |                         | Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction |                                                             |                                      |                      |                                                                                                                       |                               |  |

|                                              | PC = address (HERE)<br>After Instruction<br>PC = address (Jump) |                                                                                                          |                         |                                                            |                                                             | $FLAG_REG = 0x8A$                    |                      |                                                                                                                       |                               |  |

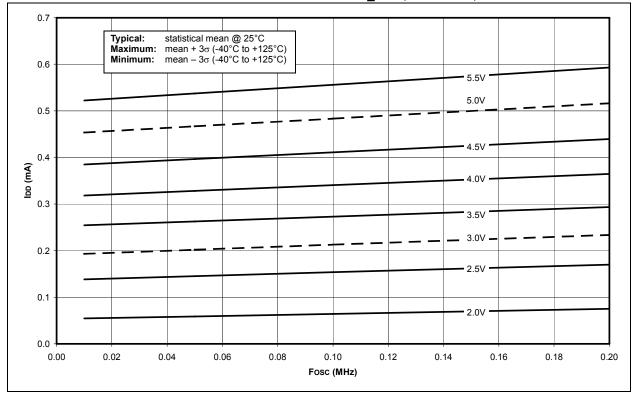

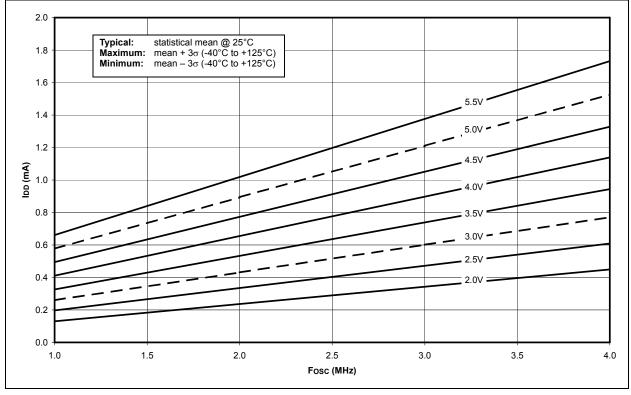

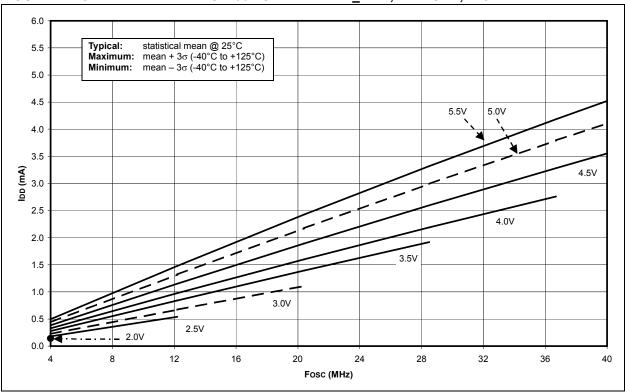

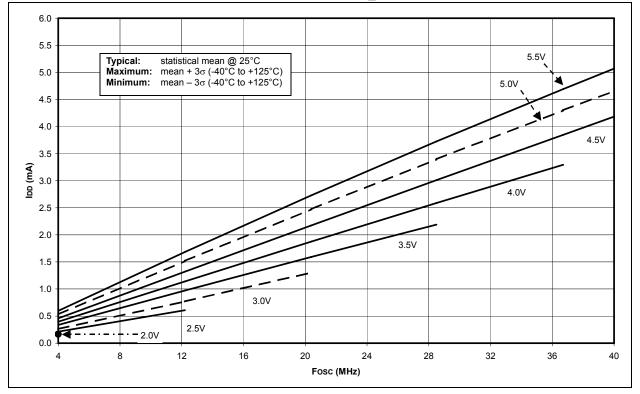

#### 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2220/2320/4220/4320 (Industrial) PIC18LF2220/2320/4220/4320 (Industrial) (Continued)

| PIC18LF2220/2320/4220/4320<br>(Industrial)<br>PIC18F2220/2320/4220/4320<br>(Industrial, Extended) |                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |    |        |                          |                                                      |  |              |

|---------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------|-----|----|--------|--------------------------|------------------------------------------------------|--|--------------|

|                                                                                                   |                                       |                                                       |     |    |        |                          |                                                      |  | Param<br>No. |

|                                                                                                   | Supply Current (IDD) <sup>(2,3)</sup> |                                                       |     |    |        |                          |                                                      |  |              |