#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2220-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| R/W-0             | R/W-0                                           | U-0                                         | R/W-0          | R/W-0             | R/W-0           | R/W-0             | R/W-0    |  |  |

|-------------------|-------------------------------------------------|---------------------------------------------|----------------|-------------------|-----------------|-------------------|----------|--|--|

| OSCFIF            | CMIF                                            | —                                           | EEIF           | BCLIF             | LVDIF           | TMR3IF            | CCP2IF   |  |  |

| bit 7             |                                                 |                                             |                |                   |                 |                   | bit (    |  |  |

|                   |                                                 |                                             |                |                   |                 |                   |          |  |  |

| Legend:           |                                                 |                                             |                |                   |                 |                   |          |  |  |

| R = Readable      |                                                 | W = Writable I                              | oit            | •                 | mented bit, rea |                   |          |  |  |

| -n = Value at POR |                                                 | '1' = Bit is set                            |                | '0' = Bit is cle  | ared            | x = Bit is unkr   | nown     |  |  |

| hit 7             |                                                 | illatar Fail Intar                          | runt Elea hit  |                   |                 |                   |          |  |  |

| bit 7             |                                                 | illator Fail Inter                          |                | as changed to     |                 | t be cleared in s | offwara) |  |  |

|                   |                                                 | lock operating                              | CIOCK INPUL II | as changed to     | INTOSC (IIIus   | t be cleared in s | ollwale) |  |  |

| bit 6             | •                                               | arator Interrupt                            | Flag bit       |                   |                 |                   |          |  |  |

|                   | •                                               | Itor input has cl                           | •              | t be cleared in   | software)       |                   |          |  |  |

|                   | 0 = Compara                                     | tor input has no                            | ot changed     |                   |                 |                   |          |  |  |

| bit 5             | Unimplemen                                      | ted: Read as '                              | )'             |                   |                 |                   |          |  |  |

| bit 4             | EEIF: Data El                                   | EPROM/Flash                                 | Write Operati  | ion Interrupt Fla | ag bit          |                   |          |  |  |

|                   |                                                 | operation is co                             |                |                   | ,               |                   |          |  |  |

| <b>h</b> # 0      |                                                 | operation is no                             | •              | r nas not been    | started         |                   |          |  |  |

| bit 3             |                                                 | Collision Interru                           | •              | o cloared in set  | ftwara)         |                   |          |  |  |

|                   |                                                 | ollision occurre                            |                |                   | lwale)          |                   |          |  |  |

| bit 2             | LVDIF: Low-V                                    | /DIF: Low-Voltage Detect Interrupt Flag bit |                |                   |                 |                   |          |  |  |

|                   |                                                 | tage condition                              |                |                   |                 |                   |          |  |  |

|                   |                                                 | ce voltage is ab                            |                | •                 | t trip point    |                   |          |  |  |

| bit 1             |                                                 | R3 Overflow Int                             |                |                   |                 |                   |          |  |  |

|                   |                                                 | gister overflowe<br>gister did not ov       |                | leared in softw   | are)            |                   |          |  |  |

| bit 0             |                                                 | 2 Interrupt Flag                            |                |                   |                 |                   |          |  |  |

|                   | Capture mode                                    |                                             | <b>,</b>       |                   |                 |                   |          |  |  |

|                   | 1 = A TMR1                                      | or TMR3 regist                              |                |                   | e cleared in sc | oftware)          |          |  |  |

|                   |                                                 | l or TMR3 regis                             | ster capture c | occurred          |                 |                   |          |  |  |

|                   | $\frac{\text{Compare mod}}{1 - A \text{ TMP1}}$ |                                             | or compore n   | notob occurrod    | (must be also   | red in software)  |          |  |  |

|                   |                                                 | or TMR3 regist                              |                |                   |                 | eu in soltware)   |          |  |  |

|                   | PWM mode:                                       | Ŭ                                           | ·              |                   |                 |                   |          |  |  |

|                   | Unused in this                                  | s mode.                                     |                |                   |                 |                   |          |  |  |

### REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| Name          | Bit#  | Buffer                                | Function                                                                                                                                                                                |

|---------------|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/AN12/INT0 | bit 0 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 0.<br>Internal software programmable weak pull-up.                                                                           |

| RB1/AN10/INT1 | bit 1 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 1.<br>Internal software programmable weak pull-up.                                                                           |

| RB2/AN8/INT2  | bit 2 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 2.<br>Internal software programmable weak pull-up.                                                                           |

| RB3/AN9/CCP2  | bit 3 | TTL <sup>(1)</sup> /ST <sup>(3)</sup> | Input/output pin or analog input. Capture 2 input/Compare 2 output/<br>PWM output when CCP2MX Configuration bit is set <sup>(4)</sup> .<br>Internal software programmable weak pull-up. |

| RB4/AN11/KBI0 | bit 4 | TTL                                   | Input/output pin (with interrupt-on-change) or analog input.<br>Internal software programmable weak pull-up.                                                                            |

| RB5/KBI1/PGM  | bit 5 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Low-voltage ICSP™ enable pin.                                                                 |

| RB6/KBI2/PGC  | bit 6 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                                                     |

| RB7/KBI3/PGD  | bit 7 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                                                      |

### TABLE 10-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a TTL input when configured as digital I/O.

- 2: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 3: This buffer is a Schmitt Trigger input when configured as the CCP2 input.

- 4: A device Configuration bit selects which I/O pin the CCP2 pin is multiplexed on.

- **5:** This buffer is a Schmitt Trigger input when used in Serial Programming mode.

| Name    | Bit 7                         | Bit 6        | Bit 5    | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------|--------------|----------|---------|--------|--------|--------|--------|----------------------|---------------------------------|

| PORTB   | RB7                           | RB6          | RB5      | RB4     | RB3    | RB2    | RB1    | RB0    | XXXX XXXX            | uuuu uuuu                       |

| LATB    | LATB LATB Data Latch Register |              |          |         |        |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| TRISB   | PORTB Da                      | ta Direction | Register |         |        |        |        |        | 1111 1111            | 1111 1111                       |

| INTCON  | GIE/GIEH                      | PEIE/GIEL    | TMR0IE   | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| INTCON2 | RBPU                          | INTEDG0      | INTEDG1  | INTEDG2 | _      | TMR0IP | _      | RBIP   | 1111 -1-1            | 1111 -1-1                       |

| INTCON3 | INT2IP                        | INT1IP       | _        | INT2IE  | INT1IE | —      | INT2IF | INT1IF | 11-0 0-00            | 11-0 0-00                       |

| ADCON1  | —                             | —            | VCFG1    | VCFG0   | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 00 0000              | 00 0000                         |

TABLE 10-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, — = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

### 14.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a lowpower oscillator rated for 32 kHz crystals. See **Section 12.2 "Timer1 Oscillator"** for further details.

### 14.3 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 Interrupt Enable bit, TMR3IE (PIE2<1>).

### 14.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "Special Event Trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3. See **Section 15.4.4 "Special Event Trigger"** for more information.

**Note:** The Special Event Triggers from the CCP module will not set interrupt flag bit, TMR3IF (PIR1<0>).

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this Reset operation may not work. In the event that a write to Timer3 coincides with a Special Event Trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer3.

| Name   | Bit 7        | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|--------------|---------------|---------|---------|---------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR2   | OSCIF        | CMIF          | _       | EEIF    | BCLIF   | LVDIF  | TMR3IF | CCP2IF | 00-0 0000            | 00-0 0000                       |

| PIE2   | OSCIE        | CMIE          | _       | EEIE    | BCLIE   | LVDIE  | TMR3IE | CCP2IE | 00-0 0000            | 00-0 0000                       |

| IPR2   | OSCIP        | CMIP          | —       | EEIP    | BCLIP   | LVDIP  | TMR3IP | CCP2IP | 11-1 1111            | 11-1 1111                       |

| TMR3L  | Timer3 Lo    | ow Byte Reg   | gister  |         |         |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| TMR3H  | Timer3 Hi    | igh Byte Re   | gister  |         |         |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| T1CON  | RD16         | T1RUN         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 0000 0000            | u0uu uuuu                       |

| T3CON  | RD16         | T3CCP2        | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 0000 0000            | uuuu uuuu                       |

TABLE 14-1:

REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

| Name    | Bit 7      | Bit 6          | Bit 5      | Bit 4         | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, E | -    |      | e on<br>other<br>sets |

|---------|------------|----------------|------------|---------------|----------|--------|---------|---------|-----------------|------|------|-----------------------|

| INTCON  | GIE/GIEH   | PEIE/GIEL      | TMR0IE     | INT0IE        | RBIE     | TMR0IF | INT0IF  | RBIF    | 0000 0          | 000x | 0000 | 000u                  |

| RCON    | IPEN       | —              | _          | RI            | TO       | PD     | POR     | BOR     | 01 1            | L1q0 | 0q   | qquu                  |

| PIR1    | PSPIF      | ADIF           | RCIF       | TXIF          | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 0000 0          | 0000 | 0000 | 0000                  |

| PIE1    | PSPIE      | ADIE           | RCIE       | TXIE          | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 0000 0          | 0000 | 0000 | 0000                  |

| IPR1    | PSPIP      | ADIP           | RCIP       | TXIP          | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 1111 1          | 1111 | 1111 | 1111                  |

| TMR2    | Timer2 Mod | dule Register  |            |               |          |        |         |         | 0000 0          | 0000 | 0000 | 0000                  |

| PR2     | Timer2 Mod | dule Period R  | egister    |               |          |        |         |         | 1111 1          | 1111 | 1111 | 1111                  |

| T2CON   | —          | TOUTPS3        | TOUTPS2    | TOUTPS1       | TOUTPS0  | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0          | 0000 | -000 | 0000                  |

| TRISC   | PORTC Da   | ta Direction F | Register   |               |          |        |         |         | 1111 1          | 1111 | 1111 | 1111                  |

| TRISD   | PORTD Da   | ta Direction F | Register   |               |          |        |         |         | 1111 1          | 1111 | 1111 | 1111                  |

| CCPR1H  | Enhanced ( | Capture/Com    | pare/PWM F | Register 1 H  | igh Byte |        |         |         | XXXX X          | xxx  | uuuu | uuuu                  |

| CCPR1L  | Enhanced ( | Capture/Com    | pare/PWM F | Register 1 Lo | ow Byte  |        |         |         | XXXX X          | xxx  | uuuu | uuuu                  |

| CCP1CON | P1M1       | P1M0           | DC1B1      | DC1B0         | CCP1M3   | CCP1M2 | CCP1M1  | CCP1M0  | 0000 0          | 0000 | 0000 | 0000                  |

| ECCPAS  | ECCPASE    | ECCPAS2        | ECCPAS1    | ECCPAS0       | PSSAC1   | PSSAC0 | PSSBD1  | PSSBD0  | 0000 0          | 0000 | 0000 | 0000                  |

| PWM1CON | PRSEN      | PDC6           | PDC5       | PDC4          | PDC3     | PDC2   | PDC1    | PDC0    | 0000 0          | 0000 | 0000 | 0000                  |

| OSCCON  | IDLEN      | IRCF2          | IRCF1      | IRCF0         | OSTS     | IOFS   | SCS1    | SCS0    | 0000 q          | 1000 | 0000 | q000                  |

| TABLE 16-2: | REGISTERS ASSOCIATED WITH ENHANCED PWM AND TIMER2 |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the ECCP module in enhanced PWM mode.

### REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

| R/W-0      | R/W-0                                                        | R/W-0                                                      | R/W-0                                                     | R/W-0                                                                                    | R/W-0                      | R/W-0                | R/W-0                |

|------------|--------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------|----------------------|----------------------|

| WCOL       | SSPOV <sup>(1)</sup>                                         | SSPEN <sup>(2)</sup>                                       | CKP                                                       | SSPM3 <sup>(3)</sup>                                                                     | SSPM2 <sup>(3)</sup>       | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7      |                                                              |                                                            |                                                           | ·                                                                                        |                            |                      | bit (                |

|            |                                                              |                                                            |                                                           |                                                                                          |                            |                      |                      |

| Legend:    |                                                              |                                                            |                                                           |                                                                                          |                            |                      |                      |

| R = Reada  | ble bit                                                      | W = Writable                                               | bit                                                       | U = Unimpler                                                                             | nented bit, read           | 1 as '0'             |                      |

| -n = Value | at POR                                                       | '1' = Bit is set                                           |                                                           | '0' = Bit is cle                                                                         | ared                       | x = Bit is unkr      | nown                 |

| bit 7      |                                                              | )                                                          | -                                                         | nit mode only)<br>e it is still transn                                                   | nitting the previ          | ous word (mus        | t be cleared ir      |

| bit 6      |                                                              | eive Overflow I                                            | ndicator hit(1                                            | )                                                                                        |                            |                      |                      |

| bit 5      | flow, the<br>SSPBUF<br>0 = No overf                          | /te is received w<br>data in SSPSR<br>; even if only tra   | t is lost. Over<br>ansmitting da                          | BUF register is s<br>flow can only o<br>ta, to avoid settii<br>Enable bit <sup>(2)</sup> | ccur in Slave m            | node. The user       | must read the        |

|            |                                                              |                                                            |                                                           | CK, SDO, SDI a<br>lese pins as I/O                                                       |                            | l port pins          |                      |

| bit 4      | 1 = Idle state                                               | Polarity Select b<br>for clock is a h<br>for clock is a lo | igh level                                                 |                                                                                          |                            |                      |                      |

| bit 3-0    | SSPM3:SSP                                                    | M0: Master Syr                                             | nchronous Se                                              | erial Port Mode                                                                          | Select bits <sup>(3)</sup> |                      |                      |

|            | 0100 = SPI S<br>0011 = SPI N<br>0010 = SPI N<br>0001 = SPI N |                                                            | ck = SCK pir<br>ock = TMR2<br>ock = Fosc/6<br>ock = Fosc/ | 64<br>16                                                                                 |                            | can be used as       | I/O pin              |

|            | In Master mode, th<br>writing to the SSP                     |                                                            | s not set sind                                            | ce each new rec                                                                          | ception (and tra           | nsmission) is ir     | itiated by           |

| •          | M/h +h - MOOD -                                              |                                                            |                                                           |                                                                                          |                            |                      |                      |

- 2: When the MSSP is enabled in SPI mode, these pins must be properly configured as input or output.

- 3: Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C<sup>™</sup> mode only.

### 17.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

The MSSP consists of a Transmit/Receive Shift register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then the Buffer Full Detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

### EXAMPLE 17-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been received(transmit complete)? |

|------|-------|-------------|---------------------------------------------|

|      | BRA   | LOOP        | ;No                                         |

|      | MOVF  | SSPBUF, W   | ;WREG reg = contents of SSPBUF              |

|      | MOVWF | RXDATA      | ;Save in user RAM, if data is meaningful    |

|      | MOVF  | TXDATA, W   | ;W reg = contents of TXDATA                 |

|      | MOVWF | SSPBUF      | ;New data to xmit                           |

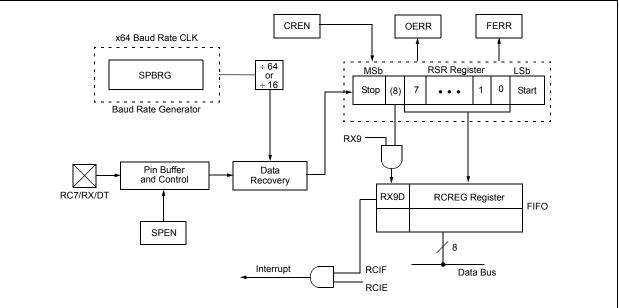

#### 18.3.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 18-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 18.2 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, RCIE.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. Enable the reception by setting bit, CREN.

- 6. Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## 18.3.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with address detect enable:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is required, set the BRGH bit.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

### FIGURE 18-4: USART RECEIVE BLOCK DIAGRAM

### 20.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs and outputs for the comparators are multiplexed with the RA0 through RA5 pins. The onchip voltage reference (Section 21.0 "Comparator Voltage Reference Module") can also be an input to the comparators.

The CMCON register, shown as Register 20-1, controls the comparator module's input and output multiplexers. A block diagram of the various comparator configurations is shown in Figure 20-1.

### 20.1 Comparator Configuration

There are eight modes of operation for the comparators. The CM bits (CMCON<2:0>) are used to select these modes. Figure 20-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in the Electrical Specifications (see **Section 26.0 "Electrical Characteristics"**).

**Note:** Comparator interrupts should be disabled during a Comparator mode change. Otherwise, a false interrupt may occur.

### REGISTER 20-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0               | R-0                                                | R/W-0                                     | R/W-0          | R/W-0            | R/W-1           | R/W-1           | R/W-1 |  |

|-------------------|----------------------------------------------------|-------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|

| C2OUT             | C1OUT                                              | C2INV                                     | C1INV          | CIS              | CM2             | CM1             | CM0   |  |

|                   | 01001                                              | GZINV                                     | CHINV          | 015              | CIVIZ           | CIMIT           |       |  |

| bit 7             |                                                    |                                           |                |                  |                 |                 | bit 0 |  |

|                   |                                                    |                                           |                |                  |                 |                 |       |  |

| Legend:           |                                                    |                                           | ,              |                  |                 |                 |       |  |

| R = Readabl       |                                                    | W = Writable                              |                | -                | nented bit, rea |                 |       |  |

| -n = Value at POR |                                                    | '1' = Bit is set                          |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |

|                   |                                                    |                                           |                |                  |                 |                 |       |  |

| bit 7             |                                                    | parator 2 Outpu                           | ut bit         |                  |                 |                 |       |  |

|                   | When C2INV                                         |                                           |                |                  |                 |                 |       |  |

|                   | 1 = C2 VIN+ ><br>0 = C2 VIN+ <                     |                                           |                |                  |                 |                 |       |  |

|                   |                                                    |                                           |                |                  |                 |                 |       |  |

|                   |                                                    | <u>en C2INV = 1:</u><br>C2 VIN+ < C2 VIN- |                |                  |                 |                 |       |  |

|                   | 0 = C2 VIN+ >                                      |                                           |                |                  |                 |                 |       |  |

| bit 6             | C1OUT: Com                                         | parator 1 Outpu                           | ut bit         |                  |                 |                 |       |  |

|                   | When C1INV                                         | • •                                       |                |                  |                 |                 |       |  |

|                   | 1 = C1 VIN+ >                                      |                                           |                |                  |                 |                 |       |  |

|                   | 0 = C1 VIN+ <                                      | < C1 VIN-                                 |                |                  |                 |                 |       |  |

|                   | When C1INV                                         |                                           |                |                  |                 |                 |       |  |

|                   | 1 = C1 VIN+ <                                      |                                           |                |                  |                 |                 |       |  |

|                   | 0 = C1 VIN+ >                                      |                                           |                |                  |                 |                 |       |  |

| bit 5             |                                                    | parator 2 Outpu                           | t Inversion bi | t                |                 |                 |       |  |

|                   | 1 = C2 outpu<br>0 = C2 outpu                       |                                           |                |                  |                 |                 |       |  |

|                   | •                                                  |                                           |                |                  |                 |                 |       |  |

| bit 4             |                                                    | parator 1 Outpu                           | t inversion di | t                |                 |                 |       |  |

|                   | 1 = C1 outpu<br>0 = C1 outpu                       |                                           |                |                  |                 |                 |       |  |

| hit 2             | -                                                  |                                           | h hit          |                  |                 |                 |       |  |

| bit 3             | -                                                  | ator Input Switc                          | In Dit         |                  |                 |                 |       |  |

|                   | $\frac{\text{When CM2:C}}{1 = C1 \text{ Visited}}$ | $\frac{1}{100} = 110$                     | 3/4N3          |                  |                 |                 |       |  |

|                   |                                                    | connects to RA                            |                |                  |                 |                 |       |  |

|                   |                                                    | connects to RA                            |                |                  |                 |                 |       |  |

|                   | C2 VIN- 0                                          | connects to RA                            | 1/AN1          |                  |                 |                 |       |  |

| bit 2-0           | CM2:CM0: C                                         | omparator Mod                             | e bits         |                  |                 |                 |       |  |

|                   | Figure 20-1 s                                      |                                           |                |                  |                 |                 |       |  |

NOTES:

| BNC         | v                                                      | Branch if                                                                        | Not Ove                                                                                                                                                                                                                                                                                    | erflow        |                 | BNZ          |  |  |

|-------------|--------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|--------------|--|--|

| Synt        | ax:                                                    | [ <i>label</i> ] B                                                               | NOV n                                                                                                                                                                                                                                                                                      |               |                 | Synt         |  |  |

| Oper        | rands:                                                 | -128 ≤ n ≤                                                                       | 127                                                                                                                                                                                                                                                                                        |               |                 | Ope          |  |  |

| Oper        | ration:                                                |                                                                                  | if Overflow bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                  |               |                 |              |  |  |

| Statu       | us Affected:                                           | None                                                                             |                                                                                                                                                                                                                                                                                            |               |                 | State        |  |  |

| Enco        | oding:                                                 | 1110                                                                             | 0101                                                                                                                                                                                                                                                                                       | nnnn          | nnnn            | Enco         |  |  |

| Desc        | cription:                                              | program v<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC + 2 + 2 | If the Overflow bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is<br>then a two-cycle instruction. |               |                 |              |  |  |

| Word        | ds:                                                    | 1                                                                                | -                                                                                                                                                                                                                                                                                          |               |                 | Wor          |  |  |

| Cycl        | es:                                                    | 1(2)                                                                             |                                                                                                                                                                                                                                                                                            |               |                 | Cycl         |  |  |

|             | ycle Activity:<br>imp:                                 |                                                                                  |                                                                                                                                                                                                                                                                                            |               |                 | Q C<br>If Ju |  |  |

|             | Q1                                                     | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                         |               | Q4              | _            |  |  |

|             | Decode                                                 | Read literal<br>'n'                                                              | Proces<br>Data                                                                                                                                                                                                                                                                             | s V           | /rite to PC     |              |  |  |

|             | No                                                     | No                                                                               | No                                                                                                                                                                                                                                                                                         |               | No              |              |  |  |

|             | operation                                              | operation                                                                        | operatio                                                                                                                                                                                                                                                                                   | on (          | operation       | ]            |  |  |

| If No       | o Jump:                                                | ~~                                                                               |                                                                                                                                                                                                                                                                                            |               | ~ ~             | lf N         |  |  |

|             | Q1                                                     | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                         | -             | Q4              | 1            |  |  |

|             | Decode                                                 | Read literal<br>'n'                                                              | Proces<br>Data                                                                                                                                                                                                                                                                             | -             | No<br>operation |              |  |  |

| <u>Exar</u> | <u>nple</u> :<br>Before Instru<br>PC                   |                                                                                  | BNOV J<br>dress (Hi                                                                                                                                                                                                                                                                        | ump<br>ERE)   |                 | Exar         |  |  |

|             | After Instruct<br>If Overflo<br>PC<br>If Overflo<br>PC | w = 0;<br>= ad<br>w = 1;                                                         |                                                                                                                                                                                                                                                                                            | ump)<br>ERE + | 2)              |              |  |  |

| Syntax:                       | [lahel] B                                                                        | [ <i>label</i> ] BNZ n                                                                                                            |                                                                             |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| -                             | -128 < n <                                                                       |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Operands:                     |                                                                                  |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Operation:                    |                                                                                  | if Zero bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                             |                                                                             |  |  |  |  |  |

| Status Affected:              | None                                                                             |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Encoding:                     | 1110                                                                             | 0001 nnr                                                                                                                          | nn nnnn                                                                     |  |  |  |  |  |

| Description:                  | program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC + 2 + 2 | bit is '0', the<br>vill branch.<br>mplement nu<br>he PC. Since<br>mented to fe<br>, the new ad<br>2n. This instr<br>-cycle instru | umber '2n' is<br>the PC will<br>etch the next<br>dress will be<br>uction is |  |  |  |  |  |

| Words:                        | 1                                                                                |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Cycles:                       | 1(2)                                                                             | 1(2)                                                                                                                              |                                                                             |  |  |  |  |  |

| Q Cycle Activity:<br>If Jump: |                                                                                  |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Q1                            | Q2                                                                               | Q3                                                                                                                                | Q4                                                                          |  |  |  |  |  |

| Decode                        | Read literal<br>'n'                                                              | Process<br>Data                                                                                                                   | Write to PC                                                                 |  |  |  |  |  |

| No                            | No                                                                               | No                                                                                                                                | No                                                                          |  |  |  |  |  |

| operation                     | operation                                                                        | operation                                                                                                                         | operation                                                                   |  |  |  |  |  |

| If No Jump:                   |                                                                                  |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Q1                            | Q2                                                                               | Q3                                                                                                                                | Q4                                                                          |  |  |  |  |  |

| Decode                        | Read literal<br>'n'                                                              | Process<br>Data                                                                                                                   | No<br>operation                                                             |  |  |  |  |  |

|                               |                                                                                  |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Example:                      | HERE                                                                             | BNZ Jump                                                                                                                          |                                                                             |  |  |  |  |  |

| Example:<br>Before Instru     |                                                                                  | BNZ Jump                                                                                                                          |                                                                             |  |  |  |  |  |

| _      | address (HERE)           |

|--------|--------------------------|

|        |                          |

| =      | 0;<br>address (Jump)     |

| =<br>= | 1;<br>address (HERE + 2) |

|        | =<br>=<br>=<br>=         |

| DAW               | Decimal A         | Adjust W Re                           | gister      | DECF         |                    | D          |

|-------------------|-------------------|---------------------------------------|-------------|--------------|--------------------|------------|

| Syntax:           | [label] [         | WAW                                   |             | Syntax       | :                  | [ /        |

| Operands:         | None              |                                       |             | Operan       | ıds:               | 0          |

| Operation:        | -                 | >9] or [DC =                          | -           |              |                    | d          |

|                   | • • •             | $+ 6 \rightarrow W < 3:0$             | )>;         | Operati      | ion:               | a<br>/f    |

|                   | else,<br>(W<3:0>) | → W<3:0>;                             |             | Operati      | Affected:          | (f         |

|                   |                   |                                       |             |              |                    | C<br>L     |

|                   |                   | >9] or [C = $+ 6 \rightarrow W < 7$ : |             | Encodi       | -                  | L          |

|                   | else,             | $+ 0 \rightarrow VV \land I$          | 4~,         | Descrip      | Duon:              | D<br>th    |

|                   | (W<7:4>)          | → W<7:4>                              |             |              |                    | th         |

| Status Affected:  | C, DC             |                                       |             | _            |                    | ʻf<br>B    |

| Encoding:         | 0000              | 0000 000                              | 00 0111     |              |                    | th         |

| Description:      |                   | sts the eight-                        |             | -            |                    | b          |

|                   |                   | ng from the e<br>variables (e         |             |              |                    | В          |

|                   |                   |                                       | nd produces | Words:       |                    | 1          |

|                   | a correct p       | acked BCD                             | result. The | Cycles:      |                    | 1          |

|                   |                   | ay be set by setting prior            | DAW regard  | Q Cyc        | le Activity:       |            |

|                   | execution.        |                                       |             |              | Q1<br>Decode       |            |

| Words:            | 1                 |                                       |             |              | Decoue             | reg        |

| Cycles:           | 1                 |                                       |             |              |                    |            |

| Q Cycle Activity: | :                 |                                       |             | <u>Examp</u> |                    | D          |

| Q1                | Q2                | Q3                                    | Q4          | Be           | fore Instru<br>CNT | uctio<br>= |

| Decode            | Read              | Process                               | Write<br>W  |              | Z                  | =          |

|                   | register W        | Data                                  | ٧V          | Aft Aft      | ter Instruct       |            |

| Example1:         | DAW               |                                       |             |              | CNT<br>Z           | =          |

| Before Instru     | uction            |                                       |             |              |                    |            |

| W<br>C            | = 0xA5<br>= 0     |                                       |             |              |                    |            |

| DC                | = 0               |                                       |             |              |                    |            |

| After Instruct    |                   |                                       |             |              |                    |            |

| W<br>C            | = 0x05<br>= 1     |                                       |             |              |                    |            |

| DC                | = 0               |                                       |             |              |                    |            |

| Example 2:        |                   |                                       |             |              |                    |            |

| Before Instru     | uction            |                                       |             |              |                    |            |

| W<br>C            | = 0xCE<br>= 0     |                                       |             |              |                    |            |

| DC                | = 0<br>= 0        |                                       |             |              |                    |            |

| After Instruct    | tion              |                                       |             |              |                    |            |

| W<br>C            | = 0x34<br>= 1     |                                       |             |              |                    |            |

| DC                | = 0               |                                       |             |              |                    |            |

| DEC   | F              | Decremer                                                                                                                                                                                                                                                                                                         | Decrement f     |                      |  |  |  |  |

|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--|--|--|--|

| Synt  | ax:            | [ <i>label</i> ] [                                                                                                                                                                                                                                                                                               | DECF f[,d[,     | a]]                  |  |  |  |  |

| Оре   | rands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                              | 5               |                      |  |  |  |  |

| Ope   | ration:        | $(f) - 1 \rightarrow c$                                                                                                                                                                                                                                                                                          | lest            |                      |  |  |  |  |

| Statu | us Affected:   | C, DC, N,                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z |                      |  |  |  |  |

| Enco  | oding:         | 0000                                                                                                                                                                                                                                                                                                             | 01da ffi        | ff ffff              |  |  |  |  |

| Des   | cription:      | Decrement register 'f'. If 'd' is '0',<br>the result is stored in W. If 'd' is '1',<br>the result is stored back in register<br>'f' (default). If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the<br>bank will be selected as per the<br>BSR value (default). |                 |                      |  |  |  |  |

| Wor   | ds:            | 1                                                                                                                                                                                                                                                                                                                |                 |                      |  |  |  |  |

| Cycl  | es:            | 1                                                                                                                                                                                                                                                                                                                |                 |                      |  |  |  |  |

| QC    | ycle Activity: |                                                                                                                                                                                                                                                                                                                  |                 |                      |  |  |  |  |

|       | Q1             | Q2                                                                                                                                                                                                                                                                                                               | Q3              | Q4                   |  |  |  |  |

|       | Decode         | Read<br>register 'f'                                                                                                                                                                                                                                                                                             | Process<br>Data | Write to destination |  |  |  |  |

DECF CNT,

| •             |       |      |

|---------------|-------|------|

| Before Instru | uctio | n    |

| CNT           | =     | 0x01 |

| Z             | =     | 0    |

| After Instruc | tion  |      |

| CNT           | =     | 0x00 |

| Z             | =     | 1    |

| DEC         | FSZ                                                  | Decreme                                                                                                                                                                                                                                                                                                                                                                                                                                             | nt f, Skip if (                 | )                      |  |  |  |

|-------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|--|--|--|

| Synt        | ax:                                                  | [label] [                                                                                                                                                                                                                                                                                                                                                                                                                                           | DECFSZ f[,                      | d [,a]]                |  |  |  |

| Ope         | rands:                                               | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |                        |  |  |  |

| Ope         | ration:                                              | (f) – 1 $\rightarrow$ oskip if res                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |                        |  |  |  |

| Statu       | us Affected:                                         | None                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |                        |  |  |  |

| Enco        | oding:                                               | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11da ffi                        | ff ffff                |  |  |  |

| Desc        | cription:                                            | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result<br>is placed back in register 'f'<br>(default).<br>If the result is '0', the next instruc-<br>tion which is already fetched is dis-<br>carded and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the |                                 |                        |  |  |  |

| 14/0 -      | de .                                                 | BSR value                                                                                                                                                                                                                                                                                                                                                                                                                                           | be selected a<br>e (default).   | is per the             |  |  |  |

| Word        |                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |                        |  |  |  |

| Cycl<br>Q C | cs.<br>Cycle Activity                                | by                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ycles if skip a 2-word ins      | and followed truction. |  |  |  |

|             | Q1                                                   | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q3                              | Q4                     |  |  |  |

|             | Decode                                               | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                | Process<br>Data                 | Write to destination   |  |  |  |