Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-1-11-                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2320-e-sp |

#### 2.6.3 OSCTUN2 REGISTER

The internal oscillator block is calibrated at the factory to produce an INTRC output frequency of approximately 31 kHz. (See parameters F20 and F21 in Table 26-8.)

The INTRC frequency can be adjusted two ways:

- If TUNSEL (OSCTUN2<7>) is clear -TUN5:TUN1 in OSCTUNE<5:1> adjusts the INTRC clock frequency and also can adjust the INTOSC clock frequency. (See Register 2-1, OSCTUNE.)

- If TUNSEL (OSCTUN2<7>) is set TUN5:TUN1 in OSCTUN2<5:1> adjusts the INTRC clock frequency without affecting the INTOSC frequency. (See Register 2-2, OSCTUN2.)

In OSCTUN2, the OSCTUN2<0> bit has no effect, but is readable and writable, enabling changes of the INTRC frequency using two increment or decrement instructions.

When the OSCTUN2 register is modified, the INTRC frequency will begin shifting to the new frequency, and will stabilize at the new frequency within 100 µs. Code execution continues during this shift.

There is no indication when the shift occurs. Operation of features that depend on the INTRC clock source frequency also will be affected by the change in frequency. This includes the WDT, Fail-Safe Clock Monitor and peripherals.

#### REGISTER 2-2: OSCTUN2: INTRC OSCILLATOR TUNING REGISTER

| R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| TUNSEL | _   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7  |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

TUNSEL: Enables tuning of INTRC using OCSTUN2<5:1> bit 7

1 = INTRC adjusted by OSCTUN2<5:1>

0 = INTRC adjusted by OSCTUNE<5:1>

bit 6 Unimplemented: Read as '0'

bit 5-1 TUN<5:1>: Frequency Tuning bits – Adjusts the frequency of INTRC when TUNSEL is set

011111 = Maximum frequency

000001

000000 = Center frequency. Oscillator module is running at the calibrated frequency.

111111

100000 = Minimum frequency

bit 0 TUN<0>: A placeholder with no effect on the INTRC frequency. Provided to facilitate incrementation

and decrementation of the OSCTUN2 register and adjustment of the INTRC frequency.

### REGISTER 2-3: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R <sup>(1)</sup> | R-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------------|------|-------|-------|

| IDLEN | IRCF2 | IRCF1 | IRCF0 | OSTS             | IOFS | SCS1  | SCS0  |

| bit 7 |       |       |       |                  |      |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 IDLEN: Idle Enable bit

1 = Idle mode enabled; CPU core is not clocked in power-managed modes

0 = Run mode enabled; CPU core is clocked in power-managed modes

bit 6-4 IRCF2:IRCF0: Internal Oscillator Frequency Select bits

111 = 8 MHz (8 MHz source drives clock directly)

110 **= 4 MHz**

101 **= 2 MHz**

100 **= 1 MHz**

011 **= 500 kHz**

010 = 250 kHz 001 = 125 kHz

000 = 31 kHz (INTRC source drives clock directly)

bit 3 OSTS: Oscillator Start-up Time-out Status bit<sup>(1)</sup>

1 = Oscillator Start-up Timer time-out has expired; primary oscillator is running

0 = Oscillator Start-up Timer time-out is running; primary oscillator is not ready

bit 2 **IOFS:** INTOSC Frequency Stable bit

1 = INTOSC frequency is stable

0 = INTOSC frequency is not stable

bit 1-0 SCS1:SCS0: System Clock Select bits

1x = Internal oscillator block (RC modes)

01 = Timer1 oscillator (Secondary modes)(2)

00 = Primary oscillator (Sleep and PRI\_IDLE modes)

Note 1: Depends on state of IESO bit in Configuration Register 1H.

2: SCS0 may not be set while T1OSCEN (T1CON<3>) is clear.

#### 3.6.1 EXAMPLE – USART

An adjustment may be indicated when the USART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the system clock frequency is too high – try decrementing the value in the OSCTUNE register to reduce the system clock frequency. Errors in data may suggest that the system clock speed is too low – increment OSCTUNE.

### 3.6.2 EXAMPLE - TIMERS

This technique compares system clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast – decrement OSCTUNE.

# 3.6.3 EXAMPLE – CCP IN CAPTURE MODE

A CCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast – decrement OSCTUNE. If the measured time is much less than the calculated time, the internal oscillator block is running too slow – increment OSCTUNE.

TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2220/2320/4220/4320) (CONTINUED)

| File Name            | Bit 7                 | Bit 6                                                | Bit 5          | Bit 4                | Bit 3         | Bit 2        | Bit 1        | Bit 0  | Value on POR, BOR | Details on page: |  |

|----------------------|-----------------------|------------------------------------------------------|----------------|----------------------|---------------|--------------|--------------|--------|-------------------|------------------|--|

| EEADR                | EEPROM AC             | Idress Registe                                       | er             |                      |               |              |              |        | 0000 0000         | 48, 81           |  |

| EEDATA               | EEPROM Da             | ata Register                                         |                |                      |               |              |              |        | 0000 0000         | 48, 84           |  |

| EECON2               | EEPROM Co             | ontrol Register                                      | 2 (not a phys  | sical register)      |               |              |              |        | 0000 0000         | 48, 72, 81       |  |

| EECON1               | EEPGD                 | CFGS                                                 | _              | FREE                 | WRERR         | WREN         | WR           | RD     | xx-0 x000         | 48, 73, 82       |  |

| IPR2                 | OSCFIP                | CMIP                                                 | _              | EEIP                 | BCLIP         | LVDIP        | TMR3IP       | CCP2IP | 11-1 1111         | 49, 97           |  |

| PIR2                 | OSCFIF                | CMIF                                                 | _              | EEIF                 | BCLIF         | LVDIF        | TMR3IF       | CCP2IF | 00-0 0000         | 49, 93           |  |

| PIE2                 | OSCFIE                | CMIE                                                 | _              | EEIE                 | BCLIE         | LVDIE        | TMR3IE       | CCP2IE | 00-0 0000         | 49, 95           |  |

| IPR1                 | PSPIP <sup>(5)</sup>  | ADIP                                                 | RCIP           | TXIP                 | SSPIP         | CCP1IP       | TMR2IP       | TMR1IP | 1111 1111         | 49, 96           |  |

| PIR1                 | PSPIF <sup>(5)</sup>  | ADIF                                                 | RCIF           | TXIF                 | SSPIF         | CCP1IF       | TMR2IF       | TMR1IF | 0000 0000         | 49, 92           |  |

| PIE1                 | PSPIE <sup>(5)</sup>  | ADIE                                                 | RCIE           | TXIE                 | SSPIE         | CCP1IE       | TMR2IE       | TMR1IE | 0000 0000         | 49, 94           |  |

| OSCTUNE              | _                     | _                                                    | TUN5           | TUN4                 | TUN3          | TUN2         | TUN1         | TUN0   | 00 0000           | 23, 49           |  |

| TRISE <sup>(5)</sup> | IBF                   | IBF OBF IBOV PSPMODE — Data Direction bits for PORTE |                |                      |               |              |              |        |                   |                  |  |

| TRISD <sup>(5)</sup> | Data Direction        | n Control Reg                                        | gister for POR | RTD                  |               |              |              |        | 1111 1111         | 49, 110          |  |

| TRISC                | Data Direction        | n Control Rec                                        | gister for POR | RTC                  |               |              |              |        | 1111 1111         | 49, 108          |  |

| TRISB                | Data Direction        | n Control Rec                                        | gister for POR | RTB                  |               |              |              |        | 1111 1111         | 49, 106          |  |

| TRISA                | TRISA7 <sup>(2)</sup> | TRISA6 <sup>(1)</sup>                                | Data Direction | on Control Reg       | ister for POF | RTA          |              |        | 1111 1111         | 49, 103          |  |

| LATE <sup>(5)</sup>  | _                     | _                                                    | _              | _                    | _             | Read/Write F | PORTE Data L | atch   | xxx               | 49, 113          |  |

| LATD <sup>(5)</sup>  | Read/Write F          | PORTD Data I                                         | atch           |                      |               |              |              |        | xxxx xxxx         | 49, 110          |  |

| LATC                 | Read/Write F          | PORTC Data I                                         | _atch          |                      |               |              |              |        | xxxx xxxx         | 49, 108          |  |

| LATB                 | Read/Write F          | PORTB Data L                                         | _atch          |                      |               |              |              |        | xxxx xxxx         | 49, 106          |  |

| LATA                 | LATA<7>(2)            | LATA<6>(1)                                           | Read/Write I   | PORTA Data L         | atch          |              |              |        | xxxx xxxx         | 49, 103          |  |

| PORTE <sup>(5)</sup> | _                     | _                                                    | _              | _                    | qxxx          | 49, 113      |              |        |                   |                  |  |

| PORTD <sup>(5)</sup> | Read PORTI            |                                                      | xxxx xxxx      | 49, 110              |               |              |              |        |                   |                  |  |

| PORTC                | Read PORT             | C pins, Write I                                      | PORTC Data     | Latch                |               |              |              |        | xxxx xxxx         | 49, 108          |  |

| PORTB                | Read PORTI            | 3 pins, Write F                                      | PORTB Data     | Latch <sup>(4)</sup> |               |              |              |        | xxxx xxxx         | 49, 106          |  |

| PORTA                | RA7 <sup>(2)</sup>    | RA6 <sup>(1)</sup>                                   | Read PORT      | A pins, Write F      | ORTA Data I   | Latch        |              |        | xx0x 0000         | 49, 103          |  |

Legend:

x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO, ECIO and INTIO2 (with port function on RA6) Oscillator mode only and read as '0' in all other oscillator modes.

- 2: RA7 and associated bits are configured as port pins in INTIO2 Oscillator mode only and read as '0' in all other modes.

- 3: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

- 4: If PBADEN = 0, PORTB<4:0> are configured as digital inputs and read unknown and if PBADEN = 1, PORTB<4:0> are configured as analog inputs and read as '0' following a Reset.

- These registers and/or bits are not implemented on the PIC18F2X20 devices and read as 0x00.

- 6: The RE3 port bit is available as an input only pin only in 40-pin devices when Master Clear functionality is disabled (CONFIG3H<7> = 0).

### 9.0 INTERRUPTS

The PIC18F2320/4320 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 000008h and the low-priority interrupt vector is at 000018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- · PIR1, PIR2

- PIE1, PIE2

- · IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB® IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority (most interrupt sources have priority bits)

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC® mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

### 12.4 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing Timer1 interrupt enable bit, TMR1IE (PIE1<0>).

### 12.5 Resetting Timer1 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "Special Event Trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion if the A/D module is enabled (see Section 15.4.4 "Special Event Trigger" for more information).

Note: The Special Event Triggers from the CCP1 module will not set interrupt flag bit, TMR1IF (PIR1<0>).

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

### 12.6 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 high byte buffer. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

# 12.7 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 12.2 "Timer1 Oscillator"** above), gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 12-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine, which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the MSbit of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1) as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

#### 17.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### REGISTER 17-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/A | Р   | S   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:           |                                                                      |                      |                    |  |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

bit 7 **SMP:** Sample bit

SPI Master mode:

1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

SPI Slave mode:

SMP must be cleared when SPI is used in Slave mode.

bit 6 **CKE:** SPI Clock Edge Select bit

When CKP = 0:

1 = Data transmitted on rising edge of SCK

$\circ$  = Data transmitted on falling edge of SCK

When CKP = 1:

1 = Data transmitted on falling edge of SCK

0 = Data transmitted on rising edge of SCK

bit 5 **D/A**: Data/Address bit

Used in I<sup>2</sup>C mode only.

bit 4 P: Stop bit

Used in I<sup>2</sup>C mode only.

bit 3 S: Start bit

Used in I<sup>2</sup>C mode only.

bit 2 **R/W**: Read/Write Information bit

Used in I<sup>2</sup>C mode only.

bit 1 **UA:** Update Address bit

Used in I<sup>2</sup>C mode only.

bit 0 **BF:** Buffer Full Status bit (Receive mode only)

1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

### REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 WCOL: Write Collision Detect bit (Transmit mode only)

1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

0 = No collision

bit 6 SSPOV: Receive Overflow Indicator bit (1)

SPI Slave mode:

1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).

0 = No overflow

bit 5 SSPEN: Master Synchronous Serial Port Enable bit<sup>(2)</sup>

1 = Enables serial port and configures SCK, SDO, SDI and  $\overline{SS}$  as serial port pins

0 = Disables serial port and configures these pins as I/O port pins

bit 4 **CKP:** Clock Polarity Select bit

1 = Idle state for clock is a high level

0 = Idle state for clock is a low level

bit 3-0 SSPM3:SSPM0: Master Synchronous Serial Port Mode Select bits<sup>(3)</sup>

0101 = SPI Slave mode, clock = SCK pin, SS pin control disabled, SS can be used as I/O pin

0100 = SPI Slave mode, clock = SCK pin, SS pin control enabled

0011 = SPI Master mode, clock = TMR2 output/2

0010 = SPI Master mode, clock = Fosc/64

0001 = SPI Master mode, clock = Fosc/16

0000 = SPI Master mode, clock = Fosc/4

**Note 1:** In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.

2: When the MSSP is enabled in SPI mode, these pins must be properly configured as input or output.

3: Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C™ mode only.

#### 17.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The MSSP consists of a Transmit/Receive Shift register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then the Buffer Full Detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the

SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

### **EXAMPLE 17-1: LOADING THE SSPBUF (SSPSR) REGISTER**

| LOOP | BTFSS<br>BRA<br>MOVF | SSPSTAT, BF<br>LOOP<br>SSPBUF, W | ;Has data been received(transmit complete)? ;No ;WREG reg = contents of SSPBUF |

|------|----------------------|----------------------------------|--------------------------------------------------------------------------------|

|      | MOVWF                | RXDATA                           | ;Save in user RAM, if data is meaningful                                       |

|      | MOVF<br>MOVWF        | TXDATA, W<br>SSPBUF              | ;W reg = contents of TXDATA ;New data to xmit                                  |

To set up an Asynchronous Transmission:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 18.2 "USART Baud Rate Generator (BRG)").

- Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set Transmit bit, TX9. Can be used as address/data bit.

- Enable the transmission by setting bit, TXEN, which will also set bit, TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set

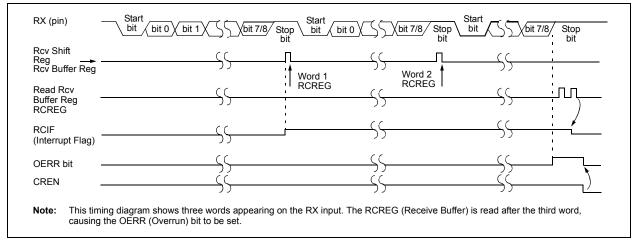

FIGURE 18-5: ASYNCHRONOUS RECEPTION

TABLE 18-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name   | Bit 7                  | Bit 6         | Bit 5      | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------|---------------|------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/GIEH               | PEIE/<br>GIEL | TMR0IE     | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>   | ADIF          | RCIF       | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>   | ADIE          | RCIE       | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>   | ADIP          | RCIP       | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 1111 1111            | 1111 1111                       |

| RCSTA  | SPEN                   | RX9           | SREN       | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| RCREG  | USART Receive Register |               |            |        |       |        |        |        |                      | 0000 0000                       |

| TXSTA  | CSRC                   | TX9           | TXEN       | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate              | Generato      | or Registe | r      | •     |        |        | ·      | 0000 0000            | 0000 0000                       |

**Legend:** x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X20 devices; always maintain these bits clear.

The value in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see **Section 19.1** "A/D Acquisition Requirements". After this acquisition time has elapsed, the A/D conversion can be started. An acquisition time can be programmed to occur between setting the GO/DONE bit and the actual start of the conversion.

The following steps should be followed to do an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D acquisition time (ADCON2)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- · Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time (if required).

- 4. Start conversion:

- Set GO/DONE bit (ADCON0 register)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- · Waiting for the A/D interrupt

- Read A/D Result registers (ADRESH:ADRESL); clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before next acquisition starts.

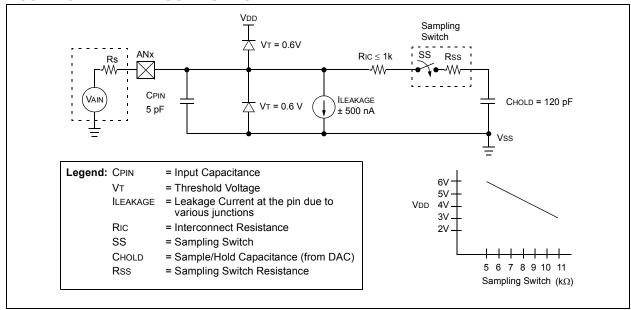

### FIGURE 19-2: ANALOG INPUT MODEL

### 20.2 Comparator Operation

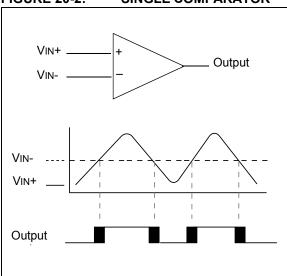

A single comparator is shown in Figure 20-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 20-2 represent the uncertainty due to input offsets and response time.

### 20.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 20-2).

FIGURE 20-2: SINGLE COMPARATOR

#### 20.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD and can be applied to either pin of the comparator(s).

#### 20.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. **Section 21.0 "Comparator Voltage Reference Module"** contains a detailed description of the comparator voltage reference module that provides this signal. The internal reference signal is used when comparators are in mode, CM2:CM0 = 110 (Figure 20-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

Depending on the setting of the CVROE bit (CVRCON<6>), the voltage reference may also be available on pin RA2.

### 20.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (see Table 26-2 in Section 26.0 "Electrical Characteristics").

### 20.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexers in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 20-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<4:5>).

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

### REGISTER 23-8: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0   | U-0 | U-0 | U-0 | R/P-1               | R/P-1               | R/P-1 | R/P-1 |

|-------|-----|-----|-----|---------------------|---------------------|-------|-------|

| _     | _   | _   | _   | WRT3 <sup>(1)</sup> | WRT2 <sup>(1)</sup> | WRT1  | WRT0  |

| bit 7 |     |     |     |                     |                     |       | bit 0 |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

bit 7-4 **Unimplemented:** Read as '0' bit 3 **WRT3:** Write Protection bit<sup>(1)</sup>

1 = Block 3 (001800-001FFFh) not write-protected 0 = Block 3 (001800-001FFFh) write-protected

bit 2 WRT2: Write Protection bit<sup>(1)</sup>

1 = Block 2 (001000-0017FFh) not write-protected 0 = Block 2 (001000-0017FFh) write-protected

bit 1 WRT1: Write Protection bit

1 = Block 1 (000800-000FFFh) not write-protected 0 = Block 1 (000800-000FFFh) write-protected

bit 0 WRT0: Write Protection bit

1 = Block 0 (000200-0007FFh) not write-protected 0 = Block 0 (000200-0007FFh) write-protected

Note 1: Unimplemented in PIC18FX220 devices; maintain this bit set.

### REGISTER 23-9: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| R/P-1 | R/P-1 | R-1                 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|---------------------|-----|-----|-----|-----|-------|

| WRTD  | WRTB  | WRTC <sup>(1)</sup> | _   | _   | _   | _   | _     |

| bit 7 |       |                     |     |     |     |     | bit 0 |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

bit 7 WRTD: Data EEPROM Write Protection bit

1 = Data EEPROM is not write-protected0 = Data EEPROM is write-protected

bit 6 WRTB: Boot Block Write Protection bit

1 = Boot block (000000-0001FFh) is not write-protected 0 = Boot block (000000-0001FFh) is write-protected **WRTC:** Configuration Register Write Protection bit<sup>(1)</sup>

bit 5 WRTC: Configuration Register Write Protection bit<sup>(1)</sup>

1 = Configuration registers (300000-3000FFh) are not write-protected 0 = Configuration registers (300000-3000FFh) are write-protected

bit 4-0 **Unimplemented:** Read as '0'

Note 1: This bit is read-only in normal execution mode; it can be written only in Program mode.

BTG Bit Toggle f

Syntax: [ label ] BTG f,b[,a]

Operands:  $0 \le f \le 255$

$0 \le b < 7$  $a \in [0,1]$

Operation:  $(\overline{f < b >}) \rightarrow f < b >$

Status Affected: None

Encoding: 0111 bbba ffff ffff

Description: Bit 'b' in data memory location 'f' is inverted. If 'a' is '0', the Access Bank

will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value

(default).

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: BTG PORTC, 4

Before Instruction:

PORTC = 0111 0101 [0x75]

After Instruction:

PORTC = 0110 0101 [0x65]

| BOV | Branch if Overflow |

|-----|--------------------|

|     |                    |

Syntax: [label] BOV n Operands:  $-128 \le n \le 127$ Operation: if Overflow bit is '1',

Status Affected: None

Encoding: 1110 0100 nnnn nnnn

Description: If the Overflow bit is '1', then the

program will branch.

$(PC) + 2 + 2n \rightarrow PC$

The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a two-cycle instruction.

1

Cycles: 1(2)

Q Cycle Activity:

If Jump:

Words:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | ʻn'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BOV JUMP

Before Instruction

PC = address (HERE)

After Instruction

If Overflow = 1;

PC = address (JUMP)

If Overflow = 0; PC = address (HERE + 2)

| GOTO              | Unconditional Branch        |                     |       |                   |   |  |

|-------------------|-----------------------------|---------------------|-------|-------------------|---|--|

| Syntax:           | [ label ]                   | GOTO                | k     |                   | ļ |  |

| Operands:         | $0 \leq k \leq 1048575$     |                     |       |                   |   |  |

| Operation:        | $k \rightarrow PC < 20:1 >$ |                     |       |                   |   |  |

| Status Affected:  | None                        |                     |       |                   |   |  |

| Encoding:         |                             |                     |       |                   |   |  |

| 1st word (k<7:0>) | 1110                        | 1111                | k7kkk | kkkk <sub>0</sub> |   |  |

| 2nd word(k<19:8>) | 1111                        | k <sub>19</sub> kkk | kkkk  | kkkk <sub>8</sub> |   |  |

Description: GOTO allows an unconditional

branch anywhere within entire 2 Mbyte memory range. The 20-bit value 'k' is loaded into PC<20:1>. GOTO is always a two-cycle

instruction.

Words: 2 Cycles: 2

Q Cycle Activity:

| Q1           | Q2                     | Q3              | Q4                                        |

|--------------|------------------------|-----------------|-------------------------------------------|

| Decode       | Read literal 'k'<7:0>, | No<br>operation | Read literal<br>'k'<19:8>,<br>Write to PC |

| No operation | No operation           | No operation    | No operation                              |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

| INCF             | Increment f                                                                   |           |             |      |  |  |

|------------------|-------------------------------------------------------------------------------|-----------|-------------|------|--|--|

| Syntax:          | [ label ]                                                                     | INCF      | f [,d [,a]] |      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 25 \\ d \in [0,1] \\ a \in [0,1] \end{array}$ | 55        |             |      |  |  |

| Operation:       | $(f) + 1 \rightarrow$                                                         | dest      |             |      |  |  |

| Status Affected: | C, DC, N                                                                      | I, OV, Z  |             |      |  |  |

| Encoding:        | 0010                                                                          | 10da      | ffff        | ffff |  |  |

| Description      | The cont                                                                      | onto of r | ogiotor (f) | oro  |  |  |

Description: The contents of register 'f' are incremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default). If 'a' is '0', the Access

Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the

BSR value (default).

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example: INCF CNT,

Before Instruction

CNT = 0xFF Z = 0 C = ? DC = ?

After Instruction

CNT = 0x00 Z = 1 C = 1 DC = 1

# 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2220/2320/4220/4320 (Industrial) PIC18LF2220/2320/4220/4320 (Industrial) (Continued)

| PIC18LF2220/2320/4220/4320<br>(Industrial)          |                                       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial                                                                        |     |       |            |              |                                       |  |  |

|-----------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--------------|---------------------------------------|--|--|

| PIC18F2220/2320/4220/4320<br>(Industrial, Extended) |                                       | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |     |       |            |              |                                       |  |  |

| Param<br>No.                                        | Device                                | Тур                                                                                                                                                                                                                                | Max | Units | Conditions |              |                                       |  |  |

|                                                     | Supply Current (IDD) <sup>(2,3)</sup> |                                                                                                                                                                                                                                    |     |       |            |              |                                       |  |  |

|                                                     | PIC18LF2X20/4X20                      | 100                                                                                                                                                                                                                                | 220 | μА    | -40°C      |              |                                       |  |  |

|                                                     |                                       | 110                                                                                                                                                                                                                                | 220 | μА    | +25°C      | VDD = 2.0V   |                                       |  |  |

|                                                     |                                       | 120                                                                                                                                                                                                                                | 220 | μΑ    | +85°C      |              |                                       |  |  |

|                                                     | PIC18LF2X20/4X20                      | 180                                                                                                                                                                                                                                | 330 | μΑ    | -40°C      |              |                                       |  |  |

|                                                     |                                       | 180                                                                                                                                                                                                                                | 330 | μΑ    | +25°C      | VDD = 3.0V   | Fosc = 1 MHz<br>( <b>RC RUN</b> mode, |  |  |

|                                                     |                                       | 170                                                                                                                                                                                                                                | 330 | μΑ    | +85°C      |              | internal oscillator source)           |  |  |

|                                                     | All devices                           | 340                                                                                                                                                                                                                                | 550 | μА    | -40°C      |              | ,                                     |  |  |

|                                                     |                                       | 330                                                                                                                                                                                                                                | 550 | μА    | +25°C      | VDD = 5.0V   |                                       |  |  |

|                                                     |                                       | 310                                                                                                                                                                                                                                | 550 | μΑ    | +85°C      | VDD = 5.0V   |                                       |  |  |

|                                                     | Extended devices                      | 410                                                                                                                                                                                                                                | 650 | μА    | +125°C     |              |                                       |  |  |

|                                                     | PIC18LF2X20/4X20                      | 350                                                                                                                                                                                                                                | 600 | μА    | -40°C      |              |                                       |  |  |

|                                                     |                                       | 360                                                                                                                                                                                                                                | 600 | μА    | +25°C      | VDD = 2.0V   |                                       |  |  |

|                                                     |                                       | 370                                                                                                                                                                                                                                | 600 | μА    | +85°C      |              |                                       |  |  |

|                                                     | PIC18LF2X20/4X20                      | 580                                                                                                                                                                                                                                | 900 | μА    | -40°C      |              |                                       |  |  |

|                                                     |                                       | 580                                                                                                                                                                                                                                | 900 | μΑ    | +25°C      | VDD = 3.0V   | Fosc = 4 MHz<br>( <b>RC RUN</b> mode, |  |  |

|                                                     |                                       | 560                                                                                                                                                                                                                                | 900 | μΑ    | +85°C      |              | internal oscillator source)           |  |  |

|                                                     | All devices                           | 1.1                                                                                                                                                                                                                                | 1.8 | mA    | -40°C      |              | , , , ,                               |  |  |

|                                                     |                                       | 1.1                                                                                                                                                                                                                                | 1.8 | mA    | +25°C      | VDD = 5.0V   | VDD = 5 0V                            |  |  |

|                                                     |                                       | 1.0                                                                                                                                                                                                                                | 1.8 | mA    | +85°C      | J 700 - 5.0V |                                       |  |  |

|                                                     | Extended devices                      | 1.2                                                                                                                                                                                                                                | 1.8 | mA    | +125°C     |              |                                       |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in  $k\Omega$ .

- 4: Standard low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

TABLE 26-11: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Symbol    |                           | Characteristi               | С                    | Min                                          | Max    | Units | Conditions                               |

|--------------|-----------|---------------------------|-----------------------------|----------------------|----------------------------------------------|--------|-------|------------------------------------------|

| 40           | Тт0Н      | T0CKI High                | Pulse Width                 | No prescaler         | 0.5 Tcy + 20                                 | _      | ns    |                                          |

|              |           |                           |                             | With prescaler       | 10                                           | _      | ns    |                                          |

| 41           | TT0L      | T0CKI Low                 | Pulse Width                 | No prescaler         | 0.5 Tcy + 20                                 | _      | ns    |                                          |

|              |           |                           |                             | With prescaler       | 10                                           | _      | ns    |                                          |

| 42           | Тт0Р      | T0CKI Peri                | od                          | No prescaler         | Tcy + 10                                     | _      | ns    |                                          |

|              |           |                           |                             | With prescaler       | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N | _      | ns    | N = prescale<br>value<br>(1, 2, 4,, 256) |

| 45           | T⊤1H      | T1CKI                     | Synchronous, no             | prescaler            | 0.5 Tcy + 20                                 | _      | ns    |                                          |

|              |           | High Time                 | Synchronous, with prescaler | PIC18 <b>F</b> XX20  | 10                                           | _      | ns    |                                          |

|              |           |                           |                             | PIC18 <b>LF</b> XX20 | 25                                           | _      | ns    |                                          |

|              |           |                           | Asynchronous                | PIC18 <b>F</b> XX20  | 30                                           | _      | ns    |                                          |

|              |           |                           |                             | PIC18 <b>LF</b> XX20 | 50                                           | _      | ns    |                                          |

| 46           | T⊤1L      | T1CKI                     | Synchronous, no             | prescaler            | 0.5 Tcy + 5                                  | _      | ns    |                                          |

|              |           | Low Time                  | Low Time Synchronous,       | PIC18 <b>F</b> XX20  | 10                                           | _      | ns    |                                          |

|              |           |                           | with prescaler              | PIC18 <b>LF</b> XX20 | 25                                           | _      | ns    |                                          |

|              |           |                           | Asynchronous                | PIC18 <b>F</b> XX20  | 30                                           | _      | ns    |                                          |

|              |           |                           |                             | PIC18 <b>LF</b> XX20 | 50                                           | _      | ns    |                                          |

| 47           | Тт1Р      | T1CKI<br>Input<br>Period  | Synchronous                 |                      | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N | _      | ns    | N = prescale<br>value<br>(1, 2, 4, 8)    |

|              |           |                           | Asynchronous                |                      | 60                                           | _      | ns    |                                          |

|              | FT1       | T1CKI Osc                 | illator Input Freque        | ency Range           | DC                                           | 50     | kHz   |                                          |

| 48           | TCKE2TMRI | Delay from<br>Timer Incre | External T1CKI C            | lock Edge to         | 2 Tosc                                       | 7 Tosc | _     |                                          |

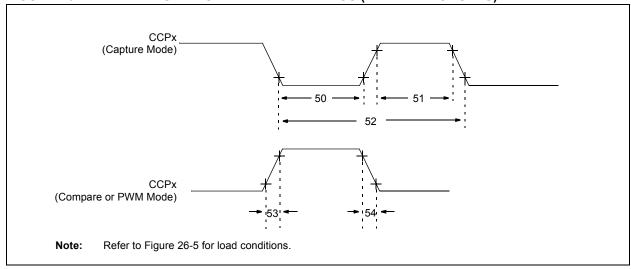

FIGURE 26-11: CAPTURE/COMPARE/PWM TIMINGS (ALL CCP MODULES)

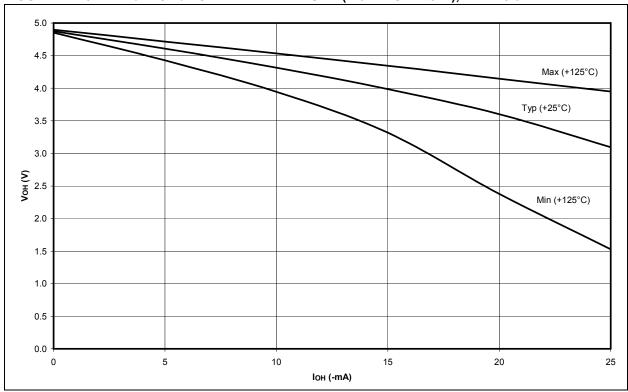

FIGURE 27-25: Voh vs. Ioh OVER TEMPERATURE (-40°C TO +125°C), VDD = 5.0V

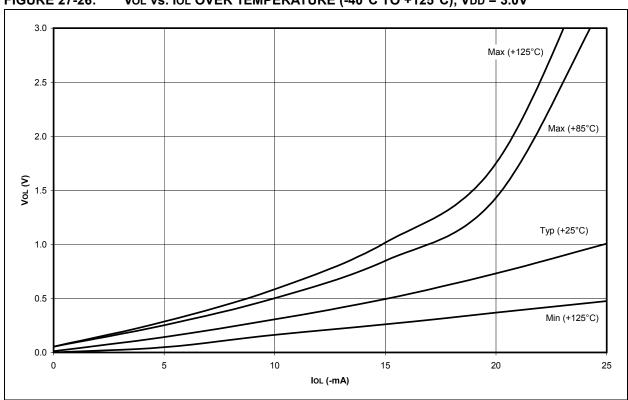

FIGURE 27-26: Vol vs. Iol OVER TEMPERATURE (-40°C TO +125°C), VDD = 3.0V

| BTFSC                                          | 270 | Interrupt Sources                                | 237 |

|------------------------------------------------|-----|--------------------------------------------------|-----|

| BTFSS                                          | 270 | A/D Conversion Complete                          | 215 |

| BTG                                            | 271 | Capture Complete (CCP)                           | 135 |

| BZ                                             | 272 | Compare Complete (CCP)                           | 136 |

| CALL                                           | 272 | Interrupt-on-Change (RB7:RB4)                    | 104 |

| CLRF                                           | 273 | INTx Pin                                         | 99  |

| CLRWDT                                         | 273 | PORTB, Interrupt-on-Change                       | 99  |

| COMF                                           | 274 | TMR0                                             | 99  |

| CPFSEQ                                         | 274 | TMR1 Overflow                                    |     |

| CPFSGT                                         | 275 | TMR2 to PR2 Match                                | 128 |

| CPFSLT                                         |     | TMR2 to PR2 Match (PWM)12                        |     |

| DAW                                            | 276 | TMR3 Overflow12                                  |     |

| DCFSNZ                                         |     | USART Receive/Transmit Complete                  | ,   |

| DECF                                           |     | Interrupts                                       |     |

| DECFSZ                                         |     | Interrupts, Enable Bits                          | 0,  |

| GOTO                                           |     | CCP1 Enable (CCP1IE Bit)                         | 135 |

| INCF                                           |     | Interrupts, Flag Bits                            | 100 |

| INCFSZ                                         |     | CCP1 Flag (CCP1IF Bit)                           | 125 |

| INFSNZ                                         |     | CCP1IF Flag (CCP1IF Bit)                         |     |

| IORLW                                          |     | ÷ , , ,                                          | 130 |

|                                                |     | Interrupt-on-Change (RB7:RB4) Flag               | 104 |

| IORWF                                          |     | (RBIF Bit)                                       |     |

| LFSR                                           |     | INTOSC Frequency Drift                           | 40  |

| MOVF                                           |     | INTOSC, INTRC. See Internal Oscillator Block.    | 000 |

| MOVFF                                          |     | IORLW                                            |     |

| MOVLB                                          |     | IORWF                                            |     |

| MOVLW                                          |     | IPR Registers                                    | 96  |

| MOVWF                                          |     | L                                                |     |

| MULLW                                          |     | <del>-</del>                                     | 004 |

| MULWF                                          |     | LFSR                                             |     |

| NEGF                                           |     | Look-up Tables                                   |     |

| NOP                                            | 285 | Low-Voltage Detect                               |     |

| POP                                            | 286 | Characteristics                                  |     |

| PUSH                                           | 286 | Effects of a Reset                               |     |

| RCALL                                          | 287 | Operation                                        |     |

| Reset                                          | 287 | Current Consumption                              |     |

| RETFIE                                         | 288 | Reference Voltage Set Point                      | 235 |

| RETLW                                          | 288 | Operation During Sleep                           | 235 |

| RETURN                                         | 289 | Low-Voltage ICSP Programming                     |     |

| RLCF                                           | 289 | LVD. See Low-Voltage Detect                      | 231 |

| RLNCF                                          | 290 | М                                                |     |

| RRCF                                           | 290 | M                                                |     |

| RRNCF                                          | 291 | Master Synchronous Serial Port (MSSP). See MSSP. |     |

| SETF                                           |     | Master Synchronous Serial Port. See MSSP         |     |

| SLEEP                                          |     | Memory Organization                              | 53  |

| SUBFWB                                         |     | Data Memory                                      | 59  |

| SUBLW                                          |     | Program Memory                                   |     |

| SUBWF                                          |     | Memory Programming Requirements                  | 321 |

| SUBWFB                                         |     | Microchip Internet Web Site                      |     |

| SWAPF                                          |     | Migration from Baseline to Enhanced Devices      |     |

| TBLRD                                          |     | Migration from High-End to Enhanced Devices      |     |

| TBLWT                                          |     | Migration from Mid-Range to Enhanced Devices     |     |

| TSTFSZ                                         |     | MOVF                                             |     |

| XORLW                                          |     | MOVFF                                            |     |

|                                                |     | MOVLB                                            |     |

| XORWF                                          |     | MOVLW                                            |     |

| Summary Table                                  | 260 | MOVWF                                            |     |

| ITCON Register                                 |     |                                                  |     |

| RBIF Bit                                       |     | MPLAB ASM30 Assembler, Linker, Librarian         |     |

| ITCON Registers                                | 89  | MPLAB ICD 2 In-Circuit Debugger                  | 303 |

| iter-Integrated Circuit. See I <sup>2</sup> C. |     | MPLAB ICE 2000 High-Performance                  |     |

| ternal Oscillator Block                        | 22  | Universal In-Circuit Emulator                    | 303 |

| iternal RC Oscillator                          |     | MPLAB Integrated Development                     |     |

| Use with WDT                                   | 246 | Environment Software                             |     |

| iternet Address                                | 389 | MPLAB PM3 Device Programmer                      |     |

|                                                |     | MPLAB REAL ICE In-Circuit Emulator System        | 303 |