#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

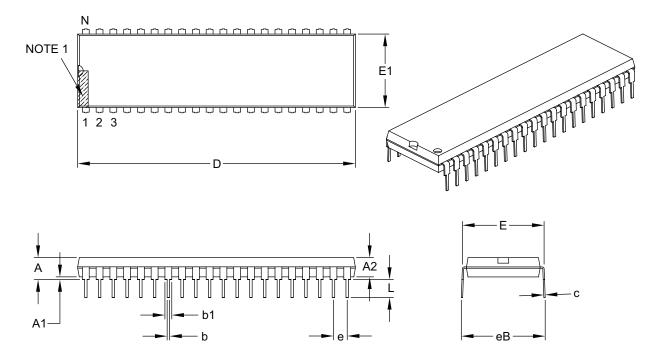

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2320-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din New-                                                     | Pin N | umber | Pin                     | Buffer                              | Description                                                                                                                                                      |

|--------------------------------------------------------------|-------|-------|-------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                     | PDIP  | SOIC  | Туре                    | Туре                                | Description                                                                                                                                                      |

| MCLR/VPP<br>MCLR                                             | 1     | 1     | I                       | ST                                  | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low Rese<br>to the device.                             |

| VPP                                                          |       |       | Р                       |                                     | Programming voltage input.                                                                                                                                       |

| OSC1/CLKI/RA7<br>OSC1<br>CLKI                                | 9     | 9     | 1                       | ST<br>CMOS                          | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode, CMOS otherwise. |

| RA7                                                          |       |       | ı<br>1/0                | TTL                                 | External clock source input. Always associated with pin<br>function OSC1. (See related OSC1/CLKI, OSC2/CLKO pins.<br>General purpose I/O pin.                    |

| OSC2/CLKO/RA6<br>OSC2                                        | 10    | 10    | 0                       |                                     | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonator                                                               |

| CLKO                                                         |       |       | 0                       | —                                   | in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKO which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate                   |

| RA6                                                          |       |       | I/O                     | TTL                                 | General purpose I/O pin.                                                                                                                                         |

| RA0/AN0<br>RA0<br>AN0                                        | 2     | 2     | I/O<br>I                | TTL<br>Analog                       | PORTA is a bidirectional I/O port.<br>Digital I/O.<br>Analog input 0.                                                                                            |

| RA1/AN1<br>RA1<br>AN1                                        | 3     | 3     | I/O<br>I                | TTL<br>Analog                       | Digital I/O.<br>Analog input 1.                                                                                                                                  |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF          | 4     | 4     | I/O<br> <br> <br>0      | TTL<br>Analog<br>Analog<br>Analog   | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (low) input.<br>Comparator reference voltage output.                                                    |

| RA3/AN3/Vref+<br>RA3<br>AN3<br>Vref+                         | 5     | 5     | I/O<br>I<br>I           | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (high) input.                                                                                           |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT                     | 6     | 6     | I/O<br>I<br>O           | ST/OD<br>ST                         | Digital I/O. Open drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                       |

| RA5/AN4/SS/LVDIN/C2OUT<br>RA5<br>AN4<br>SS<br>LVDIN<br>C2OUT | 7     | 7     | I/O<br> <br> <br> <br>0 | TTL<br>Analog<br>TTL<br>Analog<br>— | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Low-Voltage Detect input.<br>Comparator 2 output.                                                  |

| RA6                                                          |       |       |                         |                                     | See the OSC2/CLKO/RA6 pin.                                                                                                                                       |

| RA7                                                          |       |       |                         |                                     | See the OSC1/CLKI/RA7 pin.                                                                                                                                       |

| Legend: TTL = TTL comp<br>ST = Schmitt Tr<br>O = Output      |       |       | ith CM                  | OS levels                           | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                 |

#### **TABLE 1-2:** PIC18F2220/2320 PINOUT I/O DESCRIPTIONS

O = Output OD = Open-drain (no diode to VDD)

Note 1: Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

| Din Norre                                         | Pin Number |      |     | Pin Buffe       | Buffer               | Description                                                                                                      |  |  |

|---------------------------------------------------|------------|------|-----|-----------------|----------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                          | PDIP       | TQFP | QFN | Туре            | Туре                 | Description                                                                                                      |  |  |

|                                                   |            |      |     |                 |                      | PORTB is a bidirectional I/O port. PORTB can be software<br>programmed for internal weak pull-ups on all inputs. |  |  |

| RB0/AN12/INT0<br>RB0<br>AN12<br>INT0              | 33         | 8    | 9   | I/O<br>I<br>I   | TTL<br>Analog<br>ST  | Digital I/O.<br>Analog input 12.<br>External interrupt 0.                                                        |  |  |

| RB1/AN10/INT1<br>RB1<br>AN10<br>INT1              | 34         | 9    | 10  | I/O<br>I<br>I   | TTL<br>Analog<br>ST  | Digital I/O.<br>Analog input 10.<br>External interrupt 1.                                                        |  |  |

| RB2/AN8/INT2<br>RB2<br>AN8<br>INT2                | 35         | 10   | 11  | I/O<br>I<br>I   | TTL<br>Analog<br>ST  | Digital I/O.<br>Analog input 8.<br>External interrupt 2.                                                         |  |  |

| RB3/AN9/CCP2<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup> | 36         | 11   | 12  | I/O<br>I<br>I/O | TTL<br>Analog<br>ST  | Digital I/O.<br>Analog input 9.<br>Capture 2 input, Compare 2 output, PWM2 output.                               |  |  |

| RB4/AN11/KBI0<br>RB4<br>AN11<br>KBI0              | 37         | 14   | 14  | I/O<br>I<br>I   | TTL<br>Analog<br>TTL | Digital I/O.<br>Analog input 11.<br>Interrupt-on-change pin.                                                     |  |  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                | 38         | 15   | 15  | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>Low-voltage ICSP™ programming enable pin.                            |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                | 39         | 16   | 16  | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.                  |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                | 40         | 17   | 17  | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                   |  |  |

Ρ

= Power

#### **TABLE 1-3:** PIC18F4220/4320 PINOUT I/O DESCRIPTIONS (CONTINUED)

O = Output

OD = Open-drain (no diode to VDD)

**Note 1:** Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

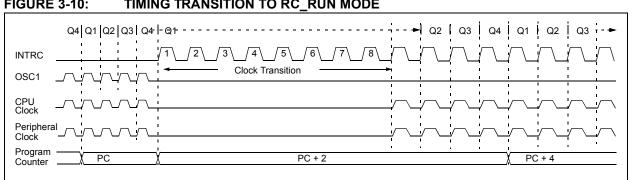

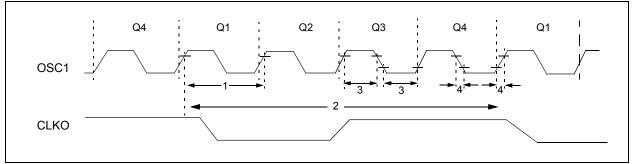

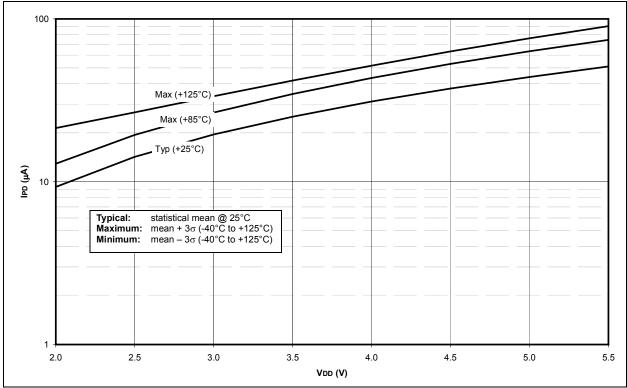

#### 3.4.3 RC\_RUN MODE

In RC RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer and the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications which are not highly timing sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either of the INTIO1 or INTIO2 oscillators), there are no distinguishable differences between PRI RUN and RC RUN modes during execution. However, a clock switch delay will occur during entry to, and exit from, RC RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC RUN mode is not recommended.

This mode is entered by clearing the IDLEN bit, setting SCS1 (SCS0 is ignored) and executing a SLEEP instruction. The IRCF bits may select the clock frequency before the **SLEEP** instruction is executed. When the clock source is switched to the INTOSC multiplexer (see Figure 3-10), the primary oscillator is shut down and the OSTS bit is cleared.

The IRCF bits may be modified at any time to immediately change the system clock speed. Executing a SLEEP instruction is not required to select a new clock frequency from the INTOSC multiplexer.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

If the IRCF bits are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear: there will be no indication of the current clock source. The INTRC source is providing the system clocks.

If the IRCF bits are changed from all clear (thus enabling the INTOSC output), the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the system continue while the INTOSC source stabilizes in approximately 1 ms.

If the IRCF bits were previously at a non-zero value before the **SLEEP** instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set.

When a wake-up event occurs, the system continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 3-8). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

#### **FIGURE 3-10:** TIMING TRANSITION TO RC\_RUN MODE

#### 5.8 Look-up Tables

Look-up tables are implemented two ways:

- Computed GOTO

- Table Reads

#### 5.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-4.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW  $0 \times nn$  instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW  $0 \times nn$  instructions that returns the value  $0 \times nn$  to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSB = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-4: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVFW  | OFFSET |

|-------|--------|--------|

|       | CALL   | TABLE  |

| ORG   | 0xnn00 |        |

| TABLE | ADDWF  | PCL    |

|       | RETLW  | 0xnn   |

|       | RETLW  | 0xnn   |

|       | RETLW  | 0xnn   |

|       | •      |        |

|       | •      |        |

|       | •      |        |

|       |        |        |

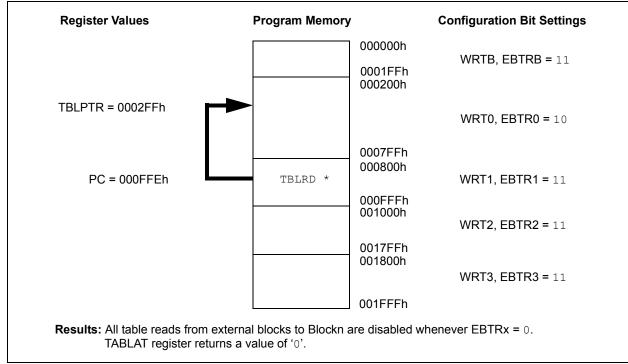

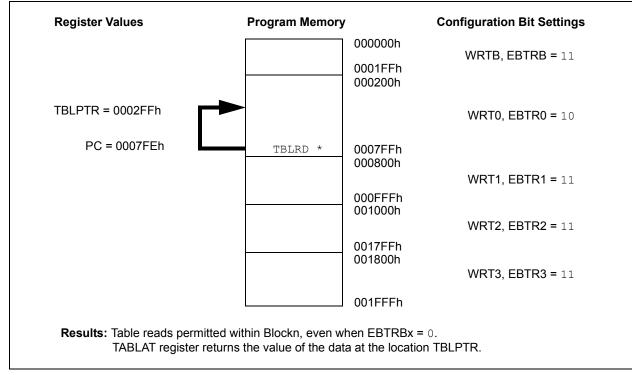

#### 5.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory, one byte at a time.

The Table Read/Table Write operation is discussed further in Section 6.1 "Table Reads and Table Writes".

### 5.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 5-6 shows the data memory organization for the PIC18F2X20/4X20 devices.

The data memory map is divided into as many as 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits of the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (FFFh) and extend towards F80h. Any remaining space beyond the SFRs in the bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the data memory map without banking. See Section 5.12 "Indirect Addressing, INDF and FSR Registers" for indirect addressing details.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. **Section 5.10 "Access Bank"** provides a detailed description of the Access RAM.

#### 5.9.1 GENERAL PURPOSE REGISTER FILE

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

Data RAM is available for use as GPR registers by all instructions. The second half of Bank 15 (F80h to FFFh) contains SFRs. All other banks of data memory contain GPRs, starting with Bank 0.

#### **REGISTER 6-1: EECON1: DATA EEPROM CONTROL REGISTER 1**

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | EEPGD: Flash Program or Data EEPROM Memory Select bit                                                                                                                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Access Flash program memory                                                                                                                                                                                                                                         |

|         | 0 = Access data EEPROM memory                                                                                                                                                                                                                                           |

| bit 6   | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                                                                                                                                                                                             |

|         | 1 = Access Configuration registers                                                                                                                                                                                                                                      |

|         | 0 = Access Flash program or data EEPROM memory                                                                                                                                                                                                                          |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                              |

| bit 4   | FREE: Flash Row Erase Enable bit                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by completion of erase operation)</li> <li>0 = Perform write-only</li> </ul>                                                                                              |

| L:1 0   |                                                                                                                                                                                                                                                                         |

| bit 3   | WRERR: EEPROM Error Flag bit <sup>(1)</sup>                                                                                                                                                                                                                             |

|         | <ul> <li>1 = A write operation was prematurely terminated (any Reset during self-timed programming)</li> <li>0 = The write operation completed normally</li> </ul>                                                                                                      |

| bit 2   | WREN: Write Enable bit                                                                                                                                                                                                                                                  |

|         | 1 = Allows write cycles to Flash program/data EEPROM                                                                                                                                                                                                                    |

|         | 0 = Inhibits write cycles to Flash program/data EEPROM                                                                                                                                                                                                                  |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete.<br/>The WR bit can only be set (not cleared) in software.)</li> </ul> |

|         | 0 = Write cycle completed                                                                                                                                                                                                                                               |

| bit 0   | RD: Read Control bit                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Initiates a memory read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1.)</li> </ul>                                                                           |

|         | 0 = Read completed                                                                                                                                                                                                                                                      |

| Note 1: | When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error                                                                                                                                                                          |

condition.

## 6.4 Erasing Flash Program Memory

The minimum erase block size is 32 words or 64 bytes under firmware control. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in Flash memory is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased; TBLPTR<5:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The CFGS bit must be clear to access program Flash and data EEPROM memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation. The WR bit is set as part of the required instruction sequence (as shown in Example 6-2) and starts the actual erase operation. It is not necessary to load the TABLAT register with any data as it is ignored.

For protection, the write initiate sequence using EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

#### 6.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer with address of row being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Execute a NOP.

- 9. Re-enable interrupts.

#### EXAMPLE 6-2: ERASING A FLASH PROGRAM MEMORY ROW

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW | ; load TBLPTR with the base<br>; address of the memory block |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|

|           | MOVWF                                     | TBLPTRL                                                                  |                                                              |

| ERASE_ROW |                                           |                                                                          |                                                              |

|           | BSF                                       | EECON1,EEPGD                                                             | ; point to Flash program memory                              |

|           | BSF                                       | EECON1,WREN                                                              | ; enable write to memory                                     |

|           | BSF                                       | EECON1, FREE                                                             | ; enable Row Erase operation                                 |

|           |                                           | ,                                                                        | -                                                            |

|           | BCF                                       | INTCON, GIE                                                              | ; disable interrupts                                         |

|           | MOVLW                                     | 55h                                                                      |                                                              |

|           | MOVWF                                     | EECON2                                                                   | ; write 55H                                                  |

| Required  | MOVLW                                     | AAh                                                                      | ,                                                            |

| -         |                                           |                                                                          |                                                              |

| Sequence  | MOVWF                                     | EECON2                                                                   | ; write AAH                                                  |

|           | BSF                                       | EECON2,WR                                                                | ; start erase (CPU stall)                                    |

|           | NOP                                       |                                                                          |                                                              |

|           | BSF                                       | INTCON, GIE                                                              | ; re-enable interrupts                                       |

# PIC18F2220/2320/4220/4320

| R/W-1           | R/W-1                                                                     | R/W-1                             | R/W-1            | U-0              | R/W-1            | U-0            | R/W-1 |

|-----------------|---------------------------------------------------------------------------|-----------------------------------|------------------|------------------|------------------|----------------|-------|

| RBPU            | INTEDG0                                                                   | INTEDG1                           | INTEDG2          | —                | TMR0IP           | —              | RBIP  |

| bit 7           |                                                                           | •                                 |                  |                  |                  |                | bit 0 |

|                 |                                                                           |                                   |                  |                  |                  |                |       |

| Legend:         |                                                                           |                                   |                  |                  |                  |                |       |

| R = Readable    |                                                                           | W = Writable                      |                  | -                | mented bit, read |                |       |

| -n = Value at F | POR                                                                       | '1' = Bit is set                  |                  | '0' = Bit is cle | eared            | x = Bit is unk | nown  |

| bit 7           |                                                                           | B Pull-up Enal                    | hla hit          |                  |                  |                |       |

|                 |                                                                           | B pull-ups are                    |                  |                  |                  |                |       |

|                 |                                                                           | oull-ups are en                   |                  | idual port latch | n values         |                |       |

| bit 6           |                                                                           | ternal Interrup                   |                  |                  |                  |                |       |

|                 |                                                                           | on rising edge                    |                  |                  |                  |                |       |

|                 | 0 = Interrupt                                                             | on falling edge                   | •                |                  |                  |                |       |

| bit 5           |                                                                           | ternal Interrup                   | t 1 Edge Seleo   | ct bit           |                  |                |       |

|                 |                                                                           | on rising edge<br>on falling edge |                  |                  |                  |                |       |

| bit 4           | •                                                                         | ternal Interrup                   |                  | ct bit           |                  |                |       |

|                 |                                                                           | on rising edge                    | 0                |                  |                  |                |       |

|                 | 0 = Interrupt                                                             | on falling edge                   | •                |                  |                  |                |       |

| bit 3           | Unimplemen                                                                | ted: Read as '                    | 0'               |                  |                  |                |       |

| bit 2           |                                                                           | R0 Overflow In                    | terrupt Priority | ' bit            |                  |                |       |

|                 | 1 = High prio                                                             |                                   |                  |                  |                  |                |       |

| bit 1           | 0 = Low prior                                                             | -                                 | o <b>'</b>       |                  |                  |                |       |

| bit 0           | Unimplemented: Read as '0'<br>RBIP: RB Port Change Interrupt Priority bit |                                   |                  |                  |                  |                |       |

|                 | 1 = High prio                                                             | •                                 | rupt Friority D  | it.              |                  |                |       |

|                 | 0 = Low prior                                                             |                                   |                  |                  |                  |                |       |

|                 |                                                                           | -                                 |                  |                  |                  |                |       |

| Note: Inte      |                                                                           |                                   | • • •            |                  | regardless of t  |                |       |

#### REGISTER 9-2: INTCON2: INTERRUPT CONTROL REGISTER 2

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

## 9.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from powermanaged mode. RCON also contains the bit that enables interrupt priorities (IPEN).

### REGISTER 9-10: RCON: RESET CONTROL REGISTER

| R/W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-------|-------|

| IPEN  | _   | _   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |     |       |     |     |       | bit 0 |

| Legend:                                                                                                                                      |                                |                                                                                                                                                                                                               |                        |                    |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|--|--|--|--|

| R = Reada                                                                                                                                    | ble bit                        | W = Writable bit                                                                                                                                                                                              | U = Unimplemented bit, | read as '0'        |  |  |  |  |

| -n = Value                                                                                                                                   | at POR                         | '1' = Bit is set                                                                                                                                                                                              | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |

| bit 7 <b>IPEN:</b> Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (F |                                |                                                                                                                                                                                                               |                        | mode)              |  |  |  |  |

| bit 6-5                                                                                                                                      | Unimplemented: Read as '0'     |                                                                                                                                                                                                               |                        |                    |  |  |  |  |

| bit 4                                                                                                                                        | RI: RESET Instruction Flag bit |                                                                                                                                                                                                               |                        |                    |  |  |  |  |

| 0 = T                                                                                                                                        |                                | <ul> <li>The RESET instruction was not executed (set by firmware only)</li> <li>The RESET instruction was executed causing a device Reset (must be set in software after a Brown-out Reset occurs)</li> </ul> |                        |                    |  |  |  |  |

|       | Brown out (coot occurry)                                                                |

|-------|-----------------------------------------------------------------------------------------|

| bit 3 | TO: Watchdog Time-out Flag bit                                                          |

|       | 1 = Set by power-up, CLRWDT instruction or SLEEP instruction                            |

|       | 0 = A WDT time-out occurred                                                             |

| bit 2 | PD: Power-Down Detection Flag bit                                                       |

|       | 1 = Set by power-up or by the CLRWDT instruction                                        |

|       | 0 = Cleared by execution of the SLEEP instruction                                       |

| bit 1 | POR: Power-on Reset Status bit                                                          |

|       | 1 = A Power-on Reset has not occurred (set by firmware only)                            |

|       | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)   |

| bit 0 | BOR: Brown-out Reset Status bit                                                         |

|       | 1 = A Brown-out Reset has not occurred (set by firmware only)                           |

|       | 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs) |

| Name                        | Bit#  | Buffer Type | Function                                                                                                                                     |

|-----------------------------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI             | bit 0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                                                                        |

| RC1/T1OSI/CCP2              | bit 1 | ST          | Input/output port pin, Timer1 oscillator input or Capture 2 input/<br>Compare 2 output/PWM output when CCP2MX Configuration bit is disabled. |

| RC2/CCP1/P1A <sup>(1)</sup> | bit 2 | ST          | Input/output port pin, Capture 1 input/Compare 1 output/PWM1 output or Enhanced PWM output A <sup>(1)</sup> .                                |

| RC3/SCK/SCL                 | bit 3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C^{TM}$ modes.                                                             |

| RC4/SDI/SDA                 | bit 4 | ST          | RC4 can also be the SPI data in (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                              |

| RC5/SDO                     | bit 5 | ST          | Input/output port pin or Master Synchronous Serial Port data output.                                                                         |

| RC6/TX/CK                   | bit 6 | ST          | Input/output port pin, addressable USART asynchronous transmit or addressable USART synchronous clock.                                       |

| RC7/RX/DT                   | bit 7 | ST          | Input/output port pin, addressable USART asynchronous receive or addressable USART synchronous data.                                         |

#### TABLE 10-5: PORTC FUNCTIONS

**Legend:** ST = Schmitt Trigger input

**Note 1:** Enhanced PWM output is available only on PIC18F4X20 devices.

#### TABLE 10-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7  | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|--------|-----------|------------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| PORTC | RC7    | RC6       | RC5        | RC4   | RC3   | RC2   | RC1   | RC0   | XXXX XXXX            | uuuu uuuu                       |

| LATC  | LATC D | ata Latch | Register   |       |       |       |       |       | XXXX XXXX            | uuuu uuuu                       |

| TRISC | PORTC  | Data Dire | ection Reg | ister |       |       |       |       | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged

#### 17.3.3 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI must have TRISC<4> bit cleared

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

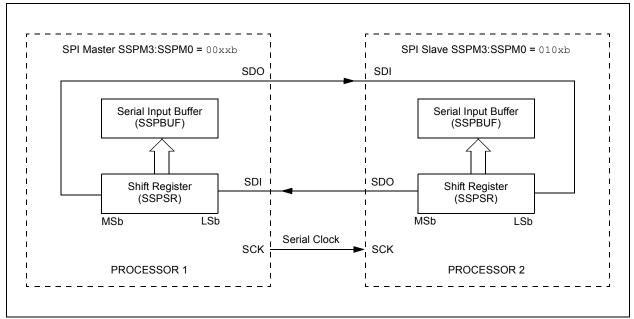

### 17.3.4 TYPICAL CONNECTION

Register 17-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- · Master sends dummy data Slave sends data

#### FIGURE 17-2: SPI MASTER/SLAVE CONNECTION

## 18.2 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit Baud Rate Generator. The SPBRG register controls the period of a free-running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 18-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 18-1. From this, the error in baud rate can be determined.

Example 18-1 shows the calculation of the baud rate error for the following conditions:

- Fosc = 16 MHz

- Desired Baud Rate = 9600

- BRGH = 0

- SYNC = 0

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks, because the Fosc/(16 (X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 18.2.1 POWER-MANAGED MODE OPERATION

The system clock is used to generate the desired baud rate; however, when a power-managed mode is entered, the clock source may be operating at a different frequency than in PRI\_RUN mode. In Sleep mode, no clocks are present and in PRI\_IDLE, the primary clock source continues to provide clocks to the baud rate generator; however, in other power-managed modes, the clock frequency will probably change. This may require the value in SPBRG to be adjusted.

#### 18.2.2 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

### EXAMPLE 18-1: CALCULATING BAUD RATE ERROR

| Desired Baud Rate    | = Fosc/(64 (X + 1))                            |

|----------------------|------------------------------------------------|

| Solving for X:       |                                                |

| Х                    | = ((Fosc/Desired Baud Rate)/64) – 1            |

| Х                    | = ((1600000/9600)/64) - 1                      |

| Х                    | = [25.042] = 25                                |

| Calculated Baud Rate | $e = \frac{16000000}{(64 (25 + 1))}$<br>= 9615 |

| Error                | = (Calculated Baud Rate – Desired Baud Rate)   |

| Desired Baud Rate    |                                                |

|                      | = (9615 - 9600)/9600                           |

|                      | = 0.16%                                        |

#### TABLE 18-1: BAUD RATE FORMULA

| SYNC             | BRGH = 0 (Low Speed)          | BRGH = 1 (High Speed)         |

|------------------|-------------------------------|-------------------------------|

| 0 (Asynchronous) | Baud Rate = Fosc/(64 (X + 1)) | Baud Rate = Fosc/(16 (X + 1)) |

| 1 (Synchronous)  | Baud Rate = Fosc/(4 (X + 1))  | N/A                           |

**Legend:** X = value in SPBRG (0 to 255)

#### TABLE 18-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name  | Bit 7   | Bit 6     | Bit 5     | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|---------|-----------|-----------|-------|---------|-------|-------|-------|----------------------|---------------------------------|

| TXSTA | CSRC    | TX9       | TXEN      | SYNC  | —       | BRGH  | TRMT  | TX9D  | 0000 -010            | 0000 -010                       |

| RCSTA | SPEN    | RX9       | SREN      | CREN  | ADDEN   | FERR  | OERR  | RX9D  | 0000 000x            | 0000 000x                       |

| SPBRG | Baud Ra | 0000 0000 | 0000 0000 |       |         |       |       |       |                      |                                 |

|       |         |           |           |       | 1 (1) 0 |       |       |       |                      |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

|             |                       |            | -                           |                       |            |                             |                       | •          | •, =• •                     |                       | ,          |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Foso                  | c = 40.000 | ) MHz                       | Foso                  | ; = 20.00  | 0 MHz                       | Fos                   | c = 16.000 | ) MHz                       | Fos                   | c = 10.000 | ) MHz                       |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     |            |                             | _                     | _          | _                           | 0.98                  | 225.52     | 255                         | 0.61                  | 103.45     | 255                         |

| 1.2         | _                     | _          | _                           | 1.22                  | 1.73       | 255                         | 1.20                  | 0.16       | 207                         | 1.20                  | 0.16       | 129                         |

| 2.4         | 2.44                  | 1.73       | 255                         | 2.40                  | 0.16       | 129                         | 2.40                  | 0.16       | 103                         | 2.40                  | 0.16       | 64                          |

| 9.6         | 9.62                  | 0.16       | 64                          | 9.47                  | -1.36      | 32                          | 9.62                  | 0.16       | 25                          | 9.77                  | 1.73       | 15                          |

| 19.2        | 18.94                 | -1.36      | 32                          | 19.53                 | 1.73       | 15                          | 19.23                 | 0.16       | 12                          | 19.53                 | 1.73       | 7                           |

| 38.4        | 39.06                 | 1.73       | 15                          | 39.06                 | 1.73       | 7                           | 35.71                 | -6.99      | 6                           | 39.06                 | 1.73       | 3                           |

| 57.6        | 56.82                 | -1.36      | 10                          | 62.50                 | 8.51       | 4                           | 62.50                 | 8.51       | 3                           | 52.08                 | -9.58      | 2                           |

| 76.8        | 78.13                 | 1.73       | 7                           | 78.13                 | 1.73       | 3                           | 83.33                 | 8.51       | 2                           | 78.13                 | 1.73       | 1                           |

| 96.0        | 89.29                 | -6.99      | 6                           | 104.17                | 8.51       | 2                           | _                     | _          | —                           | —                     | _          | —                           |

| 115.2       | 125.00                | 8.51       | 4                           | —                     | —          | —                           | 125.00                | 8.51       | 1                           | 78.13                 | -32.18     | 1                           |

| 250.0       | 208.33                | -16.67     | 2                           | —                     | —          |                             | 250.00                | 0.00       | 0                           | —                     | _          | —                           |

| 300.0       | 312.50                | 4.17       | 1                           | 312.50                | 4.17       | 0                           | —                     |            | —                           | —                     | —          | —                           |

| 625.0       | 625.00                | 0.00       | 0                           | —                     | —          | —                           | _                     |            | —                           | _                     |            | —                           |

#### TABLE 18-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0, LOW SPEED)

| BAUD        | Fosc                  | = 8.0000   | 00 MHz                      | Fosc                  | = 7.15909  | 90 MHz                      | Fosc                  | = 5.06880  | 00 MHz                      | Fosc                  | = 4.00000  | 0 MHz                       |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.49                  | 62.76      | 255                         | 0.44                  | 45.65      | 255                         | 0.31                  | 3.13       | 255                         | 0.30                  | 0.16       | 207                         |

| 1.2         | 1.20                  | 0.16       | 103                         | 1.20                  | 0.23       | 92                          | 1.20                  | 0.00       | 65                          | 1.20                  | 0.16       | 51                          |

| 2.4         | 2.40                  | 0.16       | 51                          | 2.38                  | -0.83      | 46                          | 2.40                  | 0.00       | 32                          | 2.40                  | 0.16       | 25                          |

| 9.6         | 9.62                  | 0.16       | 12                          | 9.32                  | -2.90      | 11                          | 9.90                  | 3.13       | 7                           | 8.93                  | -6.99      | 6                           |

| 19.2        | 17.86                 | -6.99      | 6                           | 18.64                 | -2.90      | 5                           | 19.80                 | 3.13       | 3                           | 20.83                 | 8.51       | 2                           |

| 38.4        | 41.67                 | 8.51       | 2                           | 37.29                 | -2.90      | 2                           | 39.60                 | 3.13       | 1                           | 31.25                 | -18.62     | 1                           |

| 57.6        | 62.50                 | 8.51       | 1                           | 55.93                 | -2.90      | 1                           | _                     | _          | _                           | 62.50                 | 8.51       | 0                           |

| —           | —                     | _          | —                           | —                     | _          | _                           | 79.20                 | 3.13       | 0                           | —                     | —          | —                           |

| 115.2       | 125.00                | 8.51       | 0                           | 111.86                | -2.90      | 0                           | _                     | _          | —                           | —                     | _          | —                           |

| DAUD                | Fosc                  | = 3.57954  | 15 MHz                      | Fosc                  | = 2.00000  | 00 MHz                      | Fosc                  | = 1.00000  | 0 MHz                       | Fosc                  | = 0.03276  | 68 MHz                      |

|---------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.30                  | 0.23       | 185                         | 0.30                  | 0.16       | 103                         | 0.30                  | 0.16       | 51                          | 0.26                  | -14.67     | 1                           |

| 1.2                 | 1.19                  | -0.83      | 46                          | 1.20                  | 0.16       | 25                          | 1.20                  | 0.16       | 12                          | —                     | _          | _                           |

| 2.4                 | 2.43                  | 1.32       | 22                          | 2.40                  | 0.16       | 12                          | 2.23                  | -6.99      | 6                           | —                     | _          | _                           |

| 9.6                 | 9.32                  | -2.90      | 5                           | 10.42                 | 8.51       | 2                           | 7.81                  | -18.62     | 1                           | —                     | _          | _                           |

| 19.2                | 18.64                 | -2.90      | 2                           | 15.63                 | -18.62     | 1                           | 15.63                 | -18.62     | 0                           | —                     | _          | _                           |

| 38.4                | _                     | _          | _                           | 31.25                 | -18.62     | 0                           | _                     | _          | _                           | —                     | _          | _                           |

| 57.6                | 55.93                 | -2.90      | 0                           | —                     | _          | _                           | —                     | —          | —                           | —                     | —          | _                           |

| U-0          | U-0                  |                                                           | R/W-0       |               | R/W-0       | F      | R/W-0 <sup>(1</sup> | )                  | R/W <sup>(</sup>   | 1)          | R/W     | /(1)    | R      | /W(1)       |

|--------------|----------------------|-----------------------------------------------------------|-------------|---------------|-------------|--------|---------------------|--------------------|--------------------|-------------|---------|---------|--------|-------------|

| _            | —                    |                                                           | VCFG1       |               | VCFG0       |        | PCFG3               |                    | PCFG               | 62          | PCF     | G1      | PC     | CFGC        |

| oit 7        |                      |                                                           |             |               |             |        |                     |                    |                    |             |         |         |        | b           |

| Legend:      |                      |                                                           |             |               |             |        |                     |                    |                    |             |         |         |        |             |

| R = Readab   | le hit               | W :                                                       | = Writal    | nle hit       |             | 11:    | = Unim              | olemer             | nted hit           | read a      | as 'O'  |         |        |             |

| -n = Value a |                      |                                                           | = Bit is    |               |             |        | = Bit is            |                    |                    |             | x = Bit | is unkr | nown   |             |

|              |                      | 1                                                         | - Dit 13    | 301           |             | 0      | - Dit 13            | cicarc             | u                  | ,           |         |         | 100011 |             |

| bit 7-6      | Unimplem             | ented:                                                    | Read a      | <b>as</b> '0' |             |        |                     |                    |                    |             |         |         |        |             |

| bit 5        | -                    | VCFG1: Voltage Reference Configuration bit (VREF- source) |             |               |             |        |                     |                    |                    |             |         |         |        |             |

|              | 1 = VREF-            | •                                                         |             |               | 0           | (      |                     | ,                  | ,                  |             |         |         |        |             |

|              | 0 <b>= V</b> SS      | . /                                                       |             |               |             |        |                     |                    |                    |             |         |         |        |             |

| bit 4        | VCFG0: V             | VCFG0: Voltage Reference Configuration bit (VREF+ source) |             |               |             |        |                     |                    |                    |             |         |         |        |             |

|              | 1 = VREF+            | (AN3)                                                     |             |               |             |        |                     |                    |                    |             |         |         |        |             |

|              | 0 <b>= V</b> DD      |                                                           |             |               |             |        |                     |                    |                    |             |         |         |        |             |

| bit 3-0      | PCFG3:PC             | CFG0: /                                                   | A/D Por     | t Confi       | guration    | Contr  |                     |                    |                    |             |         |         |        |             |

|              | PCFG3:               | 12                                                        | 11          | 10            | 6           | ~      | 7(2)                | 3 <sup>(2)</sup>   | 5 <sup>(2)</sup>   | 4           | 8       | 2       | -      | 0           |

|              | PCFG0                | AN12                                                      | AN11        | AN10          | AN9         | AN8    | AN7 <sup>(2)</sup>  | AN6 <sup>(2)</sup> | AN5 <sup>(2)</sup> | AN4         | AN3     | AN2     | AN1    | ANO         |

|              | <sub>0000</sub> (1)  | А                                                         | А           | А             | Α           | А      | Α                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0001                 | Α                                                         | Α           | Α             | Α           | Α      | Α                   | Α                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0010                 | Α                                                         | Α           | Α             | Α           | А      | Α                   | Α                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0011                 | D                                                         | А           | А             | А           | А      | А                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0100                 | D                                                         | D           | А             | А           | А      | А                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0101                 | D                                                         | D           | D             | Α           | А      | Α                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0110                 | D                                                         | D           | D             | D           | Α      | Α                   | Α                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0111 <b>(1)</b>      | D                                                         | D           | D             | D           | D      | А                   | А                  | Α                  | Α           | Α       | Α       | Α      | A           |

|              | 1000                 | D                                                         | D           | D             | D           | D      | D                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 1001                 | D                                                         | D           | D             | D           | D      | D                   | D                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              |                      |                                                           |             | -             | D           | D      | D                   | D                  | D                  | Α           | Α       | Α       | Α      | Α           |

|              | 1010                 | D                                                         | D           | D             | 5           |        |                     | -                  | D                  | D           | Α       | •       | •      | Α           |

|              | 1010<br>1011         | D<br>D                                                    | D<br>D      | D             | D           | D      | D                   | D                  | U                  | _           | А       | Α       | Α      | A           |

|              |                      |                                                           |             |               |             | D<br>D | D<br>D              | D                  | D                  | D           | D       | A       | A<br>A | A           |

|              | 1011                 | D                                                         | D<br>D<br>D | D<br>D<br>D   | D<br>D<br>D | D<br>D | D<br>D              | D<br>D             | D<br>D             | D<br>D      | D<br>D  | A<br>D  | A<br>A | A<br>A      |

|              | 1011<br>1100         | D<br>D                                                    | D<br>D      | D<br>D        | D<br>D      | D      | D                   | D                  | D                  | D<br>D<br>D | D       | Α       | Α      | A<br>A<br>A |

|              | 1011<br>1100<br>1101 | D<br>D<br>D                                               | D<br>D<br>D | D<br>D<br>D   | D<br>D<br>D | D<br>D | D<br>D              | D<br>D             | D<br>D             | D<br>D      | D<br>D  | A<br>D  | A<br>A |             |

### REGISTER 19-2: ADCON1: A/D CONTROL REGISTER 1

**Note 1:** The POR value of the PCFG bits depends on the value of the PBADEN Configuration bit. When PBADEN = 1, PCFG<3:0> = 0000; when PBADEN = 0, PCFG<3:0> = 0111.

2: AN5 through AN7 are available only in PIC18F4X20 devices.

#### REGISTER 23-4: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| R/P-1                                                                                                                                           | U-0                                                                                                                                                   | U-0                            | U-0             | U-0               | U-0              | R/P-1        | R/P-1       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|-------------------|------------------|--------------|-------------|--|--|

| MCLRE                                                                                                                                           | _                                                                                                                                                     | —                              | —               | —                 | —                | PBAD         | CCP2MX      |  |  |

| bit 7                                                                                                                                           |                                                                                                                                                       |                                |                 |                   |                  |              | bit (       |  |  |

| Logondu                                                                                                                                         |                                                                                                                                                       |                                |                 |                   |                  |              |             |  |  |

| Legend:<br>R = Readat                                                                                                                           | ole bit                                                                                                                                               | P = Program                    | nable bit       | U = Unimpler      | nented bit, read | as '0'       |             |  |  |

| R = Readable bitP = Programmable bitU = Unimplemented bit, read as '0'-n = Value when device is unprogrammedu = Unchanged from programmed state |                                                                                                                                                       |                                |                 |                   |                  |              |             |  |  |

| bit 6-2                                                                                                                                         | $0 = \overline{\text{MCLR}}$ dis                                                                                                                      |                                | out is enabled  |                   | es only (PIC18   | F4X20)       |             |  |  |

|                                                                                                                                                 |                                                                                                                                                       | enabled; RE3<br>abled; RE3 inp |                 |                   | es only (PIC18   | F4X20)       |             |  |  |

| bit 1                                                                                                                                           |                                                                                                                                                       |                                | bit (Affects AD | CON1 Reset        | state. ADCON1    | controls POR | TB<4:0> pin |  |  |