Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4220-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

## TABLE 1-3: PIC18F4220/4320 PINOUT I/O DESCRIPTIONS

| Din Nama                                            | Pi               | n Numb                          | ber     | Pin                | Buffer                              | Description                                                                                                                                                                                                             |

|-----------------------------------------------------|------------------|---------------------------------|---------|--------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                            | PDIP             | TQFP                            | QFN     | Туре               | Туре                                | Description                                                                                                                                                                                                             |

| MC <u>LR</u> /Vpp/RE3<br>MCLR<br>Vpp                | 1                | 18                              | 18      | I<br>P             | ST                                  | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.<br>Programming voltage input.                                                     |

| RE3                                                 |                  |                                 |         | , i                | ST                                  | Digital input.                                                                                                                                                                                                          |

| OSC1/CLKI/RA7<br>OSC1<br>CLKI                       | 13               | 30                              | 32      |                    | ST<br>CMOS                          | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode, CMOS otherwise.<br>External clock source input. Always associated with |

| RA7                                                 |                  |                                 |         | I/O                | TTL                                 | pin function OSC1. (See related OSC1/CLKI,<br>OSC2/CLKO pins.)<br>General purpose I/O pin.                                                                                                                              |

| OSC2/CLKO/RA6<br>OSC2                               | 14               | 31                              | 33      | 0                  | _                                   | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonator                                                                                                                      |

| CLKO                                                |                  |                                 |         | ο                  | _                                   | in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKO which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate                                                                          |

| RA6                                                 |                  |                                 |         | I/O                | TTL                                 | General purpose I/O pin.                                                                                                                                                                                                |

| RA0/AN0<br>RA0                                      | 2                | 19                              | 19      | I/O                | TTL                                 | PORTA is a bidirectional I/O port.<br>Digital I/O.                                                                                                                                                                      |

| AN0                                                 |                  |                                 |         | I                  | Analog                              | Analog input 0.                                                                                                                                                                                                         |

| RA1/AN1<br>RA1<br>AN1                               | 3                | 20                              | 20      | I/O<br>I           | TTL<br>Analog                       | Digital I/O.<br>Analog input 1.                                                                                                                                                                                         |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4                | 21                              | 21      | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog   | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (low) input.<br>Comparator reference voltage output.                                                                                                           |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                | 5                | 22                              | 22      | I/O<br>I<br>I      | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (high) input.                                                                                                                                                  |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT            | 6                | 23                              | 23      | I/O<br>I<br>O      | ST/OD<br>ST                         | Digital I/O. Open drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                                                                              |

| RA5/AN4/SS/LVDIN/                                   | 7                | 24                              | 24      |                    |                                     |                                                                                                                                                                                                                         |

| C2OUT<br>RA5<br><u>AN4</u><br>SS<br>LVDIN<br>C2OUT  |                  |                                 |         | I/O<br>I<br>I<br>O | TTL<br>Analog<br>TTL<br>Analog<br>— | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Low-Voltage Detect input.<br>Comparator 2 output.                                                                                                         |

| RA6                                                 |                  |                                 |         |                    |                                     | See the OSC2/CLKO/RA6 pin.                                                                                                                                                                                              |

| RA7                                                 |                  |                                 |         |                    |                                     | See the OSC1/CLKI/RA7 pin.                                                                                                                                                                                              |

| O = Outp                                            | nitt Trig<br>out | tible inp<br>ger inp<br>(no dio | ut with |                    | 8 levels                            | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                                                                        |

OD = Open-drain (no diode to VDD)

**Note 1:** Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

| Pin Name                       | Pi        | n Numl               | ber          | Pin           | Buffer              | Description                                                                                                                  |

|--------------------------------|-----------|----------------------|--------------|---------------|---------------------|------------------------------------------------------------------------------------------------------------------------------|

|                                | PDIP      | TQFP                 | QFN          | Туре          | Туре                | Description                                                                                                                  |

| RE0/AN5/RD                     | 8         | 25                   | 25           |               |                     | PORTE is a bidirectional I/O port.                                                                                           |

| RE0<br>AN5<br>RD               |           |                      |              | I/O<br>I<br>I | ST<br>Analog<br>TTL | Digital I/O.<br>Analog input 5.<br>Read control for Parallel Slave Port<br>(see also WR and CS pins).                        |

| RE1/AN6/WR<br>RE1<br>AN6<br>WR | 9         | 26                   | 26           | I/O<br>I<br>I | ST<br>Analog<br>TTL | Digital I/O.<br>Analog input 6.<br>Write <u>control for</u> Parallel Slave Port<br>(see CS and RD pins).                     |

| RE2/AN7/CS<br>RE2<br>AN7<br>CS | 10        | 27                   | 27           | I/O<br>I<br>I | ST<br>Analog<br>TTL | Digital I/O.<br>Analog input 7.<br>Chip select c <u>ont</u> rol fo <u>r P</u> arallel Slave Port<br>(see related RD and WR). |

| RE3                            | 1         | 18                   | 18           |               | _                   | See MCLR/VPP/RE3 pin.                                                                                                        |

| Vss                            | 12,<br>31 | 6, 29                | 6, 30,<br>31 | Ρ             |                     | Ground reference for logic and I/O pins.                                                                                     |

| Vdd                            | 11, 32    | 7, 28                | 7, 8<br>29   | Ρ             |                     | Positive supply for logic and I/O pins.                                                                                      |

| NC                             |           |                      | 13,<br>28    | NC            | NC                  | No connect.                                                                                                                  |

| Legend: TTL = TTL<br>ST = Schr |           | tible inp<br>ger inp |              | CMOS          | 6 levels            | CMOS = CMOS compatible input or output<br>I = Input                                                                          |

#### **TABLE 1-3**: PIC18F4220/4320 PINOUT I/O DESCRIPTIONS (CONTINUED)

O = Output

Ρ = Power

OD = Open-drain (no diode to VDD)

Note 1: Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

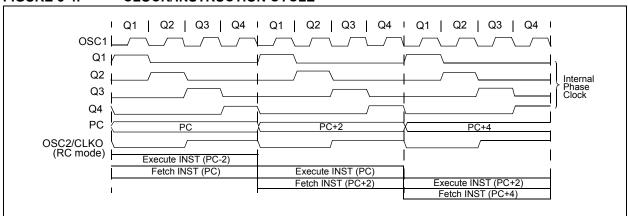

### 5.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the Program Counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 5-4.

# 5.6 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 5-2).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 5-4: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 5-2: INSTRUCTION PIPELINE FLOW

|          |                | TCY0        | TCY1      | TCY2      | TCY3      | TCY4        | TCY5          |

|----------|----------------|-------------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW | 55h            | Fetch 1     | Execute 1 |           |           |             |               |

| 2. MOVWE | PORTB          |             | Fetch 2   | Execute 2 |           | _           |               |

| 3. BRA   | SUB_1          |             |           | Fetch 3   | Execute 3 |             |               |

| 4. BSF   | PORTA, BIT3 (  | Forced NOP) |           |           | Fetch 4   | Flush (NOP) |               |

| 5. Instr | uction @ addre | ss SUB_1    |           |           |           | Fetch SUB_1 | Execute SUB_1 |

|          |                |             |           |           |           |             |               |

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### **REGISTER 6-1: EECON1: DATA EEPROM CONTROL REGISTER 1**

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | EEPGD: Flash Program or Data EEPROM Memory Select bit                                                                                                                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Access Flash program memory                                                                                                                                                                                                                                         |

|         | 0 = Access data EEPROM memory                                                                                                                                                                                                                                           |

| bit 6   | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                                                                                                                                                                                             |

|         | 1 = Access Configuration registers                                                                                                                                                                                                                                      |

|         | 0 = Access Flash program or data EEPROM memory                                                                                                                                                                                                                          |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                              |

| bit 4   | FREE: Flash Row Erase Enable bit                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by completion of erase operation)</li> <li>0 = Perform write-only</li> </ul>                                                                                              |

| L:1 0   |                                                                                                                                                                                                                                                                         |

| bit 3   | WRERR: EEPROM Error Flag bit <sup>(1)</sup>                                                                                                                                                                                                                             |

|         | <ul> <li>1 = A write operation was prematurely terminated (any Reset during self-timed programming)</li> <li>0 = The write operation completed normally</li> </ul>                                                                                                      |

| bit 2   | WREN: Write Enable bit                                                                                                                                                                                                                                                  |

|         | 1 = Allows write cycles to Flash program/data EEPROM                                                                                                                                                                                                                    |

|         | 0 = Inhibits write cycles to Flash program/data EEPROM                                                                                                                                                                                                                  |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete.<br/>The WR bit can only be set (not cleared) in software.)</li> </ul> |

|         | 0 = Write cycle completed                                                                                                                                                                                                                                               |

| bit 0   | RD: Read Control bit                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Initiates a memory read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1.)</li> </ul>                                                                           |

|         | 0 = Read completed                                                                                                                                                                                                                                                      |

| Note 1: | When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error                                                                                                                                                                          |

condition.

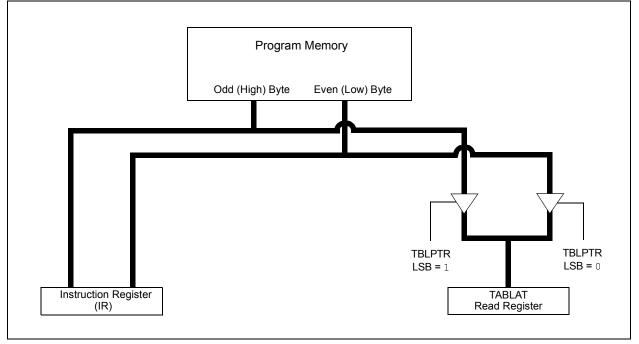

### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and place it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing a TBLRD instruction places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

# FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base             |

|-----------|---------|-----------------|---|---------------------------------------|

|           | MOVWF   | TBLPTRU         | ; | address of the word                   |

|           | MOVLW   | CODE_ADDR_HIGH  |   |                                       |

|           | MOVWF   | TBLPTRH         |   |                                       |

|           | MOVLW   | CODE ADDR LOW   |   |                                       |

|           | MOVWF   | TBLPTRL         |   |                                       |

| READ_WORD |         |                 |   |                                       |

|           | TBLRD*+ |                 | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD EVEN       |   |                                       |

|           | TBLRD*+ | _               | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD_ODD        |   |                                       |

|           |         |                 |   |                                       |

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY

|                |                |                          | - |                                                                            |

|----------------|----------------|--------------------------|---|----------------------------------------------------------------------------|

|                | MOVLW          | D'64                     | ; | number of bytes in erase block                                             |

|                | MOVWF          | COUNTER                  |   |                                                                            |

|                | MOVLW          | BUFFER_ADDR_HIGH         | ; | point to buffer                                                            |

|                | MOVWF          | FSROH                    |   |                                                                            |

|                | MOVLW          | BUFFER_ADDR_LOW          |   |                                                                            |

|                | MOVWF          | FSROL                    |   |                                                                            |

|                | MOVLW          |                          |   | Load TBLPTR with the base                                                  |

|                | MOVWF          | TBLPTRU                  | ; | address of the memory block                                                |

|                | MOVLW          | CODE_ADDR_HIGH           |   |                                                                            |

|                | MOVWF          | TBLPTRH                  |   | 6 LSB = 0                                                                  |

|                | MOVLW<br>MOVWF | CODE_ADDR_LOW<br>TBLPTRL | ' | 0 138 - 0                                                                  |

| READ BLOCK     | PIO V WE       |                          |   |                                                                            |

|                | TBLRD*+        | F                        | ; | read into TABLAT, and inc                                                  |

|                | MOVFW          | TABLAT                   |   | get data                                                                   |

|                |                | POSTINCO                 | ; | store data and increment FSR0                                              |

|                | DECFSZ         | COUNTER                  | ; | done?                                                                      |

|                | GOTO           | READ_BLOCK               | ; | repeat                                                                     |

| MODIFY_WORD    |                |                          |   |                                                                            |

|                | MOVLW          | DATA_ADDR_HIGH           | ; | point to buffer                                                            |

|                | MOVWF          | FSROH                    |   |                                                                            |

|                | MOVLW          | DATA_ADDR_LOW            |   |                                                                            |

|                | MOVWF          | FSROL                    |   |                                                                            |

|                | MOVLW          | NEW_DATA_LOW             | ; | update buffer word and increment FSR0                                      |

|                | MOVWF          | POSTINCO                 |   | undate huffer word                                                         |

|                | MOVLW<br>MOVWF | NEW_DATA_HIGH<br>INDF0   | ' | update buffer word                                                         |

| ERASE BLOCK    | MOVWE          | INDEO                    |   |                                                                            |

| BIGIOD_DECOR   | MOVLW          | CODE ADDR UPPER          | ; | load TBLPTR with the base                                                  |

|                | MOVWF          | TBLPTRU                  |   | address of the memory block                                                |

|                | MOVLW          | CODE ADDR HIGH           |   | 2                                                                          |

|                | MOVWF          | TBLPTRH                  |   |                                                                            |

|                | MOVLW          | CODE_ADDR_LOW            | ; | 6 LSB = 0                                                                  |

|                | MOVWF          | TBLPTRL                  |   |                                                                            |

|                | BCF            | EECON1,CFGS              |   | point to PROG/EEPROM memory                                                |

|                | BSF            | EECON1, EEPGD            | ; | point to Flash program memory                                              |

|                | BSF            | EECON1,WREN              |   | enable write to memory                                                     |

|                | BSF            | EECON1, FREE             |   | enable Row Erase operation                                                 |

|                | BCF            | INTCON, GIE              |   | disable interrupts                                                         |

|                | MOVLW          | 55h                      |   | Required sequence                                                          |

|                | MOVWF          | EECON2                   | ; | write 55H                                                                  |

|                | MOVLW<br>MOVWF | AAh<br>EECON2            |   | write AAH                                                                  |

|                | BSF            | EECON1,WR                |   | start erase (CPU stall)                                                    |

|                | NOP            | 220001,000               | ' | Start Stable (of Start)                                                    |

|                | BSF            | INTCON, GIE              | ; | re-enable interrupts                                                       |

| WRITE BUFFER E |                | ,                        | , | · · · · · · · · · · · · · · · · · · ·                                      |

|                | MOVLW          | 8                        | ; | number of write buffer groups of 8 bytes                                   |

|                | MOVWF          | COUNTER_HI               |   |                                                                            |

|                | MOVLW          | BUFFER_ADDR_HIGH         | ; | point to buffer                                                            |

|                | MOVWF          | FSROH                    |   |                                                                            |

|                | MOVLW          | BUFFER_ADDR_LOW          |   |                                                                            |

|                | MOVWF          | FSROL                    |   |                                                                            |

| PROGRAM_LOOP   |                |                          |   |                                                                            |

|                | MOVLW          | 8                        | ; | number of bytes in holding register                                        |

|                | MOVWF          | COUNTER                  |   |                                                                            |

| WRITE_WORD_TO_ | -              | DOGUINCO                 | - | got low but oof buffor data and increment DODO                             |

|                | MOVFW<br>MOVWF | POSTINCO<br>TABLAT       |   | get low byte of buffer data and increment FSR0 present data to table latch |

|                | TBLWT+'        |                          |   | short write                                                                |

|                | TTANT L.       |                          |   | to internal TBLWT holding register, increment                              |

|                |                |                          | , | TBLPTR                                                                     |

|                | DECFSZ         | COUNTER                  | ; | loop until buffers are full                                                |

|                | GOTO           | WRITE WORD TO HREGS      | · |                                                                            |

|                |                |                          |   |                                                                            |

# PIC18F2220/2320/4220/4320

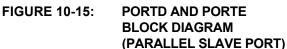

### **10.6 Parallel Slave Port**

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | PIC18F4X20 devices.                          |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 10-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation, as long as the Enhanced CCP module is not operating in dual output or quad output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit, PSPMODE, enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PFCG3:PFCG0 (ADCON1<3:0>) must also be set to '1010'.

A write to the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is set. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  lines are detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP; when this happens, the IBF and OBF bits can be polled and the appropriate action taken.

The timing for the control signals in Write and Read modes is shown in Figure 10-16 and Figure 10-17, respectively.

| Name    | Bit 7                | Bit 6          | Bit 5        | Bit 4         | Bit 3         | Bit 2    | Bit 1  | Bit 0  | Value<br>POR, B | -   | all o | e on<br>other<br>sets |

|---------|----------------------|----------------|--------------|---------------|---------------|----------|--------|--------|-----------------|-----|-------|-----------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL      | TMR0IE       | INT0IE        | RBIE          | TMR0IF   | INT0IF | RBIF   | 0000 0          | 00x | 0000  | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF           | RCIF         | TXIF          | SSPIF         | CCP1IF   | TMR2IF | TMR1IF | 0000 0          | 000 | 0000  | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE           | RCIE         | TXIE          | SSPIE         | CCP1IE   | TMR2IE | TMR1IE | 0000 0          | 000 | 0000  | 0000                  |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP           | RCIP         | TXIP          | SSPIP         | CCP1IP   | TMR2IP | TMR1IP | 1111 1          | 111 | 1111  | 1111                  |

| TRISC   | PORTC Da             | ata Direction  | Register     |               |               |          |        |        | 1111 1          | 111 | 1111  | 1111                  |

| TMR1L   | Holding Re           | egister for th | e Least Sigr | nificant Byte | of the 16-bit | TMR1 Reg | gister |        | XXXX X          | xxx | uuuu  | uuuu                  |

| TMR1H   | Holding Re           | egister for th | e Most Sign  | ificant Byte  | of the 16-bit | TMR1 Reg | ister  |        | XXXX X          | xxx | uuuu  | uuuu                  |

| T1CON   | RD16                 | T1RUN          | T1CKPS1      | T1CKPS0       | T10SCEN       | T1SYNC   | TMR1CS | TMR10N | 0000 0          | 000 | uuuu  | uuuu                  |

| CCPR1L  | Capture/C            | ompare/PW      | M Register 2 | I (LSB)       |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCPR1H  | Capture/C            | ompare/PW      | M Register 2 | I (MSB)       |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCP1CON | _                    | _              | DC1B1        | DC1B0         | CCP1M3        | CCP1M2   | CCP1M1 | CCP1M0 | 00 0            | 000 | 00    | 0000                  |

| CCPR2L  | Capture/C            | ompare/PW      | M Register 2 | 2 (LSB)       |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCPR2H  | Capture/C            | ompare/PW      | M Register 2 | 2 (MSB)       |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCP2CON | _                    | _              | DC2B1        | DC2B0         | CCP2M3        | CCP2M2   | CCP2M1 | CCP2M0 | 00 0            | 000 | 00    | 0000                  |

| PIR2    | OSCFIF               | CMIF           | _            | EEIF          | BCLIF         | LVDIF    | TMR3IF | CCP2IF | 00-0 0          | 000 | 00-0  | 0000                  |

| PIE2    | OSCFIE               | CMIE           | _            | EEIE          | BCLIE         | LVDIE    | TMR3IE | CCP2IE | 00-0 0          | 000 | 00-0  | 0000                  |

| IPR2    | OSCFIP               | CMIP           | _            | EEIP          | BCLIP         | LVDIP    | TMR3IP | CCP2IP | 11-1 1          | 111 | 11-1  | 1111                  |

| TMR3L   | Holding Re           | egister for th | e Least Sigr | nificant Byte | of the 16-bit | TMR3 Reg | gister |        | XXXX X          | xxx | uuuu  | uuuu                  |

| TMR3H   | Holding Re           | egister for th | e Most Sign  | ificant Byte  | of the 16-bit | TMR3 Reg | ister  |        | XXXX X          | xxx | uuuu  | uuuu                  |

| T3CON   | RD16                 | T3CCP2         | T3CKPS1      | T3CKPS0       | T3CCP1        | T3SYNC   | TMR3CS | TMR3ON | 0000 0          | 000 | uuuu  | uuuu                  |

#### TABLE 15-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: These bits are reserved on the PIC18F2X20 devices; always maintain these bits clear.

# 16.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

| Note: | The EC              | CP (Enha | ince | d Cap | ture/ Compa | are/ |  |  |

|-------|---------------------|----------|------|-------|-------------|------|--|--|

|       | PWM)                | module   | is   | only  | available   | on   |  |  |

|       | PIC18F4X20 devices. |          |      |       |             |      |  |  |

In 40 and 44-pin devices, the CCP1 module is implemented as a standard CCP module with enhanced PWM capabilities. Operation of the Capture, Compare and standard single output PWM modes is described in **Section 15.0 "Capture/Compare/PWM (CCP) Modules"**. Discussion in that section relating to PWM frequency and duty cycle also apply to the enhanced PWM mode. The ECCP module differs from the CCP with the addition of an enhanced PWM mode which allows for 2 or 4 output channels, user-selectable polarity, dead band control and automatic shutdown and restart. These features are discussed in detail in **Section 16.4 "Enhanced PWM Mode"**.

The control register for CCP1 is shown in Register 16-1. It differs from the CCP1CON register of PIC18F2X20 devices in that the two Most Significant bits are implemented to control enhanced PWM functionality.

# REGISTER 16-1: CCP1CON: ECCP CONTROL REGISTER (40/44-PIN DEVICES)

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0  | R/W-0              | R/W-0  |  |

|----------------------------------------------------------------------|-------|------------------|-------|----------------------|--------|--------------------|--------|--|

| P1M1                                                                 | P1M0  | DC1B1            | DC1B0 | CCP1M3               | CCP1M2 | CCP1M1             | CCP1M0 |  |

| bit 7                                                                |       | •                |       | •                    |        |                    | bit 0  |  |

|                                                                      |       |                  |       |                      |        |                    |        |  |

| Legend:                                                              |       |                  |       |                      |        |                    |        |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                      |        |                    |        |  |

| -n = Value at POR                                                    |       | '1' = Bit is set |       | '0' = Bit is cleared |        | x = Bit is unknown |        |  |

|                                                                      |       |                  |       |                      |        |                    |        |  |

bit 7-6 P1M1:P1M0: PWM Output Configuration bits If CCP1M3:CCP1M2 = 00, 01, 10 (Capture, Compare or disabled): xx = P1A assigned as Capture/Compare input; P1B, P1C, P1D assigned as port pins If CCP1M3:CCP1M2 = 11 (PWM modes): 00 = Single output: P1A modulated; P1B, P1C, P1D assigned as port pins 01 = Full-bridge output forward: P1D modulated; P1A active; P1B, P1C inactive 10 = Half-bridge output: P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins 11 = Full-bridge output reverse: P1B modulated; P1C active; P1A, P1D inactive bit 5-4 DC1B1:DC1B0: PWM Duty Cycle Least Significant bits Capture mode: Unused. Compare mode: Unused. PWM mode: These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR1L.

# 16.4 Enhanced PWM Mode

The Enhanced PWM mode provides additional PWM output options for a broader range of control applications. The module is an upwardly compatible version of the standard CCP module and offers up to four outputs, designated P1A through P1D. Users are also able to select the polarity of the signal (either active-high or active-low). The module's output mode and polarity are configured by setting the P1M1:P1M0 and CCP1M3:CCP1M0 bits of the CCP1CON register (CCP1CON<7:6> and CCP1CON<3:0>, respectively).

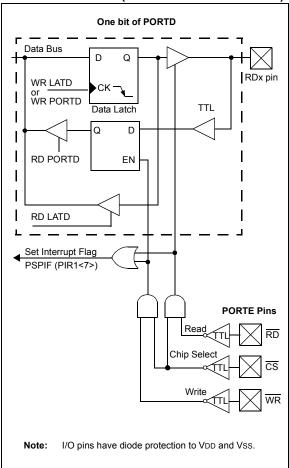

Figure 16-1 shows a simplified block diagram of PWM operation. All control registers are double-buffered and are loaded at the beginning of a new PWM cycle (the period boundary when Timer2 resets) in order to prevent glitches on any of the outputs. The exception is the PWM Delay register, ECCP1DEL, which is loaded at either the duty cycle boundary or the boundary period (whichever comes first). Because of the buffering, the module waits until the assigned timer resets instead of starting immediately. This means that enhanced PWM

waveforms do not exactly match the standard PWM waveforms but are instead offset by one full instruction cycle (4 Tosc).

As before, the user must manually configure the appropriate TRISD bits for output.

#### 16.4.1 PWM OUTPUT CONFIGURATIONS

The P1M1:P1M0 bits in the CCP1CON register allow one of four configurations:

- Single Output

- Half-Bridge Output

- Full-Bridge Output, Forward mode

- Full-Bridge Output, Reverse mode

The Single Output mode is the Standard PWM mode discussed in **Section 15.5** "**PWM Mode**". The Half-Bridge and Full-Bridge Output modes are covered in detail in the sections that follow.

The general relationship of the outputs in all configurations is summarized in Figure 16-2.

#### FIGURE 16-1: SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODULE

# PIC18F2220/2320/4220/4320

| CCP1CO<br><7:6>                         | N SIGNAL                           | Duty<br>ycle ──►<br>───── Period ─── | PR2+1 |

|-----------------------------------------|------------------------------------|--------------------------------------|-------|

| 00 (Single Ou                           | tput) P1A Modulated                | <br>Delay <sup>(1)</sup>             |       |

| LO <b>(Half-Brid</b>                    | P1A Modulated<br>ge) P1B Modulated |                                      |       |

| (Eull-Brid                              | P1A Active                         |                                      |       |

| (Full-Bridge,<br><sup>D1</sup> Forward) | d)<br>P1C Inactive                 |                                      |       |

|                                         | P1D Modulated<br>P1A Inactive      |                                      |       |

| 11 (Full-Brid<br>Reverse                |                                    |                                      |       |

|                                         | P1D Inactive                       |                                      |       |

#### FIGURE 16-2: PWM OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

#### FIGURE 16-3: PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

| CCP1CON                      | SIGNAL        | 0 Duty               |                      | PR2+1       |

|------------------------------|---------------|----------------------|----------------------|-------------|

| <7:6>                        |               | Cycl                 | e Period ——          | <b>&gt;</b> |

| 00 (Single Output)           | P1A Modulated |                      |                      |             |

|                              | P1A Modulated |                      |                      |             |

| 10 (Half-Bridge)             | P1B Modulated | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> |             |

|                              | P1A Active    |                      | 1<br>1<br>1          |             |

| (Full-Bridge,                | P1B Inactive  | $\equiv$             |                      | <u> </u>    |

| <sup>01</sup> Forward)       | P1C Inactive  | <u> </u>             |                      |             |

|                              | P1D Modulated |                      |                      |             |

|                              | P1A Inactive  |                      | 1<br>1<br>1          | 1<br>1<br>  |

| 11 (Full-Bridge,<br>Reverse) | P1B Modulated |                      | <br>                 |             |

|                              | P1C Active    | _                    |                      |             |

|                              | P1D Inactive  |                      | 1<br>                |             |

|                              |               | ;                    | I<br>I               | 1           |

#### **Relationships:**

• Period = 4 \* Tosc \* (PR2 + 1) \* (TMR2 Prescale Value)

• Duty Cycle = Tosc \* (CCPR1L<7:0>:CCP1CON<5:4>) \* (TMR2 Prescale Value)

• Delay = 4 \* Tosc \* (PWM1CON<6:0>)

Note 1: Dead band delay is programmed using the PWM1CON register (see Section 16.4.4 "Programmable Dead-Band Delay").

#### 17.3.3 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI must have TRISC<4> bit cleared

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

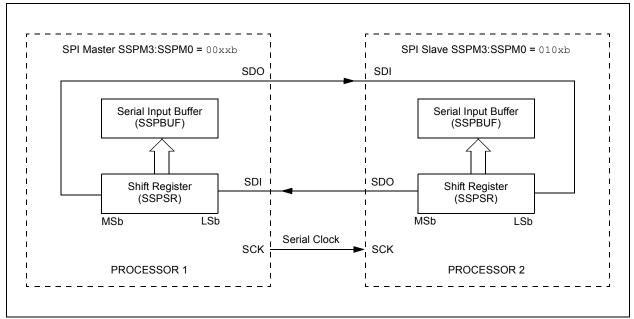

# 17.3.4 TYPICAL CONNECTION

Register 17-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 17-2: SPI MASTER/SLAVE CONNECTION

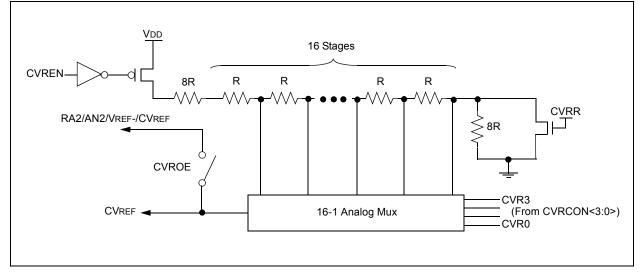

# FIGURE 21-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

# 21.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 21-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from VDD; therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in **Section 26.0 "Electrical Characteristics"**.

# 21.3 Operation in Power-Managed Modes

The contents of the CVRCON register are not affected by entry to or exit from power-managed modes. To minimize current consumption in power-managed modes, the voltage reference module should be disabled; however, this can cause an interrupt from the comparators so the comparator interrupt should also be disabled while the CVRCON register is being modified.

# 21.4 Effects of a Reset

A device Reset disables the voltage reference by clearing the CVRCON register. This also disconnects the reference from the RA2 pin, selects the high-voltage range and selects the lowest voltage tap from the resistor divider.

# 21.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be output using the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto the RA2 pin, with an input signal present, will increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, an external buffer must be used on the voltage reference output for external connections to VREF. Figure 21-2 shows an example buffering technique.

# PIC18F2220/2320/4220/4320

#### REGISTER 23-6: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

|            |                    |                                                 |               |                    | -                  |            |       |  |

|------------|--------------------|-------------------------------------------------|---------------|--------------------|--------------------|------------|-------|--|

| U-0        | U-0                | U-0                                             | U-0           | R/C-1              | R/C-1              | R/C-1      | R/C-1 |  |

| _          |                    |                                                 | _             | CP3 <sup>(1)</sup> | CP2 <sup>(1)</sup> | CP1        | CP0   |  |

| bit 7      |                    |                                                 |               |                    |                    |            | bit 0 |  |

|            |                    |                                                 |               |                    |                    |            |       |  |

| Legend:    |                    |                                                 |               |                    |                    |            |       |  |

| R = Reada  | ble bit            | C = Clearable                                   | bit           | U = Unimpler       | mented bit, read   | as '0'     |       |  |

| -n = Value | when device is unp | programmed                                      |               | u = Unchang        | ed from program    | nmed state |       |  |

|            |                    |                                                 |               |                    |                    |            |       |  |

| bit 7-4    |                    | ted: Read as '                                  | )'            |                    |                    |            |       |  |

| bit 3      | CP3: Code Pr       | otection bit <sup>(1)</sup>                     |               |                    |                    |            |       |  |

|            | (                  | 1 = Block 3 (001800-001FFFh) not code-protected |               |                    |                    |            |       |  |

|            |                    | 01800-001FFF                                    | h) code-prote | ected              |                    |            |       |  |

| bit 2      | CP2: Code Pr       | otection bit <sup>(1)</sup>                     |               |                    |                    |            |       |  |

|            | •                  | 1 = Block 2 (001000-0017FFh) not code-protected |               |                    |                    |            |       |  |

|            | 0 = Block 2 (0     | 01000-0017FF                                    | h) code-prote | ected              |                    |            |       |  |

| bit 1      | CP1: Code Pr       |                                                 |               |                    |                    |            |       |  |

|            |                    | 00800-000FFF                                    |               |                    |                    |            |       |  |

|            | ,                  | 00800-000FFF                                    | h) code-prote | ected              |                    |            |       |  |

| bit 0      | CP0: Code Pr       |                                                 |               |                    |                    |            |       |  |

|            |                    | 00200-0007FF                                    |               |                    |                    |            |       |  |

|            | 0 = Block 0 (0     | 00200-0007FF                                    | h) code-prote | ected              |                    |            |       |  |

|            |                    |                                                 |               |                    |                    |            |       |  |

Note 1: Unimplemented in PIC18FX220 devices; maintain this bit set.

# REGISTER 23-7: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1       | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|-------------|-------|-----|-----|-----|-----|-----|-----|--|

| CPD         | CPB   | —   | —   | —   | —   | —   | —   |  |

| bit 7 bit 0 |       |     |     |     |     |     |     |  |

| Legend:                   |                   |                                     |

|---------------------------|-------------------|-------------------------------------|

| R = Readable bit          | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is | unprogrammed      | u = Unchanged from programmed state |

| bit 7   | CPD: Data EEPROM Code Protection bit                  |

|---------|-------------------------------------------------------|

|         | 1 = Data EEPROM is not code-protected                 |

|         | 0 = Data EEPROM is code-protected                     |

| bit 6   | CPB: Boot Block Code Protection bit                   |

|         | 1 = Boot block (000000-0001FFh) is not code-protected |

|         | 0 = Boot block (000000-0001FFh) is code-protected     |

| bit 5-0 | Unimplemented: Read as '0'                            |

#### 23.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

#### 23.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

# 23.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code-protected.

# 23.7 In-Circuit Serial Programming

PIC18F2X20/4X20 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed (see Table 23-5).

# 23.8 In-Circuit Debugger

When the DEBUG bit in Configuration register, CONFIG4L, is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 23-4 shows which resources are required by the background debugger.

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, VSS, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

# 23.9 Low-Voltage ICSP Programming

The LVP bit in Configuration Register 4L (CONFIG4L<2>) enables Low-Voltage ICSP Programming (LVP). When LVP is enabled, the microcontroller can be programmed without requiring high voltage being applied to the MCLR/VPP pin, but the RB5/PGM pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

LVP is enabled in erased devices.

While programming using LVP, VDD is applied to the MCLR/VPP pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

| Note 1: | High-voltage programming is always<br>available, regardless of the state of the<br>LVP bit or the PGM pin, by applying VIHH |

|---------|-----------------------------------------------------------------------------------------------------------------------------|

|         | to the MCLR pin.                                                                                                            |

| •       |                                                                                                                             |

- 2: When Low-Voltage Programming is enabled, the RB5 pin can no longer be used as a general purpose I/O pin.

- **3:** When LVP is enabled, externally pull the PGM pin to Vss to allow normal program execution.

If Low-Voltage ICSP Programming mode will not be used, the LVP bit can be cleared and RB5/PGM becomes available as the digital I/O pin, RB5. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the MCLR/ VPP pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased using either a block erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a block erase is required. If a block erase is to be performed when using Low-Voltage Programming, the device must be supplied with VDD of 4.5V to 5.5V.

TABLE 23-5: ICSP™/ICD CONNECTIONS

| Signal | Pin  | Notes                                              |

|--------|------|----------------------------------------------------|

| PGD    | RB7  |                                                    |

| PGC    | RB6  |                                                    |

| MCLR   | MCLR | May require isolation from<br>application circuits |

| Vdd    | Vdd  |                                                    |

| Vss    | Vss  |                                                    |

| PGM    | RB5  | Pull RB5 low if LVP is enabled                     |

# PIC18F2220/2320/4220/4320

| DEC         | FSZ                                                  | Decreme                                                                                                                                                 | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |  |  |  |  |  |

|-------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|--|--|

| Synt        | ax:                                                  | [label] [                                                                                                                                               | [ <i>label</i> ] DECFSZ f[,d[,a]]                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |  |  |  |  |  |

| Ope         | rands:                                               | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |  |  |

| Ope         | ration:                                              | (f) – 1 $\rightarrow$ oskip if res                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |  |  |

| Statu       | us Affected:                                         | None                                                                                                                                                    | •                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |  |  |  |  |  |

| Enco        | oding:                                               | 0010                                                                                                                                                    | 11da ffi                                                                                                                                                                                                                                                                                                                                                                                                                                            | ff ffff                |  |  |  |  |  |

| Desc        | cription:                                            | decremen<br>is placed i<br>is placed l<br>(default).<br>If the resu<br>tion which<br>carded an<br>instead, m<br>instruction<br>Bank will l<br>the BSR v | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result<br>is placed back in register 'f'<br>(default).<br>If the result is '0', the next instruc-<br>tion which is already fetched is dis-<br>carded and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the |                        |  |  |  |  |  |

| 14/0        | de .                                                 | BSR value                                                                                                                                               | be selected a<br>e (default).                                                                                                                                                                                                                                                                                                                                                                                                                       | is per the             |  |  |  |  |  |

| Word        |                                                      | 1                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |  |  |

| Cycl<br>Q C | cs.<br>Cycle Activity                                | by                                                                                                                                                      | ycles if skip a 2-word ins                                                                                                                                                                                                                                                                                                                                                                                                                          | and followed truction. |  |  |  |  |  |

|             | Q1                                                   | Q2                                                                                                                                                      | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q4                     |  |  |  |  |  |

|             | Decode                                               | Read<br>register 'f'                                                                                                                                    | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                     | Write to destination   |  |  |  |  |  |

| lf sk       | kip:                                                 |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |  |  |

| 1           | Q1                                                   | Q2                                                                                                                                                      | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q4                     |  |  |  |  |  |