Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 4KB (2K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 13x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4220-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.8 Look-up Tables

Look-up tables are implemented two ways:

- Computed GOTO

- Table Reads

#### 5.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-4.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW  $0 \times nn$  instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW  $0 \times nn$  instructions that returns the value  $0 \times nn$  to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSB = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-4: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVFW  | OFFSET |

|-------|--------|--------|

|       | CALL   | TABLE  |

| ORG   | 0xnn00 |        |

| TABLE | ADDWF  | PCL    |

|       | RETLW  | 0xnn   |

|       | RETLW  | 0xnn   |

|       | RETLW  | 0xnn   |

|       | •      |        |

|       | •      |        |

|       | •      |        |

|       |        |        |

### 5.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory, one byte at a time.

The Table Read/Table Write operation is discussed further in Section 6.1 "Table Reads and Table Writes".

## 5.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 5-6 shows the data memory organization for the PIC18F2X20/4X20 devices.

The data memory map is divided into as many as 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits of the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (FFFh) and extend towards F80h. Any remaining space beyond the SFRs in the bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the data memory map without banking. See Section 5.12 "Indirect Addressing, INDF and FSR Registers" for indirect addressing details.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. **Section 5.10 "Access Bank"** provides a detailed description of the Access RAM.

#### 5.9.1 GENERAL PURPOSE REGISTER FILE

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

Data RAM is available for use as GPR registers by all instructions. The second half of Bank 15 (F80h to FFFh) contains SFRs. All other banks of data memory contain GPRs, starting with Bank 0.

Example 8-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in four registers, RES3:RES0.

#### EQUATION 8-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = |                                          |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | (ARG1L • ARG2L)                          |

### EXAMPLE 8-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

| MOVF   | ARG1L, W    |                    |

|--------|-------------|--------------------|

| MULWF  | ARG2L       | ; ARG1L * ARG2L -> |

|        |             | ; PRODH:PRODL      |

| MOVFF  | PRODH, RES1 | ;                  |

| MOVFF  | PRODL, RESO | ;                  |

| ;      |             |                    |

| MOVF   | ARG1H, W    |                    |

| MULWF  | ARG2H       | ; ARG1H * ARG2H -> |

|        |             | ; PRODH:PRODL      |

| MOVFF  | PRODH, RES3 | ;                  |

| MOVFF  | PRODL, RES2 | ;                  |

| ;      |             |                    |

| MOVF   | ARG1L, W    |                    |

| MULWF  | ARG2H       | ; ARG1L * ARG2H -> |

|        |             | ; PRODH:PRODL      |

|        | PRODL, W    |                    |

|        | RES1, F     |                    |

|        | PRODH, W    | -                  |

|        | RES2, F     | ;                  |

| -      | WREG        | ;                  |

| ADDWFC | RES3, F     | ;                  |

| ;      |             |                    |

|        | ARG1H, W    |                    |

| MULWF  | ARG2L       | ; ARG1H * ARG2L -> |

|        |             | ; PRODH:PRODL      |

|        | PRODL, W    | -                  |

|        | RES1, F     |                    |

|        | PRODH, W    | =                  |

|        | RES2, F     |                    |

| CLRF   |             | ;                  |

| ADDWFC | RES3, F     | ;                  |

Example 8-4 shows the sequence to do a 16 x 16 signed multiply. Equation 8-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs' Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EQUATION 8-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

#### RES3:RES0

- $= ARG1H:ARG1L \bullet ARG2H:ARG2L$

- =  $(ARG1H \bullet ARG2H \bullet 2^{16}) +$  $(ARG1H \bullet ARG2L \bullet 2^{8}) +$  $(ARG1L \bullet ARG2H^{2} 2^{8}) +$  $(ARG1L \bullet ARG2L) +$  $(-1 \bullet ARG2H < 7> \bullet ARG1H: ARG1L \bullet 2^{16}) +$  $(-1 \bullet ARG1H < 7> \bullet ARG2H: ARG2L \bullet 2^{16})$

#### EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|     | MOVF           | ARG1L, W    |                    |

|-----|----------------|-------------|--------------------|

|     | MULWF          | ARG2L       | ; ARG1L * ARG2L -> |

|     |                |             | ; PRODH:PRODL      |

|     | MOVEE          | PRODH, RES1 |                    |

|     | MOVFF<br>MOVFF | PRODL, RESO |                    |

|     | MOVEE          | PRODL, RESU | ;                  |

| ;   |                |             |                    |

|     |                | ARG1H, W    |                    |

|     | MULWF          | ARG2H       | ; ARG1H * ARG2H -> |

|     |                |             | ; PRODH:PRODL      |

|     | MOVFF          | PRODH, RES3 | ;                  |

|     | MOVFF          | PRODL, RES2 | ;                  |

| ;   |                |             |                    |

|     | MOVF           | ARG1L, W    |                    |

|     | MULWF          |             | ; ARG1L * ARG2H -> |

|     | PIOTIME        | ANGZII      |                    |

|     |                |             | ; PRODH:PRODL      |

|     | MOVF           | PRODL, W    | ;                  |

|     | ADDWF          | RES1, F     | ; Add cross        |

|     | MOVF           | PRODH, W    | ; products         |

|     | ADDWFC         | RES2, F     | ;                  |

|     | CLRF           | WREG        | ;                  |

|     | ADDWFC         | RES3, F     | ;                  |

| ;   |                | ,           |                    |

| '   | MOVE           | ARG1H, W    |                    |

|     |                |             | ;                  |

|     | MULWF          | ARG2L       | ; ARG1H * ARG2L -> |

|     |                |             | ; PRODH:PRODL      |

|     | MOVF           | PRODL, W    | ;                  |

|     |                | RES1, F     | ; Add cross        |

|     | MOVF           | PRODH, W    | ; products         |

|     | ADDWFC         | RES2, F     | ;                  |

|     | CLRF           | WREG        | ;                  |

|     | ADDWFC         | RES3, F     | ;                  |

| ;   |                |             |                    |

|     | BTESS          | ARG2H, 7    | ; ARG2H:ARG2L neg? |

|     | BRA            | SIGN ARG1   | ; no, check ARG1   |

|     |                | -           |                    |

|     |                | ARG1L, W    | ;                  |

|     | SUBWF          | RES2        | ;                  |

|     |                | ARG1H, W    | ;                  |

|     | SUBWFB         | RES3        |                    |

| ;   |                |             |                    |

| SIG | N_ARG1         |             |                    |

|     | BTFSS          | ARG1H, 7    | ; ARG1H:ARG1L neg? |

|     | BRA            | CONT CODE   | ; no, done         |

|     | MOVF           | ARG2L, W    | ;                  |

|     | SUBWF          | RES2        | ;                  |

|     | MOVF           | ARG2H, W    | ;                  |

|     | SUBWFB         |             | ,                  |

| Ι.  | SODWED         | U U U U U U |                    |

| ;   |                |             |                    |

|     | T_CODE         |             |                    |

|     | :              |             |                    |

| 1   |                |             |                    |

| R/W-1         | R/W-1                                      | U-0                                | R/W-0           | R/W-0            | U-0             | R/W-0              | R/W-0         |  |

|---------------|--------------------------------------------|------------------------------------|-----------------|------------------|-----------------|--------------------|---------------|--|

| INT2IP        | INT1IP                                     | —                                  | INT2IE          | INT1IE           |                 | INT2IF             | INT1IF        |  |

| bit 7         |                                            |                                    |                 |                  |                 |                    | bit (         |  |

|               |                                            |                                    |                 |                  |                 |                    |               |  |

| Legend:       |                                            |                                    |                 |                  |                 |                    |               |  |

| R = Readabl   | e bit                                      | W = Writable                       | bit             | •                | mented bit, rea | id as '0'          |               |  |

| -n = Value at | POR                                        | '1' = Bit is set                   |                 | '0' = Bit is cle | eared           | x = Bit is unkr    | nown          |  |

| bit 7         |                                            | External Interr                    | unt Driarity hi |                  |                 |                    |               |  |

|               | 1 = High prio                              | External Interro                   | upt Phonity bi  | L                |                 |                    |               |  |

|               | 0 = Low prior                              | -                                  |                 |                  |                 |                    |               |  |

| bit 6         | •                                          | External Interro                   | upt Priority bi | t                |                 |                    |               |  |

|               | 1 = High prio                              | ority                              |                 |                  |                 |                    |               |  |

|               | 0 = Low prior                              | rity                               |                 |                  |                 |                    |               |  |

| bit 5         | Unimplemen                                 | ted: Read as '                     | )'              |                  |                 |                    |               |  |

| bit 4         | INT2IE: INT2                               | External Interre                   | upt Enable bi   | t                |                 |                    |               |  |

|               |                                            | the INT2 extern                    |                 |                  |                 |                    |               |  |

|               |                                            | the INT2 exter                     | •               |                  |                 |                    |               |  |

| bit 3         | INT1IE: INT1 External Interrupt Enable bit |                                    |                 |                  |                 |                    |               |  |

|               |                                            | the INT1 extern<br>the INT1 extern |                 |                  |                 |                    |               |  |

| bit 2         |                                            | ted: Read as '                     | •               |                  |                 |                    |               |  |

| bit 1         | -                                          | External Interro                   |                 |                  |                 |                    |               |  |

|               |                                            | 2 external interr                  |                 | (must be clear   | ed in software  | N N                |               |  |

|               |                                            | 2 external interr                  |                 |                  |                 | /                  |               |  |

| bit 0         |                                            | External Interro                   | •               |                  |                 |                    |               |  |

|               |                                            | 1 external interr                  |                 | (must be clear   | ed in software) | )                  |               |  |

|               | 0 = The INT1                               | 1 external interr                  | upt did not oo  | cur              |                 |                    |               |  |

|               |                                            |                                    |                 |                  |                 |                    |               |  |

| Note: In      | terrupt flag bits                          | are set when a                     | n interrunt co  | ndition occurs   | regardless of   | the state of its ( | corresponding |  |

|               | hable bit or the g                         |                                    |                 |                  |                 |                    |               |  |

prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3

## 10.0 I/O PORTS

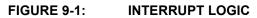

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Data Latch)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port without the interfaces to other peripherals is shown in Figure 10-1.

FIGURE 10-1: GENERIC I/O PORT

## 10.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in Configuration Register 1H (see **Section 23.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins, RA3:RA0 and RA5, as A/D converter inputs is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register 1). Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register.

Note: On a Power-on Reset, RA5 and RA3:RA0 are configured as analog inputs and read as '0'. RA4 is configured as a digital input.

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the RA pins even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| EXAMP | LE 10-1 |   | INITIALIZING PORTA    |

|-------|---------|---|-----------------------|

| CLRF  | PORTA   | ; | Initialize PORTA by   |

|       |         | ; | clearing output       |

|       |         | ; | data latches          |

| CLRF  | LATA    | ; | Alternate method      |

|       |         | ; | to clear output       |

|       |         | ; | data latches          |

| MOVLW | 0x0F    | ; | Set all A/D pins as   |

| MOVWF | ADCON1  | ; | digital I/O pins      |

| MOVLW | 0xCF    | ; | Value used to         |

|       |         | ; | initialize data       |

|       |         | ; | direction             |

| MOVWF | TRISA   | ; | Set RA<3:0> as inputs |

|       |         | ; | RA<5:4> as outputs    |

| Name                        | Bit#  | Buffer Type           | Function                                                                                                                                                                                                      |

|-----------------------------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/AN5/RD                  | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input or read control input in Parallel Slave<br>Port mode.<br>For RD (PSP Control mode):<br>1 = PSP is Idle<br>0 = Read operation. Reads PORTD register (if chip selected).    |

| RE1/AN6/WR                  | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input or write control input in Parallel<br>Slave Port mode.<br>For WR (PSP Control mode):<br>1 = PSP is Idle<br>0 = Write operation. Writes PORTD register (if chip selected). |

| RE2/AN7/CS                  | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input or chip select control input in Parallel<br>Slave Port mode.<br>For CS (PSP Control mode):<br>1 = PSP is Idle<br>0 = External device is selected                          |

| MCLR/VPP/RE3 <sup>(2)</sup> | bit 3 | ST                    | Input only port pin or programming voltage input (if $\overline{\text{MCLR}}$ is disabled);<br>Master Clear input or programming voltage input (if $\overline{\text{MCLR}}$ is enabled).                      |

#### TABLE 10-9: PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

2: The RE3 port bit is available as an input-only pin only in 40-pin devices and when Master Clear functionality is disabled (CONFIG3H<7>=0).

| TABLE 10-10: | SUMMARY OF REGISTERS | ASSOCIATED WITH PORTE |

|--------------|----------------------|-----------------------|

|              |                      |                       |

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3              | Bit 2     | Bit 1        | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|---------|--------------------|-----------|--------------|--------|----------------------|---------------------------------|

| PORTE  | _     | _     |       | _       | RE3 <sup>(1)</sup> | RE2       | RE1          | RE0    | qxxx                 | quuu                            |

| LATE   |       | —     | —     | _       | _                  | LATE Data | a Latch Reg  | ister  | xxx                  | uuu                             |

| TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _                  | PORTE Da  | ata Directio | n bits | 0000 -111            | 0000 -111                       |

| ADCON1 | _     |       | VCFG1 | VCFG0   | PCFG3              | PCFG2     | PCFG1        | PCFG0  | 00 0000              | 00 0000                         |

$\label{eq:lagend: Legend: x = unknown, u = unchanged, - = unimplemented, read as `0', q = value depends on condition. Shaded cells are not used by PORTE.$

Note 1: The RE3 port bit is available as an input-only pin only in 40-pin devices and when Master Clear functionality is disabled (CONFIG3H<7>=0).

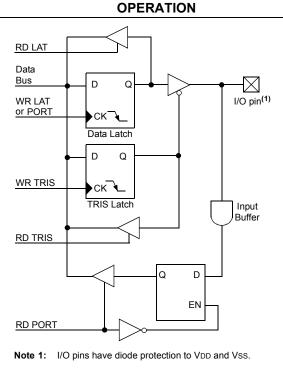

## 15.5 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force<br>the CCP1 PWM output latch to the default |

|-------|--------------------------------------------------------------------------------------|

|       | low level. This is not the PORTC I/O data latch.                                     |

Figure 15-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 15.5.3** "Setup for PWM Operation".

#### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

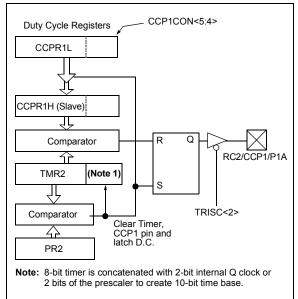

A PWM output (Figure 15-4) has a time base (*period*) and a time that the output is high (*duty cycle*). The frequency of the PWM is the inverse of the period (1/period).

## 15.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following equation.

#### EQUATION 15-1:

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is copied from CCPR1L into CCPR1H

- Note: The Timer2 postscaler (see Section 13.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

## 15.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the following equation.

### **EQUATION 15-2:**

CCPR1L and CCP1CON<5:4> can be written to at any time but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

# REGISTER 16-3: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0               | R/W-0                                                                  | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------|---------|------------------|------------------|-----------------|--------|

| ECCPASE                                                                                                                                                                                                                                                                                                                                                                                                                      | ECCPAS2             | ECCPAS1                                                                | ECCPAS0 | PSSAC1           | PSSAC0           | PSSBD1          | PSSBD0 |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                                                                        |         |                  |                  |                 | bit 0  |

|                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |                                                                        |         |                  |                  |                 |        |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |                                                                        |         |                  |                  |                 |        |

| R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                 | bit                 | W = Writable                                                           | bit     | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at F                                                                                                                                                                                                                                                                                                                                                                                                              | POR                 | '1' = Bit is set                                                       |         | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 7       ECCPASE: ECCP Auto-Shutdown Event Status bit         1 = A shutdown event has occurred; ECCP outputs are in shutdown state         0 = ECCP outputs are operating         bit 6-4       ECCPAS<2:0>: ECCP Auto-Shutdown Source Select bits         000 = Auto-shutdown is disabled         001 = Comparator 1 output         010 = Comparator 2 output         011 = Either Comparator 1 or 2         100 = INTO |                     |                                                                        |         |                  |                  |                 |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | 110 <b>= INT0 o</b> | r Comparator 1<br>r Comparator 2<br>r Comparator 1                     | 2       | or 2             |                  |                 |        |

| bit 3-2                                                                                                                                                                                                                                                                                                                                                                                                                      | 00 = Drive Pir      | Pin A and C S<br>ns A and C to '<br>ns A and C to '<br>and C tri-state | 0'      | te Control bits  |                  |                 |        |

| bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                      | 00 = Drive Pir      | Pin B and D S<br>ns B and D to '<br>ns B and D to '<br>nd D tri-state  | 0'      | te Control bits  |                  |                 |        |

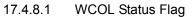

## 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

## FIGURE 17-19: FIRST START BIT TIMING

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

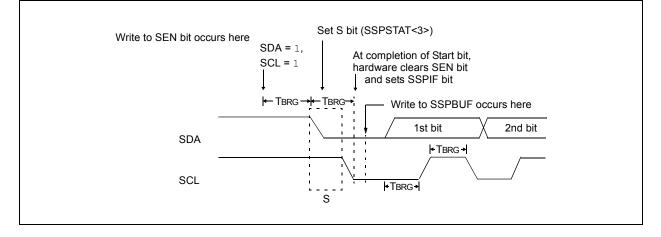

## FIGURE 21-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

## 21.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 21-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from VDD; therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in **Section 26.0 "Electrical Characteristics"**.

## 21.3 Operation in Power-Managed Modes

The contents of the CVRCON register are not affected by entry to or exit from power-managed modes. To minimize current consumption in power-managed modes, the voltage reference module should be disabled; however, this can cause an interrupt from the comparators so the comparator interrupt should also be disabled while the CVRCON register is being modified.

## 21.4 Effects of a Reset

A device Reset disables the voltage reference by clearing the CVRCON register. This also disconnects the reference from the RA2 pin, selects the high-voltage range and selects the lowest voltage tap from the resistor divider.

## 21.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be output using the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto the RA2 pin, with an input signal present, will increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, an external buffer must be used on the voltage reference output for external connections to VREF. Figure 21-2 shows an example buffering technique.

#### TABLE 24-2: PIC18FXXX INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | Description                              | Cualas     | 16-Bit Instruction Word |              |              |              | Status          | Natas      |

|-----------------------|---------------------------------|------------------------------------------|------------|-------------------------|--------------|--------------|--------------|-----------------|------------|

|                       |                                 | Description                              | Cycles     | MSb                     |              |              | LSb          | Affected        | Notes      |

| BYTE-ORI              | ENTED                           | FILE REGISTER OPERATIONS                 |            |                         |              |              |              |                 |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da         | ffff         | ffff         |                 | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da         | ffff         | ffff         | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da         | ffff         | ffff         | Z, N            | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110                    | 101a         | ffff         | ffff         | Z               | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001                    | 11da         | ffff         | ffff         | Z, N            | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a         | ffff         | ffff         | None            | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a         | ffff         | ffff         | None            | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a         | ffff         | ffff         | None            | 1, 2       |

| DECF                  | f, d, a                         | Decrement f                              | 1 ΄        | 0000                    | 01da         | ffff         | ffff         | C, DC, Z, OV, N | 1, 2, 3,   |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da         | ffff         | ffff         | None            | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da         | ffff         | ffff         | None            | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1          |                         | 10da         | ffff         | ffff         | C, DC, Z, OV, N | -          |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) |                         | 11da         | ffff         | ffff         | None            | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) |                         | 10da         | ffff         | ffff         | None            | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1          |                         | 00da         | ffff         | ffff         |                 | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1          |                         | 00da         | ffff         | ffff         | Z, N            | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          |                         | ffff         | ffff         | ffff         | ,               | •          |

|                       | 's, 'd                          | $f_d$ (destination) 2nd word             | 2          |                         | ffff         | ffff         | ffff         | None            |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          |                         | 1111a        | ffff         | ffff         | None            |            |

| MULWF                 | f. a                            | Multiply WREG with f                     | 1          |                         | 001a         | ffff         | ffff         | None            |            |

| NEGF                  | f, a                            | Negate f                                 | 1          |                         | 110a         | ffff         | ffff         | C, DC, Z, OV, N | 1 2        |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          |                         | 01da         | ffff         | ffff         |                 | 1, 2       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          |                         |              | 1111<br>ffff |              |                 | 1, 2       |

| RRCF                  | f, d, a                         |                                          | 1          |                         | 01da         | ffff         | ffff<br>ffff |                 | 1, 2       |

|                       |                                 | Rotate Right f through Carry             | 1          | 0011                    | 00da         |              |              |                 |            |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1          |                         | 00da         | ffff         | ffff         | ,               |            |

| SETF                  | f, a                            | Set f                                    | -          |                         | 100a         | ffff         | ffff         | None            | 1 0        |

| SUBFWB                | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da         | ffff         | ffff         | C, DC, Z, OV, N | Ι, Ζ       |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da         | ffff         | ffff         | C, DC, Z, OV, N |            |

| SUBWFB                | f, d, a                         | Subtract WREG from f with<br>Borrow      | 1          | 0101                    | 10da         | ffff         | ffff         |                 | 1, 2       |

| SWAPF                 | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da         | ffff         | ffff         | None            | 4          |

| TSTFSZ                | r, d, a<br>f, a                 |                                          | 1 (2 or 3) | 0011                    | 10da<br>011a | IIII<br>ffff | IIII<br>ffff | None            | 4<br>1, 2  |

|                       | ,                               | Test f, Skip if 0                        | ( )        |                         |              |              |              |                 | 1, 2       |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da         | ffff         | ffff         | Z, N            |            |

|                       |                                 | E REGISTER OPERATIONS                    | 1          |                         |              |              |              | I               |            |

| BCF                   | f, b, a                         | Bit Clear f                              | 1          | 1001                    | bbba         | ffff         | ffff         | None            | 1, 2       |

| BSF                   | f, b, a                         | Bit Set f                                | 1          | 1000                    | bbba         | ffff         | ffff         | None            | 1, 2       |

| BTFSC                 | f, b, a                         | Bit Test f, Skip if Clear                | 1 (2 or 3) | 1011                    | bbba         | ffff         | ffff         | None            | 3, 4       |

| BTFSS                 | f, b, a                         | Bit Test f, Skip if Set                  | 1 (2 or 3) | 1010                    | bbba         | ffff         | ffff         | None            | 3, 4       |

| BTG                   | f, d, a                         | Bit Toggle f                             | 1          | 0111                    | bbba         | ffff         | ffff         | None            | 1, 2       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| BCF                                                                                                       | Bit Clear f                                     |                                                                                                                                                                                                         |    |                     |  |  |  |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------|--|--|--|

| Syntax:                                                                                                   | Syntax: [ label ] BCF f,b[,a]                   |                                                                                                                                                                                                         |    |                     |  |  |  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                      |                                                 |                                                                                                                                                                                                         |    |                     |  |  |  |

| Operation:                                                                                                | $0 \rightarrow f < b >$                         |                                                                                                                                                                                                         |    |                     |  |  |  |

| Status Affected:                                                                                          | None                                            |                                                                                                                                                                                                         |    |                     |  |  |  |

| Encoding:                                                                                                 | 1001 3                                          | bbba ff                                                                                                                                                                                                 | ff | ffff                |  |  |  |

| Description:                                                                                              | is '0', the A<br>selected, ov<br>If 'a' = 1, th | Bit 'b' in register 'f' is cleared. If 'a'<br>is '0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default) |    |                     |  |  |  |

| Words:                                                                                                    | 1                                               | 1                                                                                                                                                                                                       |    |                     |  |  |  |

| Cycles:                                                                                                   | 1                                               |                                                                                                                                                                                                         |    |                     |  |  |  |

| Q Cycle Activity                                                                                          |                                                 |                                                                                                                                                                                                         |    |                     |  |  |  |

| Q1                                                                                                        | Q2                                              | Q3                                                                                                                                                                                                      |    | Q4                  |  |  |  |

| Decode                                                                                                    | Read<br>register 'f'                            | Process<br>Data                                                                                                                                                                                         |    | Write<br>gister 'f' |  |  |  |

| Example: BCF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |                                                 |                                                                                                                                                                                                         |    |                     |  |  |  |

| BN               | Branch if                                                           | Branch if Negative                                                                                                 |                                                         |  |  |  |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] B                                                  | Nn                                                                                                                 |                                                         |  |  |  |

| Operands:        | -128 ≤ n ≤                                                          | 127                                                                                                                |                                                         |  |  |  |

| Operation:       | if Negative<br>(PC) + 2 +                                           |                                                                                                                    |                                                         |  |  |  |

| Status Affected: | None                                                                |                                                                                                                    |                                                         |  |  |  |

| Encoding:        | 1110                                                                | 0110 nnr                                                                                                           | nn nnnn                                                 |  |  |  |

|                  | added to t<br>have incre<br>instruction<br>PC + 2 + 2<br>then a two | vill branch.<br>Implement nu<br>he PC. Since<br>emented to fe<br>I, the new ad<br>2n. This instr<br>D-cycle instru | e the PC wi<br>etch the ne<br>dress will b<br>uction is |  |  |  |

| Words:           | 1                                                                   |                                                                                                                    |                                                         |  |  |  |

| Cycles:          | 1(2)                                                                |                                                                                                                    |                                                         |  |  |  |

| Q Cycle Activity | <b>y</b> :                                                          |                                                                                                                    |                                                         |  |  |  |

| Q1               | Q2                                                                  | Q3                                                                                                                 | Q4                                                      |  |  |  |

| Decode           | Read literal<br>'n'                                                 | Process<br>Data                                                                                                    | Write to PC                                             |  |  |  |

| No               | No                                                                  | No                                                                                                                 | No                                                      |  |  |  |

| operation        | operation                                                           | operation                                                                                                          | operation                                               |  |  |  |

| If No Jump:      |                                                                     |                                                                                                                    |                                                         |  |  |  |

| Q1               | Q2                                                                  | Q3                                                                                                                 | Q4                                                      |  |  |  |

| Decode           | Read literal<br>'n'                                                 | Process<br>Data                                                                                                    | No<br>operation                                         |  |  |  |

| Example:         | HERE                                                                | BN Jump                                                                                                            |                                                         |  |  |  |

| Before Inst      | ruction                                                             |                                                                                                                    |                                                         |  |  |  |

| PC               | = ad                                                                | dress (HERE)                                                                                                       |                                                         |  |  |  |

| PC                | = | address (HERE)     |

|-------------------|---|--------------------|

| After Instruction |   |                    |

| If Negative       | = | 1;                 |

| РC                | = | address (Jump)     |

| If Negative       | = | 0;                 |

| PC                | = | address (HERE + 2) |

| INC      | SZ                                                    | Incremen                                                                                                                                                                 | t f, Skip if 0                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |

|----------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|

| Synt     | ax:                                                   | [ label ]                                                                                                                                                                | INCFSZ f[                                                                                                                                                                                                                                                                                                                        | ,d [,a]]                |  |  |  |

| Ope      | rands:                                                | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                |                         |  |  |  |

| Ope      | ration:                                               | (f) + 1 $\rightarrow$ c<br>skip if resu                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  |                         |  |  |  |

| Statu    | us Affected:                                          | None                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                  |                         |  |  |  |

| Enco     | oding:                                                | 0011                                                                                                                                                                     | 11da ffi                                                                                                                                                                                                                                                                                                                         | ff ffff                 |  |  |  |

| Word     |                                                       | increment<br>is placed i<br>(default).<br>If the resu<br>instruction<br>is discarde<br>instead, m<br>instruction<br>Bank will b<br>the BSR v<br>bank will b<br>BSR value | If the result is '0', the next<br>instruction which is already fetched<br>is discarded and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the<br>bank will be selected as per the<br>BSR value (default). |                         |  |  |  |

| Cycl     | es:                                                   | 1(2)                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                  |                         |  |  |  |

| -        |                                                       | Note: 3 c                                                                                                                                                                | ycles if skip a<br>a 2-word inst                                                                                                                                                                                                                                                                                                 |                         |  |  |  |

| QC       | ycle Activity:                                        |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                  |                         |  |  |  |

|          | Q1                                                    | Q2                                                                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                               | Q4                      |  |  |  |

|          | Decode                                                | Read<br>register 'f'                                                                                                                                                     | Process<br>Data                                                                                                                                                                                                                                                                                                                  | Write to<br>destination |  |  |  |

| lf sk    | (ip:                                                  | regiotor                                                                                                                                                                 | Dulu                                                                                                                                                                                                                                                                                                                             | dootinution             |  |  |  |

|          | Q1                                                    | Q2                                                                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                               | Q4                      |  |  |  |

|          | No                                                    | No                                                                                                                                                                       | No                                                                                                                                                                                                                                                                                                                               | No                      |  |  |  |

|          | operation                                             | operation                                                                                                                                                                | operation                                                                                                                                                                                                                                                                                                                        | operation               |  |  |  |

| IT SK    | kip and follow                                        |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                  | 04                      |  |  |  |

|          | Q1<br>No                                              | Q2<br>No                                                                                                                                                                 | Q3<br>No                                                                                                                                                                                                                                                                                                                         | Q4<br>No                |  |  |  |

|          | operation                                             | operation                                                                                                                                                                | operation                                                                                                                                                                                                                                                                                                                        | operation               |  |  |  |

|          | No                                                    | No                                                                                                                                                                       | No                                                                                                                                                                                                                                                                                                                               | No                      |  |  |  |

|          | operation                                             | operation                                                                                                                                                                | operation                                                                                                                                                                                                                                                                                                                        | operation               |  |  |  |

| Example: |                                                       | NZERO                                                                                                                                                                    | INCFSZ CN<br>:<br>:                                                                                                                                                                                                                                                                                                              | Τ                       |  |  |  |

|          | Before Instru<br>PC                                   | = Address                                                                                                                                                                | 6 (HERE)                                                                                                                                                                                                                                                                                                                         |                         |  |  |  |

|          | After Instruct<br>CNT<br>If CNT<br>PC<br>If CNT<br>PC | ion<br>= CNT + 7<br>= 0;<br>= Address<br>≠ 0;<br>= Address                                                                                                               | S (ZERO)                                                                                                                                                                                                                                                                                                                         |                         |  |  |  |

| C            | SNZ                                                                                            | Incremen                                                                                                                                                 | Increment f, Skip if Not 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |  |  |  |