Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

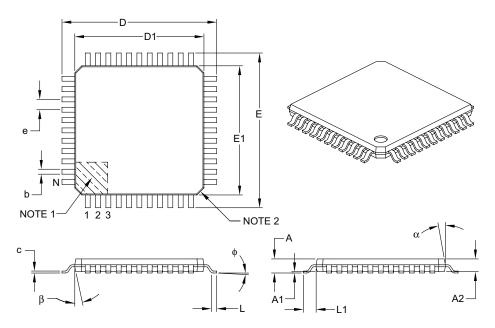

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4220-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                           | Pin Number |      | Pin | Buffer          | Description |                                                                                                                                                                          |  |  |

|------------------------------------|------------|------|-----|-----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                           | PDIP       | TQFP | QFN | Туре            | Туре        | Description                                                                                                                                                              |  |  |

|                                    |            |      |     |                 |             | PORTD is a bidirectional I/O port or a Parallel Slave Port (PSP) for interfacing to a microprocessor port. These pins have TTL input buffers when PSP module is enabled. |  |  |

| RD0/PSP0<br>RD0<br>PSP0            | 19         | 38   | 38  | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                |  |  |

| RD1/PSP1<br>RD1<br>PSP1            | 20         | 39   | 39  | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                |  |  |

| RD2/PSP2<br>RD2<br>PSP2            | 21         | 40   | 40  | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                |  |  |

| RD3/PSP3<br>RD3<br>PSP3            | 22         | 41   | 41  | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                |  |  |

| RD4/PSP4<br>RD4<br>PSP4            | 27         | 2    | 2   | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                |  |  |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B | 28         | 3    | 3   | I/O<br>I/O<br>O | ST<br>TTL   | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                       |  |  |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C | 29         | 4    | 4   | I/O<br>I/O<br>O | ST<br>TTL   | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                       |  |  |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D | 30         | 5    | 5   | I/O<br>I/O<br>O | ST<br>TTL   | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                       |  |  |

| TABLE 1-3: | PIC18F4220/4320 | PINOUT I/O  | DESCRIPTIONS ( |  |

|------------|-----------------|-------------|----------------|--|

|            |                 | 1 11001 1/0 |                |  |

ST = Schmitt Trigger input with CMOS levels

= Output

0

= Input L

Ρ = Power

OD = Open-drain (no diode to VDD)

Note 1: Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

## 3.5.2 EXIT BY RESET

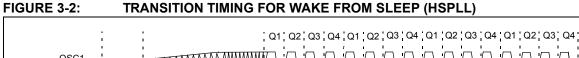

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock (defined in Configuration Register 1H) becomes ready. At that time, the OSTS bit is set and the device begins executing code.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see Section 23.3 "Two-Speed Start-up") or Fail-Safe Clock Monitor (see Section 23.4 "Fail-Safe Clock Monitor") are enabled in Configuration Register 1H, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Since the OSCCON register is cleared following all Resets, the INTRC clock source is selected. A higher speed clock may be selected by modifying the IRCF bits in the OSCCON register. Execution is clocked by the internal oscillator block until either the primary clock becomes ready, or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

## 3.5.3 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in a wake-up from the power-managed mode (see Section 3.2 "Sleep Mode" through Section 3.4 "Run Modes").

If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see **Section 23.2** "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the system clock source.

### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. These are:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these cases, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes).

However, a fixed delay (approximately 10  $\mu$ s) following the wake-up event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## 3.6 INTOSC Frequency Drift

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz. However, this frequency may drift as VDD or temperature changes, which can affect the controller operation in a variety of ways.

It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has the side effect that the INTRC clock source frequency is also affected. However, the features that use the INTRC source often do not require an exact frequency. These features include the Fail-Safe Clock Monitor, the Watchdog Timer and the RC\_RUN/RC\_IDLE modes when the INTRC clock source is selected.

Being able to adjust the INTOSC requires knowing when an adjustment is required, in which direction it should be made and in some cases, how large a change is needed. Three examples are shown but other techniques may be used.

## 6.5 Writing to Flash Program Memory

The programming block size is 4 words or 8 bytes. Word or byte programming is not supported.

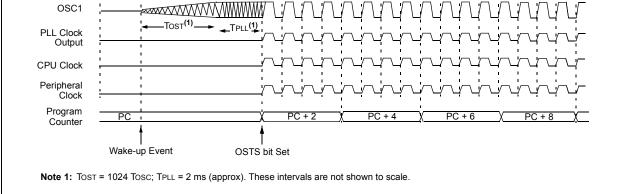

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 8 holding registers used by the table writes for programming. Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction has to be executed 8 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating 8 registers, the EECON1 register must be written to, to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

#### FIGURE 6-5: TABLE WRITES TO FLASH PROGRAM MEMORY

#### 6.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer with address being erased.

- 4. Do the row erase procedure (see Section 6.4.1 "Flash Program Memory Erase Sequence").

- 5. Load Table Pointer with address of first byte being written.

- 6. Write the first 8 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- · set WREN bit to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Execute a NOP.

- 14. Re-enable interrupts.

- 15. Repeat steps 6-14 seven times, to write 64 bytes.

- 16. Verify the memory (table read).

This procedure will require about 18 ms to update one row of 64 bytes of memory. An example of the required code is given in Example 6-3.

## 9.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising if the corresponding INTEDGx bit is set in the INTCON2 register, or falling if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from the power-managed modes if bit INTxIE was set prior to going into power-managed modes. If the global interrupt enable bit GIE is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the Interrupt Priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high-priority interrupt source.

## 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF. In 16-bit mode, an overflow (FFFFh  $\rightarrow$  0000h) in the TMR0H:TMR0L registers will set flag bit TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 11.0 "Timer0 Module" for further details on the Timer0 module.

### 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

## 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (See **Section 5.3 "Fast Register Stack"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

#### EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

MOVWF W TEMP ; W TEMP is in virtual bank MOVFF STATUS, STATUS TEMP ; STATUS TEMP located anywhere MOVFF BSR, BSR TEMP ; BSR TMEP located anywhere ; ; USER ISR CODE • MOVFF BSR TEMP, BSR ; Restore BSR MOVF W TEMP, W ; Restore WREG STATUS\_TEMP, STATUS MOVFF ; Restore STATUS

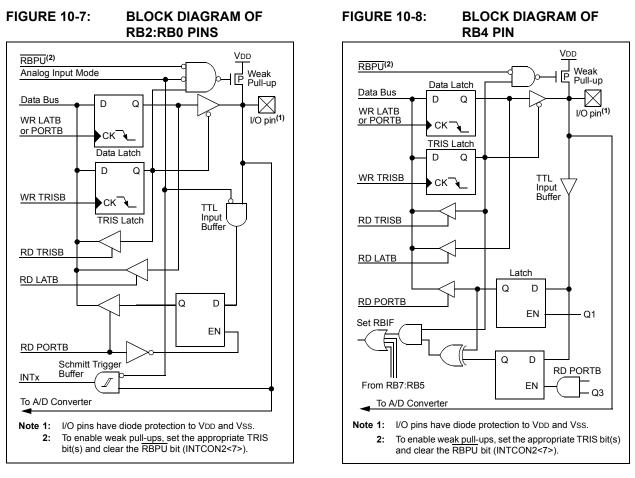

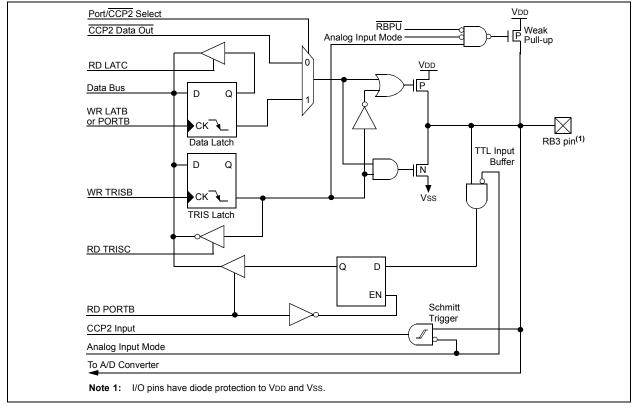

#### FIGURE 10-9: BLOCK DIAGRAM OF RB3/CCP2 PIN

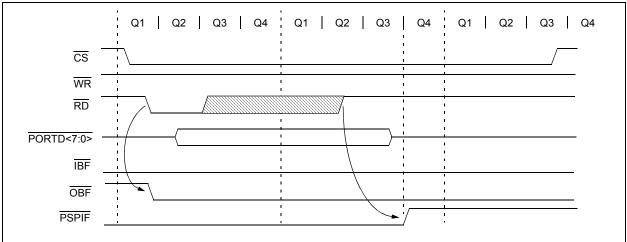

#### FIGURE 10-17: PARALLEL SLAVE PORT READ WAVEFORMS

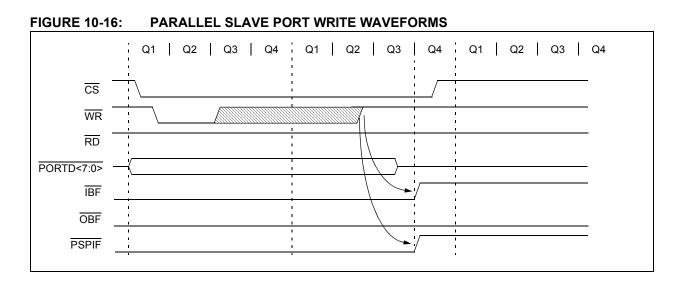

#### TABLE 10-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7        | Bit 6         | Bit 5        | Bit 4          | Bit 3 | Bit 2     | Bit 1        | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|--------------|---------------|--------------|----------------|-------|-----------|--------------|--------|----------------------|---------------------------------|

| PORTD  | Port Data    | Latch whe     | n written; F | Port pins when | read  |           |              |        | XXXX XXXX            | uuuu uuuu                       |

| LATD   | LATD Data    | a Latch bit   | s            |                |       |           |              |        | XXXX XXXX            | uuuu uuuu                       |

| TRISD  | PORTD D      | ata Directi   | on bits      |                |       |           |              |        | 1111 1111            | 1111 1111                       |

| PORTE  | _            | _             | _            | _              | RE3   | RE2       | RE1          | RE0    | qxxx                 | quuu                            |

| LATE   | _            | _             | _            | _              | —     | LATE Data | a Latch bits |        | xxx                  | uuu                             |

| TRISE  | IBF          | OBF           | IBOV         | PSPMODE        | _     | PORTE D   | ata Directio | n bits | 0000 -111            | 0000 -111                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IF       | INTOIE         | RBIE  | TMR0IF    | INTOIF       | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF        | ADIF          | RCIF         | TXIF           | SSPIF | CCP1IF    | TMR2IF       | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE        | ADIE          | RCIE         | TXIE           | SSPIE | CCP1IE    | TMR2IE       | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP        | ADIP          | RCIP         | TXIP           | SSPIP | CCP1IP    | TMR2IP       | TMR1IP | 1111 1111            | 1111 1111                       |

| ADCON1 | —            | —             | VCFG1        | VCFG0          | PCFG3 | PCFG2     | PCFG1        | PCFG0  | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

## 16.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

| Note: | The ECCP (Enhanced Capture/ Compare/ |        |    |      |           |    |

|-------|--------------------------------------|--------|----|------|-----------|----|

|       | PWM)                                 | module | is | only | available | on |

|       | PIC18F4X20 devices.                  |        |    |      |           |    |

In 40 and 44-pin devices, the CCP1 module is implemented as a standard CCP module with enhanced PWM capabilities. Operation of the Capture, Compare and standard single output PWM modes is described in **Section 15.0 "Capture/Compare/PWM (CCP) Modules"**. Discussion in that section relating to PWM frequency and duty cycle also apply to the enhanced PWM mode. The ECCP module differs from the CCP with the addition of an enhanced PWM mode which allows for 2 or 4 output channels, user-selectable polarity, dead band control and automatic shutdown and restart. These features are discussed in detail in **Section 16.4 "Enhanced PWM Mode"**.

The control register for CCP1 is shown in Register 16-1. It differs from the CCP1CON register of PIC18F2X20 devices in that the two Most Significant bits are implemented to control enhanced PWM functionality.

## REGISTER 16-1: CCP1CON: ECCP CONTROL REGISTER (40/44-PIN DEVICES)

| R/W-0            | R/W-0                             | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |  |

|------------------|-----------------------------------|-------|-----------------------------------------|------------------------------------|--------|--------|--------|--|--|

| P1M1             | P1M0                              | DC1B1 | DC1B0                                   | CCP1M3                             | CCP1M2 | CCP1M1 | CCP1M0 |  |  |

| bit 7            |                                   | •     |                                         | •                                  |        |        | bit 0  |  |  |

|                  |                                   |       |                                         |                                    |        |        |        |  |  |

| Legend:          |                                   |       |                                         |                                    |        |        |        |  |  |

| R = Readable b   | eadable bit W = Writable bit      |       |                                         | U = Unimplemented bit, read as '0' |        |        |        |  |  |

| -n = Value at Po | n = Value at POR (1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                                    |        |        |        |  |  |

|                  |                                   |       |                                         |                                    |        |        |        |  |  |

bit 7-6 P1M1:P1M0: PWM Output Configuration bits If CCP1M3:CCP1M2 = 00, 01, 10 (Capture, Compare or disabled): xx = P1A assigned as Capture/Compare input; P1B, P1C, P1D assigned as port pins If CCP1M3:CCP1M2 = 11 (PWM modes): 00 = Single output: P1A modulated; P1B, P1C, P1D assigned as port pins 01 = Full-bridge output forward: P1D modulated; P1A active; P1B, P1C inactive 10 = Half-bridge output: P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins 11 = Full-bridge output reverse: P1B modulated; P1C active; P1A, P1D inactive bit 5-4 DC1B1:DC1B0: PWM Duty Cycle Least Significant bits Capture mode: Unused. Compare mode: Unused. PWM mode: These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR1L.

## 17.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 17.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode

## 17.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual Configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

### 17.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received, simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/SS/LVDIN/C2OUT

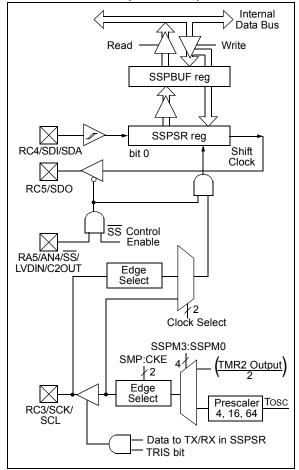

Register 17-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 17-1: MSSP BLOCK DIAGRAM (SPI MODE)

## 17.4.4 CLOCK STRETCHING

Both 7 and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 17.4.4.1 Clock Stretching for 7-Bit Slave Receive Mode (SEN = 1)

In 7-Bit Slave Receive mode, on the falling edge of the ninth clock at the end of the ACK sequence if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 17-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

### 17.4.4.2 Clock Stretching for 10-Bit Slave Receive Mode (SEN = 1)

In 10-Bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but the CKP bit is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

**Note:** If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

### 17.4.4.3 Clock Stretching for 7-Bit Slave Transmit Mode

7-Bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 17-9).

| Note 1: | If the user loads the contents of SSPBUF,     |  |  |  |  |  |

|---------|-----------------------------------------------|--|--|--|--|--|

|         | setting the BF bit before the falling edge of |  |  |  |  |  |

|         | the ninth clock, the CKP bit will not be      |  |  |  |  |  |

|         | cleared and clock stretching will not occur.  |  |  |  |  |  |

| 2.      | The CKP bit can be set in software            |  |  |  |  |  |

regardless of the state of the BF bit.

#### 17.4.4.4 Clock Stretching for 10-Bit Slave Transmit Mode

In 10-Bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-Bit Slave Receive mode. The first two addresses are followed by a third address sequence which contains the high-order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-Bit Slave Transmit mode (see Figure 17-11).

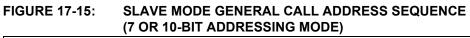

#### 17.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 17-15).

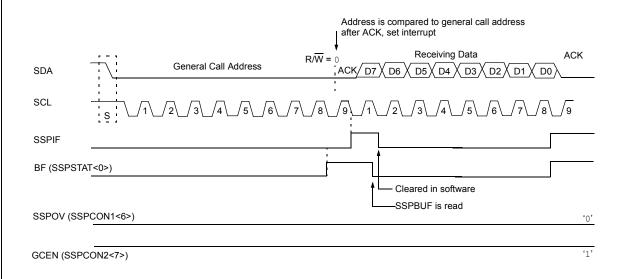

## 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

## 17.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

## FIGURE 17-19: FIRST START BIT TIMING

## 22.1 Control Register

The Low-Voltage Detect Control register controls the operation of the Low-Voltage Detect circuitry.

#### REGISTER 22-1: LVDCON: LOW-VOLTAGE DETECT CONTROL REGISTER

| U-0                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                          | R-0                                                                                                                                                                    | R/W-0           | R/W-0                   | R/W-1                | R/W-0                | R/W-1                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|----------------------|----------------------|----------------------|

| _                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                              | IRVST                                                                                                                                                                  | LVDEN           | LVDL3 <sup>(1)</sup>    | LVDL2 <sup>(1)</sup> | LVDL1 <sup>(1)</sup> | LVDL0 <sup>(1)</sup> |

| bit 7                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                              |                                                                                                                                                                        |                 |                         |                      |                      | bit 0                |

|                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |                                                                                                                                                                        |                 |                         |                      |                      |                      |

| Legend:                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                              |                                                                                                                                                                        |                 |                         |                      |                      |                      |

| R = Readab                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              | W = Writable                                                                                                                                                           |                 |                         | nented bit, read     |                      |                      |

| -n = Value a                                                                                                                                                                                                                                                                                                                                                                  | t POR                                                                                                                                                                                                                                        | '1' = Bit is set                                                                                                                                                       |                 | '0' = Bit is cle        | ared                 | x = Bit is unkr      | nown                 |

| bit 7-6                                                                                                                                                                                                                                                                                                                                                                       | Unimplement                                                                                                                                                                                                                                  | ted: Read as '                                                                                                                                                         | ∩ <b>'</b>      |                         |                      |                      |                      |

| bit 5                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                            |                                                                                                                                                                        |                 | Flag bit                |                      |                      |                      |

| <ul> <li>bit 5 IRVST: Internal Reference Voltage Stable Flag bit</li> <li>1 = Indicates that the Low-Voltage Detect logic will generate the interrupt flag at the specified voltage range</li> <li>0 = Indicates that the Low-Voltage Detect logic will not generate the interrupt flag at the specified voltage range and the LVD interrupt should not be enabled</li> </ul> |                                                                                                                                                                                                                                              |                                                                                                                                                                        |                 |                         |                      |                      |                      |

| bit 4                                                                                                                                                                                                                                                                                                                                                                         | LVDEN: Low-                                                                                                                                                                                                                                  | Voltage Detect                                                                                                                                                         | Power Enab      | le bit                  |                      |                      |                      |

|                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                              | .VD, powers up<br>LVD, powers de                                                                                                                                       |                 | uit                     |                      |                      |                      |

| bit 3-0                                                                                                                                                                                                                                                                                                                                                                       | LVDL3:LVDL                                                                                                                                                                                                                                   | 0: Low-Voltage                                                                                                                                                         | Detection Lir   | mit bits <sup>(1)</sup> |                      |                      |                      |

|                                                                                                                                                                                                                                                                                                                                                                               | 1111 = Extern<br>1110 = 4.50V<br>1101 = 4.20V<br>100 = 4.00V<br>1011 = 3.80V<br>1010 = 3.60V<br>1001 = 3.50V<br>1000 = 3.30V<br>0111 = 3.00V<br>0110 = 2.80V<br>0101 = 2.70V<br>0101 = 2.20V<br>0011 = 2.20V<br>0001 = 2.00V<br>0000 = Reser | -4.78V<br>-4.46V<br>-4.26V<br>-4.26V<br>-4.04V<br>-3.84V<br>-3.72V<br>-3.52V<br>-3.52V<br>-3.52V<br>-2.98V<br>-2.98V<br>-2.86V<br>-2.66V<br>-2.55V<br>-2.34V<br>-2.12V | ıt is used (inp | ut comes from           | the LVDIN pin)       |                      |                      |

**Note 1:** LVDL3:LVDL0 modes which result in a trip point below the valid operating voltage of the device are not tested.

## REGISTER 23-10: CONFIG7L: CONFIGURATION REGISTER 7 LOW (BYTE ADDRESS 30000Ch)

| U-0           | U-0                                                                                                                                                                                                | U-0             | U-0                   | R/P-1                | R/P-1                | R/P-1       | R/P-1 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|----------------------|----------------------|-------------|-------|

| _             | —                                                                                                                                                                                                  | —               | _                     | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1       | EBTR0 |

| bit 7         |                                                                                                                                                                                                    |                 |                       |                      |                      |             | bit 0 |

|               |                                                                                                                                                                                                    |                 |                       |                      |                      |             |       |

| Legend:       |                                                                                                                                                                                                    |                 |                       |                      |                      |             |       |

| R = Readable  | bit                                                                                                                                                                                                | P = Programn    | nable bit             | U = Unimpler         | nented bit, read     | as '0'      |       |

| -n = Value wh | en device is unp                                                                                                                                                                                   | programmed      |                       | u = Unchang          | ed from progran      | nmed state  |       |

|               |                                                                                                                                                                                                    |                 |                       |                      |                      |             |       |

| bit 7-4       | Unimplemen                                                                                                                                                                                         | ted: Read as '  | )'                    |                      |                      |             |       |

| bit 3         | EBTR3: Table                                                                                                                                                                                       | e Read Protecti | on bit <sup>(1)</sup> |                      |                      |             |       |

|               |                                                                                                                                                                                                    |                 |                       |                      | reads executed       |             |       |

|               | -                                                                                                                                                                                                  |                 |                       | from table read      | Is executed in o     | ther blocks |       |

| bit 2         | EBTR2: Table                                                                                                                                                                                       | e Read Protecti | on bit <sup>(1)</sup> |                      |                      |             |       |

|               | <ul> <li>1 = Block 2 (001000-0017FFh) not protected from table reads executed in other blocks</li> <li>0 = Block 2 (001000-0017FFh) protected from table reads executed in other blocks</li> </ul> |                 |                       |                      |                      |             |       |

| bit 1         | EBTR1: Table                                                                                                                                                                                       | e Read Protecti | on bit                |                      |                      |             |       |

|               | <ul> <li>1 = Block 1 (000800-000FFFh) not protected from table reads executed in other blocks</li> <li>0 = Block 1 (000800-000FFFh) protected from table reads executed in other blocks</li> </ul> |                 |                       |                      |                      |             |       |

| bit 0         | EBTR0: Table                                                                                                                                                                                       | e Read Protecti | on bit                |                      |                      |             |       |

|               | 1 = Block 0 (000200-0007FFh) not protected from table reads executed in other blocks<br>0 = Block 0 (000200-0007FFh) protected from table reads executed in other blocks                           |                 |                       |                      |                      |             |       |

Note 1: Unimplemented in PIC18FX220 devices; maintain this bit set.

#### REGISTER 23-11: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)

| U-0   | R/P-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| —     | EBTRB | —   | —   | —   | —   |     | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend | I: |

|--------|----|

|--------|----|

| R = Readable bit             | P = Programmable bit | U = Unimplemented bit, read as '0'  |

|------------------------------|----------------------|-------------------------------------|

| -n = Value when device is un | programmed           | u = Unchanged from programmed state |

bit 7

Unimplemented: Read as '0'

bit 6

EBTRB: Boot Block Table Read Protection bit

1 = Boot block (000000-0001FFh) is not protected from table reads executed in other blocks

0 = Boot block (000000-0001FFh) is protected from table reads executed in other blocks

bit 5-0

Unimplemented: Read as '0'

| MOVFF                                                                                                                                                                                                                                                       | Move f to                                                                                                                                                                                                                               | f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                |                                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                     | [label]                                                                                                                                                                                                                                 | MOVFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>s</sub> ,f <sub>d</sub> |                                        |  |  |  |

| Operands:                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                       | $\begin{array}{l} 0 \leq f_s \leq 4095 \\ 0 \leq f_d \leq 4095 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |                                        |  |  |  |

| Operation:                                                                                                                                                                                                                                                  | $(f_s) \to f_d$                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                        |  |  |  |

| Status Affected:                                                                                                                                                                                                                                            | None                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                        |  |  |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.                                                                                                                                                                                                         |                                                                                                                                                                                                                                         | ffff<br>ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ffff<br>ffff                   | ffff <sub>s</sub><br>ffff <sub>d</sub> |  |  |  |

| Description:                                                                                                                                                                                                                                                | are moved<br>'f <sub>d</sub> '. Locati<br>anywhere<br>space (00)<br>of destinat<br>anywhere<br>Either sou<br>W (a usefu<br>MOVFF is J<br>transferrin<br>to a periph<br>transmit b<br>The MOVF<br>the PCL, T<br>the destinat<br>The MOVF | The contents of source register ' $f_s$ ' are moved to destination register ' $f_d$ '. Location of source ' $f_s$ ' can be anywhere in the 4096-byte data space (000h to FFFh) and location of destination ' $f_d$ ' can also be anywhere from 000h to FFFh. Either source or destination can be W (a useful special situation). MOVFF is particularly useful for transferring a data memory location to a peripheral register (such as the transmit buffer or an I/O port). The MOVFF instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register. The MOVFF instruction should not be used to modify interrupt settings while any interrupt is enabled (see Page 87). |                                |                                        |  |  |  |

| Words:                                                                                                                                                                                                                                                      | 2                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                        |  |  |  |

| Cycles:                                                                                                                                                                                                                                                     | 2 (3)                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                        |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                        |  |  |  |

| Q1                                                                                                                                                                                                                                                          | Q2                                                                                                                                                                                                                                      | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                | Q4                                     |  |  |  |

| Decode                                                                                                                                                                                                                                                      | Read<br>register 'f'<br>(src)                                                                                                                                                                                                           | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                | No<br>eration                          |  |  |  |

| Decode                                                                                                                                                                                                                                                      | No<br>operation<br>No dummy<br>read                                                                                                                                                                                                     | No<br>operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | n re                           | Write<br>gister 'f'<br>(dest)          |  |  |  |

| Example:       MOVFF       REG1, REG2         Before Instruction       REG1       =       0x33         REG2       =       0x11         After Instruction       REG1       =       0x33, REG2         REG1       =       0x33, REG2       =       0x33, REG2 |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                        |  |  |  |

| MO\         | /LB           | Move Literal to Low Nibble in BSR |                |     |       |                           |

|-------------|---------------|-----------------------------------|----------------|-----|-------|---------------------------|

| Synt        | ax:           | [ label ]                         | MOVLB          | k   |       |                           |

| Ope         | rands:        | $0 \le k \le 25$                  | 5              |     |       |                           |

| Ope         | ration:       | $k \to BSR$                       |                |     |       |                           |

| Statu       | us Affected:  | None                              |                |     |       |                           |

| Enco        | oding:        | 0000                              | 0001           | kk. | kk    | kkkk                      |

| Des         | cription:     | The 8-bit I the Bank              |                |     |       |                           |

| Wor         | ds:           | 1                                 |                |     |       |                           |

| Cycl        | es:           | 1                                 |                |     |       |                           |

| QC          | ycle Activity | :                                 |                |     |       |                           |

|             | Q1            | Q2                                | Q3             |     |       | Q4                        |

|             | Decode        | Read literal<br>'k'               | Proce:<br>Data |     | liter | Vrite<br>al 'k' to<br>BSR |

| <u>Exar</u> | nple:         | MOVLB 5                           | 5              |     |       |                           |

Before Instruction BSR register = 0x02 After Instruction BSR register = 0x05

## 26.3 DC Characteristics: PIC18F2220/2320/4220/4320 (Industrial) PIC18LF2220/2320/4220/4320 (Industrial)

| DC CHA       | RACTE  | RISTICS                                | Standard Operating Conditions (unless other<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for ir<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for |          | ≤ +85°C for industrial |                                                  |

|--------------|--------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------|--------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                         | Min                                                                                                                                                               | Мах      | Units                  | Conditions                                       |

|              | VIL    | Input Low Voltage                      |                                                                                                                                                                   |          |                        |                                                  |

|              |        | I/O Ports:                             |                                                                                                                                                                   |          |                        |                                                  |

| D030         |        | with TTL Buffer                        | Vss                                                                                                                                                               | 0.15 Vdd | V                      | VDD < 4.5V                                       |

| D030A        |        |                                        | —                                                                                                                                                                 | 0.8      | V                      | $4.5V \le V\text{DD} \le 5.5V$                   |

| D031         |        | with Schmitt Trigger Buffer            | Vss                                                                                                                                                               | 0.2 VDD  | V                      |                                                  |

|              |        | RC3 and RC4                            | Vss                                                                                                                                                               | 0.3 VDD  | V                      |                                                  |

| D032         |        | MCLR                                   | Vss                                                                                                                                                               | 0.2 VDD  | V                      |                                                  |

| D032A        |        | OSC1 and T1OSI                         | Vss                                                                                                                                                               | 0.2 Vdd  | V                      | LP, XT, HS, HSPLL<br>modes <sup>(1)</sup>        |

| D033         |        | OSC1                                   | Vss                                                                                                                                                               | 0.2 Vdd  | V                      | EC mode <sup>(1)</sup>                           |

|              | VIH    | Input High Voltage                     |                                                                                                                                                                   |          |                        |                                                  |

|              |        | I/O Ports:                             |                                                                                                                                                                   |          |                        |                                                  |

| D040         |        | with TTL Buffer                        | 0.25 VDD + 0.8V                                                                                                                                                   | Vdd      | V                      | VDD < 4.5V                                       |

| D040A        |        |                                        | 2.0                                                                                                                                                               | Vdd      | V                      | $4.5V \leq V \text{DD} \leq 5.5V$                |

| D041         |        | with Schmitt Trigger Buffer            | 0.8 Vdd                                                                                                                                                           | Vdd      | V                      |                                                  |

|              |        | RC3 and RC4                            | 0.7 Vdd                                                                                                                                                           | Vdd      | V                      |                                                  |

| D042         |        | MCLR                                   | 0.8 Vdd                                                                                                                                                           | Vdd      | V                      |                                                  |

| D042A        |        | OSC1 and T1OSI                         | 1.6                                                                                                                                                               | Vdd      | V                      | LP, XT, HS, HSPLL<br>modes <sup>(1)</sup>        |