Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 13x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4320-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nomo                                              | Pi               | n Numl   | ber      | Pin Buffer        | Description      |                                                                                                                                          |

|-------------------------------------------------------|------------------|----------|----------|-------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                              | PDIP             | TQFP     | QFN      | Туре              | Туре             | Description                                                                                                                              |

|                                                       |                  |          |          |                   |                  | PORTC is a bidirectional I/O port.                                                                                                       |

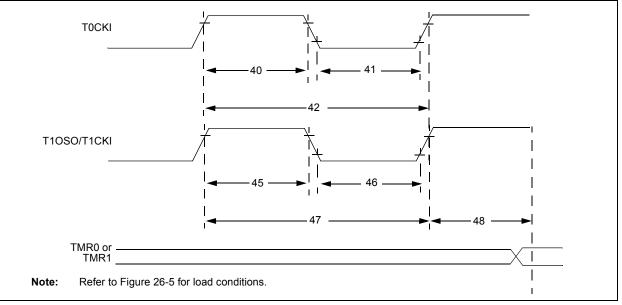

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI              | 15               | 32       | 34       | I/O<br>O<br>I     | ST<br>—<br>ST    | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                         |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(2)</sup> | 16               | 35       | 35       | I/O<br>I<br>I/O   | ST<br>CMOS<br>ST | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input, Compare 2 output, PWM2 output.                                              |

| RC2/CCP1/P1A<br>RC2<br>CCP1<br>P1A                    | 17               | 36       | 36       | I/O<br>I/O<br>O   | ST<br>ST         | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Enhanced CCP1 output.                                                   |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                      | 18               | 37       | 37       | I/O<br>I/O<br>I/O | ST<br>ST<br>ST   | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                      | 23               | 42       | 42       | I/O<br>I<br>I/O   | ST<br>ST<br>ST   | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |

| RC5/SDO<br>RC5<br>SDO                                 | 24               | 43       | 43       | I/O<br>O          | ST<br>—          | Digital I/O.<br>SPI data out.                                                                                                            |

| RC6/TX/CK<br>RC6<br>TX<br>CK                          | 25               | 44       | 44       | I/O<br>O<br>I/O   | ST<br>—<br>ST    | Digital I/O.<br>USART asynchronous transmit.<br>USART synchronous clock (see related RX/DT).                                             |

| RC7/RX/DT<br>RC7<br>RX<br>DT                          | 26               | 1        | 1        | I/O<br>I<br>I/O   | ST<br>ST<br>ST   | Digital I/O.<br>USART asynchronous receive.<br>USART synchronous data (see related TX/CK).                                               |

| Legend: TTL = TTL<br>ST = Sch<br>O = Out              | mitt Trig<br>put | gger inp | out with |                   | evels            | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                         |

## TABLE 1-3: PIC18F4220/4320 PINOUT I/O DESCRIPTIONS (CONTINUED)

OD = Open-drain (no diode to VDD) **Note 1:** Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

| Pin Name                       | Pi        | n Numl               | ber          | Pin           | Buffer              | Description                                                                                                         |  |  |  |

|--------------------------------|-----------|----------------------|--------------|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                | PDIP      | TQFP                 | QFN          | Туре          | Туре                | Description                                                                                                         |  |  |  |

| RE0/AN5/RD                     | 8         | 25                   | 25           |               |                     | PORTE is a bidirectional I/O port.                                                                                  |  |  |  |

| RE0<br>AN5<br>RD               |           |                      |              | I/O<br>I<br>I | ST<br>Analog<br>TTL | Digital I/O.<br>Analog input 5.<br>Read control for Parallel Slave Port<br>(see also WR and CS pins).               |  |  |  |

| RE1/AN6/WR<br>RE1<br>AN6<br>WR | 9         | 26                   | 26           | I/O<br>I<br>I | ST<br>Analog<br>TTL | Digital I/O.<br>Analog input 6.<br>Write <u>control for</u> Parallel Slave Port<br>(see CS and RD pins).            |  |  |  |

| RE2/AN7/CS<br>RE2<br>AN7<br>CS | 10        | 27                   | 27           | I/O<br>I<br>I | ST<br>Analog<br>TTL | Digital I/O.<br>Analog input 7.<br>Chip select control fo <u>r P</u> arallel Slave Port<br>(see related RD and WR). |  |  |  |

| RE3                            | 1         | 18                   | 18           |               | _                   | See MCLR/VPP/RE3 pin.                                                                                               |  |  |  |

| Vss                            | 12,<br>31 | 6, 29                | 6, 30,<br>31 | Ρ             |                     | Ground reference for logic and I/O pins.                                                                            |  |  |  |

| Vdd                            | 11, 32    | 7, 28                | 7, 8<br>29   | Ρ             |                     | Positive supply for logic and I/O pins.                                                                             |  |  |  |

| NC                             |           |                      | 13,<br>28    | NC            | NC                  | No connect.                                                                                                         |  |  |  |

| Legend: TTL = TTL<br>ST = Schr |           | tible inp<br>ger inp |              | CMOS          | 6 levels            | CMOS = CMOS compatible input or output<br>I = Input                                                                 |  |  |  |

#### **TABLE 1-3**: PIC18F4220/4320 PINOUT I/O DESCRIPTIONS (CONTINUED)

O = Output

Ρ = Power

OD = Open-drain (no diode to VDD)

Note 1: Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

#### 4.1 Power-on Reset (POR)

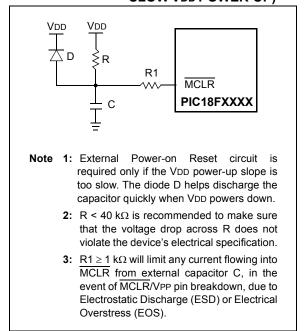

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, just tie the MCLR pin through a resistor (1k to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

FIGURE 4-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

### 4.2 Power-up Timer (PWRT)

The Power-up Timer (PWRT) of the PIC18F2X20/4X20 devices is an 11-bit counter, which uses the INTRC source as the clock input. This yields a count of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter #33 for details.

The PWRT is enabled by clearing Configuration bit, PWRTEN.

### 4.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most power-managed modes.

#### 4.4 PLL Lock Time-out

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 4.5 Brown-out Reset (BOR)

A Configuration bit, BOREN, can disable (if clear/ programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below VBOR (parameter D005) for greater than TBOR (parameter #35), the brown-out situation will reset the chip. A Reset may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR. If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay TPWRT (parameter #33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay. Enabling BOR Reset does not automatically enable the PWRT.

### 4.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, after the POR pulse has cleared, PWRT time-out is invoked (if enabled). Then, the OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

Table 4-2 shows the Reset conditions for some Special Function Registers, while Table 4-3 shows the Reset conditions for all the registers.

### 5.3 Fast Register Stack

A "fast return" option is available for interrupts. A Fast Register Stack is provided for the STATUS, WREG and BSR registers and are only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers if the RETFIE, FAST instruction is used to return from the interrupt.

All interrupt sources will push values into the stack registers. If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. Users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt.

If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

|                 | -                       |

|-----------------|-------------------------|

| CALL SUB1, FAST | ;STATUS, WREG, BSR      |

|                 | ;SAVED IN FAST REGISTER |

|                 | ;STACK                  |

| •               |                         |

| •               |                         |

|                 |                         |

| SUB1 •          |                         |

| •               |                         |

| RETURN FAST     | ;RESTORE VALUES SAVED   |

|                 | ;IN FAST REGISTER STACK |

|                 |                         |

### 5.4 PCL, PCLATH and PCLATU

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21-bits wide. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register may be performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

The contents of PCLATH and PCLATU will be transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 5.8.1** "**Computed** GOTO").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

#### 6.3 Reading the Flash Program Memory

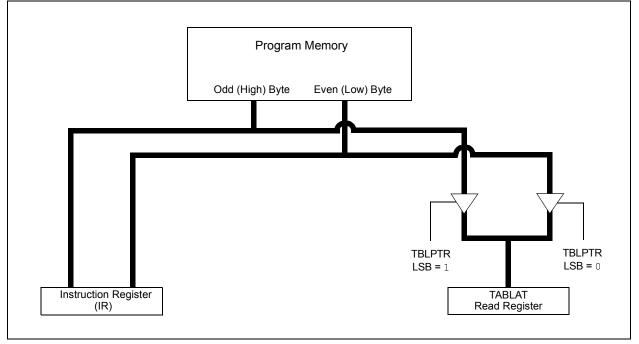

The TBLRD instruction is used to retrieve data from program memory and place it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing a TBLRD instruction places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base             |

|-----------|---------|-----------------|---|---------------------------------------|

|           | MOVWF   | TBLPTRU         | ; | address of the word                   |

|           | MOVLW   | CODE_ADDR_HIGH  |   |                                       |

|           | MOVWF   | TBLPTRH         |   |                                       |

|           | MOVLW   | CODE ADDR LOW   |   |                                       |

|           | MOVWF   | TBLPTRL         |   |                                       |

| READ_WORD |         |                 |   |                                       |

|           | TBLRD*+ |                 | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD EVEN       |   |                                       |

|           | TBLRD*+ | _               | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD_ODD        |   |                                       |

|           |         |                 |   |                                       |

#### 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Flag registers (PIR1, PIR2).

- **Note 1:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

#### REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0                            | R-0                                                | R-0            | R/W-0                         | R/W-0            | R/W-0           | R/W-0  |

|----------------------|----------------------------------|----------------------------------------------------|----------------|-------------------------------|------------------|-----------------|--------|

| PSPIF <sup>(1)</sup> | ADIF                             | RCIF                                               | TXIF           | SSPIF                         | CCP1IF           | TMR2IF          | TMR1IF |

| bit 7                |                                  |                                                    |                | •                             |                  |                 | bit 0  |

|                      |                                  |                                                    |                |                               |                  |                 |        |

| Legend:              | - F.H                            |                                                    | L :4           |                               |                  | l (0)           |        |

| R = Readable         |                                  | W = Writable                                       |                | •                             | mented bit, read |                 |        |

| -n = Value at        | PUR                              | '1' = Bit is set                                   |                | '0' = Bit is cle              | eared            | x = Bit is unkr | lown   |

| bit 7                | PSPIF: Para                      | llel Slave Port F                                  | Read/Write Inf | terrupt Flag bit <sup>(</sup> | (1)              |                 |        |

|                      | 1 = A read o                     |                                                    | ion has taken  |                               | e cleared in sof | tware)          |        |

| bit 6                | ADIF: A/D C                      | onverter Interru                                   | pt Flag bit    |                               |                  |                 |        |

|                      |                                  | conversion com                                     |                | be cleared in s               | oftware)         |                 |        |

| 6.4 F                |                                  | conversion is r                                    | •              |                               |                  |                 |        |

| bit 5                |                                  | T Receive Inter                                    |                | is full (cleared              | when RCREG i     | s read)         |        |

|                      |                                  | ART receive but                                    |                |                               |                  | 51000           |        |

| bit 4                | TXIF: USAR                       | T Transmit Inter                                   | rupt Flag bit  |                               |                  |                 |        |

|                      |                                  | ART transmit bu<br>ART transmit bu                 |                | is empty (clear               | red when TXRE    | G is written)   |        |

| bit 3                | SSPIF: Mast                      | er Synchronous                                     | Serial Port I  | nterrupt Flag b               | it               |                 |        |

|                      |                                  | smission/recept<br>o transmit/recei                |                | te (must be cle               | ared in software | e)              |        |

| bit 2                | CCP1IF: CC                       | P1 Interrupt Fla                                   | g bit          |                               |                  |                 |        |

|                      |                                  | <u>le:</u><br>register capture<br>1 register captu |                | ust be cleared                | in software)     |                 |        |

|                      |                                  |                                                    |                |                               | cleared in softw | /are)           |        |

|                      | <u>PWM mode:</u><br>Unused in th |                                                    |                |                               |                  |                 |        |

| bit 1                | TMR2IF: TM                       | R2 to PR2 Mate                                     | ch Interrupt F | lag bit                       |                  |                 |        |

|                      |                                  | PR2 match oc<br>2 to PR2 match                     | •              | be cleared in s               | oftware)         |                 |        |

| bit 0                | TMR1IF: TM                       | R1 Overflow Int                                    | terrupt Flag b | it                            |                  |                 |        |

|                      |                                  | egister overflow<br>egister did not o              |                | leared in softw               | vare)            |                 |        |

|                      |                                  |                                                    |                |                               |                  |                 |        |

Note 1: This bit is reserved on PIC18F2X20 devices; always maintain this bit clear.

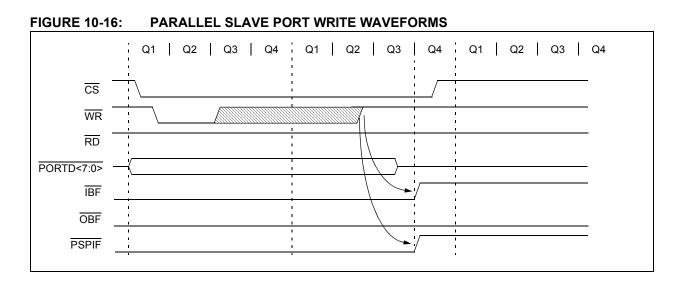

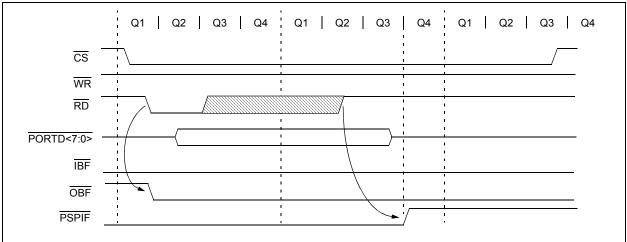

#### FIGURE 10-17: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 10-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7                                             | Bit 6         | Bit 5   | Bit 4   | Bit 3 | Bit 2     | Bit 1        | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------------------------------------------------|---------------|---------|---------|-------|-----------|--------------|--------|----------------------|---------------------------------|

| PORTD  | Port Data Latch when written; Port pins when read |               |         |         |       |           |              |        |                      | uuuu uuuu                       |

| LATD   | LATD Data                                         | a Latch bit   | s       |         |       |           |              |        | XXXX XXXX            | uuuu uuuu                       |

| TRISD  | PORTD D                                           | ata Directi   | on bits |         |       |           |              |        | 1111 1111            | 1111 1111                       |

| PORTE  | _                                                 | _             | _       | _       | RE3   | RE2       | RE1          | RE0    | qxxx                 | quuu                            |

| LATE   | _                                                 | _             | _       | _       | _     | LATE Data | a Latch bits |        | xxx                  | uuu                             |

| TRISE  | IBF                                               | OBF           | IBOV    | PSPMODE | _     | PORTE D   | ata Directio | n bits | 0000 -111            | 0000 -111                       |

| INTCON | GIE/<br>GIEH                                      | PEIE/<br>GIEL | TMR0IF  | INTOIE  | RBIE  | TMR0IF    | INTOIF       | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF                                             | ADIF          | RCIF    | TXIF    | SSPIF | CCP1IF    | TMR2IF       | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE                                             | ADIE          | RCIE    | TXIE    | SSPIE | CCP1IE    | TMR2IE       | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP                                             | ADIP          | RCIP    | TXIP    | SSPIP | CCP1IP    | TMR2IP       | TMR1IP | 1111 1111            | 1111 1111                       |

| ADCON1 | —                                                 | —             | VCFG1   | VCFG0   | PCFG3 | PCFG2     | PCFG1        | PCFG0  | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

## 14.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers: TMR3H and TMR3L)

- Readable and writable (both registers)

- · Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Figure 14-1 is a simplified block diagram of the Timer3 module.

Register 14-1 shows the Timer3 Control register. This register controls the operating mode of the Timer3 module and sets the CCP clock source.

Register 12-1 shows the Timer1 Control register. This register controls the operating mode of the Timer1 module, as well as contains the Timer1 Oscillator Enable bit (T1OSCEN) which can be a clock source for Timer3.

#### REGISTER 14-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

| Legend:      |                      |                                                                                     |                                                    |                                        |

|--------------|----------------------|-------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|

| R = Readal   | ole bit              | W = Writable bit                                                                    | U = Unimplemented bit                              | t, read as '0'                         |

| -n = Value a | at POR               | '1' = Bit is set                                                                    | '0' = Bit is cleared                               | x = Bit is unknown                     |

| bit 7        | <b>RD16</b> : 16     | -Bit Read/Write Mode Enab                                                           | le bit                                             |                                        |

|              |                      | oles register read/write of Tin<br>oles register read/write of Tin                  |                                                    |                                        |

| bit 6, 3     | T3CCP2:              | T3CCP1: Timer3 and Timer                                                            | 1 to CCPx Enable bits                              |                                        |

|              | 01 = Tim<br>Tim      | er3 is the capture/compare o<br>er1 is the capture/compare o                        |                                                    |                                        |

| bit 5-4      | T3CKPS               | 1:T3CKPS0: Timer3 Input C                                                           | lock Prescale Select bits                          |                                        |

|              |                      | Prescale value                                                                      |                                                    |                                        |

|              |                      | Prescale value<br>Prescale value                                                    |                                                    |                                        |

|              |                      | Prescale value                                                                      |                                                    |                                        |

| bit 2        |                      | : Timer3 External Clock Inpu<br>le if the device clock comes                        | t Synchronization Control bit from Timer1/Timer3.) |                                        |

|              | 1 = Do no            | I <u>R3CS = 1:</u><br>ot synchronize external clock<br>nronize external clock input | (input                                             |                                        |

|              |                      | I <u>R3CS = 0:</u><br>ignored. Timer3 uses the in                                   | ternal clock when TMR3CS =                         | = 0.                                   |

| bit 1        | TMR3CS               | : Timer3 Clock Source Selec                                                         | ct bit                                             |                                        |

|              |                      | rnal clock input from Timer1 o<br>nal clock (Fosc/4)                                | oscillator or T13CKI (on the ris                   | sing edge after the first falling edge |

| bit 0        | TMR3ON               | : Timer3 On bit                                                                     |                                                    |                                        |

|              | 1 = Enat<br>0 = Stop | oles Timer3<br>s Timer3                                                             |                                                    |                                        |

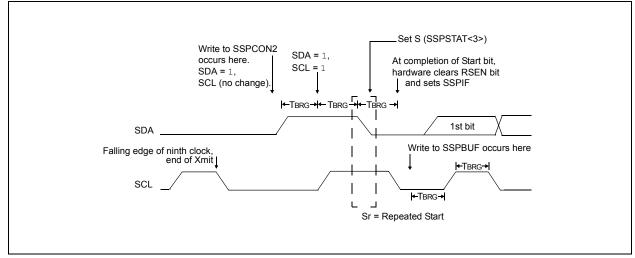

#### 17.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 17.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

### FIGURE 17-20: REPEAT START CONDITION WAVEFORM

#### REGISTER 18-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0         | R/W-0                                                                  | R/W-0                                                                              | R/W-0           | R/W-0             | R-0              | R-0               | R-x     |

|---------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-------------------|---------|

| SPEN          | RX9                                                                    | SREN                                                                               | CREN            | ADDEN             | FERR             | OERR              | RX9D    |

| bit 7         |                                                                        | L                                                                                  |                 |                   |                  |                   | bit     |

|               |                                                                        |                                                                                    |                 |                   |                  |                   |         |

| Legend:       |                                                                        |                                                                                    |                 |                   |                  |                   |         |

| R = Readabl   | e bit                                                                  | W = Writable                                                                       | bit             | U = Unimplen      | nented bit, read | d as '0'          |         |

| -n = Value at | POR                                                                    | '1' = Bit is set                                                                   |                 | '0' = Bit is clea | ared             | x = Bit is unkr   | nown    |

| bit 7         | SPEN: Seria                                                            | al Port Enable bi                                                                  | t               |                   |                  |                   |         |

|               |                                                                        | ort enabled (con                                                                   |                 | and TX/CK pir     | ns as serial por | t pins)           |         |

|               | •                                                                      | ort disabled (hel                                                                  | •               | ·                 |                  | . ,               |         |

| bit 6         | <b>RX9:</b> 9-Bit F                                                    | Receive Enable I                                                                   | oit             |                   |                  |                   |         |

|               |                                                                        | 9-bit reception<br>8-bit reception                                                 |                 |                   |                  |                   |         |

| bit 5         | SREN: Sing                                                             | le Receive Enat                                                                    | ole bit         |                   |                  |                   |         |

|               | <u>Asynchrono</u><br>Don't care.                                       | <u>us mode:</u>                                                                    |                 |                   |                  |                   |         |

|               | 1 = Enable<br>0 = Disable                                              | <u>is mode – Maste</u><br>s single receive<br>s single receive<br>eared after rece |                 | ete               |                  |                   |         |

|               |                                                                        | s mode – Slave:                                                                    |                 |                   |                  |                   |         |

| bit 4         | CREN: Con                                                              | tinuous Receive                                                                    | Enable bit      |                   |                  |                   |         |

|               | Asynchrono<br>1 = Enables<br>0 = Disables<br>Synchronou<br>1 = Enables | s receiver<br>s receiver                                                           | eive until enab | ble bit, CREN, is | s cleared (CRE   | N overrides SR    | EN)     |

|               | 0 = Disables                                                           | s continuous rec                                                                   | eive            |                   |                  |                   |         |

| bit 3         |                                                                        | Idress Detect En                                                                   |                 |                   |                  |                   |         |

|               | 1 = Enables                                                            | <u>us mode 9-bit (F</u><br>s address detect<br>s address detec                     | ion, enables i  |                   |                  |                   |         |

| bit 2         | FERR: Fran                                                             | ning Error bit                                                                     |                 |                   |                  |                   |         |

|               | 1 = Framing<br>0 = No fram                                             | ı error (can be u<br>ing error                                                     | odated by rea   | ding RCREG re     | egister and rece | eiving next valio | l byte) |

| bit 1         | OERR: Ove                                                              | rrun Error bit                                                                     |                 |                   |                  |                   |         |

|               | 1 = Overrun<br>0 = No over                                             | error (can be cl<br>run error                                                      | eared by clea   | ring bit CREN)    |                  |                   |         |

| bit 0         | <b>RX9D:</b> 9th b                                                     | oit of Received D                                                                  | )ata            |                   |                  |                   |         |

|               |                                                                        |                                                                                    |                 |                   |                  |                   |         |

#### REGISTER 23-12: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F2220/2320/4220/4320 DEVICES

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:                      |                      |                                     |

|------------------------------|----------------------|-------------------------------------|

| R = Read-only bit            | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is un | programmed           | u = Unchanged from programmed state |

| bit 7-5 | DEV2:DEV0: Device ID bits                            |

|---------|------------------------------------------------------|

|         | 000 = PIC18F2320                                     |

|         | 001 = PIC18F4320                                     |

|         | 100 = PIC18F2220                                     |

|         | 101 = PIC18F4220                                     |

| bit 4-0 | REV3:REV0: Revision ID bits                          |

|         | These bits are used to indicate the device revision. |

#### REGISTER 23-13: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F2220/2320/4220/4320 DEVICES

| R                    | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV10 <sup>(1)</sup> | DEV9 <sup>(1)</sup> | DEV8 <sup>(1)</sup> | DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> |

| bit 7                |                     |                     |                     |                     |                     |                     | bit 0               |

| Legend:                      |                      |                                     |

|------------------------------|----------------------|-------------------------------------|

| R = Read-only bit            | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is un | programmed           | u = Unchanged from programmed state |

bit 7-0 **DEV10:DEV3:** Device ID bits These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number. 0000 0101 = PIC18F2220/2320/4220/4320 devices

**Note 1:** These values for DEV10:DEV3 may be shared with other devices. The specific device is always identified by using the entire DEV10:DEV0 bit sequence.

After Instruction

If Carry PC If Carry PC

= = =

| ANDWF                                                                                                                                                                                                                                                                                                  | AND W with f                     |             | BC                                                              | Branch if                     | Carry                  |                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------|-----------------------------------------------------------------|-------------------------------|------------------------|-----------------|

| Syntax:                                                                                                                                                                                                                                                                                                | [label] ANDWF f                  | ,d [,a]]    | Syntax:                                                         | [ <i>label</i> ] E            | BC n                   |                 |

| Operands:                                                                                                                                                                                                                                                                                              | $0 \leq f \leq 255$              |             | Operands:                                                       | -128 ≤ n ≤                    | ≤ <b>12</b> 7          |                 |

|                                                                                                                                                                                                                                                                                                        | d ∈ [0,1]<br>a ∈ [0,1]           |             | Operation:                                                      | if Carry bi<br>(PC) + 2 ·     | t is '1',<br>+ 2n → PC |                 |

| Operation:                                                                                                                                                                                                                                                                                             | (W) .AND. (f) $\rightarrow$ dest |             | Status Affect                                                   | ed: None                      |                        |                 |

| Status Affected:                                                                                                                                                                                                                                                                                       | N, Z                             |             | Encoding:                                                       | 1110                          | 0010 nn                | nn nnnn         |

| Encoding:                                                                                                                                                                                                                                                                                              | 0001 01da ff                     | ff ffff     | Description:                                                    | If the Car                    | ry bit is '1', th      | ien the         |

| Description: The contents of W are AND'ed with<br>register 'f'. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected. If 'a' is '1', the BSR will<br>not be overridden (default). |                                  |             | The 2's co<br>added to<br>have incre<br>instruction<br>PC + 2 + | the PC. Sinc<br>emented to fe |                        |                 |

| Words:                                                                                                                                                                                                                                                                                                 | 1                                |             | Words:                                                          | 1                             |                        |                 |

| Cycles:                                                                                                                                                                                                                                                                                                | 1                                |             | Cycles:                                                         | 1(2)                          |                        |                 |

| Q Cycle Activity:                                                                                                                                                                                                                                                                                      |                                  |             | Q Cycle Act                                                     | ivity:                        |                        |                 |

| Q1                                                                                                                                                                                                                                                                                                     | Q2 Q3                            | Q4          | If Jump:                                                        |                               |                        | _               |

| Decode                                                                                                                                                                                                                                                                                                 | Read Process                     | Write to    | Q1                                                              | Q2                            | Q3                     | Q4              |

|                                                                                                                                                                                                                                                                                                        | register 'f' Data                | destination | Decod                                                           | e Read literal<br>'n'         | Process<br>Data        | Write to PC     |

| Example:                                                                                                                                                                                                                                                                                               | ANDWF REG, W                     |             | No<br>operati                                                   | No<br>on operation            | No<br>operation        | No<br>operation |

| Before Instru                                                                                                                                                                                                                                                                                          |                                  |             | If No Jump:                                                     |                               |                        |                 |

| W<br>REG                                                                                                                                                                                                                                                                                               | = 0x17<br>= 0xC2                 |             | Q1                                                              | Q2                            | Q3                     | Q4              |

| After Instruct                                                                                                                                                                                                                                                                                         | ion                              |             | Decod                                                           | e Read literal                | Process<br>Data        | No<br>operation |

| W<br>REG                                                                                                                                                                                                                                                                                               | = 0x02<br>= 0xC2                 |             |                                                                 |                               | Dulu                   | operation       |

| REG                                                                                                                                                                                                                                                                                                    | = 0xC2                           |             | Example:                                                        | HERE                          | BC JUMP                | )               |

|                                                                                                                                                                                                                                                                                                        |                                  |             | Before I<br>PC                                                  | nstruction<br>= ac            | Idress (HERE           | )               |

1; address (JUMP) 0; address (HERE + 2)

| BTG                      | Bit Toggle                                                                                | e f                                          |                                       |                            | BO    | /                              | Branch if                                             | Overflow                                 |                 |

|--------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------|----------------------------|-------|--------------------------------|-------------------------------------------------------|------------------------------------------|-----------------|

| Syntax:                  | [ <i>label</i> ] B                                                                        | TG f,b[,a]                                   |                                       |                            | Synt  | Syntax: [ <i>label</i> ] BOV n |                                                       | OV n                                     |                 |

| Operands:                | 0 ≤ f ≤ 255                                                                               | 5                                            |                                       |                            | Ope   | rands:                         | -128 ≤ n ≤                                            | 127                                      |                 |

|                          | 0 ≤ b < 7<br>a ∈ [0,1]                                                                    |                                              |                                       |                            | Ope   | ration:                        | if Overflow<br>(PC) + 2 +                             |                                          |                 |

| Operation:               | $(\overline{f} < b >) \to f$                                                              | <b></b>                                      |                                       |                            | State | us Affected:                   | None                                                  |                                          |                 |

| Status Affected:         | None                                                                                      |                                              |                                       |                            | Enc   | odina:                         | 1110                                                  | 0100 nn                                  | nn nnnn         |

| Encoding:                | 0111                                                                                      | bbba                                         | ffff                                  | ffff                       |       | cription:                      | -                                                     | flow bit is '1                           |                 |

| Description:             | Bit 'b' in da<br>inverted. I'<br>will be sele<br>value. If 'a<br>selected a<br>(default). | f 'a' is '0', '<br>ected, ove<br>' = 1, ther | the Acces<br>erriding the<br>the bank | s Bank<br>e BSR<br>will be |       |                                | added to t<br>have incre<br>instruction<br>PC + 2 + 2 | mplement n<br>he PC. Sinc<br>mented to f |                 |

| Words:                   | 1                                                                                         |                                              |                                       |                            | Wor   | de                             | 1                                                     |                                          |                 |

| Cycles:                  | 1                                                                                         | 1                                            |                                       |                            |       | -                              |                                                       |                                          |                 |

| Q Cycle Activity:        |                                                                                           |                                              |                                       |                            | Cyc   |                                | 1(2)                                                  |                                          |                 |

| Q1                       | Q2                                                                                        | Q3                                           | Q                                     |                            |       | Q Cycle Activity:<br>If Jump:  |                                                       |                                          |                 |

| Decode                   | Read<br>register 'f'                                                                      | Process<br>Data                              | Wri<br>regist                         |                            | 11 51 | Q1                             | Q2                                                    | Q3                                       | Q4              |

| Example:                 | BTG F                                                                                     | PORTC, 4                                     |                                       |                            |       | Decode                         | Read literal<br>'n'                                   | Process<br>Data                          | Write to PC     |

| Before Instru            |                                                                                           |                                              |                                       |                            |       | No                             | No                                                    | No                                       | No              |

| PORTC                    |                                                                                           | 101 <b>[0x75</b>                             | 5]                                    |                            | LE NI | operation                      | operation                                             | operation                                | operation       |

| After Instructi          | ion:                                                                                      | -                                            | -                                     |                            | IT N  | o Jump:                        | 00                                                    | 00                                       | <u></u>         |

| PORTC = 0110 0101 [0x65] |                                                                                           |                                              |                                       | Q1                         | Q2    | Q3                             | Q4                                                    |                                          |                 |

|                          |                                                                                           |                                              |                                       |                            |       | Decode                         | Read literal<br>'n'                                   | Process<br>Data                          | No<br>operation |

|                          |                                                                                           |                                              |                                       |                            |       | L                              |                                                       | Data                                     | operation       |

|                          |                                                                                           |                                              |                                       |                            | Exa   | <u>mple</u> :                  | HERE                                                  | BOV JUME                                 | 2               |

|                          |                                                                                           |                                              |                                       |                            |       | Before Instr                   | uction                                                |                                          |                 |

PC

After Instruction

If Overflow = PC = If Overflow = PC =

=

1;

address (HERE)

address (JUMP) 0; address (HERE + 2)

| Syntax: $[ label ]$ CPFSGT $f [a]$ Operands: $0 \le f \le 255$ $a \in [0,1]$ Operands: $0 \le f \le 255$ $a \in [0,1]$ Operands: $0 \le f \le 255$ Operands: $0 \le f \le 255$ $a \in [0,1]$ Operands: $0 \le f \le 255$ Description: $0 \ge f \le 255$ Compares the contents of data<br>memory location 1 to the contents $0 \le f \le 255$ $a \in [0,1]$ Operands: $0 \le f \le 255$ Description:Compares the contents of data<br>memory location 1 to the contentsIf the contents of V are greater than<br>the contents of V REG, then the<br>fetched instruction is discarded and<br>a sof is executed instead, making its<br>tis a two-cycle instruction. If a 's 's '', the Access Bank will be<br>selected. coverding the DBR value,<br>(default).Words:1Cycles:1(2)<br>Note:Note:3 cycles if skip and followed<br>by a 2-word instruction.Q 1Q2Q3Q1Q2Q3Q1Q2Q3Q1Q2Q3Q1Q2Q3Q1Q2Q3Q1Q2Q3Q1Q2Q3Q1Q2Q3Q1Q2Q3Q2Q3Q1Q2Q3Q2Q3Q1Q2Q3Q2Q3Q1Q2Q3Q2Q3Q1Q2Q3Q2Q3Q1Q2Q3Q2Q3Q1Q2Q3<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CPFSGT                                                                                                         | Compare                                                                                                                                                       | f with W, Sk                                                                                                                                                                 | tip if f > W                                                                                                                                                              | CPF        | SLT          | Compar                                                                                                                           | e f with W, Sl                                                                                                                                                              | kip if f < W                                                                                                                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| $\begin{array}{ccccc} a \in [0,1] \\ Operation: (f) = (W), \\ (unsigned comparison) \\ Status Affected: None \\ Encoding: 0110 0104 rfff fff fff \\ Description: Compares the contents of data memory location if to the contents of the contents of the performing an unsigned subtraction. If a file contents of the greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If a file contents of the BSR value (default). \\ Words: 1 \\ Cycles: 1 (C) \\ Words: 1 \\ Cycles: 1 (C) \\ Words: 1 \\ Cycles: 1 (C) \\ Words: 3 cycles if skip and followed by a 2-word instruction. \\ Q Cycle Activity: Q1 Q2 Q3 Q4 \\ If skip in Q1 Q2 Q3 Q4 \\ If skip in to looperation operation o$                                                                                                                                                                                                                                                                                                                                                                         | Syntax:                                                                                                        | [label] (                                                                                                                                                     | CPFSGT f[                                                                                                                                                                    | ,a]                                                                                                                                                                       | Syn        | tax:         | [ label ]                                                                                                                        | CPFSLT f[                                                                                                                                                                   | ,a]                                                                                                                              |  |