Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4320-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din New-                                                     | Pin N | umber | Pin                     | Buffer                              | Description                                                                                                                                                      |  |  |

|--------------------------------------------------------------|-------|-------|-------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                     | PDIP  | SOIC  | Туре                    | Туре                                | Description                                                                                                                                                      |  |  |

| MCLR/VPP<br>MCLR                                             | 1     | 1     | I                       | ST                                  | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low Rese<br>to the device.                             |  |  |

| VPP                                                          |       |       | Р                       |                                     | Programming voltage input.                                                                                                                                       |  |  |

| OSC1/CLKI/RA7<br>OSC1<br>CLKI                                | 9     | 9     | 1                       | ST<br>CMOS                          | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode, CMOS otherwise. |  |  |

| RA7                                                          |       |       | ı<br>1/0                | TTL                                 | External clock source input. Always associated with pin<br>function OSC1. (See related OSC1/CLKI, OSC2/CLKO pins.<br>General purpose I/O pin.                    |  |  |

| OSC2/CLKO/RA6<br>OSC2                                        | 10    | 10    | 0                       |                                     | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonator                                                               |  |  |

| CLKO                                                         |       |       | 0                       | —                                   | in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKO which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate                   |  |  |

| RA6                                                          |       |       | I/O                     | TTL                                 | General purpose I/O pin.                                                                                                                                         |  |  |

| RA0/AN0<br>RA0<br>AN0                                        | 2     | 2     | I/O<br>I                | TTL<br>Analog                       | PORTA is a bidirectional I/O port.<br>Digital I/O.<br>Analog input 0.                                                                                            |  |  |

| RA1/AN1<br>RA1<br>AN1                                        | 3     | 3     | I/O<br>I                | TTL<br>Analog                       | Digital I/O.<br>Analog input 1.                                                                                                                                  |  |  |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF          | 4     | 4     | I/O<br> <br> <br>0      | TTL<br>Analog<br>Analog<br>Analog   | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (low) input.<br>Comparator reference voltage output.                                                    |  |  |

| RA3/AN3/Vref+<br>RA3<br>AN3<br>Vref+                         | 5     | 5     | I/O<br>I<br>I           | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (high) input.                                                                                           |  |  |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT                     | 6     | 6     | I/O<br>I<br>O           | ST/OD<br>ST                         | Digital I/O. Open drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                       |  |  |

| RA5/AN4/SS/LVDIN/C2OUT<br>RA5<br>AN4<br>SS<br>LVDIN<br>C2OUT | 7     | 7     | I/O<br> <br> <br> <br>0 | TTL<br>Analog<br>TTL<br>Analog<br>— | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Low-Voltage Detect input.<br>Comparator 2 output.                                                  |  |  |

| RA6                                                          |       |       |                         |                                     | See the OSC2/CLKO/RA6 pin.                                                                                                                                       |  |  |

| RA7                                                          |       |       |                         |                                     | See the OSC1/CLKI/RA7 pin.                                                                                                                                       |  |  |

| Legend: TTL = TTL comp<br>ST = Schmitt Tr<br>O = Output      |       |       | ith CM                  | OS levels                           | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                 |  |  |

#### **TABLE 1-2:** PIC18F2220/2320 PINOUT I/O DESCRIPTIONS

O = Output OD = Open-drain (no diode to VDD)

Note 1: Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

### 3.0 POWER-MANAGED MODES

The PIC18F2X20 and PIC18F4X20 devices offer a total of six operating modes for more efficient power management (see Table 3-1). These operating modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- · Sleep mode

- Idle modes

- Run modes

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or INTOSC multiplexer); the Sleep mode does not use a clock source.

The clock switching feature offered in other PIC18 devices (i.e., using the Timer1 oscillator in place of the primary oscillator) and the Sleep mode offered by all PIC<sup>®</sup> devices (where all system clocks are stopped) are both offered in the PIC18F2X20/4X20 devices (SEC\_RUN and Sleep modes, respectively). However, additional power-managed modes are available that allow the user greater flexibility in determining what portions of the device are operating. The power-managed modes are event driven; that is, some specific event must occur for the device to enter or (more particularly) exit these operating modes.

For PIC18F2X20/4X20 devices, the power-managed modes are invoked by using the existing SLEEP instruction. All modes exit to PRI\_RUN mode when triggered by an interrupt, a Reset, or a WDT time-out (PRI\_RUN mode is the normal full-power execution mode; the CPU and peripherals are clocked by the primary oscillator source). In addition, power-managed Run modes may also exit to Sleep mode or their corresponding Idle mode.

#### 3.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires deciding if the CPU is to be clocked or not and selecting a clock source. The IDLEN bit controls CPU clocking while the SC1:SCS0 bits select a clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

#### 3.1.1 CLOCK SOURCES

The clock source is selected by setting the SCS bits of the OSCCON register. Three clock sources are available for use in power-managed Idle modes: the primary clock (as configured in Configuration Register 1H), the secondary clock (Timer1 oscillator) and the internal oscillator block. The secondary and internal oscillator block sources are available for the power-managed modes (PRI\_RUN mode is the normal full-power execution mode; the CPU and peripherals are clocked by the primary oscillator source).

| Mode     | oscco | ON<7,1:0> | Module  | Clocking    | Available Clock and Oscillator Source                                                                        |  |  |

|----------|-------|-----------|---------|-------------|--------------------------------------------------------------------------------------------------------------|--|--|

| wode     | IDLEN | SCS1:SCS0 | CPU     | Peripherals |                                                                                                              |  |  |

| Sleep    | 0     | 00        | Off     | Off         | None – All clocks are disabled                                                                               |  |  |

| PRI_RUN  | 0     | 00        | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC, INTRC <sup>(1)</sup> .<br>This is the normal full-power execution mode. |  |  |

| SEC_RUN  | 0     | 01        | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                                |  |  |

| RC_RUN   | 0     | 1x        | Clocked | Clocked     | Internal Oscillator Block <sup>(1)</sup>                                                                     |  |  |

| PRI_IDLE | 1     | 00        | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                          |  |  |

| SEC_IDLE | 1     | 01        | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                                |  |  |

| RC_IDLE  | 1     | 1x        | Off     | Clocked     | Internal Oscillator Block <sup>(1)</sup>                                                                     |  |  |

#### TABLE 3-1: POWER-MANAGED MODES

Note 1: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

### TABLE 3-3:ACTIVITY AND EXIT DELAY ON WAKE-UP FROM SLEEP MODE OR<br/>ANY IDLE MODE (BY CLOCK SOURCES)

| Clock in<br>Power-Managed                             | Primary System<br>Clock      | Power-Managed          | Clock Ready<br>Status Bit | Activity During Wake-up from<br>Power-Managed Mode |                                           |  |

|-------------------------------------------------------|------------------------------|------------------------|---------------------------|----------------------------------------------------|-------------------------------------------|--|

| Mode                                                  | CIOCK                        | Mode Exit Delay        | (OSCCON)                  | Exit by Interrupt                                  | Exit by Reset                             |  |

|                                                       | LP, XT, HS                   |                        | OSTS                      | CPU and peripherals                                | Not clocked or                            |  |

| Primary System<br>Clock                               | HSPLL                        | 5-10 μs <sup>(5)</sup> | 0315                      | clocked by primary clock                           | Two-Speed                                 |  |

| (PRI_IDLE mode)                                       | EC, RC, INTRC <sup>(1)</sup> | 5-10 µS(*)             | —                         | and executing<br>instructions.                     | Start-up<br>(if enabled) <sup>(3)</sup> . |  |

| (· · · ·· <u>_</u> ·· <u>_</u> ·· <u>_</u> ·········) | INTOSC <sup>(2)</sup>        |                        | IOFS                      |                                                    | (il enabled).                             |  |

|                                                       | LP, XT, HS                   | OST                    | 0010                      | CPU and peripherals                                |                                           |  |

| T1OSC or INTRC <sup>(1)</sup>                         | HSPLL                        | OST + 2 ms             | OSTS                      | clocked by selected                                |                                           |  |

| TIUSC OF INTROVY                                      | EC, RC, INTRC <sup>(1)</sup> | 5-10 μs <sup>(5)</sup> | —                         | power-managed mode<br>clock and executing          |                                           |  |

|                                                       | INTOSC <sup>(2)</sup>        | 5-10 μs <sup>(4)</sup> | IOFS                      | instructions until primary                         |                                           |  |

|                                                       | LP, XT, HS                   | OST                    | OSTS                      | clock source becomes                               |                                           |  |

| INTOSC <sup>(2)</sup>                                 | HSPLL                        | OST + 2 ms             | 0313                      | ready.                                             |                                           |  |

|                                                       | EC, RC, INTRC <sup>(1)</sup> | 5-10 μs <sup>(5)</sup> | —                         |                                                    |                                           |  |

|                                                       | INTOSC <sup>(2)</sup>        | None                   | IOFS                      |                                                    |                                           |  |

|                                                       | LP, XT, HS                   | OST                    | OSTS                      | Not clocked or                                     |                                           |  |

| Sleep mode                                            | HSPLL                        | OST + 2 ms             | 0313                      | Two-Speed Start-up (if                             |                                           |  |

|                                                       | EC, RC, INTRC <sup>(1)</sup> | 5-10 μs <sup>(5)</sup> | _                         | enabled) until primary<br>clock source becomes     |                                           |  |

|                                                       | INTOSC <sup>(2)</sup>        | 5-10 μs <sup>(4)</sup> | IOFS                      | ready <sup>(3)</sup> .                             |                                           |  |

**Note 1:** In this instance, refers specifically to the INTRC clock source.

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

3: Two-Speed Start-up is covered in greater detail in Section 23.3 "Two-Speed Start-up".

4: Execution continues during the INTOSC stabilization period.

5: Required delay when waking from Sleep and all Idle modes. This delay runs concurrently with any other required delays (see Section 3.3 "Idle Modes").

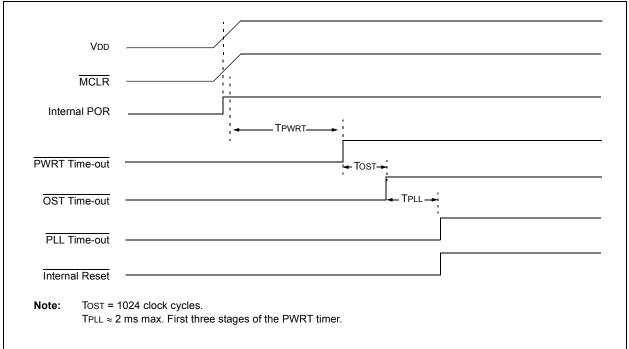

### FIGURE 4-7: TIME-OUT SEQUENCE ON POR W/ PLL ENABLED (MCLR TIED TO VDD)

NOTES:

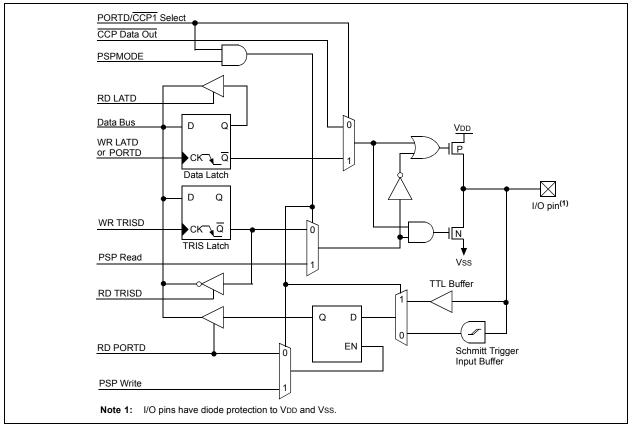

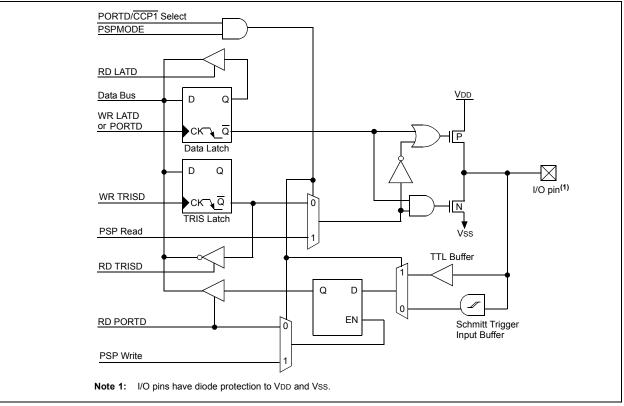

#### 10.4 PORTD, TRISD and LATD Registers

| Note: | PORTD is only available on PIC18F4X20 |

|-------|---------------------------------------|

|       | devices.                              |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Three of the PORTD pins are multiplexed with outputs P1B, P1C and P1D of the Enhanced CCP module. The operation of these additional PWM output pins is covered in greater detail in Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

Note: On a Power-on Reset, these pins are configured as digital inputs.

PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 10.6 "Parallel Slave Port"** for additional information on the Parallel Slave Port (PSP).

| Note: | When the enhanced PWM mode is used        |

|-------|-------------------------------------------|

|       | with either dual or quad outputs, the PSP |

|       | functions of PORTD are automatically      |

|       | disabled.                                 |

#### EXAMPLE 10-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATD  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISD | : Set RD<3:0> as inputs |

|       |       | ; RD<5:4> as outputs    |

|       |       | ; RD<7:6> as inputs     |

|       |       | , 100 as inpaces        |

#### FIGURE 10-11: BLOCK DIAGRAM OF RD7:RD5 PINS

#### FIGURE 10-12: BLOCK DIAGRAM OF RD4:RD0 PINS

#### TABLE 10-7: PORTD FUNCTIONS

| Name         | Bit#  | Buffer Type           | Function                                                                     |

|--------------|-------|-----------------------|------------------------------------------------------------------------------|

| RD0/PSP0     | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 0.                          |

| RD1/PSP1     | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 1.                          |

| RD2/PSP2     | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 2.                          |

| RD3/PSP3     | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 3.                          |

| RD4/PSP4     | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 4.                          |

| RD5/PSP5/P1B | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 5 or Enhanced PWM output P1B. |

| RD6/PSP6/P1C | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 6 or Enhanced PWM output P1C. |

| RD7/PSP7/P1D | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 7 or Enhanced PWM output P1D. |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

#### TABLE 10-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name    | Bit 7     | Bit 6        | Bit 5      | Bit 4   | Bit 3  | Bit 2   | Bit 1       | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------|--------------|------------|---------|--------|---------|-------------|---------|----------------------|---------------------------------|

| PORTD   | RD7       | RD6          | RD5        | RD4     | RD3    | RD2     | RD1         | RD0     | XXXX XXXX            | uuuu uuuu                       |

| LATD    | LATD Data | a Latch Re   | gister     |         |        |         |             |         | XXXX XXXX            | uuuu uuuu                       |

| TRISD   | PORTD D   | ata Directio | on Registe | r       |        |         |             |         | 1111 1111            | 1111 1111                       |

| TRISE   | IBF       | OBF          | IBOV       | PSPMODE | _      | PORTE D | ata Directi | on bits | 0000 -111            | 0000 -111                       |

| CCP1CON | P1M1      | P1M0         | DC1B1      | DC1B0   | CCP1M3 | CCP1M2  | CCP1M1      | CCP1M0  | 0000 0000            | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

#### 12.4 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing Timer1 interrupt enable bit, TMR1IE (PIE1<0>).

#### 12.5 Resetting Timer1 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "Special Event Trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion if the A/D module is enabled (see **Section 15.4.4 "Special Event Trigger"** for more information).

| Note: | The Spe | cial E | Event | Trig | gers from t | he C | CP1  |

|-------|---------|--------|-------|------|-------------|------|------|

|       | module  | will   | not   | set  | interrupt   | flag | bit, |

|       | TMR1IF  | (PIR   | 1<0>  | ·).  |             |      |      |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

#### 12.6 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 high byte buffer. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid due to a rollover between reads. A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

#### 12.7 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 12.2 "Timer1 Oscillator"** above), gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 12-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine, which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the MSbit of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1) as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

#### 15.4 Compare Mode

In Compare mode, the 16-bit CCPR1 (CCPR2) register value is constantly compared against either the TMR1 register pair value, or the TMR3 register pair value. When a match occurs, the RC2/CCP1/P1A (RC1/T10SI/CCP2) pin:

- · Is driven high

- · Is driven low

- · Toggles output (high-to-low or low-to-high)

- Remains unchanged (interrupt only)

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP2M3:CCP2M0). At the same time, interrupt flag bit, CCP1IF (CCP2IF), is set.

#### 15.4.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRISC bit.

**Note:** Clearing the CCP1CON register will force the RC2/CCP1/P1A compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 15.4.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 15.4.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 15.4.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The Special Event Trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable Period register for Timer1.

The special trigger output of CCP2 resets either the TMR1 or TMR3 register pair. Additionally, the CCP2 Special Event Trigger will start an A/D conversion if the A/D module is enabled.

Note: The Special Event Trigger from the CCP2 module will not set the Timer1 or Timer3 interrupt flag bits.

#### FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Reset Timer1 or Timer3 but not set Timer1 or Timer3 interrupt flag bit and set bit GO/DONE (ADCON0<2>) which starts an A/D conversion (CCP2 only) Special Event Trigger Set Flag bit CCP1IF CCPR1H CCPR1L Х O S Output Comparator Logic RC2/CCP1/P1A Match R pin TRISC<2> **Output Enable** CCP1CON<3:0> T3CCP2 0 Mode Select TMR1H TMR1L TMR3H TMR3L Special Event Trigger Set Flag bit CCP2IF T3CCP1 0 T3CCP2 1 S Q Output Comparator Loġic RC1/T1OSI/CCP2 Match R pin TRISC<1> CCPR2H CCPR2L Output Enable CCP2CON<3:0> Mode Select

### 18.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules available in the PIC18F2X20/4X20 family of microcontrollers. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The USART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

The RC6/TX/CK and RC7/RX/DT pins must be configured as shown for use with the Universal Synchronous Asynchronous Receiver Transmitter:

- SPEN (RCSTA<7>) bit must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be cleared (= 0)

Register 18-1 shows the Transmit Status and Control register (TXSTA) and Register 18-2 shows the Receive Status and Control register (RCSTA).

#### 18.1 Asynchronous Operation in Power-Managed Modes

The USART may operate in Asynchronous mode while the peripheral clocks are being provided by the internal oscillator block. This mode makes it possible to remove the crystal or resonator that is commonly connected as the primary clock on the OSC1 and OSC2 pins.

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz. However, this frequency may drift as VDD or temperature changes and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output back to 8 MHz. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source (see **Section 3.6 "INTOSC Frequency Drift**" for more information).

The other method adjusts the value in the Baud Rate Generator since there may be not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

NOTES:

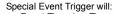

### 23.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO bit in Configuration Register 1H (CONFIG1H<7>).

Two-Speed Start-up is available only if the primary oscillator mode is LP, XT, HS or HSPLL (Crystal-Based modes). Other sources do not require a OST start-up delay; for these, Two-Speed Start-up is disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a POR Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

Because the OSCCON register is cleared on Reset events, the INTOSC (or postscaler) clock source is not initially available after a Reset event; the INTRC clock is used directly at its base frequency. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits IFRC2:IFRC0 immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IFRC2:IFRC0 prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 23.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to **Section 3.1.3 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS1:SCS0 bit settings and issue SLEEP commands before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the system clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the system clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

| BNOV                                                  | Branch if                                                                        | Not Overflo                            | w                                                                             | BNZ         |

|-------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------|-------------|

| Syntax:                                               | [ <i>label</i> ] B                                                               | NOV n                                  |                                                                               | Syn         |

| Operands:                                             | -128 ≤ n ≤                                                                       | 127                                    |                                                                               | Ope         |

| Operation:                                            | if Overflov<br>(PC) + 2 +                                                        | v bit is '0',<br>- 2n $\rightarrow$ PC |                                                                               | Оре         |

| Status Affected:                                      | None                                                                             |                                        |                                                                               | Stat        |

| Encoding:                                             | 1110                                                                             | 0101 nni                               | nn nnnn                                                                       | Enc         |

| Description:                                          | program v<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC + 2 + 2 | he PC. Since<br>mented to fe           | umber '2n' is<br>e the PC will<br>etch the next<br>dress will be<br>uction is | Des         |

| Words:                                                | 1                                                                                |                                        |                                                                               | Wor         |

| Cycles:                                               | 1(2)                                                                             |                                        |                                                                               | Сус         |

| Q Cycle Activity<br>If Jump:                          | :                                                                                |                                        |                                                                               | Q (<br>If J |

| Q1                                                    | Q2                                                                               | Q3                                     | Q4                                                                            | -           |

| Decode                                                | Read literal<br>'n'                                                              | Process<br>Data                        | Write to PC                                                                   |             |

| No                                                    | No                                                                               | No                                     | No                                                                            |             |

| operation                                             | operation                                                                        | operation                              | operation                                                                     | ]<br>If N   |

| If No Jump:<br>Q1                                     | Q2                                                                               | Q3                                     | 04                                                                            | IT IN       |

| Decode                                                | Read literal                                                                     | Process                                | Q4<br>No                                                                      | 1           |

| Decode                                                | 'n'                                                                              | Data                                   | operation                                                                     |             |

| Example:<br>Before Instr<br>PC                        |                                                                                  | BNOV Jump<br>dress (HERE)              |                                                                               | Exa         |

| After Instruc<br>If Overflu<br>PC<br>If Overflu<br>PC | ow = 0;<br>= ad<br>ow = 1;                                                       | dress (Jump)<br>dress (HERE            |                                                                               |             |

| Syntax:                       | [ <i>label</i> ] B                                                               | [ <i>label</i> ] BNZ n                                                                                                            |                                                                            |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| Operands:                     | -128 < n <                                                                       |                                                                                                                                   |                                                                            |  |  |  |  |

| •                             |                                                                                  |                                                                                                                                   |                                                                            |  |  |  |  |

| Operation:                    | if Zero bit<br>(PC) + 2 +                                                        | ,                                                                                                                                 |                                                                            |  |  |  |  |

| Status Affected:              | None                                                                             |                                                                                                                                   |                                                                            |  |  |  |  |

| Encoding:                     | 1110                                                                             | 0001 nni                                                                                                                          | nn nnnn                                                                    |  |  |  |  |

| Description:                  | program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC + 2 + 2 | bit is '0', the<br>vill branch.<br>mplement nu<br>he PC. Since<br>mented to fe<br>, the new ad<br>2n. This instr<br>-cycle instru | umber '2n' is<br>the PC will<br>tch the next<br>dress will be<br>uction is |  |  |  |  |

| Words:                        | 1                                                                                | 1                                                                                                                                 |                                                                            |  |  |  |  |

| Cycles:                       | 1(2)                                                                             | 1(2)                                                                                                                              |                                                                            |  |  |  |  |

| Q Cycle Activity:<br>If Jump: |                                                                                  |                                                                                                                                   |                                                                            |  |  |  |  |

| Q1                            | Q2                                                                               | Q3                                                                                                                                | Q4                                                                         |  |  |  |  |

| Decode                        | Read literal<br>'n'                                                              | Process<br>Data                                                                                                                   | Write to PC                                                                |  |  |  |  |

| No                            | No                                                                               | No                                                                                                                                | No                                                                         |  |  |  |  |

| operation                     | operation                                                                        | operation                                                                                                                         | operation                                                                  |  |  |  |  |

| If No Jump:                   |                                                                                  |                                                                                                                                   |                                                                            |  |  |  |  |

| Q1                            | Q2                                                                               | Q3                                                                                                                                | Q4                                                                         |  |  |  |  |

| Decode                        | Read literal<br>'n'                                                              | Process<br>Data                                                                                                                   | No<br>operation                                                            |  |  |  |  |

|                               |                                                                                  |                                                                                                                                   |                                                                            |  |  |  |  |

| Example:                      | HERE                                                                             | BNZ Jump                                                                                                                          |                                                                            |  |  |  |  |

| Example:<br>Before Instru     | HERE                                                                             | BNZ Jump                                                                                                                          |                                                                            |  |  |  |  |

| PC                             | =           | address (HERE)                                   |

|--------------------------------|-------------|--------------------------------------------------|

| After Instruction              |             |                                                  |

| If Zero<br>PC<br>If Zero<br>PC | =<br>=<br>= | 0;<br>address (Jump)<br>1;<br>address (HERE + 2) |

| Operands: $0 \le k \le 255$ Operation:(W) .OR. $k \to W$ Status Affected:N, ZEncoding: $0000$ 1001 kkkk kkkkDescription:The contents of W are OR'ed with<br>the eight-bit literal 'k'. The result is<br>placed in W.Words:1Cycles:1Q Cycle Activity:Q1 Q2 Q3 Q4DecodeRead<br>literal 'k' DataExample:IORLW0x35Before Instruction<br>W= 0x9A                                                                                                                                                                                | IORLW             | Inclusive OR Lit           | teral with | w         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|------------|-----------|

| Operation:(W) .OR. k $\rightarrow$ WStatus Affected:N, ZEncoding:00001001kkkkDescription:The contents of W are OR'ed with<br>the eight-bit literal 'k'. The result is<br>placed in W.Words:1Cycles:1Q Cycle Activity:Q2Q3Q1Q2Q3Q4DecodeRead<br>literal 'k'DecodeRead<br>literal 'k'ProcessWrite to W0x35Before Instruction<br>W=0x9A                                                                                                                                                                                       | Syntax:           | [label] IORLW              | ′ k        |           |

| Status Affected:       N, Z         Encoding:       0000       1001       kkkk       kkkk         Description:       The contents of W are OR'ed with the eight-bit literal 'k'. The result is placed in W.         Words:       1         Cycles:       1         Q Cycle Activity:         Q1       Q2       Q3       Q4         Decode       Read       Process       Write to W         Iteral 'k'       Data       Vata         Example:       IORLW       0x35         Before Instruction       W       =       0x9A | Operands:         | $0 \leq k \leq 255$        |            |           |

| Encoding:<br>Description:<br>The contents of W are OR'ed with<br>the eight-bit literal 'k'. The result is<br>placed in W.<br>Words:<br>1<br>Cycles:<br>1<br>Q Cycle Activity:<br>Q1<br>Q2<br>Q3<br>Q4<br>Decode<br>Read<br>literal 'k'<br>Data<br>Write to W<br>Example:<br>IORLW<br>0x35<br>Before Instruction<br>W = 0x9A                                                                                                                                                                                                | Operation:        | (W) .OR. $k \rightarrow W$ |            |           |

| Description: The contents of W are OR'ed with<br>the eight-bit literal 'k'. The result is<br>placed in W.<br>Words: 1<br>Cycles: 1<br>Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to W<br>literal 'k' Data Write to W<br>Example: IORLW $0x35$<br>Before Instruction<br>W = 0x9A                                                                                                                                                                                                                         | Status Affected:  | N, Z                       |            |           |

| the eight-bit literal 'k'. The result is<br>placed in W.<br>Words: 1<br>Cycles: 1<br>Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to W<br>literal 'k' Data<br>Example: IORLW 0x35<br>Before Instruction<br>W = 0x9A                                                                                                                                                                                                                                                                                       | Encoding:         | 0000 1001                  | kkkk       | kkkk      |

| Cycles: 1<br>Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to W<br>literal 'k' Data Vrite to W<br>Example: IORLW 0x35<br>Before Instruction<br>W = 0x9A                                                                                                                                                                                                                                                                                                                                                    | Description:      | the eight-bit litera       |            | •••       |

| Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to W<br>literal 'k' Data<br>Example: IORLW 0x35<br>Before Instruction<br>W = 0x9A                                                                                                                                                                                                                                                                                                                                                                            | Words:            | 1                          |            |           |

| Q1     Q2     Q3     Q4       Decode     Read<br>literal 'k'     Process<br>Data     Write to W       Example:     IORLW     0x35       Before Instruction<br>W     =     0x9A                                                                                                                                                                                                                                                                                                                                             | Cycles:           | 1                          |            |           |

| Decode     Read<br>literal 'k'     Process<br>Data     Write to W       Example:     IORLW     0x35       Before Instruction<br>W     = 0x9A                                                                                                                                                                                                                                                                                                                                                                               | Q Cycle Activity: |                            |            |           |

| literal 'k'     Data       Example:     IORLW     0x35       Before Instruction     W     = 0x9A                                                                                                                                                                                                                                                                                                                                                                                                                           | Q1                | Q2 Q                       | 3          | Q4        |

| Before Instruction<br>W = 0x9A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Decode            |                            |            | rite to W |

| W = 0x9A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Example:          | IORLW 0x35                 |            |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Before Instru     | ction                      |            |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W                 | = 0x9A                     |            |           |

| After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | After Instruct    | on                         |            |           |

| W = 0xBF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W                 | = 0xBF                     |            |           |

|                              | Inclusive                                                                 | OR W v                            | vith f                            |                                          |

|------------------------------|---------------------------------------------------------------------------|-----------------------------------|-----------------------------------|------------------------------------------|

| Syntax:                      | [label]                                                                   | ORWF                              | f [,d                             | [,a]]                                    |

| Operands:                    | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                     | 5                                 |                                   |                                          |

| Operation:                   | (W) .OR. (                                                                | $f) \rightarrow de$               | st                                |                                          |

| Status Affected:             | N, Z                                                                      |                                   |                                   |                                          |

| Encoding:                    | 0001                                                                      | 00da                              | ffff                              | ffff                                     |

|                              | 'd' is '1', th<br>register 'f'<br>Access Ba<br>riding the I<br>the bank w | (default<br>ank will I<br>BSR val | ). If 'a'<br>be sele<br>ue. If 'a | is '0', the<br>ected, ove<br>a' = 1, the |

|                              | BSR value                                                                 | e (defau                          | lt).                              | as per the                               |

| Words:                       | BSR value<br>1                                                            | e (defau                          | lt).                              | as per the                               |

| Words:<br>Cycles:            |                                                                           | e (defau                          | lt).                              | as per the                               |

|                              | 1                                                                         | e (defau                          | lt).                              | as per the                               |

| Cycles:                      | 1                                                                         | e (defau<br>Q3                    |                                   | as per the                               |

| Cycles:<br>Q Cycle Activity: | 1<br>1                                                                    |                                   | ss                                |                                          |

| Before Instruction |   |      |  |  |  |

|--------------------|---|------|--|--|--|

| RESULT             | = | 0x13 |  |  |  |

| W                  | = | 0x91 |  |  |  |

| After Instruction  |   |      |  |  |  |

|                    |   |      |  |  |  |

| RESULT | = | 0x13 |

|--------|---|------|

| W      | = | 0x93 |

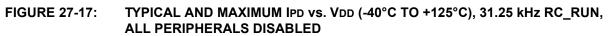

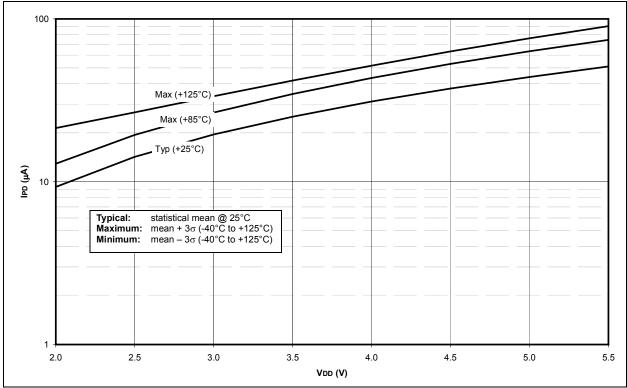

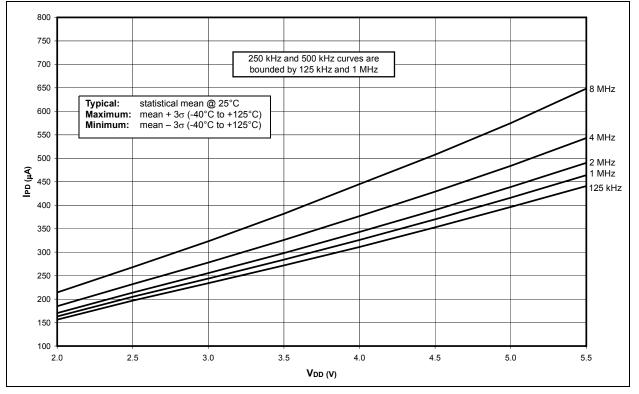

### 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2220/2320/4220/4320 (Industrial) PIC18LF2220/2320/4220/4320 (Industrial)

|              | <b>2220/2320/4220/4320</b><br>strial)                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |          |            |                                                                                                  |            |                                    |  |

|--------------|-----------------------------------------------------------|-------------------------------------------------------|----------|------------|--------------------------------------------------------------------------------------------------|------------|------------------------------------|--|

| PIC18F2      |                                                           | rd Oper                                               | •        | -40°C ≤ T⁄ | <b>s otherwise stated</b><br>$A \le +85^{\circ}C$ for indust<br>$A \le +125^{\circ}C$ for extend | rial       |                                    |  |

| Param<br>No. | Device                                                    | Тур                                                   | Max      | Units      | Conditions                                                                                       |            |                                    |  |

|              | Power-down Current (IPD)                                  | (1)                                                   |          |            |                                                                                                  |            |                                    |  |

| l            | PIC18LF2X20/4X20                                          | 0.1                                                   | 0.5      | μA         | -4                                                                                               | 40°C       |                                    |  |

|              |                                                           | 0.1                                                   | 0.5      | μΑ         | +2                                                                                               | 25°C       | VDD = 2.0V<br>( <b>Sleep</b> mode) |  |

|              |                                                           | 0.2                                                   | 1.7      | μA         | +8                                                                                               | 85°C       | ()                                 |  |

|              | PIC18LF2X20/4X20                                          | 0.1                                                   | 0.5      | μA         | -4                                                                                               | 10°C       | VDD = 3.0V                         |  |

|              |                                                           | 0.1                                                   | 0.5      | μΑ         |                                                                                                  | 25°C       | ( <b>Sleep</b> mode)               |  |

|              |                                                           | 0.3                                                   | 1.7      | μΑ         |                                                                                                  | +85°C      |                                    |  |

|              | All devices                                               | 0.1                                                   | 2.0      | μA         |                                                                                                  | 10°C       | $V_{DD} = 5.0V$                    |  |

|              |                                                           | 0.1                                                   | 2.0      | μA         |                                                                                                  | 25°C       |                                    |  |

|              | Estavolado da visca                                       | 0.4                                                   | 6.5      | μA         |                                                                                                  | 35°C       | ( <b>Sleep</b> mode)               |  |

|              | Extended devices                                          | 11.2                                                  | 50       | μA         | +1                                                                                               | 25°C       |                                    |  |

|              | Supply Current (IDD) <sup>(2,3)</sup><br>PIC18LF2X20/4X20 | 11                                                    | 25       |            | -40°C                                                                                            |            |                                    |  |

|              | PIC 10LF2X20/4X20                                         | 13                                                    | 25<br>25 | μΑ<br>μΑ   | -40 C<br>+25°C                                                                                   | VDD = 2.0V |                                    |  |

|              |                                                           | 13                                                    | 25       | μΑ         | +25 C<br>+85°C                                                                                   | VDD - 2.0V |                                    |  |

|              | PIC18LF2X20/4X20                                          | 34                                                    | 40       | μΑ         | -40°C                                                                                            |            |                                    |  |

|              |                                                           | 28                                                    | 40       | μΑ         | +25°C                                                                                            | VDD = 3.0V | Fosc = 31 kHz                      |  |

|              |                                                           | 25                                                    | 40       | μΑ         | +85°C                                                                                            |            | ( <b>RC_RUN</b> mode,              |  |

|              | All devices                                               | 77                                                    | 80       | μA         | -40°C                                                                                            |            | internal oscillator source)        |  |

|              |                                                           | 62                                                    | 80       | μΑ         | +25°C                                                                                            |            |                                    |  |

|              |                                                           | 53                                                    | 80       | μA         | +85°C                                                                                            | VDD = 5.0V |                                    |  |

|              | Extended devices                                          | 50                                                    | 80       | μA         | +125°C                                                                                           | 1          |                                    |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

4: Standard low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

#### 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2220/2320/4220/4320 (Industrial) PIC18LF2220/2320/4220/4320 (Industrial) (Continued)

| PIC18LF2<br>(Indus | <b>2220/2320/4220/4320</b><br>strial)   | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                    |          |                                 |                                                               | ,    |

|--------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|---------------------------------|---------------------------------------------------------------|------|

|                    | 220/2320/4220/4320<br>strial, Extended) |                                                                                                                                    | rd Oper<br>ng temp |          |                                 | otherwise stated<br>≤ +85°C for industr<br>≤ +125°C for exter | rial |

| Param<br>No.       | Device                                  | Тур                                                                                                                                | Max                | Units    | Conditions                      |                                                               |      |

|                    | Module Differential Currer              | nts (∆lw                                                                                                                           | от, ∆Іво           | R, ∆ILVD | , $\Delta$ IOSCB, $\Delta$ IAD) |                                                               |      |

| D022               | Watchdog Timer                          | 1.5                                                                                                                                | 3.8                | μA       | -40°C                           |                                                               |      |

| (∆IWDT)            |                                         | 2.2                                                                                                                                | 3.8                | μA       | +25°C                           | VDD = 2.0V<br>VDD = 3.0V                                      |      |

|                    |                                         | 2.7                                                                                                                                | 4.0                | μA       | +85°C                           |                                                               |      |

|                    |                                         | 2.3                                                                                                                                | 4.6                | μA       | -40°C                           |                                                               |      |

|                    |                                         | 2.7                                                                                                                                | 4.6                | μA       | +25°C                           |                                                               |      |

|                    |                                         | 3.1                                                                                                                                | 4.8                | μA       | +85°C                           |                                                               |      |

|                    |                                         | 3.0                                                                                                                                | 10.0               | μA       | -40°C                           |                                                               |      |

|                    |                                         | 3.3                                                                                                                                | 10.0               | μA       | +25°C                           | VDD = 5.0V                                                    |      |

|                    |                                         | 3.9                                                                                                                                | 10.0               | μA       | +85°C                           | 100 0.01                                                      |      |

|                    | Extended devices only                   | 4.0                                                                                                                                | 13.0               | μA       | +125°C                          |                                                               |      |

| D022A              | Brown-out Reset                         | 35                                                                                                                                 | 50                 | μA       | -40°C to +85°C -                | VDD = 3.0V                                                    |      |

| ( $\Delta$ IBOR)   |                                         | 42                                                                                                                                 | 60                 | μA       | 40 0 10 700 0                   | VDD = 5.0V                                                    |      |

|                    | Extended devices only                   | 46                                                                                                                                 | 65                 | μA       | -40°C to +125°C                 |                                                               |      |