Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4320t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din New-                                                     | Pin N | umber | Pin                     | Buffer                              | Description                                                                                                                                                      |

|--------------------------------------------------------------|-------|-------|-------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                     | PDIP  | SOIC  | Туре                    | Туре                                | Description                                                                                                                                                      |

| MCLR/VPP<br>MCLR                                             | 1     | 1     | I                       | ST                                  | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low Rese<br>to the device.                             |

| VPP                                                          |       |       | Р                       |                                     | Programming voltage input.                                                                                                                                       |

| OSC1/CLKI/RA7<br>OSC1<br>CLKI                                | 9     | 9     | 1                       | ST<br>CMOS                          | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode, CMOS otherwise. |

| RA7                                                          |       |       | ı<br>1/0                | TTL                                 | External clock source input. Always associated with pin<br>function OSC1. (See related OSC1/CLKI, OSC2/CLKO pins.<br>General purpose I/O pin.                    |

| OSC2/CLKO/RA6<br>OSC2                                        | 10    | 10    | 0                       |                                     | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonator                                                               |

| CLKO                                                         |       |       | 0                       | —                                   | in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKO which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate                   |

| RA6                                                          |       |       | I/O                     | TTL                                 | General purpose I/O pin.                                                                                                                                         |

| RA0/AN0<br>RA0<br>AN0                                        | 2     | 2     | I/O<br>I                | TTL<br>Analog                       | PORTA is a bidirectional I/O port.<br>Digital I/O.<br>Analog input 0.                                                                                            |

| RA1/AN1<br>RA1<br>AN1                                        | 3     | 3     | I/O<br>I                | TTL<br>Analog                       | Digital I/O.<br>Analog input 1.                                                                                                                                  |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF          | 4     | 4     | I/O<br> <br> <br>0      | TTL<br>Analog<br>Analog<br>Analog   | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (low) input.<br>Comparator reference voltage output.                                                    |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                         | 5     | 5     | I/O<br>I<br>I           | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (high) input.                                                                                           |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT                     | 6     | 6     | I/O<br>I<br>O           | ST/OD<br>ST                         | Digital I/O. Open drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                       |

| RA5/AN4/SS/LVDIN/C2OUT<br>RA5<br>AN4<br>SS<br>LVDIN<br>C2OUT | 7     | 7     | I/O<br> <br> <br> <br>0 | TTL<br>Analog<br>TTL<br>Analog<br>— | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Low-Voltage Detect input.<br>Comparator 2 output.                                                  |

| RA6                                                          |       |       |                         |                                     | See the OSC2/CLKO/RA6 pin.                                                                                                                                       |

| RA7                                                          |       |       |                         |                                     | See the OSC1/CLKI/RA7 pin.                                                                                                                                       |

| Legend: TTL = TTL comp<br>ST = Schmitt Tr<br>O = Output      |       |       | ith CM                  | OS levels                           | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                 |

#### **TABLE 1-2:** PIC18F2220/2320 PINOUT I/O DESCRIPTIONS

O = Output OD = Open-drain (no diode to VDD)

Note 1: Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

| Din Nama                                              | Pin Number |       | Pin               | Buffer           | Description                                                                                                                              |  |  |  |  |

|-------------------------------------------------------|------------|-------|-------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                              | PDIP       | SOIC  | Туре              | Туре             | Description                                                                                                                              |  |  |  |  |

|                                                       |            |       |                   |                  | PORTC is a bidirectional I/O port.                                                                                                       |  |  |  |  |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI              | 11         | 11    | I/O<br>O<br>I     | ST<br>—<br>ST    | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                         |  |  |  |  |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(2)</sup> | 12         | 12    | I/O<br>I<br>I/O   | ST<br>CMOS<br>ST | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input, Compare 2 output, PWM2 output.                                              |  |  |  |  |

| RC2/CCP1/P1A<br>RC2<br>CCP1<br>P1A                    | 13         | 13    | I/O<br>I/O<br>O   | ST<br>ST         | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Enhanced CCP1 output.                                                   |  |  |  |  |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                      | 14         | 14    | I/O<br>I/O<br>I/O | ST<br>ST<br>ST   | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |  |  |  |  |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                      | 15         | 15    | I/O<br>I<br>I/O   | ST<br>ST<br>ST   | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |  |  |  |  |

| RC5/SDO<br>RC5<br>SDO                                 | 16         | 16    | I/O<br>O          | ST<br>—          | Digital I/O.<br>SPI data out.                                                                                                            |  |  |  |  |

| RC6/TX/CK<br>RC6<br>TX<br>CK                          | 17         | 17    | I/O<br>O<br>I/O   | ST<br>—<br>ST    | Digital I/O.<br>USART asynchronous transmit.<br>USART synchronous clock (see related RX/DT).                                             |  |  |  |  |

| RC7/RX/DT<br>RC7<br>RX<br>DT                          | 18         | 18    | I/O<br>I<br>I/O   | ST<br>ST<br>ST   | Digital I/O.<br>USART asynchronous receive.<br>USART synchronous data (see related TX/CK).                                               |  |  |  |  |

| Vss                                                   | 8, 19      | 8, 19 | Р                 |                  | Ground reference for logic and I/O pins.                                                                                                 |  |  |  |  |

| Vdd                                                   | 20         | 20    | Р                 | —                | Positive supply for logic and I/O pins.                                                                                                  |  |  |  |  |

| Legend: TTL = TTL con<br>ST = Schmitt                 | Trigger i  |       | ith CM            | OS levels        | CMOS = CMOS compatible input or output<br>s I = Input                                                                                    |  |  |  |  |

#### **TABLE 1-2:** PIC18F2220/2320 PINOUT I/O DESCRIPTIONS (CONTINUED)

= Input Ρ = Power

O = Output OD = Open-drain (no diode to VDD)

Note 1: Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

### TABLE 1-3: PIC18F4220/4320 PINOUT I/O DESCRIPTIONS

| Din Nama                                            | Pi               | n Numb                          | ber     | Pin                | Buffer                              | Description                                                                                                                                                                                                             |

|-----------------------------------------------------|------------------|---------------------------------|---------|--------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                            | PDIP             | TQFP                            | QFN     | Туре               | Туре                                | Description                                                                                                                                                                                                             |

| MC <u>LR</u> /Vpp/RE3<br>MCLR<br>Vpp                | 1                | 18                              | 18      | I<br>P             | ST                                  | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.<br>Programming voltage input.                                                     |

| RE3                                                 |                  |                                 |         | , i                | ST                                  | Digital input.                                                                                                                                                                                                          |

| OSC1/CLKI/RA7<br>OSC1<br>CLKI                       | 13               | 30                              | 32      |                    | ST<br>CMOS                          | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode, CMOS otherwise.<br>External clock source input. Always associated with |

| RA7                                                 |                  |                                 |         | I/O                | TTL                                 | pin function OSC1. (See related OSC1/CLKI,<br>OSC2/CLKO pins.)<br>General purpose I/O pin.                                                                                                                              |

| OSC2/CLKO/RA6<br>OSC2                               | 14               | 31                              | 33      | 0                  | _                                   | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonator                                                                                                                      |

| CLKO                                                |                  |                                 |         | ο                  | _                                   | in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKO which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate                                                                          |

| RA6                                                 |                  |                                 |         | I/O                | TTL                                 | General purpose I/O pin.                                                                                                                                                                                                |

| RA0/AN0<br>RA0                                      | 2                | 19                              | 19      | I/O                | TTL                                 | PORTA is a bidirectional I/O port.<br>Digital I/O.                                                                                                                                                                      |

| AN0                                                 |                  |                                 |         | I                  | Analog                              | Analog input 0.                                                                                                                                                                                                         |

| RA1/AN1<br>RA1<br>AN1                               | 3                | 20                              | 20      | I/O<br>I           | TTL<br>Analog                       | Digital I/O.<br>Analog input 1.                                                                                                                                                                                         |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4                | 21                              | 21      | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog   | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (low) input.<br>Comparator reference voltage output.                                                                                                           |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                | 5                | 22                              | 22      | I/O<br>I<br>I      | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (high) input.                                                                                                                                                  |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT            | 6                | 23                              | 23      | I/O<br>I<br>O      | ST/OD<br>ST                         | Digital I/O. Open drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                                                                              |

| RA5/AN4/SS/LVDIN/                                   | 7                | 24                              | 24      |                    |                                     |                                                                                                                                                                                                                         |

| C2OUT<br>RA5<br><u>AN4</u><br>SS<br>LVDIN<br>C2OUT  |                  |                                 |         | I/O<br>I<br>I<br>O | TTL<br>Analog<br>TTL<br>Analog<br>— | Digital I/O.<br>Analog input 4.<br>SPI slave select input.<br>Low-Voltage Detect input.<br>Comparator 2 output.                                                                                                         |

| RA6                                                 |                  |                                 |         |                    |                                     | See the OSC2/CLKO/RA6 pin.                                                                                                                                                                                              |

| RA7                                                 |                  |                                 |         |                    |                                     | See the OSC1/CLKI/RA7 pin.                                                                                                                                                                                              |

| O = Outp                                            | nitt Trig<br>out | tible inp<br>ger inp<br>(no dio | ut with |                    | 8 levels                            | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                                                                        |

OD = Open-drain (no diode to VDD)

**Note 1:** Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

# 2.7.2 OSCILLATOR TRANSITIONS

The PIC18F2X20/4X20 devices contain circuitry to prevent clocking "glitches" when switching between clock sources. A short pause in the system clock occurs during the clock switch. The length of this pause is between 8 and 9 clock periods of the new clock source. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes"**.

# 2.8 Effects of Power-Managed Modes on the Various Clock Sources

When the device executes a SLEEP instruction, the system is switched to one of the power-managed modes, depending on the state of the IDLEN and SCS1:SCS0 bits of the OSCCON register. See **Section 3.0 "Power-Managed Modes"** for details.

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the system clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the system clock source. The INTRC output can be used directly to provide the system clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 23.2 "Watchdog Timer (WDT)" through Section 23.4 "Fail-Safe Clock Monitor"). The INTOSC output at 8 MHz may be used directly to clock the system or may be divided down first. The INTOSC output is disabled if the system clock is provided directly from the INTRC output. If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a system clock source (i.e., MSSP slave, PSP, INTx pins, A/D conversions and others).

# 2.9 Power-up Delays

Power-up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see Section 4.1 "Power-on Reset (POR)" through Section 4.5 "Brown-out Reset (BOR)".

The first timer is the Power-up Timer (PWRT) which provides a fixed delay on power-up (parameter 33, Table 26-10), if enabled, in Configuration Register 2L. The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms, following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of 5 to 10  $\mu s,$  following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| OSC Mode       | OSC1 Pin                                                 | OSC2 Pin                                                 |  |  |  |

|----------------|----------------------------------------------------------|----------------------------------------------------------|--|--|--|

| RC, INTIO1     | Floating, external resistor should pull high             | At logic low (clock/4 output)                            |  |  |  |

| RCIO, INTIO2   | Floating, external resistor should pull high             | Configured as PORTA, bit 6                               |  |  |  |

| ECIO           | Floating, pulled by external clock                       | Configured as PORTA, bit 6                               |  |  |  |

| EC             | Floating, pulled by external clock                       | At logic low (clock/4 output)                            |  |  |  |

| LP, XT, and HS | Feedback inverter disabled at<br>quiescent voltage level | Feedback inverter disabled at<br>quiescent voltage level |  |  |  |

### TABLE 2-3: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-1 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

#### 3.1.2 ENTERING POWER-MANAGED MODES

In general, entry, exit and switching between powermanaged clock sources requires clock source switching. In each case, the sequence of events is the same.

Any change in the power-managed mode begins with loading the OSCCON register and executing a SLEEP instruction. The SCS1:SCS0 bits select one of three power-managed clock sources; the primary clock (as defined in Configuration Register 1H), the secondary clock (the Timer1 oscillator) and the internal oscillator block (used in RC modes). Modifying the SCS bits will have no effect until a SLEEP instruction is executed. Entry to the power-managed mode is triggered by the execution of a SLEEP instruction.

Figure 3-5 shows how the system is clocked while switching from the primary clock to the Timer1 oscillator. When the SLEEP instruction is executed, clocks to the device are stopped at the beginning of the next instruction cycle. Eight clock cycles from the new clock source are counted to synchronize with the new clock source are counted, clocks from the new clock source are counted, clocks from the new clock source are counted, clocks from the new clock source resume clocking the system. The actual length of the pause is between eight and nine clock periods from the new clock source. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

Three bits indicate the current clock source: OSTS and IOFS in the OSCCON register and T1RUN in the T1CON register. Only one of these bits will be set while in a power-managed mode other than PRI\_RUN. When the OSTS bit is set, the primary clock is providing the system clock. When the IOFS bit is set, the INTOSC output is providing a stable 8 MHz clock source and is providing the system clock. When the T1RUN bit is set, the Timer1 oscillator is providing the system clock. If none of these bits are set, then either the INTRC clock source is clocking the system or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source in Configuration Register 1H, then both the OSTS and IOFS bits may be set when in PRI\_RUN or PRI\_IDLE modes. This indicates that the primary clock (INTOSC output) is generating a stable 8 MHz output. Entering a power-managed RC mode (same frequency) would clear the OSTS bit.

- Note 1: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

- 2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode; executing a SLEEP instruction is simply a trigger to place the controller into a power-managed mode selected by the OSCCON register, one of which is Sleep mode.

### 3.1.3 MULTIPLE SLEEP COMMANDS

The power-managed mode that is invoked with the SLEEP instruction is determined by the settings of the IDLEN and SCS bits at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by these same bits at that time. If the bits have changed, the device will enter the new power-managed mode specified by the new bit settings.

#### 3.1.4 COMPARISONS BETWEEN RUN AND IDLE MODES

Clock source selection for the Run modes is identical to the corresponding Idle modes. When a SLEEP instruction is executed, the SCS bits in the OSCCON register are used to switch to a different clock source. As a result, if there is a change of clock source at the time a SLEEP instruction is executed, a clock switch will occur.

In Idle modes, the CPU is not clocked and is not running. In Run modes, the CPU is clocked and executing code. This difference modifies the operation of the WDT when it times out. In Idle modes, a WDT time-out results in a wake from power-managed modes. In Run modes, a WDT time-out results in a WDT Reset (see Table 3-2).

During a wake-up from an Idle mode, the CPU starts executing code by entering the corresponding Run mode until the primary clock becomes ready. When the primary clock becomes ready, the clock source is automatically switched to the primary clock. The IDLEN and SCS bits are unchanged during and after the wake-up.

Figure 3-2 shows how the system is clocked during the clock source switch. The example assumes the device was in SEC\_IDLE or SEC\_RUN mode when a wake is triggered (the primary clock was configured in HSPLL mode).

| Register Applicabl |      | e Devi | ces  | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |                          |

|--------------------|------|--------|------|------------------------------------|---------------------------------------------------------------|---------------------------------|--------------------------|

| TOSU               | 2220 | 2320   | 4220 | 4320                               | 0 0000                                                        | 0 0000                          | 0 uuuu <b>(3)</b>        |

| TOSH               | 2220 | 2320   | 4220 | 4320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu <sup>(3)</sup> |

| TOSL               | 2220 | 2320   | 4220 | 4320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu <sup>(3)</sup> |

| STKPTR             | 2220 | 2320   | 4220 | 4320                               | uu-0 0000                                                     | 00-0 0000                       | uu-u uuuu <sup>(3)</sup> |

| PCLATU             | 2220 | 2320   | 4220 | 4320                               | 0 0000                                                        | 0 0000                          | u uuuu                   |

| PCLATH             | 2220 | 2320   | 4220 | 4320                               | 0000 0000                                                     | 0000 0000                       | นนนน นนนน                |

| PCL                | 2220 | 2320   | 4220 | 4320                               | 0000 0000                                                     | 0000 0000                       | PC + 2 <sup>(2)</sup>    |

| TBLPTRU            | 2220 | 2320   | 4220 | 4320                               | 00 0000                                                       | 00 0000                         | uu uuuu                  |

| TBLPTRH            | 2220 | 2320   | 4220 | 4320                               | 0000 0000                                                     | 0000 0000                       | นนนน นนนน                |

| TBLPTRL            | 2220 | 2320   | 4220 | 4320                               | 0000 0000                                                     | 0000 0000                       | นนนน นนนน                |

| TABLAT             | 2220 | 2320   | 4220 | 4320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu                |

| PRODH              | 2220 | 2320   | 4220 | 4320                               | XXXX XXXX                                                     | นนนน นนนน                       | սսսս սսսս                |

| PRODL              | 2220 | 2320   | 4220 | 4320                               | XXXX XXXX                                                     | սսսս սսսս                       | uuuu uuuu                |

| INTCON             | 2220 | 2320   | 4220 | 4320                               | 0000 000x                                                     | 0000 000u                       | uuuu uuuu <b>(1)</b>     |

| INTCON2            | 2220 | 2320   | 4220 | 4320                               | 1111 -1-1                                                     | 1111 -1-1                       | uuuu -u-u <b>(1)</b>     |

| INTCON3            | 2220 | 2320   | 4220 | 4320                               | 11-0 0-00                                                     | 11-0 0-00                       | uu-u u-uu <b>(1)</b>     |

| INDF0              | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| POSTINC0           | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| POSTDEC0           | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| PREINC0            | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| PLUSW0             | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| FSR0H              | 2220 | 2320   | 4220 | 4320                               | xxxx                                                          | uuuu                            | uuuu                     |

| FSR0L              | 2220 | 2320   | 4220 | 4320                               | XXXX XXXX                                                     | uuuu uuuu                       | uuuu uuuu                |

| WREG               | 2220 | 2320   | 4220 | 4320                               | XXXX XXXX                                                     | นนนน นนนน                       | นนนน นนนน                |

| INDF1              | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| POSTINC1           | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| POSTDEC1           | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| PREINC1            | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

| PLUSW1             | 2220 | 2320   | 4220 | 4320                               | N/A                                                           | N/A                             | N/A                      |

### TABLE 4-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-2 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

# 5.0 MEMORY ORGANIZATION

There are three memory types in enhanced MCU devices. These memory types are:

- Program Memory

- Data RAM

- Data EEPROM

Data and program memory use separate busses which allow for concurrent access of these types.

Additional detailed information for Flash program memory and data EEPROM is provided in Section 6.0 "Flash Program Memory" and Section 7.0 "Data EEPROM Memory", respectively.

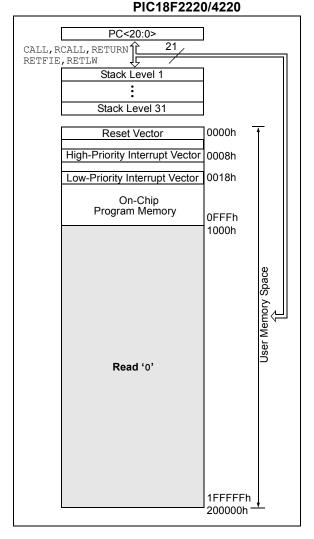

# FIGURE 5-1: PROGRAM MEMORY MAP AND STACK FOR

# 5.1 Program Memory Organization

A 21-bit program counter is capable of addressing the 2-Mbyte program memory space. Accessing a location between the physically implemented memory and the 2-Mbyte address will cause a read of all '0's (a NOP instruction).

The PIC18F2220 and PIC18F4220 each have 4 Kbytes of Flash memory and can store up to 2,048 single-word instructions.

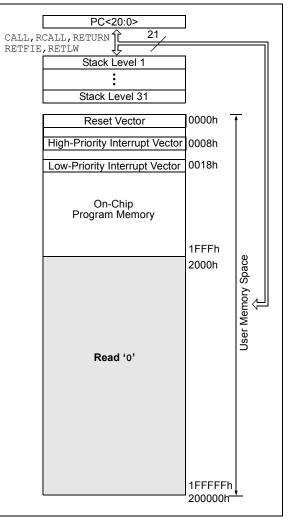

The PIC18F2320 and PIC18F4320 each have 8 Kbytes of Flash memory and can store up to 4,096 single-word instructions.

The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The Program Memory Maps for PIC18F2220/4220 and PIC18F2320/4320 devices are shown in Figure 5-1 and Figure 5-2, respectively.

#### PROGRAM MEMORY MAP AND STACK FOR PIC18F2320/4320

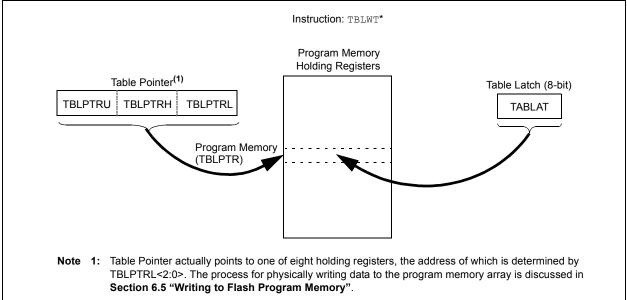

# FIGURE 6-2: TABLE WRITE OPERATION

# 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

# 6.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit, EEPGD, determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The FREE bit controls program memory erase operations. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled. The WREN bit enables and disables erase and write operations. When set, erase and write operations are allowed. When clear, erase and write operations are disabled – the WR bit cannot be set while the WREN bit is clear. This process helps to prevent accidental writes to memory due to errant (unexpected) code execution.

Firmware should keep the WREN bit clear at all times except when starting erase or write operations. Once firmware has set the WR bit, the WREN bit may be cleared. Clearing the WREN bit will not affect the operation in progress.

The WRERR bit is set when a write operation is interrupted by a Reset. In these situations, the user can check the WRERR bit and rewrite the location. It will be necessary to reload the data and address registers (EEDATA and EEADR) as these registers have cleared as a result of the Reset.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 6.3 "Reading the Flash Program Memory"** regarding table reads.

**Note:** Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

# 9.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from powermanaged mode. RCON also contains the bit that enables interrupt priorities (IPEN).

### REGISTER 9-10: RCON: RESET CONTROL REGISTER

| R/W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-------|-------|

| IPEN  | _   | _   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |     |       |     |     |       | bit 0 |

| Legend:          |          |                                                                                                    |                                                            |                                         |  |  |  |  |

|------------------|----------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit |          | W = Writable bit                                                                                   | U = Unimplemented bit, read as '0'                         |                                         |  |  |  |  |

| -n = Value       | at POR   | '1' = Bit is set                                                                                   | '0' = Bit is cleared                                       | x = Bit is unknown                      |  |  |  |  |

| bit 7            | 1 = Enat | terrupt Priority Enable bit<br>ble priority levels on interrupt<br>ble priority levels on interrup | s<br>ts (PIC16CXXX Compatibility                           | mode)                                   |  |  |  |  |

| bit 6-5          | Unimple  | mented: Read as '0'                                                                                |                                                            |                                         |  |  |  |  |

| bit 4            | RI: RESE | T Instruction Flag bit                                                                             |                                                            |                                         |  |  |  |  |

|                  | 0 = The  |                                                                                                    | executed (set by firmware only cuted causing a device Rese | )<br>t (must be set in software after a |  |  |  |  |

|       | Brown out (coot occurry)                                                                |

|-------|-----------------------------------------------------------------------------------------|

| bit 3 | TO: Watchdog Time-out Flag bit                                                          |

|       | 1 = Set by power-up, CLRWDT instruction or SLEEP instruction                            |

|       | 0 = A WDT time-out occurred                                                             |

| bit 2 | PD: Power-Down Detection Flag bit                                                       |

|       | 1 = Set by power-up or by the CLRWDT instruction                                        |

|       | 0 = Cleared by execution of the SLEEP instruction                                       |

| bit 1 | POR: Power-on Reset Status bit                                                          |

|       | 1 = A Power-on Reset has not occurred (set by firmware only)                            |

|       | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)   |

| bit 0 | BOR: Brown-out Reset Status bit                                                         |

|       | 1 = A Brown-out Reset has not occurred (set by firmware only)                           |

|       | 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs) |

| Name    | Bit 7                                                                      | Bit 6          | Bit 5        | Bit 4         | Bit 3         | Bit 2    | Bit 1  | Bit 0  | Value<br>POR, B | -   | all o | e on<br>other<br>sets |

|---------|----------------------------------------------------------------------------|----------------|--------------|---------------|---------------|----------|--------|--------|-----------------|-----|-------|-----------------------|

| INTCON  | GIE/GIEH                                                                   | PEIE/GIEL      | TMR0IE       | INT0IE        | RBIE          | TMR0IF   | INT0IF | RBIF   | 0000 0          | 00x | 0000  | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup>                                                       | ADIF           | RCIF         | TXIF          | SSPIF         | CCP1IF   | TMR2IF | TMR1IF | 0000 0          | 000 | 0000  | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup>                                                       | ADIE           | RCIE         | TXIE          | SSPIE         | CCP1IE   | TMR2IE | TMR1IE | 0000 0          | 000 | 0000  | 0000                  |

| IPR1    | PSPIP <sup>(1)</sup>                                                       | ADIP           | RCIP         | TXIP          | SSPIP         | CCP1IP   | TMR2IP | TMR1IP | 1111 1          | 111 | 1111  | 1111                  |

| TRISC   | PORTC Da                                                                   | ata Direction  | Register     |               |               |          |        |        | 1111 1          | 111 | 1111  | 1111                  |

| TMR1L   | Holding Re                                                                 | egister for th | e Least Sigr | nificant Byte | of the 16-bit | TMR1 Reg | gister |        | XXXX X          | xxx | uuuu  | uuuu                  |

| TMR1H   | Holding Re                                                                 | egister for th | e Most Sign  | ificant Byte  | of the 16-bit | TMR1 Reg | ister  |        | XXXX X          | xxx | uuuu  | uuuu                  |

| T1CON   | RD16                                                                       | T1RUN          | T1CKPS1      | T1CKPS0       | T10SCEN       | T1SYNC   | TMR1CS | TMR10N | 0000 0          | 000 | uuuu  | uuuu                  |

| CCPR1L  | Capture/C                                                                  | ompare/PW      | M Register 2 | I (LSB)       |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCPR1H  | Capture/C                                                                  | ompare/PW      | M Register 2 | I (MSB)       |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCP1CON | _                                                                          | _              | DC1B1        | DC1B0         | CCP1M3        | CCP1M2   | CCP1M1 | CCP1M0 | 00 0            | 000 | 00    | 0000                  |

| CCPR2L  | Capture/C                                                                  | ompare/PW      | M Register 2 | 2 (LSB)       |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCPR2H  | Capture/C                                                                  | ompare/PW      | M Register 2 | 2 (MSB)       |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCP2CON | _                                                                          | _              | DC2B1        | DC2B0         | CCP2M3        | CCP2M2   | CCP2M1 | CCP2M0 | 00 0            | 000 | 00    | 0000                  |

| PIR2    | OSCFIF                                                                     | CMIF           | _            | EEIF          | BCLIF         | LVDIF    | TMR3IF | CCP2IF | 00-0 0          | 000 | 00-0  | 0000                  |

| PIE2    | OSCFIE                                                                     | CMIE           | _            | EEIE          | BCLIE         | LVDIE    | TMR3IE | CCP2IE | 00-0 0          | 000 | 00-0  | 0000                  |

| IPR2    | OSCFIP                                                                     | CMIP           | _            | EEIP          | BCLIP         | LVDIP    | TMR3IP | CCP2IP | 11-1 1          | 111 | 11-1  | 1111                  |

| TMR3L   | Holding Re                                                                 | egister for th | e Least Sigr | nificant Byte | of the 16-bit | TMR3 Reg | gister |        | XXXX X          | xxx | uuuu  | uuuu                  |

| TMR3H   | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register |                |              |               |               |          |        |        |                 | xxx | uuuu  | uuuu                  |

| T3CON   | RD16                                                                       | T3CCP2         | T3CKPS1      | T3CKPS0       | T3CCP1        | T3SYNC   | TMR3CS | TMR3ON | 0000 0          | 000 | uuuu  | uuuu                  |

#### TABLE 15-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: These bits are reserved on the PIC18F2X20 devices; always maintain these bits clear.

# 19.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) converter module has 10 inputs for the PIC18F2X20 devices and 13 for the PIC18F4X20 devices. This module allows conversion of an analog input signal to a corresponding 10-bit digital number.

A new feature for the A/D converter is the addition of programmable acquisition time. This feature allows the user to select a new channel for conversion and setting the GO/DONE bit immediately. When the GO/DONE bit is set, the selected channel is sampled for the programmed acquisition time before a conversion is actually started. This removes the firmware overhead that may have been required to allow for an acquisition (sampling) period (see Register 19-3 and Section 19.3 "Selecting and Configuring Automatic Acquisition Time"). The module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 19-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 19-2, configures the functions of the port pins. The ADCON2 register, shown in Register 19-3, configures the A/D clock source, programmed acquisition time and justification.

#### REGISTER 19-1: ADCON0: A/D CONTROL REGISTER 0

| U-0          | U-0                                                                                | R/W-0                                            | R/W-0      | R/W-0                                                                         | R/W-0           | R/W-0    | R/W-0 |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------|--------------------------------------------------|------------|-------------------------------------------------------------------------------|-----------------|----------|-------|--|--|--|--|--|

| _            | —                                                                                  | CHS3                                             | CHS2       | CHS1                                                                          | CHS0            | GO/DONE  | ADON  |  |  |  |  |  |

| bit 7        |                                                                                    |                                                  |            |                                                                               |                 |          | bit ( |  |  |  |  |  |

| Legend:      |                                                                                    |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

| R = Readab   | ole bit                                                                            | W = Writable                                     | bit        | U = Unimpler                                                                  | mented bit, rea | d as '0' |       |  |  |  |  |  |

| -n = Value a | t POR                                                                              | '1' = Bit is set                                 |            | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unknown |                 |          |       |  |  |  |  |  |

| bit 7-6      | Unimplomon                                                                         | ted: Read as '                                   | o'         |                                                                               |                 |          |       |  |  |  |  |  |

|              | •                                                                                  |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

| bit 5-2      | CHS3:CHS0: Analog Channel Select bits<br>0000 = Channel 0 (AN0)                    |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              |                                                                                    |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              |                                                                                    | 0001 = Channel 1 (AN1)<br>0010 = Channel 2 (AN2) |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 0011 = Channel 3 (AN3)                                                             |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 0100 = Channel 4 (AN4)                                                             |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 0101 = Channel 5 (AN5) <sup>(1,2)</sup>                                            |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 0110 = Channel 6 (AN6) <sup>(1,2)</sup><br>0111 = Channel 7 (AN7) <sup>(1,2)</sup> |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              |                                                                                    |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 1000 <b>= Chan</b><br>1001 <b>= Chan</b>                                           |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 1010 <b>= Chan</b>                                                                 |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 1011 <b>= Chan</b>                                                                 |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 1100 = Channel 12 (AN12)                                                           |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 1101 <b>= Unim</b>                                                                 |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 1110 <b>= Unim</b>                                                                 |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 1111 <b>= Unim</b>                                                                 |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

| bit 1        |                                                                                    | /D Conversion                                    | Status bit |                                                                               |                 |          |       |  |  |  |  |  |

|              | $\frac{\text{When ADON} = 1}{1} = \text{A/D conversion in progress}$               |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | 1 = A/D conve<br>0 = A/D Idle                                                      | ersion in progre                                 | ess        |                                                                               |                 |          |       |  |  |  |  |  |

| <b>h</b> # 0 |                                                                                    |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

| bit 0        | ADON: A/D C                                                                        |                                                  |            |                                                                               |                 |          |       |  |  |  |  |  |

|              |                                                                                    | erter module is<br>erter module is               |            |                                                                               |                 |          |       |  |  |  |  |  |

|              | U = A/U CONVe                                                                      |                                                  | nisanien   |                                                                               |                 |          |       |  |  |  |  |  |

2: Performing a conversion on unimplemented channels returns full-scale results.

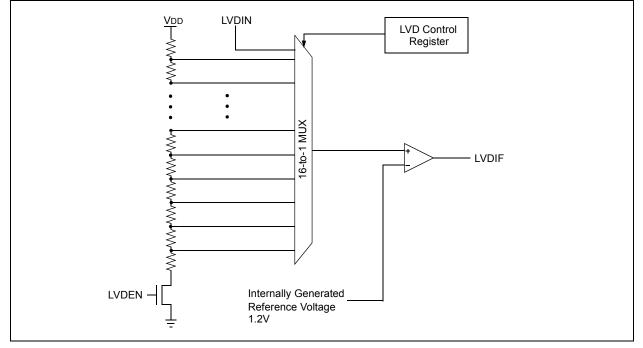

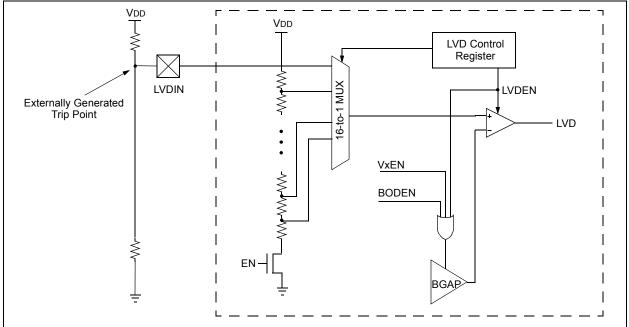

### FIGURE 22-2: LOW-VOLTAGE DETECT (LVD) BLOCK DIAGRAM

The LVD module has an additional feature that allows the user to supply the sense voltage to the module from an external source. This mode is enabled when bits LVDL3:LVDL0 are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, LVDIN (Figure 22-3). This gives users flexibility because it allows them to configure the Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

| MO         | /LW             | Move Lite           | eral to V     | v            |            | MOVWF              |

|------------|-----------------|---------------------|---------------|--------------|------------|--------------------|

| Synt       | tax:            | [ label ]           | MOVLW         | / k          |            | Syntax:            |

| Ope        | rands:          | $0 \le k \le 25$    | 55            |              |            | Operand            |

| Ope        | ration:         | $k \to W$           |               |              |            |                    |

| Statu      | us Affected:    | None                |               |              |            | Operatio           |

| Enco       | oding:          | 0000                | 1110          | kkkk         | kkkk       | Status A           |

| Des        | cription:       | The eight<br>W.     | -bit litera   | ıl 'k' is lo | paded into | Encodin Descript   |

| Wor        | ds:             | 1                   |               |              |            |                    |

| Cycl       | es:             | 1                   |               |              |            |                    |

| QC         | Cycle Activity: |                     |               |              |            |                    |

|            | Q1              | Q2                  | Q             | 3            | Q4         |                    |

|            | Decode          | Read<br>literal 'k' | Proce<br>Data |              | Vrite to W | Words:             |

| <u>Exa</u> | mple:           | MOVLW               | 0x5A          |              |            | Cycles:<br>Q Cycle |

|            | After Instruct  | ion                 |               |              |            | <b>, , ,</b>       |

| Synt               | ax:                          | [ label ]                                                                    | MOVWF 1                                                                                                               | [,a]                                |                                           |  |  |  |

|--------------------|------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------|--|--|--|

| Ope                | rands:                       | $0 \le f \le 25$                                                             | $0 \le f \le 255$                                                                                                     |                                     |                                           |  |  |  |

|                    |                              | a ∈ [0,1]                                                                    |                                                                                                                       |                                     |                                           |  |  |  |

| Ope                | ration:                      | $(W) \to f$                                                                  |                                                                                                                       |                                     |                                           |  |  |  |

| Statu              | us Affected:                 | None                                                                         |                                                                                                                       |                                     |                                           |  |  |  |

| Enco               | Encoding: 0110 111a ffff fff |                                                                              |                                                                                                                       |                                     |                                           |  |  |  |

| Deso               | cription:                    | Location <sup>4</sup><br>256-byte I<br>Access Ba<br>riding the<br>the bank v | a from W to i<br>f' can be any<br>bank. If 'a' is<br>ank will be si<br>BSR value. I<br>will be select<br>e (default). | /whe<br>'0', t<br>electo<br>f 'a' = | re in the<br>he<br>ed, over-<br>= 1, then |  |  |  |

| Wor                | ds:                          | 1                                                                            |                                                                                                                       |                                     |                                           |  |  |  |

| Cycl               | es:                          | 1                                                                            |                                                                                                                       |                                     |                                           |  |  |  |

| QC                 | ycle Activity:               |                                                                              |                                                                                                                       |                                     |                                           |  |  |  |

|                    | Q1                           | Q2                                                                           | Q3                                                                                                                    |                                     | Q4                                        |  |  |  |

|                    | Decode                       | Read                                                                         | Process                                                                                                               |                                     | Write                                     |  |  |  |

|                    |                              | register 'f'                                                                 | Data                                                                                                                  | reg                                 | gister 'f'                                |  |  |  |

|                    |                              |                                                                              |                                                                                                                       |                                     |                                           |  |  |  |

| Exar               | nple:                        | MOVWF                                                                        | REG                                                                                                                   |                                     |                                           |  |  |  |

| Refore Instruction |                              |                                                                              |                                                                                                                       |                                     |                                           |  |  |  |

Move W to f

| Before Instruction |   |              |  |  |

|--------------------|---|--------------|--|--|

| W<br>REG           | = | 0x4F<br>0xFF |  |  |

| After Instru       | _ | UXET         |  |  |

| W                  | = | 0x4F         |  |  |

REG = 0x4F

© 2007 Microchip Technology Inc.

W

= 0x5A

| MULLW               | Multiply I                                                 | _iteral with \                                                                                                     | v                                           | MULWF                             | Multiply V                                                                                                                                                             | V with f                                                                                       |                                                               |

|---------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Syntax:             | [ label ]                                                  | MULLW k                                                                                                            |                                             | Syntax:                           | [ label ]                                                                                                                                                              | MULWF f                                                                                        | [,a]                                                          |

| Operands:           | $0 \le k \le 25$                                           | 5                                                                                                                  |                                             | Operands:                         | $0 \le f \le 258$                                                                                                                                                      | 5                                                                                              |                                                               |

| Operation:          | (W) x k $\rightarrow$                                      | PRODH:PR                                                                                                           | ODL                                         |                                   | a ∈ [0,1]                                                                                                                                                              |                                                                                                |                                                               |

| Status Affected:    | None                                                       |                                                                                                                    |                                             | Operation:                        | (W) x (f) –                                                                                                                                                            | → PRODH:P                                                                                      | RODL                                                          |

| Encoding:           | 0000                                                       | 1101 kk                                                                                                            | kk kkkk                                     | Status Affected:                  | None                                                                                                                                                                   |                                                                                                |                                                               |

| Description:        | An unsign                                                  | ed multiplica                                                                                                      | tion is                                     | Encoding:                         | 0000                                                                                                                                                                   | 001a ffi                                                                                       | ff ffff                                                       |

|                     | of W and<br>16-bit resu<br>PRODH:F<br>PRODH c<br>W is unch | t between the<br>the 8-bit litera<br>ult is placed i<br>PRODL regist<br>contains the h<br>anged.<br>he Status flag | al 'k'. The<br>n<br>ter pair.<br>ligh byte. | Description:                      | carried ou<br>of W and t<br>'f'. The 16<br>the PROD<br>pair. PRO<br>byte.                                                                                              | ed multiplica<br>t between th<br>he register fi<br>-bit result is<br>H:PRODL ro<br>DH contains | e contents<br>le location<br>stored in<br>egister<br>the high |

|                     | Note that carry is po                                      | neither overf<br>ossible in this<br>ro result is po<br>red.                                                        | opera-                                      |                                   | Both W and 'f' are unchang<br>None of the Status flags an<br>affected.<br>Note that neither overflow<br>carry is possible in this ope<br>tion. A zero result is possib |                                                                                                |                                                               |

| Words:              | 1                                                          |                                                                                                                    |                                             |                                   |                                                                                                                                                                        | o result is po<br>ed. If 'a' is '0                                                             |                                                               |