Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

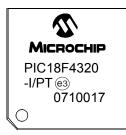

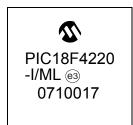

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4320t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

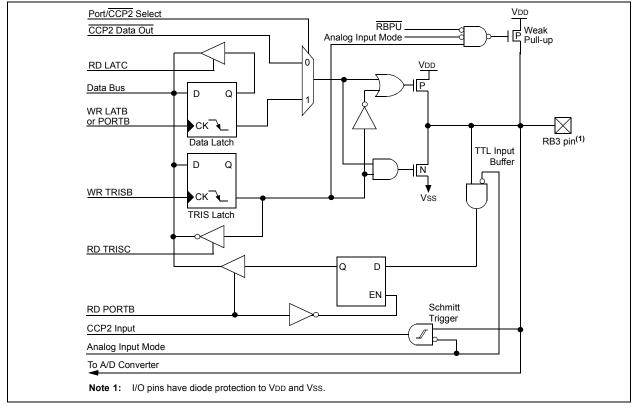

#### FIGURE 10-9: BLOCK DIAGRAM OF RB3/CCP2 PIN

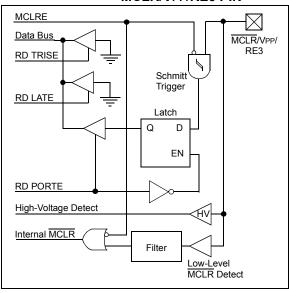

# FIGURE 10-14: BLOCK DIAGRAM OF MCLR/VPP/RE3 PIN

### REGISTER 10-1: TRISE REGISTER

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-------|---------|-----|--------|--------|--------|

| IBF   | OBF | IBOV  | PSPMODE | —   | TRISE2 | TRISE1 | TRISE0 |

| bit 7 |     |       |         |     |        |        | bit 0  |

| Legend:           |                  |                        |                                    |  |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |  |

| bit 7 | <ul> <li><b>IBF:</b> Input Buffer Full Status bit</li> <li>1 = A word has been received and waiting to be read by the CPU</li> <li>0 = No word has been received</li> </ul>                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>OBF</b> : Output Buffer Full Status bit<br>1 = The output buffer still holds a previously written word<br>0 = The output buffer has been read                                                                                        |

| bit 5 | <ul> <li><b>IBOV</b>: Input Buffer Overflow Detect bit (in Microprocessor mode)</li> <li>1 = A write occurred when a previously input word has not been read (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |

| bit 4 | <b>PSPMODE</b> : Parallel Slave Port Mode Select bit<br>1 = Parallel Slave Port mode<br>0 = General Purpose I/O mode                                                                                                                    |

| bit 3 | Unimplemented: Read as '0'                                                                                                                                                                                                              |

| bit 2 | TRISE2: RE2 Direction Control bit<br>1 = Input<br>0 = Output                                                                                                                                                                            |

| bit 1 | TRISE1: RE1 Direction Control bit<br>1 = Input<br>0 = Output                                                                                                                                                                            |

| bit 0 | TRISE0: RE0 Direction Control bit<br>1 = Input<br>0 = Output                                                                                                                                                                            |

| Name    | Bit 7                                                                       | Bit 6          | Bit 5        | Bit 4         | Bit 3         | Bit 2    | Bit 1  | Bit 0  | Value<br>POR, B | -    | all o | e on<br>other<br>sets |

|---------|-----------------------------------------------------------------------------|----------------|--------------|---------------|---------------|----------|--------|--------|-----------------|------|-------|-----------------------|

| INTCON  | GIE/GIEH                                                                    | PEIE/GIEL      | TMR0IE       | INT0IE        | RBIE          | TMR0IF   | INT0IF | RBIF   | 0000 0          | 00x  | 0000  | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup>                                                        | ADIF           | RCIF         | TXIF          | SSPIF         | CCP1IF   | TMR2IF | TMR1IF | 0000 0          | 000  | 0000  | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup>                                                        | ADIE           | RCIE         | TXIE          | SSPIE         | CCP1IE   | TMR2IE | TMR1IE | 0000 0          | 000  | 0000  | 0000                  |

| IPR1    | PSPIP <sup>(1)</sup>                                                        | ADIP           | RCIP         | TXIP          | SSPIP         | CCP1IP   | TMR2IP | TMR1IP | 1111 1          | 111  | 1111  | 1111                  |

| TRISC   | PORTC Da                                                                    | ata Direction  | Register     |               |               |          |        |        | 1111 1          | 111  | 1111  | 1111                  |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |              |               |               |          |        |        | XXXX X          | xxx  | uuuu  | uuuu                  |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |                |              |               |               |          |        | XXXX X | xxx             | uuuu | uuuu  |                       |

| T1CON   | RD16                                                                        | T1RUN          | T1CKPS1      | T1CKPS0       | T10SCEN       | T1SYNC   | TMR1CS | TMR10N | 0000 0          | 000  | uuuu  | uuuu                  |

| CCPR1L  | Capture/C                                                                   | ompare/PW      | M Register 2 | I (LSB)       |               |          |        |        | XXXX X          | xxx  | uuuu  | uuuu                  |

| CCPR1H  | Capture/Compare/PWM Register 1 (MSB)                                        |                |              |               |               |          |        |        | XXXX X          | xxx  | uuuu  | uuuu                  |

| CCP1CON | _                                                                           | _              | DC1B1        | DC1B0         | CCP1M3        | CCP1M2   | CCP1M1 | CCP1M0 | 00 0            | 000  | 00    | 0000                  |

| CCPR2L  | Capture/C                                                                   | ompare/PW      | M Register 2 | 2 (LSB)       |               |          |        |        | XXXX X          | xxx  | uuuu  | uuuu                  |

| CCPR2H  | Capture/C                                                                   | ompare/PW      | M Register 2 | 2 (MSB)       |               |          |        |        | XXXX X          | xxx  | uuuu  | uuuu                  |

| CCP2CON | _                                                                           | _              | DC2B1        | DC2B0         | CCP2M3        | CCP2M2   | CCP2M1 | CCP2M0 | 00 0            | 000  | 00    | 0000                  |

| PIR2    | OSCFIF                                                                      | CMIF           | _            | EEIF          | BCLIF         | LVDIF    | TMR3IF | CCP2IF | 00-0 0          | 000  | 00-0  | 0000                  |

| PIE2    | OSCFIE                                                                      | CMIE           | _            | EEIE          | BCLIE         | LVDIE    | TMR3IE | CCP2IE | 00-0 0          | 000  | 00-0  | 0000                  |

| IPR2    | OSCFIP                                                                      | CMIP           | _            | EEIP          | BCLIP         | LVDIP    | TMR3IP | CCP2IP | 11-1 1          | 111  | 11-1  | 1111                  |

| TMR3L   | Holding Re                                                                  | egister for th | e Least Sigr | nificant Byte | of the 16-bit | TMR3 Reg | gister |        | XXXX X          | xxx  | uuuu  | uuuu                  |

| TMR3H   | Holding Re                                                                  | egister for th | e Most Sign  | ificant Byte  | of the 16-bit | TMR3 Reg | ister  |        | XXXX X          | xxx  | uuuu  | uuuu                  |

| T3CON   | RD16                                                                        | T3CCP2         | T3CKPS1      | T3CKPS0       | T3CCP1        | T3SYNC   | TMR3CS | TMR3ON | 0000 0          | 000  | uuuu  | uuuu                  |

#### TABLE 15-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: These bits are reserved on the PIC18F2X20 devices; always maintain these bits clear.

### **REGISTER 17-3:** SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

| R/W-0 | R/W-0 | R-0 | R-0              | R-0              | R-0 | R-0 | R-0   |

|-------|-------|-----|------------------|------------------|-----|-----|-------|

| SMP   | CKE   | D/Ā | P <sup>(1)</sup> | S <sup>(2)</sup> | R/W | UA  | BF    |

| bit 7 |       |     |                  |                  |     |     | bit 0 |

| Legend:   | lahla hit                  | \\/ \\/##+-!-!- !- !+                                                             | 11 - 11 minerale area (199 | read as (0)                        |

|-----------|----------------------------|-----------------------------------------------------------------------------------|----------------------------|------------------------------------|

| R = Read  |                            | W = Writable bit                                                                  | U = Unimplemented bit,     |                                    |

| -n = Valu | e at POR                   | '1' = Bit is set                                                                  | '0' = Bit is cleared       | x = Bit is unknown                 |

| bit 7     |                            | ew Rate Control bit<br><u>r or Slave mode:</u>                                    |                            |                                    |

|           | 1 = Slev                   | v rate control disabled<br>v rate control enabled                                 |                            |                                    |

| bit 6     | CKE: SN                    | /Bus Select bit                                                                   |                            |                                    |

|           | 1 = Enal                   | <u>r or Slave mode:</u><br>ble SMBus specific inputs<br>ble SMBus specific inputs |                            |                                    |

| bit 5     | D/A: Dat                   | a/Address bit                                                                     |                            |                                    |

|           | <u>In Maste</u><br>Reserve |                                                                                   |                            |                                    |

|           |                            | mode:<br>ates that the last byte receive<br>ates that the last byte receive       |                            | 5                                  |

| bit 4     | P: Stop I                  | pit <sup>(1)</sup>                                                                |                            |                                    |

|           | 0 <b>= Stop</b>            | ates that a Stop bit has been bit was not detected last                           | detected last              |                                    |

| bit 3     | S: Start                   | oit <sup>(2)</sup>                                                                |                            |                                    |

|           | 0 <b>= Start</b>           | ates that a Start bit has been<br>bit was not detected last                       |                            |                                    |

| bit 2     |                            | ad/Write bit Information (I <sup>2</sup> C r                                      | mode only)                 |                                    |

|           | <u>In Slave</u><br>1 = Rea | <u>mode:</u> ( <sup>3)</sup><br>d                                                 |                            |                                    |

|           | 0 = Write                  | 9                                                                                 |                            |                                    |

|           |                            | <u>r mode:<sup>(4)</sup></u>                                                      |                            |                                    |

|           |                            | smit is in progress<br>smit is not in progress                                    |                            |                                    |

| oit 1     | UA: Upd                    | ate Address bit (10-Bit Slave                                                     | mode only)                 |                                    |

|           |                            | ates that the user needs to up<br>ess does not need to be upda                    |                            | ADD register                       |

| oit 0     | BF: Buff                   | er Full Status bit                                                                |                            |                                    |

|           | 1 <b>= Data</b>            | <u>mit mode:</u><br>transmit in progress (does no<br>transmit complete (does not  |                            |                                    |

|           | 1 = Rece                   | <u>ve mode:</u><br>eive complete, SSPBUF is ful<br>eive not complete, SSPBUF is   |                            |                                    |

|           |                            | •                                                                                 |                            |                                    |

| Note 1:   |                            | ared on Reset when SSPEN i                                                        |                            |                                    |

| 2:        |                            | ared on Reset when SSPEN i                                                        |                            |                                    |

| 3:        | address mato               | the R/W bit information follow<br>h to the next Start bit, Stop bi                | t or not ACK bit.          |                                    |

| 4٠        | ORing this hit             | with the SSPCON2 hits SEN                                                         | RSEN PEN RCEN or ACK       | KEN will indicate if the MSSP is i |

4: ORing this bit with the SSPCON2 bits, SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in Idle mode.

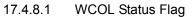

### 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

### FIGURE 17-19: FIRST START BIT TIMING

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

| U-0          | U-0                                                                       |                                                                              | R/W-0       |               | R/W-0       | F        | R/W-0 <sup>(1</sup> | )                  | R/W <sup>(</sup>   | 1)          | R/W     | /(1)    | R      | /W(1)       |

|--------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------|---------------|-------------|----------|---------------------|--------------------|--------------------|-------------|---------|---------|--------|-------------|

| _            | —                                                                         |                                                                              | VCFG1       |               | VCFG0       |          | PCFG3               |                    | PCFG               | 62          | PCF     | G1      | PC     | CFGC        |

| oit 7        |                                                                           |                                                                              |             |               |             |          |                     |                    |                    |             |         |         |        | b           |

| Legend:      |                                                                           |                                                                              |             |               |             |          |                     |                    |                    |             |         |         |        |             |

| R = Readab   | le hit                                                                    | W :                                                                          | = Writal    | nle hit       |             | 11:      | = Unim              | olemer             | nted hit           | read a      | as 'O'  |         |        |             |

| -n = Value a |                                                                           |                                                                              | = Bit is    |               |             |          | = Bit is            |                    |                    |             | x = Bit | is unkr | nown   |             |

|              |                                                                           | 1                                                                            | - Dit 13    | 301           |             | 0        | - Dit 13            | cicarc             | u                  | ,           |         |         | 100011 |             |

| bit 7-6      | Unimplem                                                                  | ented:                                                                       | Read a      | <b>as</b> '0' |             |          |                     |                    |                    |             |         |         |        |             |

| bit 5        | -                                                                         |                                                                              |             |               | nfiguratio  | on bit ( | VREF- S             | source             | )                  |             |         |         |        |             |

|              | VCFG1: Voltage Reference Configuration bit (VREF- source) 1 = VREF- (AN2) |                                                                              |             |               |             |          |                     |                    |                    |             |         |         |        |             |

|              | 0 <b>= V</b> SS                                                           | . /                                                                          |             |               |             |          |                     |                    |                    |             |         |         |        |             |

| bit 4        | VCFG0: V                                                                  | oltage F                                                                     | Referen     | ce Cor        | nfiguratio  | on bit ( | VREF+               | source             | e)                 |             |         |         |        |             |

|              |                                                                           | VCFG0: Voltage Reference Configuration bit (VREF+ source)<br>1 = VREF+ (AN3) |             |               |             |          |                     |                    |                    |             |         |         |        |             |

|              | 0 <b>= V</b> DD                                                           |                                                                              |             |               |             |          |                     |                    |                    |             |         |         |        |             |

| bit 3-0      | PCFG3:PC                                                                  | CFG0: /                                                                      | A/D Por     | t Confi       | guration    | Contr    |                     |                    |                    |             |         |         |        |             |

|              | PCFG3:                                                                    | 12                                                                           | 11          | 10            | 6           | ~        | 7(2)                | 3 <sup>(2)</sup>   | 5 <sup>(2)</sup>   | 4           | 8       | 2       | -      | 0           |

|              | PCFG0                                                                     | AN12                                                                         | AN11        | AN10          | AN9         | AN8      | AN7 <sup>(2)</sup>  | AN6 <sup>(2)</sup> | AN5 <sup>(2)</sup> | AN4         | AN3     | AN2     | AN1    | ANO         |

|              | <sub>0000</sub> (1)                                                       | А                                                                            | А           | А             | Α           | А        | Α                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0001                                                                      | Α                                                                            | Α           | Α             | Α           | Α        | Α                   | Α                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0010                                                                      | Α                                                                            | Α           | Α             | Α           | А        | Α                   | Α                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0011                                                                      | D                                                                            | А           | А             | А           | А        | А                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0100                                                                      | D                                                                            | D           | А             | А           | А        | А                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0101                                                                      | D                                                                            | D           | D             | Α           | А        | Α                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0110                                                                      | D                                                                            | D           | D             | D           | Α        | Α                   | Α                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 0111 <b>(1)</b>                                                           | D                                                                            | D           | D             | D           | D        | А                   | А                  | Α                  | Α           | Α       | Α       | Α      | A           |

|              | 1000                                                                      | D                                                                            | D           | D             | D           | D        | D                   | А                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              | 1001                                                                      | D                                                                            | D           | D             | D           | D        | D                   | D                  | Α                  | Α           | Α       | Α       | Α      | Α           |

|              |                                                                           |                                                                              |             | -             | D           | D        | D                   | D                  | D                  | Α           | Α       | Α       | Α      | Α           |

|              | 1010                                                                      | D                                                                            | D           | D             | 5           |          |                     | -                  | D                  | D           | Α       | •       | •      | Α           |

|              | 1010<br>1011                                                              | D<br>D                                                                       | D<br>D      | D             | D           | D        | D                   | D                  | U                  | _           | А       | Α       | Α      | A           |

|              |                                                                           |                                                                              |             |               |             | D<br>D   | D<br>D              | D                  | D                  | D           | D       | A       | A<br>A | A           |

|              | 1011                                                                      | D                                                                            | D<br>D<br>D | D<br>D<br>D   | D<br>D<br>D | D<br>D   | D<br>D              | D<br>D             | D<br>D             | D<br>D      | D<br>D  | A<br>D  | A<br>A | A<br>A      |

|              | 1011<br>1100                                                              | D<br>D                                                                       | D<br>D      | D<br>D        | D<br>D      | D        | D                   | D                  | D                  | D<br>D<br>D | D       | Α       | Α      | A<br>A<br>A |

|              | 1011<br>1100<br>1101                                                      | D<br>D<br>D                                                                  | D<br>D<br>D | D<br>D<br>D   | D<br>D<br>D | D<br>D   | D<br>D              | D<br>D             | D<br>D             | D<br>D      | D<br>D  | A<br>D  | A<br>A |             |

### REGISTER 19-2: ADCON1: A/D CONTROL REGISTER 1

**Note 1:** The POR value of the PCFG bits depends on the value of the PBADEN Configuration bit. When PBADEN = 1, PCFG<3:0> = 0000; when PBADEN = 0, PCFG<3:0> = 0111.

2: AN5 through AN7 are available only in PIC18F4X20 devices.

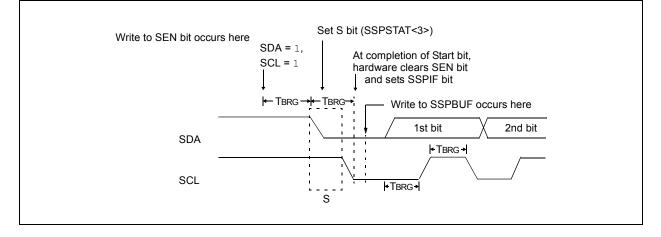

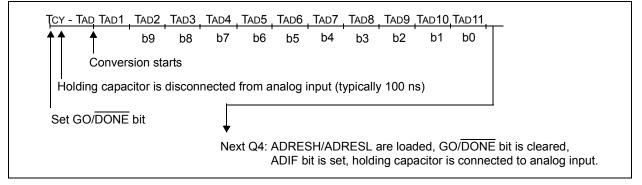

### 19.7 A/D Conversions

Figure 19-3 shows the operation of the A/D converter after the GO/DONE bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

Figure 19-4 shows the operation of the A/D converter after the GO/DONE bit has been set and the ACQT2:ACQT0 bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

#### FIGURE 19-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 19-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

### REGISTER 23-8: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0        | U-0                | U-0                                              | U-0            | R/P-1               | R/P-1               | R/P-1      | R/P-1 |  |  |  |  |  |

|------------|--------------------|--------------------------------------------------|----------------|---------------------|---------------------|------------|-------|--|--|--|--|--|

| _          | —                  | —                                                | _              | WRT3 <sup>(1)</sup> | WRT2 <sup>(1)</sup> | WRT1       | WRT0  |  |  |  |  |  |

| bit 7      | ·                  |                                                  |                |                     |                     |            | bit 0 |  |  |  |  |  |

|            |                    |                                                  |                |                     |                     |            |       |  |  |  |  |  |

| Legend:    |                    |                                                  |                |                     |                     |            |       |  |  |  |  |  |

| R = Reada  | ble bit            | P = Programn                                     | nable bit      | U = Unimpler        | nented bit, read    | as '0'     |       |  |  |  |  |  |

| -n = Value | when device is unp | programmed                                       |                | u = Unchang         | ed from progran     | nmed state |       |  |  |  |  |  |

|            |                    |                                                  |                |                     |                     |            |       |  |  |  |  |  |

| bit 7-4    | Unimplement        | ted: Read as '                                   | )'             |                     |                     |            |       |  |  |  |  |  |

| bit 3      | WRT3: Write        | WRT3: Write Protection bit <sup>(1)</sup>        |                |                     |                     |            |       |  |  |  |  |  |

|            |                    | 1 = Block 3 (001800-001FFFh) not write-protected |                |                     |                     |            |       |  |  |  |  |  |

|            | •                  | 0 = Block 3 (001800-001FFFh) write-protected     |                |                     |                     |            |       |  |  |  |  |  |

| bit 2      | WRT2: Write        | WRT2: Write Protection bit <sup>(1)</sup>        |                |                     |                     |            |       |  |  |  |  |  |

|            |                    | 1 = Block 2 (001000-0017FFh) not write-protected |                |                     |                     |            |       |  |  |  |  |  |

|            | , i                | 01000-0017FF                                     | h) write-prote | ected               |                     |            |       |  |  |  |  |  |

| bit 1      |                    | WRT1: Write Protection bit                       |                |                     |                     |            |       |  |  |  |  |  |

|            |                    | 00800-000FFF                                     | · ·            |                     |                     |            |       |  |  |  |  |  |

|            | ,                  | 0 = Block 1 (000800-000FFFh) write-protected     |                |                     |                     |            |       |  |  |  |  |  |

| bit 0      | WRT0: Write        | Protection bit                                   |                |                     |                     |            |       |  |  |  |  |  |

|            |                    | 00200-0007FF                                     |                |                     |                     |            |       |  |  |  |  |  |

|            | 0 = Block 0 (0     | 00200-0007FF                                     | h) write-prote | cted                |                     |            |       |  |  |  |  |  |

Note 1: Unimplemented in PIC18FX220 devices; maintain this bit set.

#### REGISTER 23-9: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| R/P-1 | R/P-1 | R-1                 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|---------------------|-----|-----|-----|-----|-------|

| WRTD  | WRTB  | WRTC <sup>(1)</sup> | _   | _   | —   | —   | —     |

| bit 7 |       |                     |     |     |     |     | bit 0 |

| Legend:    |                                                                           |                                                                                                          |                                     |

|------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------|

| R = Read   | R = Readable bitP = Programmable bitn = Value when device is unprogrammed |                                                                                                          | U = Unimplemented bit, read as '0'  |

| -n = Value |                                                                           |                                                                                                          | u = Unchanged from programmed state |

| bit 7      | WRTD:                                                                     | Data EEPROM Write Protection                                                                             | n bit                               |

|            |                                                                           | a EEPROM is not write-protecter<br>a EEPROM is write-protected                                           | d                                   |

| bit 6      | 1 <b>= Boo</b>                                                            | Boot Block Write Protection bit<br>t block (000000-0001FFh) is not<br>t block (000000-0001FFh) is wri    | •                                   |

| bit 5      | 1 <b>= Con</b>                                                            | Configuration Register Write Pro<br>figuration registers (300000-300<br>figuration registers (300000-300 | 00FFh) are not write-protected      |

bit 4-0 Unimplemented: Read as '0'

**Note 1:** This bit is read-only in normal execution mode; it can be written only in Program mode.

### REGISTER 23-14: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 |

|-------|-----|-----|-----|-----|-----|-----|-----------------------|

| —     | —   | —   | _   | _   | —   | -   | SWDTEN <sup>(1)</sup> |

| bit 7 |     |     |     |     |     |     | bit 0                 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit<sup>(1)</sup>

1 = Watchdog Timer is on

0 = Watchdog Timer is off

**Note 1:** This bit has no effect if the Configuration bit, WDTEN (CONFIG2H<0>), is enabled.

#### TABLE 23-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|-------|-------|-------|--------|--------|--------|--------|--------|

| CONFIG2H | —     | _     | _     | WDTPS3 | WDTPS2 | WDTPS2 | WDTPS0 | WDTEN  |

| RCON     | IPEN  | _     | -     | RI     | TO     | PD     | POR    | BOR    |

| WDTCON   | —     | -     | l     | —      | —      | _      | l      | SWDTEN |

**Legend:** Shaded cells are not used by the Watchdog Timer.

## 24.0 INSTRUCTION SET SUMMARY

The PIC18 instruction set adds many enhancements to the previous PIC MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets.

Most instructions are a single program memory word (16 bits) but there are three instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- · Control operations

The PIC18 instruction set summary in Table 24-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 24-1 shows the opcode field descriptions.

Most **byte-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction.

The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located.

The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word except for three double word instructions. These three instructions were made double word instructions so that all the required information is available in these 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 24-1 shows the general formats that the instructions can have.

All examples use the format 'nnh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

The Instruction Set Summary, shown in Table 24-2, lists the instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup>). **Section 24.2** "Instruction **Set**" provides a description of each instruction.

### 24.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a "BCF PORTB, 1" instruction will read PORTB, clear bit 1 of the data, then write the result back to PORTB. The read operation would have the unintended result that any condition that sets the RBIF flag would be cleared. The R-M-W operation may also copy the level of an input pin to its corresponding output latch.

After Instruction

If Carry PC If Carry PC

= = =

| ANDWF             | AND W with f                                                                                                                                                                                           |                                                                                 | BC             | Branch if                                                       | Carry                         |                 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------|-------------------------------|-----------------|

| Syntax:           | [label] ANDWF f                                                                                                                                                                                        | ,d [,a]]                                                                        | Syntax:        | [ <i>label</i> ] E                                              | BC n                          |                 |

| Operands:         | $0 \leq f \leq 255$                                                                                                                                                                                    |                                                                                 | Operands:      | -128 ≤ n ≤                                                      | ≤ <b>12</b> 7                 |                 |

|                   | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                 |                                                                                 | Operation:     | if Carry bi<br>(PC) + 2 ·                                       | t is '1',<br>+ 2n → PC        |                 |

| Operation:        | (W) .AND. (f) $\rightarrow$ dest                                                                                                                                                                       |                                                                                 | Status Affect  | ed: None                                                        |                               |                 |

| Status Affected:  | N, Z                                                                                                                                                                                                   |                                                                                 | Encoding:      | 1110                                                            | 0010 nn                       | nn nnnn         |

| Encoding:         | 0001 01da ff                                                                                                                                                                                           | ff ffff                                                                         | Description:   | If the Car                                                      | ry bit is '1', th             | ien the         |

| Description:      | The contents of W are<br>register 'f'. If 'd' is '0', t<br>stored in W. If 'd' is '1'<br>stored back in register<br>If 'a' is '0', the Access<br>selected. If 'a' is '1', th<br>not be overridden (def | he result is<br>, the result is<br>'f' (default).<br>Bank will be<br>e BSR will |                | The 2's co<br>added to<br>have incre<br>instruction<br>PC + 2 + | the PC. Sinc<br>emented to fe |                 |

| Words:            | 1                                                                                                                                                                                                      |                                                                                 | Words:         | 1                                                               |                               |                 |

| Cycles:           | 1                                                                                                                                                                                                      |                                                                                 | Cycles:        | 1(2)                                                            |                               |                 |

| Q Cycle Activity: |                                                                                                                                                                                                        |                                                                                 | Q Cycle Act    | ivity:                                                          |                               |                 |

| Q1                | Q2 Q3                                                                                                                                                                                                  | Q4                                                                              | If Jump:       |                                                                 |                               | _               |

| Decode            | Read Process                                                                                                                                                                                           | Write to                                                                        | Q1             | Q2                                                              | Q3                            | Q4              |

|                   | register 'f' Data                                                                                                                                                                                      | destination                                                                     | Decod          | e Read literal<br>'n'                                           | Process<br>Data               | Write to PC     |

| Example:          | ANDWF REG, W                                                                                                                                                                                           |                                                                                 | No<br>operati  | No<br>on operation                                              | No<br>operation               | No<br>operation |

| Before Instru     |                                                                                                                                                                                                        |                                                                                 | If No Jump:    |                                                                 |                               |                 |

| W<br>REG          | = 0x17<br>= 0xC2                                                                                                                                                                                       |                                                                                 | Q1             | Q2                                                              | Q3                            | Q4              |

| After Instruct    | ion                                                                                                                                                                                                    |                                                                                 | Decod          | e Read literal                                                  | Process<br>Data               | No<br>operation |

| W<br>REG          | = 0x02<br>= 0xC2                                                                                                                                                                                       |                                                                                 |                |                                                                 | Dulu                          | operation       |

| REG               | = 0xC2                                                                                                                                                                                                 |                                                                                 | Example:       | HERE                                                            | BC JUMP                       | )               |

|                   |                                                                                                                                                                                                        |                                                                                 | Before I<br>PC | nstruction<br>= ac                                              | Idress (HERE                  | )               |

1; address (JUMP) 0; address (HERE + 2)

| BNOV                                                  | Branch if                                                                        | Not Overflo                                                                                                                                                                                                                                                                 | w           | BNZ         |  |  |  |

|-------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--|--|--|

| Syntax:                                               | [ <i>label</i> ] B                                                               | [ <i>label</i> ] BNOV n                                                                                                                                                                                                                                                     |             |             |  |  |  |

| Operands:                                             | -128 ≤ n ≤                                                                       | $-128 \le n \le 127$                                                                                                                                                                                                                                                        |             |             |  |  |  |

| Operation:                                            |                                                                                  | if Overflow bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                   |             |             |  |  |  |

| Status Affected:                                      | None                                                                             |                                                                                                                                                                                                                                                                             |             | Stat        |  |  |  |

| Encoding:                                             | 1110                                                                             | 0101 nni                                                                                                                                                                                                                                                                    | nn nnnn     | Enc         |  |  |  |

| Description:                                          | program v<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC + 2 + 2 | If the Overflow bit is '0', then the program will branch.<br>The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be $PC + 2 + 2n$ . This instruction is then a two-cycle instruction. |             |             |  |  |  |

| Words:                                                | 1                                                                                |                                                                                                                                                                                                                                                                             |             | Wor         |  |  |  |

| Cycles:                                               | 1(2)                                                                             |                                                                                                                                                                                                                                                                             |             | Сус         |  |  |  |

| Q Cycle Activity<br>If Jump:                          | :                                                                                |                                                                                                                                                                                                                                                                             |             | Q (<br>If J |  |  |  |

| Q1                                                    | Q2                                                                               | Q3                                                                                                                                                                                                                                                                          | Q4          | -           |  |  |  |

| Decode                                                | Read literal<br>'n'                                                              | Process<br>Data                                                                                                                                                                                                                                                             | Write to PC |             |  |  |  |

| No                                                    | No                                                                               | No                                                                                                                                                                                                                                                                          | No          |             |  |  |  |

| operation                                             | operation                                                                        | operation                                                                                                                                                                                                                                                                   | operation   | ]<br>If N   |  |  |  |

| If No Jump:<br>Q1                                     | Q2                                                                               | Q3                                                                                                                                                                                                                                                                          | 04          | IT IN       |  |  |  |

| Decode                                                | Read literal                                                                     | Process                                                                                                                                                                                                                                                                     | Q4<br>No    | 1           |  |  |  |

| Decode                                                | 'n'                                                                              | Data                                                                                                                                                                                                                                                                        | operation   |             |  |  |  |

| Example:<br>Before Instr<br>PC                        |                                                                                  | BNOV Jump<br>dress (HERE)                                                                                                                                                                                                                                                   |             | Exa         |  |  |  |

| After Instruc<br>If Overflu<br>PC<br>If Overflu<br>PC | ow = 0;<br>= ad<br>ow = 1;                                                       | dress (Jump)<br>dress (HERE                                                                                                                                                                                                                                                 |             |             |  |  |  |

| Syntax:                       | [ <i>label</i> ] B                                                                                                                                                                         | [ <i>label</i> ] BNZ n                                |                 |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|--|--|--|

| Operands:                     | -128 < n <                                                                                                                                                                                 |                                                       |                 |  |  |  |

| •                             |                                                                                                                                                                                            |                                                       |                 |  |  |  |

| Operation:                    |                                                                                                                                                                                            | if Zero bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC |                 |  |  |  |

| Status Affected:              | None                                                                                                                                                                                       |                                                       |                 |  |  |  |

| Encoding:                     | 1110                                                                                                                                                                                       | 0001 nni                                              | nn nnnn         |  |  |  |

| Description:                  | Description: If the Zero bit is '0<br>program will branc<br>The 2's compleme<br>added to the PC. S<br>have incremented<br>instruction, the new<br>PC + 2 + 2n. This<br>then a two-cycle in |                                                       |                 |  |  |  |

| Words:                        | 1                                                                                                                                                                                          | 1                                                     |                 |  |  |  |

| Cycles:                       | 1(2)                                                                                                                                                                                       | 1(2)                                                  |                 |  |  |  |

| Q Cycle Activity:<br>If Jump: |                                                                                                                                                                                            |                                                       |                 |  |  |  |

| Q1                            | Q2                                                                                                                                                                                         | Q3                                                    | Q4              |  |  |  |

| Decode                        | Read literal<br>'n'                                                                                                                                                                        | Process<br>Data                                       | Write to PC     |  |  |  |

| No                            | No                                                                                                                                                                                         | No                                                    | No              |  |  |  |

| operation                     | operation                                                                                                                                                                                  | operation                                             | operation       |  |  |  |

| If No Jump:                   |                                                                                                                                                                                            |                                                       |                 |  |  |  |

| Q1                            | Q2                                                                                                                                                                                         | Q3                                                    | Q4              |  |  |  |

| Decode                        | Read literal<br>'n'                                                                                                                                                                        | Process<br>Data                                       | No<br>operation |  |  |  |

|                               |                                                                                                                                                                                            |                                                       |                 |  |  |  |

| Example:                      | HERE                                                                                                                                                                                       | BNZ Jump                                              |                 |  |  |  |

| Example:<br>Before Instru     | HERE                                                                                                                                                                                       | BNZ Jump                                              |                 |  |  |  |

| PC                             | =           | address (HERE)                                   |

|--------------------------------|-------------|--------------------------------------------------|

| After Instruction              |             |                                                  |

| If Zero<br>PC<br>If Zero<br>PC | =<br>=<br>= | 0;<br>address (Jump)<br>1;<br>address (HERE + 2) |

| BRA   | <b>x</b>                                 | Unconditi                                                                                                | ional Branc                                    | h                                                                         | BS                      | F                       | Bit Set f                               |                                                    |                                                    |

|-------|------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|-------------------------|-------------------------|-----------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Synt  | tax:                                     | [ <i>label</i> ] B                                                                                       | RA n                                           |                                                                           | Sy                      | ntax:                   | [ <i>label</i> ] B                      | SF f,b[,a]                                         |                                                    |

| Ope   | rands:                                   | -1024 ≤ n                                                                                                | ≤ 1023                                         |                                                                           | Ор                      | erands:                 | $0 \le f \le 255$                       | 5                                                  |                                                    |

| Ope   | ration:                                  | (PC) + 2 +                                                                                               | $2n \rightarrow PC$                            |                                                                           |                         |                         | 0 ≤ b ≤ 7<br>a ∈ [0,1]                  |                                                    |                                                    |

| Statu | us Affected:                             | None                                                                                                     |                                                |                                                                           | On                      | eration:                | a ∈ [0, l]<br>1 → f <b></b>             |                                                    |                                                    |

| Enco  | oding:                                   | 1101                                                                                                     | 0nnn nn                                        | nn nnnn                                                                   | -                       | tus Affected:           | None None                               |                                                    |                                                    |

| Des   | cription:                                | Add the 2's complement number<br>'2n' to the PC. Since the PC will<br>have incremented to fetch the next |                                                | dd the 2's complement number<br>n' to the PC. Since the PC will Encoding: |                         | coding:                 | 1000                                    | bbba ff:                                           | ff ffff<br>et. If 'a' is '0',                      |

|       |                                          | PC + 2 + 2                                                                                               | , the new ad<br>2n. This instr<br>instruction. | dress will be<br>ruction is a                                             |                         |                         | Access Ba<br>riding the I<br>the bank v | ank will be se<br>BSR value. If<br>vill be selecte | elected, over-<br>f 'a' = 1, then<br>ed as per the |

| Wor   | ds:                                      | 1                                                                                                        |                                                |                                                                           |                         |                         | BSR value                               | <b>.</b>                                           |                                                    |

| Cycl  | es:                                      | 2                                                                                                        |                                                |                                                                           |                         | ords:                   | 1                                       |                                                    |                                                    |

| QC    | Cycle Activity:                          | :                                                                                                        |                                                |                                                                           | Cy                      | cles:                   | 1                                       |                                                    |                                                    |

|       | Q1                                       | Q2                                                                                                       | Q3                                             | Q4                                                                        | Q                       | Cycle Activity          | :                                       |                                                    |                                                    |