Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

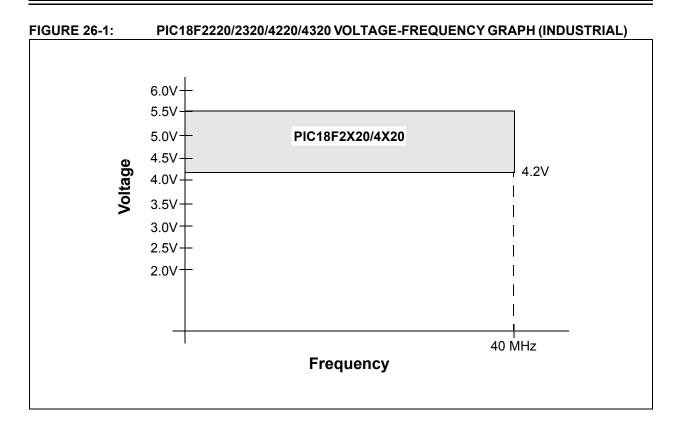

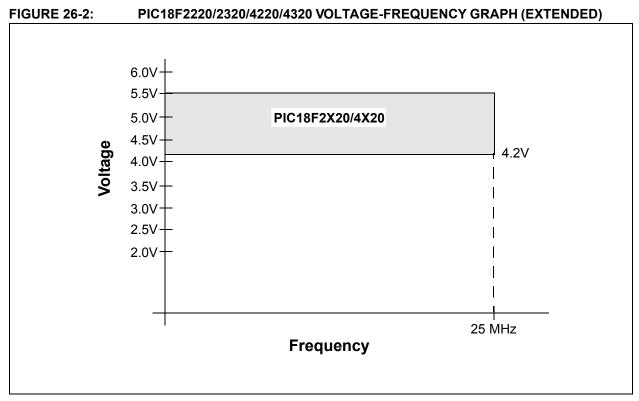

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

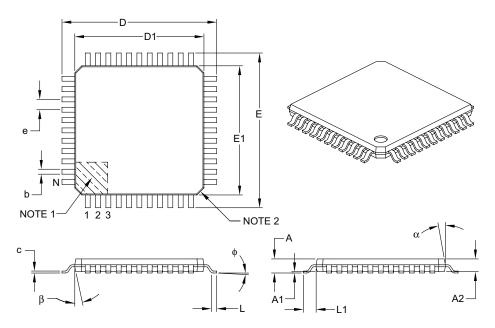

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2220-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.8 Look-up Tables

Look-up tables are implemented two ways:

- Computed GOTO

- Table Reads

#### 5.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-4.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW  $0 \times nn$  instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW  $0 \times nn$  instructions that returns the value  $0 \times nn$  to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSB = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-4: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVFW  | OFFSET |

|-------|--------|--------|

|       | CALL   | TABLE  |

| ORG   | 0xnn00 |        |

| TABLE | ADDWF  | PCL    |

|       | RETLW  | 0xnn   |

|       | RETLW  | 0xnn   |

|       | RETLW  | 0xnn   |

|       | •      |        |

|       | •      |        |

|       | •      |        |

|       |        |        |

#### 5.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory, one byte at a time.

The Table Read/Table Write operation is discussed further in Section 6.1 "Table Reads and Table Writes".

#### 5.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 5-6 shows the data memory organization for the PIC18F2X20/4X20 devices.

The data memory map is divided into as many as 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits of the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (FFFh) and extend towards F80h. Any remaining space beyond the SFRs in the bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the data memory map without banking. See Section 5.12 "Indirect Addressing, INDF and FSR Registers" for indirect addressing details.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. **Section 5.10 "Access Bank"** provides a detailed description of the Access RAM.

#### 5.9.1 GENERAL PURPOSE REGISTER FILE

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

Data RAM is available for use as GPR registers by all instructions. The second half of Bank 15 (F80h to FFFh) contains SFRs. All other banks of data memory contain GPRs, starting with Bank 0.

### 7.0 DATA EEPROM MEMORY

The data EEPROM is readable and writable during normal operation over the entire VDD range. The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are four SFRs used to read and write the program and data EEPROM memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADR

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 256 bytes of data EEPROM with an address range from 00h to FFh.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip to chip. Please refer to parameter D122 (Table 26-1 in **Section 26.0 "Electrical Characteristics"**) for exact limits.

### 7.1 EEADR

The address register can address 256 bytes of data EEPROM.

### 7.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed. Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either Flash program or data EEPROM memory.

The WREN bit enables and disables erase and write operations. When set, erase and write operations are allowed. When clear, erase and write operations are disabled; the WR bit cannot be set while the WREN bit is clear. This mechanism helps to prevent accidental writes to memory due to errant (unexpected) code execution.

Firmware should keep the WREN bit clear at all times except when starting erase or write operations. Once firmware has set the WR bit, the WREN bit may be cleared. Clearing the WREN bit will not affect the operation in progress.

The WRERR bit is set when a write operation is interrupted by a Reset. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), as these registers have cleared as a result of the Reset.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 6.1 "Table Reads and Table Writes"** regarding table reads.

Note: Interrupt flag bit, EEIF in the PIR2 register, is set when write is complete. It must be cleared in software.

| R/W-1         | R/W-1                          | U-0                                                | R/W-1           | R/W-1            | R/W-1           | R/W-1           | R/W-1  |

|---------------|--------------------------------|----------------------------------------------------|-----------------|------------------|-----------------|-----------------|--------|

| OSCFIP        | CMIP                           | —                                                  | EEIP            | BCLIP            | LVDIP           | TMR3IP          | CCP2IP |

| bit 7         |                                |                                                    |                 |                  |                 |                 | bit 0  |

| <b></b>       |                                |                                                    |                 |                  |                 |                 |        |

| Legend:       |                                |                                                    |                 |                  |                 |                 |        |

| R = Readable  | e bit                          | W = Writable                                       | bit             | U = Unimple      | mented bit, rea | id as '0'       |        |

| -n = Value at | POR                            | '1' = Bit is set                                   |                 | '0' = Bit is cle | eared           | x = Bit is unkr | nown   |

|               |                                |                                                    |                 |                  |                 |                 |        |

| bit 7         |                                | cillator Fail Inter                                | rupt Priority b | oit              |                 |                 |        |

|               | 1 = High priot                 |                                                    |                 |                  |                 |                 |        |

| bit 6         | 0 = Low prior                  | arator Interrupt                                   | Priority bit    |                  |                 |                 |        |

| DILO          | 1 = High prio                  |                                                    | FIIOIILY DIL    |                  |                 |                 |        |

|               | 0 = Low prior                  |                                                    |                 |                  |                 |                 |        |

| bit 5         | Unimplemen                     | ted: Read as '                                     | o <b>'</b>      |                  |                 |                 |        |

| bit 4         | EEIP: Data E                   | EPROM/Flash Write Operation Interrupt Priority bit |                 |                  |                 |                 |        |

|               | 1 = High prio                  | ,                                                  |                 |                  |                 |                 |        |

|               | 0 = Low prior                  | •                                                  |                 |                  |                 |                 |        |

| bit 3         |                                | Collision Interru                                  | pt Priority bit |                  |                 |                 |        |

|               | 1 = High prio<br>0 = Low prior |                                                    |                 |                  |                 |                 |        |

| bit 2         | •                              | Voltage Detect                                     | Interrupt Prio  | ritv bit         |                 |                 |        |

|               | 1 = High price                 | •                                                  |                 |                  |                 |                 |        |

|               | 0 = Low prior                  | rity                                               |                 |                  |                 |                 |        |

| bit 1         | TMR3IP: TM                     | R3 Overflow Int                                    | errupt Priority | y bit            |                 |                 |        |

|               | 1 = High pric                  |                                                    |                 |                  |                 |                 |        |

| 1.1.0         | 0 = Low prior                  |                                                    |                 |                  |                 |                 |        |

| bit 0         |                                | P2 Interrupt Prio                                  | ority bit       |                  |                 |                 |        |

|               | 1 = High prio<br>0 = Low prior |                                                    |                 |                  |                 |                 |        |

|               | o pilo                         | ···· <b>·</b>                                      |                 |                  |                 |                 |        |

#### REGISTER 9-9: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

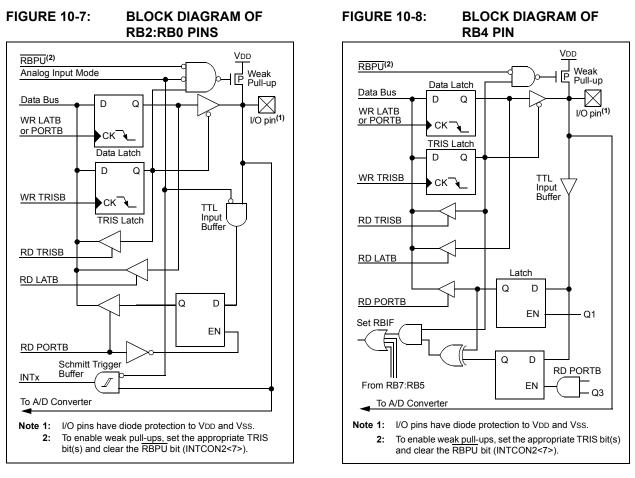

#### FIGURE 10-9: BLOCK DIAGRAM OF RB3/CCP2 PIN

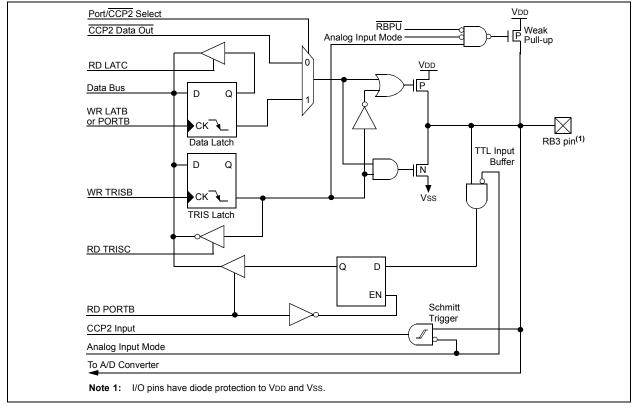

#### 10.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-5). The pins have Schmitt Trigger input buffers. RC1 is normally configured by Configuration bit, CCP2MX (CONFIG3H<0>), as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents even though a peripheral device may be overriding one or more of the pins.

#### EXAMPLE 10-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | OxCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs |

|       |       | ; RC<5:4> as outputs    |

|       |       | ; RC<7:6> as inputs     |

|       |       |                         |

#### FIGURE 10-10: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

### 14.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers: TMR3H and TMR3L)

- Readable and writable (both registers)

- · Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Figure 14-1 is a simplified block diagram of the Timer3 module.

Register 14-1 shows the Timer3 Control register. This register controls the operating mode of the Timer3 module and sets the CCP clock source.

Register 12-1 shows the Timer1 Control register. This register controls the operating mode of the Timer1 module, as well as contains the Timer1 Oscillator Enable bit (T1OSCEN) which can be a clock source for Timer3.

#### REGISTER 14-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

| Legend:      |                      |                                                                                     |                                                    |                                        |  |  |  |  |

|--------------|----------------------|-------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|--|--|--|--|

| R = Readal   | ole bit              | W = Writable bit                                                                    | U = Unimplemented bit                              | t, read as '0'                         |  |  |  |  |

| -n = Value a | at POR               | '1' = Bit is set                                                                    | '0' = Bit is cleared                               | x = Bit is unknown                     |  |  |  |  |

| bit 7        | <b>RD16</b> : 16     | -Bit Read/Write Mode Enab                                                           | le bit                                             |                                        |  |  |  |  |

|              |                      | oles register read/write of Tin<br>oles register read/write of Tin                  |                                                    |                                        |  |  |  |  |

| bit 6, 3     | T3CCP2:              | T3CCP1: Timer3 and Timer                                                            | 1 to CCPx Enable bits                              |                                        |  |  |  |  |

|              | 01 = Tim<br>Tim      | er3 is the capture/compare o<br>er1 is the capture/compare o                        |                                                    |                                        |  |  |  |  |

| bit 5-4      | T3CKPS               | 1:T3CKPS0: Timer3 Input C                                                           | lock Prescale Select bits                          |                                        |  |  |  |  |

|              |                      | 11 = 1:8 Prescale value                                                             |                                                    |                                        |  |  |  |  |

|              |                      | 10 = 1:4 Prescale value<br>01 = 1:2 Prescale value                                  |                                                    |                                        |  |  |  |  |

|              |                      | 00 = 1.1 Prescale value                                                             |                                                    |                                        |  |  |  |  |

| bit 2        |                      | : Timer3 External Clock Inpu<br>le if the device clock comes                        | t Synchronization Control bit from Timer1/Timer3.) |                                        |  |  |  |  |

|              | 1 = Do no            | I <u>R3CS = 1:</u><br>ot synchronize external clock<br>nronize external clock input | (input                                             |                                        |  |  |  |  |

|              |                      | I <u>R3CS = 0:</u><br>ignored. Timer3 uses the in                                   | ternal clock when TMR3CS =                         | = 0.                                   |  |  |  |  |

| bit 1        | TMR3CS               | TMR3CS: Timer3 Clock Source Select bit                                              |                                                    |                                        |  |  |  |  |

|              |                      | rnal clock input from Timer1 o<br>nal clock (Fosc/4)                                | oscillator or T13CKI (on the ris                   | sing edge after the first falling edge |  |  |  |  |

| bit 0        | TMR3ON               | : Timer3 On bit                                                                     |                                                    |                                        |  |  |  |  |

|              | 1 = Enat<br>0 = Stop | oles Timer3<br>s Timer3                                                             |                                                    |                                        |  |  |  |  |

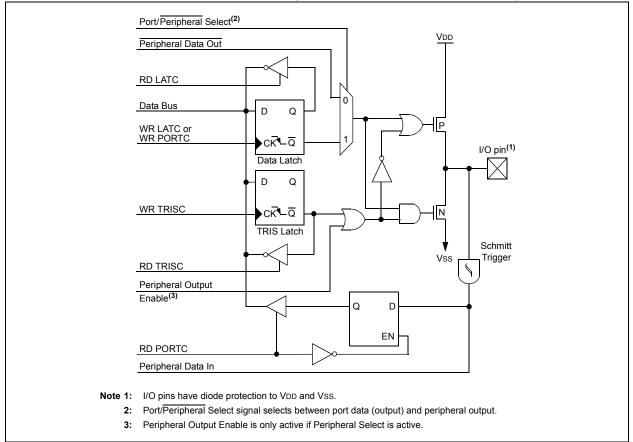

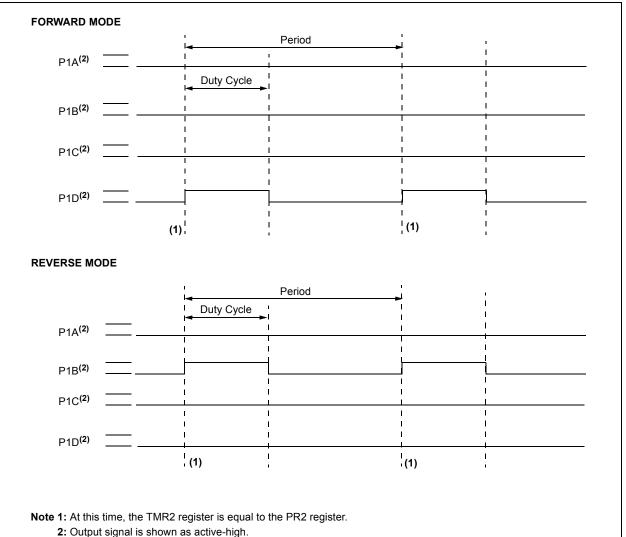

### 16.4.3 FULL-BRIDGE MODE

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, pin RC2/CCP1/P1A is continuously active and pin RD7/PSP7/P1D is modulated. In the Reverse mode, RD6/PSP6/P1C pin is continuously active and RD5/PSP5/P1B pin is modulated. These are illustrated in Figure 16-6.

P1A, P1B, P1C and P1D outputs are multiplexed with the PORTC<2> and PORTD<5:7> data latches. The TRISC<2> and TRISD<5:7> bits must be cleared to make the P1A, P1B, P1C and P1D pins output.

#### FIGURE 16-6: FULL-BRIDGE PWM OUTPUT

#### 17.3.8 MASTER IN POWER-MANAGED MODES

In Master mode, module clocks may be operating at a different speed than when in full-power mode, or in the case of the power-managed Sleep mode, all clocks are halted.

In most power-managed modes, a clock is provided to the peripherals and is derived from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the internal oscillator block (one of eight frequencies between 31 kHz and 8 MHz). See Section 2.7 "Clock Sources and Oscillator Switching" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from a power-managed mode when the master completes sending data. If an exit from a powermanaged mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will pause until the device wakes from the power-managed mode. After the device returns to full-power mode, the module will resume transmitting and receiving data.

#### 17.3.8.1 Slave in Power-Managed Modes

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if MSSP interrupts are enabled, will wake the device from a power-managed mode.

#### 17.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.3.10 BUS MODE COMPATIBILITY

Table 17-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |

|-------------------|--------------------|-----|--|--|

| Terminology       | СКР                | CKE |  |  |

| 0, 0              | 0                  | 1   |  |  |

| 0, 1              | 0                  | 0   |  |  |

| 1, 0              | 1                  | 1   |  |  |

| 1, 1              | 1                  | 0   |  |  |

#### TABLE 17-1: SPI BUS MODES

There is also an SMP bit which controls when the data is sampled.

|         |                       |                       |             |                               |       |        |        |        | Value on  | Value on            |

|---------|-----------------------|-----------------------|-------------|-------------------------------|-------|--------|--------|--------|-----------|---------------------|

| Name    | Bit 7                 | Bit 6                 | Bit 5       | Bit 4                         | Bit 3 | Bit 2  | Bit 1  | Bit 0  | POR, BOR  | all other<br>Resets |

| INTCON  | GIE/GIEH              | PEIE/<br>GIEL         | TMR0IE      | INT0IE                        | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x | 0000 000u           |

| PIR1    | PSPIF <sup>(1)</sup>  | ADIF                  | RCIF        | TXIF                          | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000 | 0000 0000           |

| PIE1    | PSPIE <sup>(1)</sup>  | ADIE                  | RCIE        | TXIE                          | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000 | 0000 0000           |

| IPR1    | PSPIP <sup>(1)</sup>  | ADIP                  | RCIP        | TXIP                          | SSPIP | CCP1IP | TMR2IP | TMR1IP | 1111 1111 | 1111 1111           |

| TRISC   | PORTC Da              | ata Direction         | Register    |                               |       |        |        |        | 1111 1111 | 1111 1111           |

| SSPBUF  | MSSP Rec              | eive Buffer/          | Transmit Re | gister                        |       |        |        |        | XXXX XXXX | uuuu uuuu           |

| SSPCON1 | WCOL                  | SSPOV                 | SSPEN       | CKP                           | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 0000 0000 | 0000 0000           |

| TRISA   | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da    | PORTA Data Direction Register |       |        |        |        | 11 1111   | 11 1111             |

| SSPSTAT | SMP                   | CKE                   | D/A         | Р                             | S     | R/W    | UA     | BF     | 0000 0000 | 0000 0000           |

| 1       |                       |                       |             |                               |       |        |        |        |           |                     |

### TABLE 17-2: REGISTERS ASSOCIATED WITH SPI OPERATION

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode. **Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X20 devices; always maintain these bits clear.

### 17.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 17.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

#### 17.4.7.2 Clock Arbitration

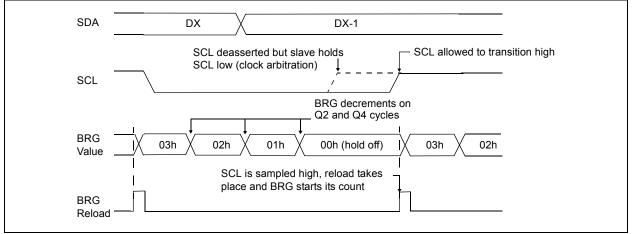

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 17-18).

#### 17.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full Flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit, during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 17-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 17.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 17.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 17.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

#### 17.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 17.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 17.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 17.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

| R/W-0        | U-0                                                                                                                                     | R/W-0                | R/W-0       | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|--------------------------|------------------|-----------------|-------|

| ADFM         |                                                                                                                                         | ACQT2                | ACQT1       | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |

| bit 7        |                                                                                                                                         |                      |             |                          |                  |                 | bit C |

|              |                                                                                                                                         |                      |             |                          |                  |                 |       |

| Legend:      |                                                                                                                                         |                      |             |                          |                  |                 |       |

| R = Readat   | ole bit                                                                                                                                 | W = Writable         | bit         | U = Unimplen             | nented bit, read | d as '0'        |       |

| -n = Value a | at POR                                                                                                                                  | '1' = Bit is set     |             | '0' = Bit is cle         | ared             | x = Bit is unkr | nown  |

| bit 7        | <b>ADFM:</b> A/D R<br>1 = Right justi<br>0 = Left justifi                                                                               |                      | Select bit  |                          |                  |                 |       |

| bit 6        | •                                                                                                                                       | ted: Read as '       | 0'          |                          |                  |                 |       |

| bit 5-3      | -                                                                                                                                       | T0: A/D Acquis       |             | lect hits                |                  |                 |       |

|              | 111 = 20 TAD<br>110 = 16 TAD<br>101 = 12 TAD<br>100 = 8 TAD<br>011 = 6 TAD<br>010 = 4 TAD<br>001 = 2 TAD<br>000 = 0 TAD <sup>(1</sup> ) | )                    |             |                          |                  |                 |       |

| bit 2-0      | 111 = FRC (cl<br>110 = Fosc/6<br>101 = Fosc/1<br>100 = Fosc/4                                                                           | 6<br>ock derived fro | m A/D RC os | cillator) <sup>(1)</sup> |                  |                 |       |

#### REGISTER 19-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

2: Mode 110 is exception. Comparator input pins obey TRISA bits.

#### 23.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

As previously mentioned, entering a power-managed mode clears the fail-safe condition. By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-safe monitoring of the power-managed clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, the device will not exit the power-managed mode on oscillator failure. Instead, the device will continue to operate as before but clocked by the INTOSC multiplexer. While in Idle mode, subsequent interrupts will cause the CPU to begin executing instructions while being clocked by the INTOSC multiplexer. The device will not transition to a different clock source until the fail-safe condition is cleared.

### 23.4.4 POR OR WAKE FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary system clock is EC, RC or INTRC modes, monitoring can begin immediately following these events.

For oscillator modes involving a crystal or resonator (HS, HSPLL, LP or XT), the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the system clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

| Note: | The same logic that prevents false oscilla-<br>tor failure interrupts on POR or wake from |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | Sleep will also prevent the detection of the                                              |  |  |  |  |  |  |

|       | oscillator's failure to start at all following                                            |  |  |  |  |  |  |

|       | these events. This can be avoided by                                                      |  |  |  |  |  |  |

|       | monitoring the OSTS bit and using a tim-                                                  |  |  |  |  |  |  |

|       | ing routine to determine if the oscillator is                                             |  |  |  |  |  |  |

|       | taking too long to start. Even so, no                                                     |  |  |  |  |  |  |

|       | oscillator failure interrupt will be flagged.                                             |  |  |  |  |  |  |

As noted in **Section 23.3.1 "Special Considerations for Using Two-Speed Start-up**", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary system clock to become stable. When the new powered managed mode is selected, the primary clock is disabled.

| DEC         | FSZ                                                  | Decreme                                                                                                                                | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |  |  |  |

|-------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|

| Synt        | ax:                                                  | [label] [                                                                                                                              | [ <i>label</i> ] DECFSZ f[,d[,a]]                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |  |  |  |

| Ope         | rands:                                               | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |

| Ope         | ration:                                              | (f) – 1 $\rightarrow$ oskip if res                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |

| Statu       | us Affected:                                         | None                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |

| Enco        | oding:                                               | 0010                                                                                                                                   | 11da ffi                                                                                                                                                                                                                                                                                                                                                                                                                                            | ff ffff                |  |  |  |

| Desc        | cription:                                            | decremen<br>is placed i<br>(default).<br>If the resu<br>tion which<br>carded an<br>instead, m<br>instruction<br>Bank will<br>the BSR v | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result<br>is placed back in register 'f'<br>(default).<br>If the result is '0', the next instruc-<br>tion which is already fetched is dis-<br>carded and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the |                        |  |  |  |

| 14/0        | de .                                                 | BSR value                                                                                                                              | bank will be selected as per the BSR value (default).                                                                                                                                                                                                                                                                                                                                                                                               |                        |  |  |  |

| Word        |                                                      | 1                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |

| Cycl<br>Q C | cs.<br>Cycle Activity                                | by                                                                                                                                     | ycles if skip a 2-word ins                                                                                                                                                                                                                                                                                                                                                                                                                          | and followed truction. |  |  |  |

|             | Q1                                                   | Q2                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q4                     |  |  |  |

|             | Decode                                               | Read<br>register 'f'                                                                                                                   | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                     | Write to destination   |  |  |  |

| lf sk       | kip:                                                 |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |

| 1           | Q1                                                   | Q2                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q4                     |  |  |  |

|             | No<br>operation                                      | No<br>operation                                                                                                                        | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                     | No<br>operation        |  |  |  |

| lf sk       |                                                      |                                                                                                                                        | d instruction:                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |  |  |  |

|             | Q1                                                   | Q2                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q4                     |  |  |  |

|             | No                                                   | No                                                                                                                                     | No                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                     |  |  |  |

|             | operation                                            | operation                                                                                                                              | operation                                                                                                                                                                                                                                                                                                                                                                                                                                           | operation              |  |  |  |

|             | No<br>operation                                      | No<br>operation                                                                                                                        | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                     | No<br>operation        |  |  |  |

| Example:    |                                                      | HERE                                                                                                                                   | DECFSZ<br>GOTO                                                                                                                                                                                                                                                                                                                                                                                                                                      | CNT<br>LOOP            |  |  |  |

|             | Before Instru<br>PC<br>After Instruc                 | = Address                                                                                                                              | S (HERE)                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        |  |  |  |

|             | Anter Instruc<br>CNT<br>If CNT<br>PC<br>If CNT<br>PC | = CNT –<br>= 0;<br>= Address<br>≠ 0;                                                                                                   | 1<br>s (Continue<br>s (Here + 2                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |

|             |                                                      |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |  |  |

| DCF         | SNZ                                                      | Decreme                                                                                                                                                                                                                                                                                                                                                                                                                              | nt f, Skip if r                | not 0           |  |  |

|-------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|--|--|

| Synt        | tax:                                                     | [label]                                                                                                                                                                                                                                                                                                                                                                                                                              | DCFSNZ f[                      | ,d [,a]]        |  |  |

| Оре         | rands:                                                   | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                  |                                |                 |  |  |

| Ope         | ration:                                                  | $(f) - 1 \rightarrow c$ skip if resi                                                                                                                                                                                                                                                                                                                                                                                                 |                                |                 |  |  |

| Statu       | us Affected:                                             | None                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                |                 |  |  |

| Enco        | oding:                                                   | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11da fff                       | f ffff          |  |  |

| Wor<br>Cycl |                                                          | <ul> <li>decremented. If 'd' is '0', the resis placed in W. If 'd' is '1', the resis placed back in register 'f' (default).</li> <li>If the result is not '0', the next instruction which is already fetcl is discarded and a NOP is executing instruction. If 'a' is '0', the Acce Bank will be selected, overridin the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value (default).</li> <li>1</li> </ul> |                                |                 |  |  |

| QC          | Cycle Activity:                                          | by                                                                                                                                                                                                                                                                                                                                                                                                                                   | cycles if skip<br>a 2-word ins |                 |  |  |

|             | Q1                                                       | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q3                             | Q4              |  |  |

|             | Decode                                                   | Read                                                                                                                                                                                                                                                                                                                                                                                                                                 | Process                        | Write to        |  |  |

|             |                                                          | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                         | Data                           | destination     |  |  |

| lf sl       |                                                          | 00                                                                                                                                                                                                                                                                                                                                                                                                                                   | 02                             | 04              |  |  |

|             | Q1<br>No                                                 | Q2<br>No                                                                                                                                                                                                                                                                                                                                                                                                                             | Q3<br>No                       | Q4<br>No        |  |  |

|             | operation                                                | operation                                                                                                                                                                                                                                                                                                                                                                                                                            | operation                      | operation       |  |  |

| lf sł       | kip and follow                                           | ed by 2-wor                                                                                                                                                                                                                                                                                                                                                                                                                          | d instruction:                 |                 |  |  |

|             | Q1                                                       | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q3                             | Q4              |  |  |

|             | No<br>operation                                          | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                      | No<br>operation                | No<br>operation |  |  |

|             | No                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                                   | No                             | No              |  |  |

|             | operation                                                | operation                                                                                                                                                                                                                                                                                                                                                                                                                            | operation                      | operation       |  |  |

| <u>Exa</u>  | <u>mple</u> :                                            | ZERO                                                                                                                                                                                                                                                                                                                                                                                                                                 | DCFSNZ TEM<br>:<br>:           | IP              |  |  |

|             | Before Instru<br>TEMP                                    | =                                                                                                                                                                                                                                                                                                                                                                                                                                    | ?                              |                 |  |  |

|             | After Instruct<br>TEMP<br>If TEMP<br>PC<br>If TEMP<br>PC | tion =<br>=<br>=<br>≠                                                                                                                                                                                                                                                                                                                                                                                                                | 0;                             | ZERO)<br>NZERO) |  |  |

| INCFSZ                                                                         |                                                       | Incremen                                                                                                                                                             | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                           |                         |  |  |  |

|--------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|

| Synt                                                                           | ax:                                                   | [label]                                                                                                                                                              | INCFSZ f[                                                                                                                                                                                                                                                                                                                        | ,d [,a]]                |  |  |  |

| Operands:                                                                      |                                                       | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                |                         |  |  |  |

| Operation:                                                                     |                                                       | .,                                                                                                                                                                   | (f) + 1 $\rightarrow$ dest,<br>skip if result = 0                                                                                                                                                                                                                                                                                |                         |  |  |  |