Welcome to E-XFL.COM

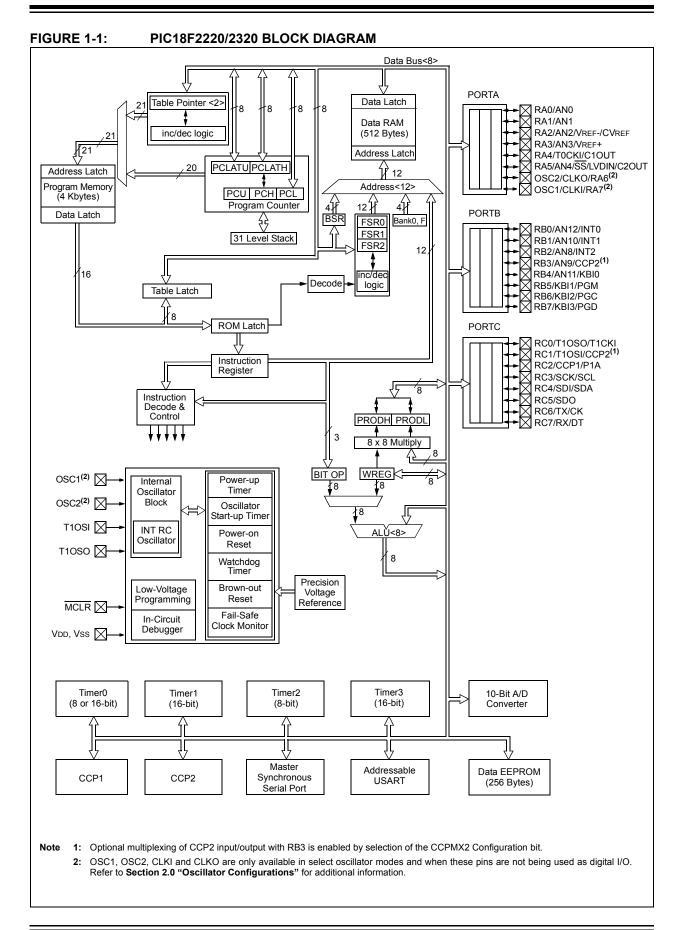

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2220-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

# TABLE 2-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Typical Capacitor Values<br>Tested: |       |  |  |

|----------|-----------------|-------------------------------------|-------|--|--|

| -        | Freq            | C1                                  | C2    |  |  |

| LP       | 32 kHz          | 33 pF                               | 33 pF |  |  |

|          | 200 kHz         | 15 pF                               | 15 pF |  |  |

| XT       | 1 MHz           | 33 pF                               | 33 pF |  |  |

|          | 4 MHz           | 27 pF                               | 27 pF |  |  |

| HS       | 4 MHz           | 27 pF                               | 27 pF |  |  |

|          | 8 MHz           | 22 pF                               | 22 pF |  |  |

|          | 20 MHz          | 15 pF                               | 15 pF |  |  |

|          |                 |                                     | _     |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. **These values are not optimized.**

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crysta  | als Used: |

|---------|-----------|

| 32 kHz  | 4 MHz     |

| 200 kHz | 8 MHz     |

| 1 MHz   | 20 MHz    |

- Note 1: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- Rs may be required to avoid overdriving crystals with low drive level specification.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

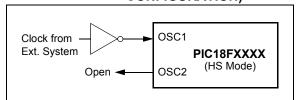

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 2-2.

#### EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

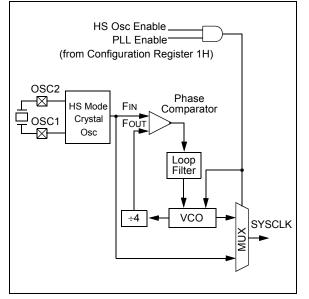

### 2.3 HSPLL

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency crystal oscillator circuit, or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals.

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz.

The PLL is enabled only when the oscillator Configuration bits are programmed for HSPLL mode. If programmed for any other mode, the PLL is not enabled.

### FIGURE 2-3: PLL BLOCK DIAGRAM

|              | 2-3. 0000                                                                                                                                                |                    |                |                                      |                  |                 |       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|--------------------------------------|------------------|-----------------|-------|

| R/W-0        | R/W-0                                                                                                                                                    | R/W-0              | R/W-0          | R <sup>(1)</sup>                     | R-0              | R/W-0           | R/W-0 |

| IDLEN        | IRCF2                                                                                                                                                    | IRCF1              | IRCF0          | OSTS                                 | IOFS             | SCS1            | SCS0  |

| bit 7        |                                                                                                                                                          |                    |                |                                      |                  |                 | bit ( |

|              |                                                                                                                                                          |                    |                |                                      |                  |                 |       |

| Legend:      |                                                                                                                                                          |                    |                |                                      |                  |                 |       |

| R = Readab   |                                                                                                                                                          | W = Writable       | bit            | U = Unimpler                         | mented bit, read | 1 as '0'        |       |

| -n = Value a | It POR                                                                                                                                                   | '1' = Bit is se    | t              | '0' = Bit is cle                     | ared             | x = Bit is unkr | nown  |

|              |                                                                                                                                                          |                    |                |                                      |                  |                 |       |

| bit 7        | IDLEN: Idle                                                                                                                                              | Enable bit         |                |                                      |                  |                 |       |

|              |                                                                                                                                                          |                    |                | clocked in powe                      |                  |                 |       |

|              |                                                                                                                                                          |                    |                | cked in power-n                      | nanaged modes    | 3               |       |

| bit 6-4      |                                                                                                                                                          | 0: Internal Osci   | •              |                                      |                  |                 |       |

|              |                                                                                                                                                          | z (8 MHz source    | e drives clock | directly)                            |                  |                 |       |

|              | 110 = 4 MH:<br>101 = 2 MH:                                                                                                                               |                    |                |                                      |                  |                 |       |

|              | 101 = 2  MHz<br>100 = 1  MHz                                                                                                                             |                    |                |                                      |                  |                 |       |

|              | 011 <b>= 500 k</b>                                                                                                                                       |                    |                |                                      |                  |                 |       |

|              | 010 <b>= 250 k</b>                                                                                                                                       |                    |                |                                      |                  |                 |       |

|              | 001 <b>= 125 k</b>                                                                                                                                       |                    |                |                                      |                  |                 |       |

|              |                                                                                                                                                          | Iz (INTRC source   |                | • ·                                  |                  |                 |       |

| bit 3        | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup><br>1 = Oscillator Start-up Timer time-out has expired; primary oscillator is running |                    |                |                                      |                  |                 |       |

|              |                                                                                                                                                          | •                  |                | s expired; prima<br>running; primary | •                | •               |       |

| bit 2        |                                                                                                                                                          | SC Frequency S     |                | anning, primary                      |                  | ready           |       |

|              |                                                                                                                                                          | frequency is st    |                |                                      |                  |                 |       |

|              |                                                                                                                                                          | frequency is no    |                |                                      |                  |                 |       |

| bit 1-0      | SCS1:SCS0                                                                                                                                                | : System Clock     | Select bits    |                                      |                  |                 |       |

|              | 1x = Interna                                                                                                                                             | l oscillator block | (RC modes)     | )                                    |                  |                 |       |

|              |                                                                                                                                                          | oscillator (Seco   |                |                                      |                  |                 |       |

|              | 00 = Primary                                                                                                                                             | y oscillator (Sle  | ep and PRI_II  | DLE modes)                           |                  |                 |       |

| Note 1: D    | Depends on state                                                                                                                                         | e of IESO bit in   | Configuration  | Register 1H.                         |                  |                 |       |

| <b>2</b> : S | SCS0 may not be                                                                                                                                          | e set while T1O    | SCEN (T1CO     | N<3>) is clear.                      |                  |                 |       |

|              | -                                                                                                                                                        |                    | -              | -                                    |                  |                 |       |

#### REGISTER 2-3: OSCCON: OSCILLATOR CONTROL REGISTER

NOTES:

| TABLE 5-2              |                                          | JUIER               |                         | MARY (P    |              | .0/2320/4/     | 220/4320)                   |           | 1                    |                     |

|------------------------|------------------------------------------|---------------------|-------------------------|------------|--------------|----------------|-----------------------------|-----------|----------------------|---------------------|

| File Name              | Bit 7                                    | Bit 6               | Bit 5                   | Bit 4      | Bit 3        | Bit 2          | Bit 1                       | Bit 0     | Value on<br>POR, BOR | Details on<br>page: |

| OSCCON                 | IDLEN                                    | IRCF2               | IRCF1                   | IRCF0      | OSTS         | IOFS           | SCS1                        | SCS0      | 0000 q000            | 27, 47              |

| LVDCON                 | —                                        |                     | IRVST                   | LVDEN      | LVDL3        | LVDL2          | LVDL1                       | LVDL0     | 00 0101              | 47, 233             |

| WDTCON                 | —                                        |                     |                         | —          | _            |                | —                           | SWDTEN    | 0                    | 47, 247             |

| RCON                   | IPEN                                     | _                   | _                       | RI         | TO           | PD             | POR                         | BOR       | 01 11q0              | 45, 69, 98          |

| TMR1H                  | Timer1 Regis                             | ster High Byte      |                         |            |              |                |                             |           | XXXX XXXX            | 47, 125             |

| TMR1L                  | Timer1 Regis                             | ster Low Byte       |                         |            |              |                |                             |           | XXXX XXXX            | 47, 125             |

| T1CON                  | RD16                                     | T1RUN               | T1CKPS1                 | T1CKPS0    | T1OSCEN      | T1SYNC         | TMR1CS                      | TMR10N    | 0000 0000            | 47, 121             |

| TMR2                   | Timer2 Regis                             | ster                |                         |            |              |                |                             |           | 0000 0000            | 47, 127             |

| PR2                    | Timer2 Perio                             | d Register          |                         |            |              |                |                             |           | 1111 1111            | 47, 127             |

| T2CON                  | —                                        | TOUTPS3             | TOUTPS2                 | TOUTPS1    | TOUTPS0      | TMR2ON         | T2CKPS1                     | T2CKPS0   | -000 0000            | 47, 127             |

| SSPBUF                 | MSSP Recei                               | ve Buffer/Trar      | nsmit Register          | -          |              |                |                             |           | XXXX XXXX            | 47, 156,<br>164     |

| SSPADD                 | MSSP Addre                               | ss Register ir      | I <sup>2</sup> C™ Slave | mode. MSSP | Baud Rate Re | eload Register | r in I <sup>2</sup> C Maste | r mode.   | 0000 0000            | 47, 164             |

| SSPSTAT                | SMP                                      | CKE                 | D/Ā                     | Р          | S            | R/W            | UA                          | BF        | 0000 0000            | 47, 156,<br>165     |

| SSPCON1                | WCOL                                     | SSPOV               | SSPEN                   | СКР        | SSPM3        | SSPM2          | SSPM1                       | SSPM0     | 0000 0000            | 47, 157,<br>166     |

| SSPCON2                | GCEN                                     | ACKSTAT             | ACKDT                   | ACKEN      | RCEN         | PEN            | RSEN                        | SEN       | 0000 0000            | 47, 167             |

| ADRESH                 | A/D Result Register High Byte            |                     |                         |            |              |                |                             | •         | XXXX XXXX            | 48, 220             |

| ADRESL                 | A/D Result R                             | egister Low B       | yte                     |            |              |                |                             |           | XXXX XXXX            | 48, 220             |

| ADCON0                 | _                                        | _                   | CHS3                    | CHS2       | CHS1         | CHS0           | GO/DONE                     | ADON      | 00 0000              | 48, 211             |

| ADCON1                 | —                                        | _                   | VCFG1                   | VCFG0      | PCFG3        | PCFG2          | PCFG1                       | PCFG0     | 00 0qqq              | 48, 212             |

| ADCON2                 | ADFM                                     | -                   | ACQT2                   | ACQT1      | ACQT0        | ADCS2          | ADCS1                       | ADCS0     | 0-00 0000            | 48, 213             |

| CCPR1H                 | Capture/Compare/PWM Register 1 High Byte |                     |                         |            |              |                | •                           | XXXX XXXX | 48, 134              |                     |

| CCPR1L                 | Capture/Com                              | npare/PWM R         | egister 1 Low           | Byte       |              |                |                             |           | XXXX XXXX            | 48, 134             |

| CCP1CON                | P1M1 <sup>(5)</sup>                      | P1M0 <sup>(5)</sup> | DC1B1                   | DC1B0      | CCP1M3       | CCP1M2         | CCP1M1                      | CCP1M0    | 0000 0000            | 48, 133,<br>141     |

| CCPR2H                 | Capture/Com                              | npare/PWM R         | egister 2 High          | Byte       |              |                |                             |           | XXXX XXXX            | 48, 134             |

| CCPR2L                 | Capture/Com                              | npare/PWM R         | egister 2 Low           | Byte       |              |                |                             |           | XXXX XXXX            | 48, 134             |

| CCP2CON                | —                                        |                     | DC2B1                   | DC2B0      | CCP2M3       | CCP2M2         | CCP2M1                      | CCP2M0    | 00 0000              | 48, 133             |

| PWM1CON <sup>(5)</sup> | PRSEN                                    | PDC6                | PDC5                    | PDC4       | PDC3         | PDC2           | PDC1                        | PDC0      | 0000 0000            | 48, 149             |

| ECCPAS <sup>(5)</sup>  | ECCPASE                                  | ECCPAS2             | ECCPAS1                 | ECCPAS0    | PSSAC1       | PSSAC0         | PSSBD1                      | PSSBD0    | 0000 0000            | 48, 150             |

| CVRCON                 | CVREN                                    | CVROE               | CVRR                    | —          | CVR3         | CVR2           | CVR1                        | CVR0      | 000- 0000            | 48, 227             |

| CMCON                  | C2OUT                                    | C1OUT               | C2INV                   | C1INV      | CIS          | CM2            | CM1                         | CM0       | 0000 0111            | 48, 221             |

| TMR3H                  | Timer3 Regis                             | ster High Byte      |                         |            |              |                |                             |           | XXXX XXXX            | 48, 131             |

| TMR3L                  | Timer3 Register Low Byte                 |                     |                         |            |              |                |                             | XXXX XXXX | 48, 131              |                     |

| T3CON                  | RD16                                     | T3CCP2              | T3CKPS1                 | T3CKPS0    | T3CCP1       | T3SYNC         | TMR3CS                      | TMR3ON    | 0000 0000            | 48, 129             |

| SPBRG                  | USART Bau                                | d Rate Genera       | ator                    |            |              |                |                             |           | 0000 0000            | 48, 198             |

| RCREG                  | USART Rece                               | eive Register       |                         |            |              |                |                             |           | 0000 0000            | 48, 204,<br>203     |

| TXREG                  | USART Tran                               | smit Register       |                         |            |              |                |                             |           | 0000 0000            | 48, 202,<br>203     |

| TXSTA                  | CSRC                                     | TX9                 | TXEN                    | SYNC       | _            | BRGH           | TRMT                        | TX9D      | 0000 -010            | 48, 196             |

| RCSTA                  | SPEN                                     | RX9                 | SREN                    | CREN       | ADDEN        | FERR           | OERR                        | RX9D      | 0000 000x            | 48, 197             |

#### TABLE 5-2:REGISTER FILE SUMMARY (PIC18F2220/2320/4220/4320) (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO, ECIO and INTIO2 (with port function on RA6) Oscillator mode only and read as '0' in all other oscillator modes.

2: RA7 and associated bits are configured as port pins in INTIO2 Oscillator mode only and read as '0' in all other modes.

3: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

4: If PBADEN = 0, PORTB<4:0> are configured as digital inputs and read unknown and if PBADEN = 1, PORTB<4:0> are configured as analog inputs and read as '0' following a Reset.

5: These registers and/or bits are not implemented on the PIC18F2X20 devices and read as 0x00.

6: The RE3 port bit is available as an input only pin only in 40-pin devices when Master Clear functionality is disabled (CONFIG3H<7>= 0).

### 9.1 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits.

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 9-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|----------|-----------|--------|--------|-------|--------|--------|---------------------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF <sup>(1)</sup> |

| bit 7    |           |        |        |       |        |        | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | GIE/GIEH: Global Interrupt Enable bit<br><u>When IPEN = 0:</u><br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts<br><u>When IPEN = 1:</u><br>1 = Enables all high-priority interrupts<br>0 = Disables all high-priority interrupts                                                                                                                             |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | PEIE/GIEL: Peripheral Interrupt Enable bit          When IPEN = 0:         1 = Enables all unmasked peripheral interrupts         0 = Disables all peripheral interrupts         When IPEN = 1:         1 = Enables all low-priority peripheral interrupts         0 = Disables all low-priority peripheral interrupts         0 = Disables all low-priority peripheral interrupts |

| bit 5 | TMR0IE: TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 overflow interrupt<br>0 = Disables the TMR0 overflow interrupt                                                                                                                                                                                                                                                  |

| bit 4 | INTOIE: INTO External Interrupt Enable bit<br>1 = Enables the INTO external interrupt<br>0 = Disables the INTO external interrupt                                                                                                                                                                                                                                                  |

| bit 3 | <b>RBIE:</b> RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                                                                                                                                                                          |

| bit 2 | <b>TMR0IF:</b> TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                                                                                                                                                            |

| bit 1 | INTOIF: INTO External Interrupt Flag bit<br>1 = The INTO external interrupt occurred (must be cleared in software)<br>0 = The INTO external interrupt did not occur                                                                                                                                                                                                                |

| bit 0 | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup><br>1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)<br>0 = None of the RB7:RB4 pins have changed state                                                                                                                                                                               |

|       |                                                                                                                                                                                                                                                                                                                                                                                    |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.

| Name                        | Bit#  | Buffer Type           | Function                                                                                                                                                                                                      |

|-----------------------------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/AN5/RD                  | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input or read control input in Parallel Slave<br>Port mode.<br>For RD (PSP Control mode):<br>1 = PSP is Idle<br>0 = Read operation. Reads PORTD register (if chip selected).    |

| RE1/AN6/WR                  | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input or write control input in Parallel<br>Slave Port mode.<br>For WR (PSP Control mode):<br>1 = PSP is Idle<br>0 = Write operation. Writes PORTD register (if chip selected). |

| RE2/AN7/CS                  | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input or chip select control input in Parallel<br>Slave Port mode.<br>For CS (PSP Control mode):<br>1 = PSP is Idle<br>0 = External device is selected                          |

| MCLR/VPP/RE3 <sup>(2)</sup> | bit 3 | ST                    | Input only port pin or programming voltage input (if $\overline{\text{MCLR}}$ is disabled);<br>Master Clear input or programming voltage input (if $\overline{\text{MCLR}}$ is enabled).                      |

#### TABLE 10-9: PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

2: The RE3 port bit is available as an input-only pin only in 40-pin devices and when Master Clear functionality is disabled (CONFIG3H<7>=0).

| TABLE 10-10: | SUMMARY OF REGISTERS | ASSOCIATED WITH PORTE |

|--------------|----------------------|-----------------------|

|              |                      |                       |

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3              | Bit 2     | Bit 1        | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|---------|--------------------|-----------|--------------|--------|----------------------|---------------------------------|

| PORTE  | —     | _     |       | _       | RE3 <sup>(1)</sup> | RE2       | RE1          | RE0    | qxxx                 | quuu                            |

| LATE   |       | —     | —     | _       | _                  | LATE Data | a Latch Reg  | ister  | xxx                  | uuu                             |

| TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _                  | PORTE Da  | ata Directio | n bits | 0000 -111            | 0000 -111                       |

| ADCON1 | _     |       | VCFG1 | VCFG0   | PCFG3              | PCFG2     | PCFG1        | PCFG0  | 00 0000              | 00 0000                         |

$\label{eq:lagend: Legend: x = unknown, u = unchanged, - = unimplemented, read as `0', q = value depends on condition. Shaded cells are not used by PORTE.$

Note 1: The RE3 port bit is available as an input-only pin only in 40-pin devices and when Master Clear functionality is disabled (CONFIG3H<7>=0).

### 11.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing the T0CS bit. In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit. In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI/C1OUT. The incrementing edge is determined by the Timer0 Source Edge Select bit (T0SE). Clearing the T0SE bit selects the rising edge.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 11.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not readable or writable.

The PSA and T0PS2:T0PS0 bits determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, x....etc.) will clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 11.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution).

### 11.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or FFFFh to 000h in 16-bit mode. This overflow sets the TMR0IF bit. The interrupt can be masked by clearing the TMR0IE bit. The TMR0IF bit must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep mode, since the timer requires clock cycles, even when T0CS is set.

# 11.4 16-Bit Mode Timer Reads and Writes

TMR0H is not the high byte of the timer/counter in 16-bit mode but is actually a buffered version of the high byte of Timer0 (refer to Figure 11-2). The high byte of the Timer0 counter/timer is not directly readable nor writable. TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0, without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

A write to the high byte of Timer0 must also take place through the TMR0H Buffer register. Timer0 high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

TABLE 11-1: REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7                     | Bit 6              | Bit 5   | Bit 4                         | Bit 3 | Bit 2  | Bit 1         | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------------------------|--------------------|---------|-------------------------------|-------|--------|---------------|-----------|----------------------|---------------------------------|

| TMR0L  | Timer0 Low Byte Register  |                    |         |                               |       |        |               | XXXX XXXX | uuuu uuuu            |                                 |

| TMR0H  | Timer0 High Byte Register |                    |         |                               |       |        |               | 0000 0000 | 0000 0000            |                                 |

| INTCON | GIE/GIEH                  | PEIE/GIEL          | TMR0IE  | INT0IE                        | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF      | x000 000x            | 0000 000u                       |

| T0CON  | TMR0ON                    | T08BIT             | TOCS    | T0SE                          | PSA   | T0PS2  | T0PS1         | T0PS0     | 1111 1111            | 1111 1111                       |

| TRISA  | RA7 <sup>(1)</sup>        | RA6 <sup>(1)</sup> | PORTA D | PORTA Data Direction Register |       |        |               |           | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

Note 1: RA6 and RA7 are enabled as I/O pins depending on the oscillator mode selected in Configuration Word 1H.

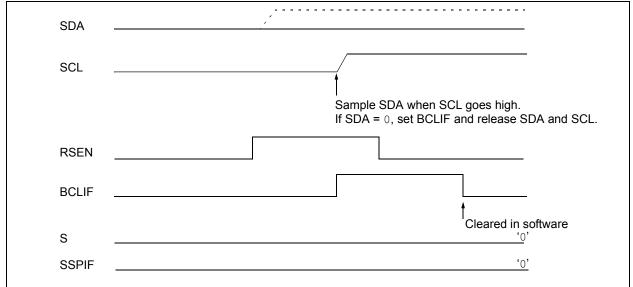

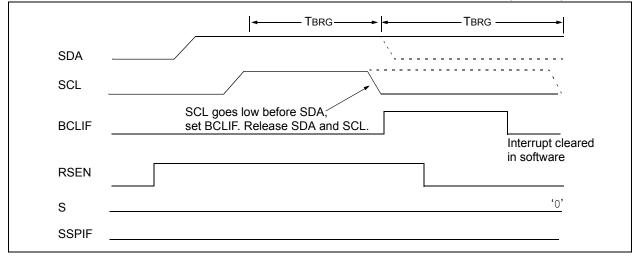

## 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 17-30).

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 17-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 17-30: BUS COLLISION DURING A REPEATED START CONDITION (CASE 2)

NOTES:

| R/P-1        | R/P-1                                                                           | U-0                                                                                                                      | U-0                                                                                                   | R/P-1                                                                   | R/P-1             | R/P-1      | R/P-1 |

|--------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|------------|-------|

| IESO         | FSCM                                                                            | —                                                                                                                        | _                                                                                                     | FOSC3                                                                   | FOSC2             | FOSC1      | FOSC0 |

| bit 7        | ·                                                                               |                                                                                                                          |                                                                                                       |                                                                         |                   |            | bit 0 |

| Legend:      |                                                                                 |                                                                                                                          |                                                                                                       |                                                                         |                   |            |       |

| R = Readab   | ole bit                                                                         | P = Program                                                                                                              | nable bit                                                                                             | U = Unimpler                                                            | mented bit, read  | l as '0'   |       |

| -n = Value v | vhen device is unp                                                              | orogrammed                                                                                                               |                                                                                                       | u = Unchang                                                             | ed from prograr   | nmed state |       |

| bit 7        | IESO: Intorna                                                                   | I/External Swit                                                                                                          | chovor hit                                                                                            |                                                                         |                   |            |       |

|              | 1 = Internal/E                                                                  | xternal Switch                                                                                                           | over mode er                                                                                          |                                                                         |                   |            |       |

| bit 6        | FCMEN: Fail-                                                                    | Safe Clock Mo                                                                                                            | nitor Enable                                                                                          | bit                                                                     |                   |            |       |

|              |                                                                                 | Clock Monitor<br>Clock Monitor                                                                                           |                                                                                                       |                                                                         |                   |            |       |

| bit 5-4      | Unimplemen                                                                      | ted: Read as '                                                                                                           | 0'                                                                                                    |                                                                         |                   |            |       |

| bit 3-0      | FOSC3:FOSC                                                                      | <b>:</b> Oscillator S                                                                                                    | Selection bits                                                                                        | (1)                                                                     |                   |            |       |

|              | 1001 = Intern<br>1000 = Intern<br>0111 = Extern<br>0110 = HS os<br>0101 = EC os | al oscillator blo<br>nal RC oscillato<br>cillator, PLL en<br>cillator, port fu<br>cillator, CLKO<br>cillator<br>cillator | ock, CLKO fu<br>ock, port functor, port function<br>or, port function<br>abled (clock<br>nction on RA | nction on RA6 a<br>tion on RA6 and<br>on on RA6<br>frequency = 4 a<br>6 | d port function o |            |       |

| Byte-oriented file register operations                                                                                                                                                                                                                                                         | Example Instruction       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| <u>15 10 9 8 7 0</u>                                                                                                                                                                                                                                                                           |                           |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                                                          | ADDWF MYREG, W, B         |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                          |                           |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                                                          |                           |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                                                              |                           |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                                                                       | MOVFF MYREG1, MYREG2      |

| 15 12 11 0                                                                                                                                                                                                                                                                                     |                           |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                                                                    |                           |

| f = 12-bit file register address                                                                                                                                                                                                                                                               |                           |

| Bit-oriented file register operations                                                                                                                                                                                                                                                          |                           |

| 15 12 11 9 8 7 0                                                                                                                                                                                                                                                                               |                           |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                                                                  | BSF MYREG, bit, B         |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                                                          |                           |

| Literal operations                                                                                                                                                                                                                                                                             |                           |

|                                                                                                                                                                                                                                                                                                | NOVIE 0 75                |

| OPCODE     k (literal)       k = 8-bit immediate value                                                                                                                                                                                                                                         | MOVLW 0x7F                |

|                                                                                                                                                                                                                                                                                                |                           |

| Control operations                                                                                                                                                                                                                                                                             |                           |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                                                               |                           |

| 15 8 7 0                                                                                                                                                                                                                                                                                       |                           |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                                                                        | GOTO Label                |

|                                                                                                                                                                                                                                                                                                |                           |

| 15 12 11 0                                                                                                                                                                                                                                                                                     |                           |

| 15         12         11         0           1111         n<19:8> (literal)         1                                                                                                                                                                                                          |                           |

|                                                                                                                                                                                                                                                                                                |                           |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                                                         |                           |

| n = 20-bit immediate value                                                                                                                                                                                                                                                                     | CALL MYFUNC               |

| 1111     n<19:8> (literal)       n = 20-bit immediate value       15     8     7     0                                                                                                                                                                                                         | CALL MYFUNC               |

| 1111       n<19:8> (literal)         n = 20-bit immediate value         15       8       7       0         OPCODE       S       n<7:0> (literal)       15         15       12       11       0                                                                                                 | CALL MYFUNC               |

| 1111     n<19:8> (literal)       n = 20-bit immediate value       15     8     7     0       OPCODE     S     n<7:0> (literal)                                                                                                                                                                 | CALL MYFUNC               |

| 1111       n<19:8> (literal)         n = 20-bit immediate value         15       8       7       0         OPCODE       S       n<7:0> (literal)       15         15       12       11       0         n       n<19:8> (literal)       15                                                      | CALL MYFUNC               |

| 1111       n<19:8> (literal)         n = 20-bit immediate value         15       8       7       0         OPCODE       S       n<7:0> (literal)       1         15       12       11       0         15       12       11       0         S = Fast bit       S       15       11       10     | CALL MYFUNC<br>BRA MYFUNC |

| 1111       n<19:8> (literal)         n = 20-bit immediate value         15       8       7       0         OPCODE       S       n<7:0> (literal)       15         15       12       11       0         15       12       11       0         S = Fast bit       S = Fast bit       S = Fast bit |                           |

| 1111       n<19:8> (literal)         n = 20-bit immediate value         15       8       7       0         OPCODE       S       n<7:0> (literal)       1         15       12       11       0         15       12       11       0         S = Fast bit       S       15       11       10     |                           |

| ADD         | WFC                                                                   | ADD W ar                                                                                  | ADD W and Carry bit to f                                                |                                                                      |                                            |  |  |  |

|-------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------|--|--|--|

| Synt        | ax:                                                                   | [ <i>label</i> ] A[                                                                       | [ <i>label</i> ] ADDWFC f [,d [,a]]                                     |                                                                      |                                            |  |  |  |

| Operands:   |                                                                       | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                     |                                                                         |                                                                      |                                            |  |  |  |

| Ope         | ration:                                                               | (W) + (f) +                                                                               | $(C) \rightarrow de$                                                    | est                                                                  |                                            |  |  |  |

| •           | us Affected:                                                          | N, OV, C,                                                                                 |                                                                         |                                                                      |                                            |  |  |  |

| Enco        | oding:                                                                | 0010                                                                                      | 00da                                                                    | ffff                                                                 | ffff                                       |  |  |  |

| Deso        | cription:                                                             | Add W, the<br>memory lo<br>result is pl<br>tion 'f'. If 'a<br>will be sele<br>will not be | ocation 'f'.<br>aced in V<br>aced in d<br>a' is '0', th<br>ected. If 'a | . If 'd' is '<br>V. If 'd' is<br>ata mem<br>ne Acces<br>a' is '1', t | 0', the<br>'1', the<br>ory loca-<br>s Bank |  |  |  |

| Wor         | ds:                                                                   | 1                                                                                         |                                                                         |                                                                      |                                            |  |  |  |

| Cycl        | es:                                                                   | 1                                                                                         |                                                                         |                                                                      |                                            |  |  |  |

| QC          | ycle Activity:                                                        |                                                                                           |                                                                         |                                                                      |                                            |  |  |  |

|             | Q1                                                                    | Q2                                                                                        | Q3                                                                      |                                                                      | Q4                                         |  |  |  |

|             | Decode                                                                | Read<br>register 'f'                                                                      | Process<br>Data                                                         |                                                                      | ite to<br>ination                          |  |  |  |

| <u>Exar</u> | <u>mple</u> :                                                         | ADDWFC                                                                                    | REG, W                                                                  | V                                                                    |                                            |  |  |  |

|             | Before Instru<br>Carry bit<br>REG<br>W<br>After Instruct<br>Carry bit | = 1<br>= 0x02<br>= 0x4D                                                                   |                                                                         |                                                                      |                                            |  |  |  |

|             | REG                                                                   | = 0x02                                                                                    |                                                                         |                                                                      |                                            |  |  |  |

| ANDLW        |             | AND Lite                              | ral with                    | W    |            |  |  |

|--------------|-------------|---------------------------------------|-----------------------------|------|------------|--|--|

| Syntax:      |             | [label] A                             | NDLW                        | k    |            |  |  |

| Operands:    |             | $0 \le k \le 25$                      | $0 \le k \le 255$           |      |            |  |  |

| Operation:   |             | (W) .AND                              | (W) .AND. $k \rightarrow W$ |      |            |  |  |

| Status A     | ffected:    | N, Z                                  |                             |      |            |  |  |

| Encodin      | g:          | 0000                                  | 1011                        | kkkk | kkkk       |  |  |

| Description: |             | The conte<br>the 8-bit I<br>placed in | iteral 'k'.                 |      |            |  |  |

| Words:       |             | •                                     | 1                           |      |            |  |  |

| Cycles:      |             | 1                                     |                             |      |            |  |  |

| Q Cycle      | e Activity: |                                       |                             |      |            |  |  |

|              | Q1          | Q2                                    | Q3                          | 3    | Q4         |  |  |

| D            | ecode       | Read literal<br>'k'                   | Proce<br>Data               |      | /rite to W |  |  |

| Example      | 2.          | ANDI.W                                | 0x5F                        |      |            |  |  |

Example: ANDLW 0x5F

| Before instruction |   |      |  |  |  |  |

|--------------------|---|------|--|--|--|--|

| W                  | = | 0xA3 |  |  |  |  |

| After Instruction  |   |      |  |  |  |  |

| W                  | = | 0x03 |  |  |  |  |

W

=

0x50

| GOT    | ю                                       | Uncondit                    | ional B                                  | ranch                     |                                                 |  |  |  |

|--------|-----------------------------------------|-----------------------------|------------------------------------------|---------------------------|-------------------------------------------------|--|--|--|

| Synt   | ax:                                     | [ label ]                   | GOTO                                     | k                         |                                                 |  |  |  |

| Ope    | rands:                                  | $0 \le k \le 10$            | $0 \leq k \leq 1048575$                  |                           |                                                 |  |  |  |

| Ope    | ration:                                 | $k \rightarrow PC < 20:1 >$ |                                          |                           |                                                 |  |  |  |

| Statu  | us Affected:                            | None                        |                                          |                           |                                                 |  |  |  |

| 1st v  | oding:<br>vord (k<7:0>)<br>word(k<19:8> |                             | 1111<br>k <sub>19</sub> kkk              | k <sub>7</sub> kk<br>kkk  | 0                                               |  |  |  |

| Desi   | cription:                               |                             | nywhere<br>nemory<br>s loaded<br>lways a | within<br>range<br>into F | n entire<br>. The 20-bit<br>PC<20:1>.           |  |  |  |

| Words: |                                         |                             |                                          |                           |                                                 |  |  |  |

| **01   | ds:                                     | 2                           |                                          |                           |                                                 |  |  |  |

| Cycl   |                                         | 2<br>2                      |                                          |                           |                                                 |  |  |  |

| Cycl   |                                         | -                           |                                          |                           |                                                 |  |  |  |

| Cycl   | es:                                     | -                           | Q                                        | 3                         | Q4                                              |  |  |  |

| Cycl   | es:<br>Sycle Activity:                  | 2                           | Q3<br>No<br>operat                       | ion                       | Q4<br>Read literal<br>'k'<19:8>,<br>Write to PC |  |  |  |

Example: GOTO THERE

After Instruction

operation

PC = Address (THERE)

operation

operation

operation

| INCF              | Incremen                                                                                                        | t f                                                                      |                                                                           |                                                    |

|-------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------|

| Syntax:           | [label]                                                                                                         | INCF                                                                     | f [,d [,a]]                                                               |                                                    |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                             | 5                                                                        |                                                                           |                                                    |

| Operation:        | (f) + 1 $\rightarrow$ 0                                                                                         | dest                                                                     |                                                                           |                                                    |

| Status Affected:  | C, DC, N,                                                                                                       | OV, Z                                                                    |                                                                           |                                                    |

| Encoding:         | 0010                                                                                                            | 10da                                                                     | ffff                                                                      | ffff                                               |

|                   | increment<br>is placed i<br>is placed b<br>(default). I<br>Bank will b<br>the BSR v<br>bank will b<br>BSR value | n W. If '<br>back in r<br>f 'a' is '<br>be selec<br>alue. If<br>be selec | d' is '1',<br>register<br>0', the A<br>ted, ove<br>'a' = 1, t<br>ted as p | the result<br>'f'<br>ccess<br>erriding<br>then the |

| Words:            | 1                                                                                                               |                                                                          |                                                                           |                                                    |

| Cycles:           | 1                                                                                                               |                                                                          |                                                                           |                                                    |

| Q Cycle Activity: |                                                                                                                 |                                                                          |                                                                           |                                                    |

| · · · ·           | Q2                                                                                                              | Q3                                                                       |                                                                           | -                                                  |

| Q1                | QZ                                                                                                              |                                                                          | ,                                                                         | Q4                                                 |

|                   | Read<br>register 'f'                                                                                            | Proce                                                                    | SS                                                                        | Q4<br>Write to<br>estination                       |