Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4220-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

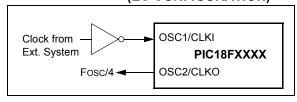

# 2.4 External Clock Input

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-4 shows the pin connections for the EC Oscillator mode.

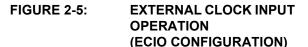

#### FIGURE 2-4: EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-5 shows the pin connections for the ECIO Oscillator mode.

## 2.5 RC Oscillator

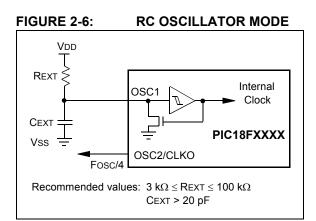

For timing insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal manufacturing variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 2-6 shows how the R/C combination is connected.

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic.

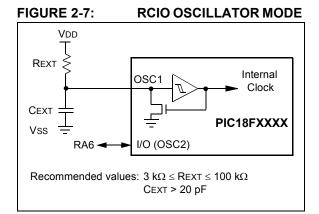

The RCIO Oscillator mode (Figure 2-7) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

| Power -Managed<br>Mode | CPU is Clocked by               | WDT<br>Time-out<br>Causes a | Peripherals are<br>Clocked by               | Clock During Wake-up<br>(while primary becomes<br>ready)                                         |

|------------------------|---------------------------------|-----------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------|

| Sleep                  | Not clocked (not running)       | Wake-up                     | Not clocked                                 | None or INTOSC multiplexer if<br>Two-Speed Start-up or<br>Fail-Safe Clock Monitor is<br>enabled. |

| Any Idle mode          | Not clocked (not running)       | Wake-up                     | Primary, Secondary or<br>INTOSC multiplexer | Unchanged from Idle mode<br>(CPU operates as in<br>corresponding Run mode).                      |

| Any Run mode           | Secondary or INTOSC multiplexer | Reset                       | Secondary or<br>INTOSC multiplexer          | Unchanged from Run mode.                                                                         |

TABLE 3-2: COMPARISON BETWEEN POWER-MANAGED MODES

# 3.2 Sleep Mode

The power-managed Sleep mode in the PIC18F2X20/ 4X20 devices is identical to that offered in all other PIC microcontrollers. It is entered by clearing the IDLEN and SCS1:SCS0 bits (this is the Reset state) and executing the SLEEP instruction. This shuts down the primary oscillator and the OSTS bit is cleared (see Figure 3-1).

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the system will not be clocked until the primary clock source becomes ready (see Figure 3-2), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see Section 23.0 "Special Features of the CPU"). In either case, the OSTS bit is set when the primary clock is providing the system clocks. The IDLEN and SCS bits are not affected by the wake-up.

# 3.3 Idle Modes

The IDLEN bit allows the controller's CPU to be selectively shut down while the peripherals continue to operate. Clearing IDLEN allows the CPU to be clocked. Setting IDLEN disables clocks to the CPU, effectively stopping program execution (see Register 2-3). The peripherals continue to be clocked regardless of the setting of the IDLEN bit. There is one exception to how the IDLEN bit functions. When all the low-power OSCCON bits are cleared (IDLEN:SCS1:SCS0 = 000), the device enters Sleep mode upon the execution of the SLEEP instruction. This is both the Reset state of the OSCCON register and the setting that selects Sleep mode. This maintains compatibility with other PIC devices that do not offer power-managed modes.

If the Idle Enable bit, IDLEN (OSCCON<7>), is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS1:SCS0 bits; however, the CPU will not be clocked. Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset.

When a wake-up event occurs, CPU execution is delayed approximately 10  $\mu$ s while it becomes ready to execute code. When the CPU begins executing code, it is clocked by the same clock source as was selected in the power-managed mode (i.e., when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals until the primary clock source becomes ready – this is essentially RC\_RUN mode). This continues until the primary clock source becomes ready. When the primary clock becomes ready, the OSTS bit is set and the system clock source is switched to the primary clock (see Figure 3-4). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or Sleep mode, a WDT time-out will result in a WDT wake-up to full-power operation.

## 4.1 Power-on Reset (POR)

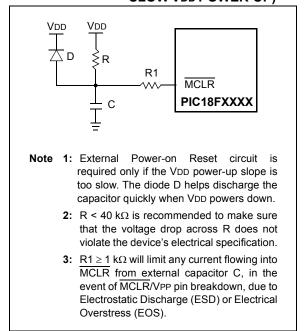

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, just tie the MCLR pin through a resistor (1k to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

FIGURE 4-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

# 4.2 Power-up Timer (PWRT)

The Power-up Timer (PWRT) of the PIC18F2X20/4X20 devices is an 11-bit counter, which uses the INTRC source as the clock input. This yields a count of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter #33 for details.

The PWRT is enabled by clearing Configuration bit, PWRTEN.

# 4.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most power-managed modes.

## 4.4 PLL Lock Time-out

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

### 4.5 Brown-out Reset (BOR)

A Configuration bit, BOREN, can disable (if clear/ programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below VBOR (parameter D005) for greater than TBOR (parameter #35), the brown-out situation will reset the chip. A Reset may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR. If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay TPWRT (parameter #33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay. Enabling BOR Reset does not automatically enable the PWRT.

# 4.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, after the POR pulse has cleared, PWRT time-out is invoked (if enabled). Then, the OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

Table 4-2 shows the Reset conditions for some Special Function Registers, while Table 4-3 shows the Reset conditions for all the registers.

# 8.0 8 X 8 HARDWARE MULTIPLIER

## 8.1 Introduction

An 8 x 8 hardware multiplier is included in the ALU of the PIC18F2X20/4X20 devices. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored into the 16-bit product register pair (PRODH:PRODL). The multiplier does not affect any flags in the STATUS register.

Making the 8 x 8 multiplier execute in a single-cycle gives the following advantages:

- Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in applications previously reserved for Digital Signal Processors.

Table 8-1 shows a performance comparison between enhanced devices using the single-cycle hardware multiply and performing the same function without the hardware multiply.

# 8.2 Operation

Example 8-1 shows the sequence to do an 8 x 8 unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiply. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF<br>MULWF | ARG1,<br>ARG2 | W | ;<br>; ARG1 * ARG2 -> |

|---------------|---------------|---|-----------------------|

|               |               |   | ; PRODH:PRODL         |

#### EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W  |                  |

|-------|----------|------------------|

| MULWF | ARG2     | ; ARG1 * ARG2 -> |

|       |          | ; PRODH:PRODL    |

| BTFSC | ARG2, SB | ; Test Sign Bit  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |

|       |          | ; – ARG1         |

| MOVF  | ARG2, W  |                  |

| BTFSC | ARG1, SB | ; Test Sign Bit  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |

|       |          | ; – ARG2         |

|       |          |                  |

|                  |                           | Program           | Cycles | Time     |          |         |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

| 9 x 9 uppigpod   | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |

| 9 x 9 signed     | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16 x 16 unsigned | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| To x To unsigned | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs   |  |

# TABLE 8-1: PERFORMANCE COMPARISON

| R/W-0         | R/W-0                       | U-0                                                          | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

|---------------|-----------------------------|--------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|--|--|

| OSCFIE        | CMIE                        | —                                                            | EEIE          | BCLIE            | LVDIE            | TMR3IE          | CCP2IE |  |  |

| bit 7         |                             |                                                              |               |                  |                  |                 | bit 0  |  |  |

|               |                             |                                                              |               |                  |                  |                 |        |  |  |

| Legend:       |                             |                                                              |               |                  |                  |                 |        |  |  |

| R = Readable  | e bit                       | W = Writable I                                               | oit           | U = Unimple      | mented bit, read | d as '0'        |        |  |  |

| -n = Value at | POR                         | '1' = Bit is set                                             |               | '0' = Bit is cle | eared            | x = Bit is unkr | nown   |  |  |

|               |                             |                                                              |               |                  |                  |                 |        |  |  |

| bit 7         | OSCFIE: Osc                 | cillator Fail Inter                                          | rupt Enable I | oit              |                  |                 |        |  |  |

|               | 1 = Enabled                 |                                                              |               |                  |                  |                 |        |  |  |

| bit 6         | 0 = Disabled                |                                                              | Enchla hit    |                  |                  |                 |        |  |  |

| DILO          | 1 = Enabled                 | arator Interrupt                                             |               |                  |                  |                 |        |  |  |

|               | 0 = Disabled                |                                                              |               |                  |                  |                 |        |  |  |

| bit 5         | Unimplemen                  | ted: Read as 'd                                              | )'            |                  |                  |                 |        |  |  |

| bit 4         | EEIE: Data E                | EEIE: Data EEPROM/Flash Write Operation Interrupt Enable bit |               |                  |                  |                 |        |  |  |

|               | 1 = Enabled                 |                                                              |               |                  |                  |                 |        |  |  |

|               | 0 = Disabled                |                                                              |               |                  |                  |                 |        |  |  |

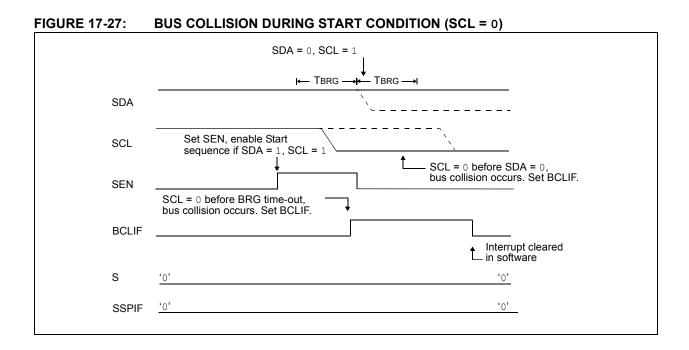

| bit 3         | 1 = Enabled                 | BCLIE: Bus Collision Interrupt Enable bit                    |               |                  |                  |                 |        |  |  |

|               | 0 = Disabled                |                                                              |               |                  |                  |                 |        |  |  |

| bit 2         | LVDIE: Low-                 | Voltage Detect I                                             | nterrupt Ena  | ble bit          |                  |                 |        |  |  |

|               | 1 = Enabled                 | 0                                                            | ·             |                  |                  |                 |        |  |  |

|               | 0 = Disabled                |                                                              |               |                  |                  |                 |        |  |  |

| bit 1         |                             | R3 Overflow Int                                              | errupt Enable | e bit            |                  |                 |        |  |  |

|               | 1 = Enabled<br>0 = Disabled |                                                              |               |                  |                  |                 |        |  |  |

| bit 0         |                             | P2 Interrupt Ena                                             | hla hit       |                  |                  |                 |        |  |  |

|               | 1 = Enabled                 |                                                              |               |                  |                  |                 |        |  |  |

|               | 0 = Disabled                |                                                              |               |                  |                  |                 |        |  |  |

|               |                             |                                                              |               |                  |                  |                 |        |  |  |

#### REGISTER 9-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

## 9.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising if the corresponding INTEDGx bit is set in the INTCON2 register, or falling if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from the power-managed modes if bit INTxIE was set prior to going into power-managed modes. If the global interrupt enable bit GIE is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the Interrupt Priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high-priority interrupt source.

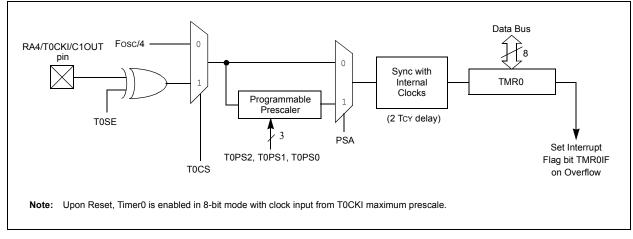

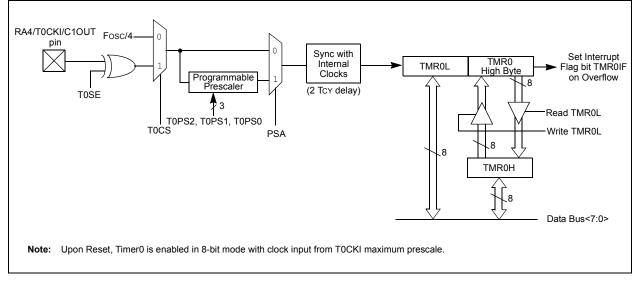

### 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF. In 16-bit mode, an overflow (FFFFh  $\rightarrow$  0000h) in the TMR0H:TMR0L registers will set flag bit TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See **Section 11.0 "Timer0 Module"** for further details on the Timer0 module.

#### 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

# 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (See **Section 5.3 "Fast Register Stack"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

#### EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

MOVWF W TEMP ; W TEMP is in virtual bank MOVFF STATUS, STATUS TEMP ; STATUS TEMP located anywhere MOVFF BSR, BSR TEMP ; BSR TMEP located anywhere ; ; USER ISR CODE • MOVFF BSR TEMP, BSR ; Restore BSR MOVF W TEMP, W ; Restore WREG STATUS\_TEMP, STATUS MOVFF ; Restore STATUS

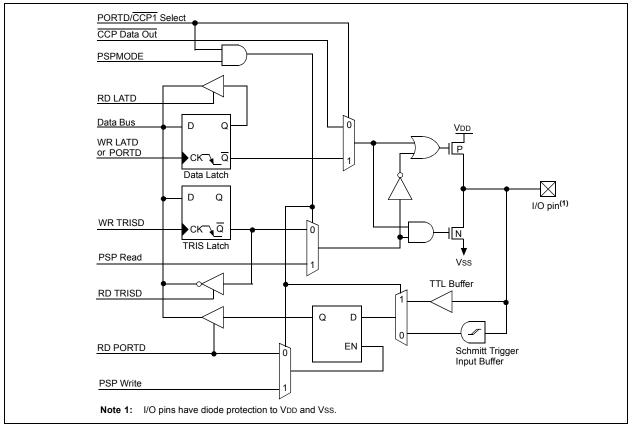

#### 10.4 PORTD, TRISD and LATD Registers

| Note: | PORTD is only available on PIC18F4X20 |

|-------|---------------------------------------|

|       | devices.                              |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Three of the PORTD pins are multiplexed with outputs P1B, P1C and P1D of the Enhanced CCP module. The operation of these additional PWM output pins is covered in greater detail in Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

Note: On a Power-on Reset, these pins are configured as digital inputs.

PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 10.6 "Parallel Slave Port"** for additional information on the Parallel Slave Port (PSP).

| Note: | When the enhanced PWM mode is used        |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | with either dual or quad outputs, the PSP |  |  |  |  |  |

|       | functions of PORTD are automatically      |  |  |  |  |  |

|       | disabled.                                 |  |  |  |  |  |

#### EXAMPLE 10-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATD  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISD | : Set RD<3:0> as inputs |

|       |       | ; RD<5:4> as outputs    |

|       |       | ; RD<7:6> as inputs     |

|       |       | , 100 as inpaces        |

# FIGURE 10-11: BLOCK DIAGRAM OF RD7:RD5 PINS

# FIGURE 11-1: TIMER0 BLOCK DIAGRAM IN 8-BIT MODE

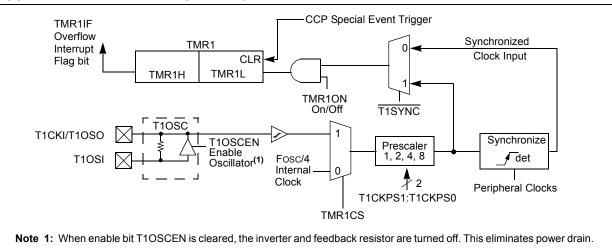

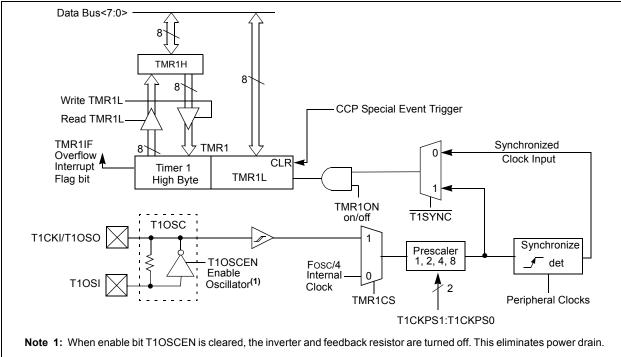

# 12.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- · As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the Clock Select bit, TMR1CS (T1CON<1>).

When TMR1CS = 0, Timer1 increments every instruction cycle. When TMR1CS = 1, Timer1 increments on every rising edge of the external clock input, or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. The TRISC1:TRISC0 values are ignored and the pins read as '0'.

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (see **Section 15.4.4 "Special Event Trigger"**).

# FIGURE 12-1: TIMER1 BLOCK DIAGRAM

NOTES:

| R/W-0         | R/W-0                                                                                                                                                                                    | R/W-0                                     | R/W-0                     | R/W-0                | R/W-0                        | R/W-0                | R/W-0                |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|----------------------|------------------------------|----------------------|----------------------|--|--|--|

| WCOL          | SSPOV                                                                                                                                                                                    | SSPEN <sup>(1)</sup>                      | CKP                       | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup>         | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |  |  |  |

| bit 7         |                                                                                                                                                                                          |                                           |                           |                      |                              |                      | bit                  |  |  |  |

|               |                                                                                                                                                                                          |                                           |                           |                      |                              |                      |                      |  |  |  |

| Legend:       |                                                                                                                                                                                          |                                           |                           |                      |                              |                      |                      |  |  |  |

| R = Readabl   | e bit                                                                                                                                                                                    | W = Writable                              | bit                       | U = Unimpler         | mented bit, read             | d as '0'             |                      |  |  |  |

| -n = Value at | POR                                                                                                                                                                                      | '1' = Bit is set                          |                           | '0' = Bit is cle     | ared                         | x = Bit is unki      | nown                 |  |  |  |

| bit 7         |                                                                                                                                                                                          | te Collision Dete                         | at bit                    |                      |                              |                      |                      |  |  |  |

|               |                                                                                                                                                                                          | ransmit mode:                             |                           |                      |                              |                      |                      |  |  |  |

|               |                                                                                                                                                                                          | to the SSPBUF                             | register wa               | s attempted w        | hile the I <sup>2</sup> C co | nditions were i      | not valid for        |  |  |  |

|               |                                                                                                                                                                                          | ssion to be starte                        |                           |                      |                              |                      |                      |  |  |  |

|               | 0 = No colli                                                                                                                                                                             |                                           | ·                         |                      |                              |                      |                      |  |  |  |

|               | In Slave Tra                                                                                                                                                                             | insmit mode:                              |                           |                      |                              |                      |                      |  |  |  |

|               |                                                                                                                                                                                          | PBUF register is                          | written while             | e it is still transr | nitting the previ            | ous word (mus        | t be cleared i       |  |  |  |

|               | softwar                                                                                                                                                                                  | /                                         |                           |                      |                              |                      |                      |  |  |  |

|               | 0 = No colli                                                                                                                                                                             |                                           | 0                         |                      |                              |                      |                      |  |  |  |

|               |                                                                                                                                                                                          | <u>mode (Master or</u><br>on't care" bit. | Slave modes               | <u>s):</u>           |                              |                      |                      |  |  |  |

| bit 6         | SSPOV: Receive Overflow Indicator bit                                                                                                                                                    |                                           |                           |                      |                              |                      |                      |  |  |  |

|               | In Receive mode:                                                                                                                                                                         |                                           |                           |                      |                              |                      |                      |  |  |  |

|               | 1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in                                                                                  |                                           |                           |                      |                              |                      |                      |  |  |  |

|               | softwar                                                                                                                                                                                  | /                                         |                           |                      |                              |                      |                      |  |  |  |

|               | 0 = No over                                                                                                                                                                              |                                           |                           |                      |                              |                      |                      |  |  |  |

|               | In Transmit                                                                                                                                                                              | <u>mode:</u><br>on't care" bit in Tr      | onomit mode               |                      |                              |                      |                      |  |  |  |

| bit 5         |                                                                                                                                                                                          |                                           |                           |                      |                              |                      |                      |  |  |  |

| bit 5         | <b>SSPEN:</b> Master Synchronous Serial Port Enable bit <sup>(1)</sup>                                                                                                                   |                                           |                           |                      |                              |                      |                      |  |  |  |

|               | <ul> <li>1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul> |                                           |                           |                      |                              |                      |                      |  |  |  |

| bit 4         |                                                                                                                                                                                          | Release Control                           | -                         |                      |                              |                      |                      |  |  |  |

|               | In Slave mo                                                                                                                                                                              | de:                                       |                           |                      |                              |                      |                      |  |  |  |

|               | 1 = Release                                                                                                                                                                              |                                           |                           |                      |                              |                      |                      |  |  |  |

|               | 0 = Holds cl                                                                                                                                                                             | lock low (clock st                        | retch), used              | to ensure data       | setup time                   |                      |                      |  |  |  |

|               | In Master m                                                                                                                                                                              |                                           |                           |                      |                              |                      |                      |  |  |  |

|               | Unused in th                                                                                                                                                                             |                                           |                           |                      | (2)                          |                      |                      |  |  |  |

| bit 3-0       | <b>SSPM3:SSPM0:</b> Master Synchronous Serial Port Mode Select bits <sup>(2)</sup><br>1111 = $I^2C$ Slave mode, 10-bit address with Start and Stop bit interrupts enabled                |                                           |                           |                      |                              |                      |                      |  |  |  |

|               |                                                                                                                                                                                          |                                           |                           |                      |                              |                      |                      |  |  |  |

|               |                                                                                                                                                                                          | Slave mode, 7-b<br>Firmware Contro        |                           |                      |                              | enabled              |                      |  |  |  |

|               |                                                                                                                                                                                          | Master mode, clo                          |                           |                      |                              |                      |                      |  |  |  |

|               | $0111 = I^2C$                                                                                                                                                                            | Slave mode, 10-                           | bit address <sup>(2</sup> | )                    | • //                         |                      |                      |  |  |  |

|               | $0110 = I^2C$                                                                                                                                                                            | Slave mode, 7-b                           | it address <sup>(2)</sup> |                      |                              |                      |                      |  |  |  |

| No.4. 14      | /hen en-1-1                                                                                                                                                                              |                                           | nine second b             |                      | income dia section of        | on outout            |                      |  |  |  |

| Note 1: W     | men enabled, ti                                                                                                                                                                          | he SDA and SCL                            | . pins must b             | e properly cont      | igureo as input              | or output.           |                      |  |  |  |

# REGISTER 17-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

- When enabled, the SDA and SCL pins must be properly configured as input or output.

- 2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

# 17.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Master mode, clock = Fosc/(4 \* (SSPADD + 1))

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 17.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The  $I^2C$  Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared by software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

#### 17.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

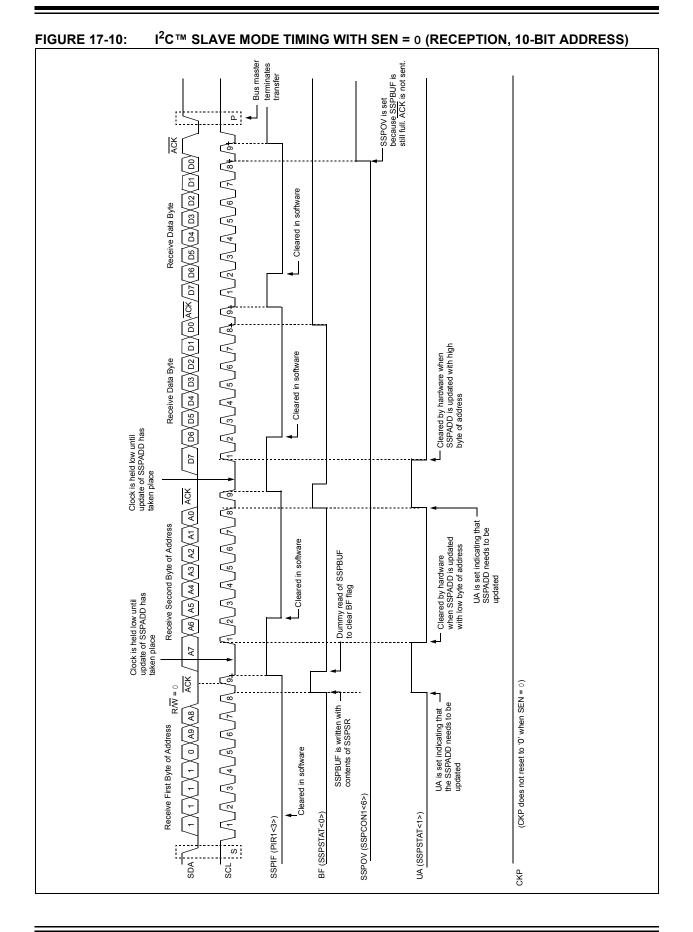

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit addressing is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of Address (clears bit, UA, and releases the SCL line).

- 3. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits, SSPIF, BF and UA, are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit, UA.

- 6. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits, SSPIF and BF, are set).

- 9. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

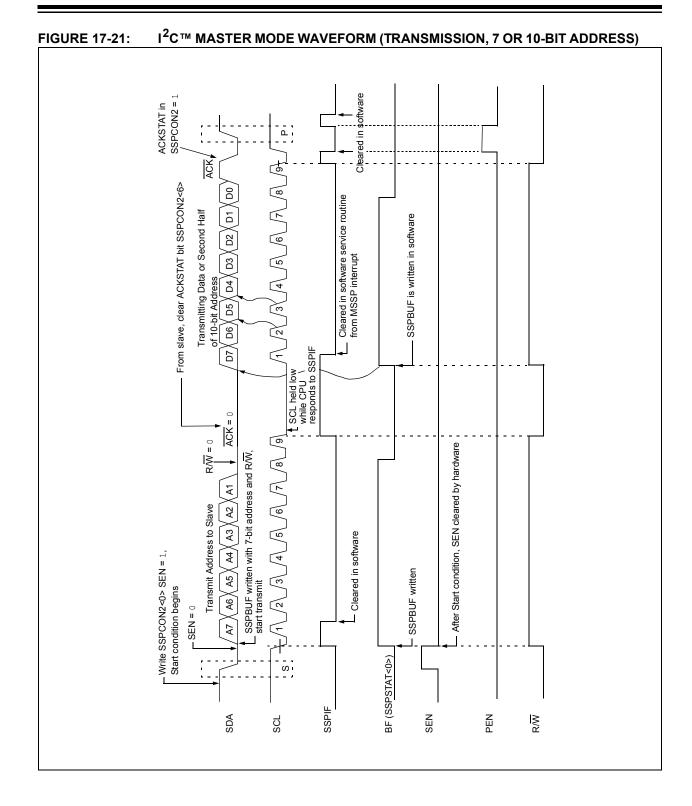

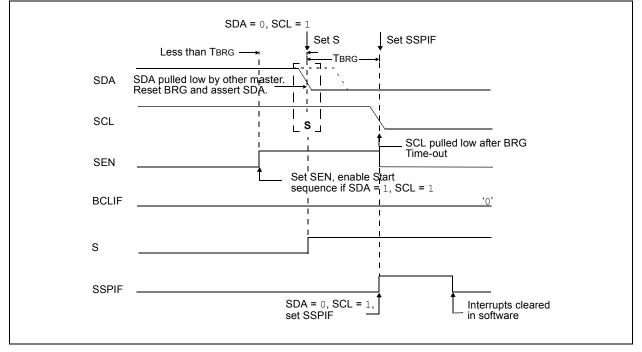

#### 17.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full Flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit, during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 17-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 17.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 17.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 17.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

## 17.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 17.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 17.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 17.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

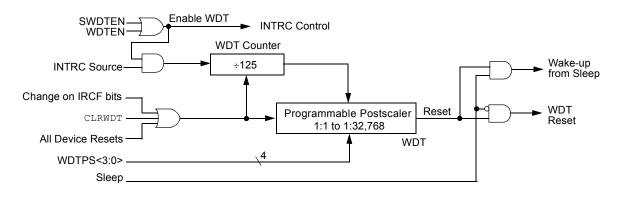

# 23.2 Watchdog Timer (WDT)

For PIC18F2X20/4X20 devices, the WDT is driven by the INTRC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: execute a SLEEP or CLRWDT instruction, the IRCF bits (OSCCON<6:4>) are changed or a clock failure has occurred.

Adjustments to the internal oscillator clock period using the OSCTUNE register also affect the period of the WDT by the same factor. For example, if the INTRC period is increased by 3%, then the WDT period is increased by 3%.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits (OSCCON<6:4> clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### 23.2.1 CONTROL REGISTER

Register 23-14 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable Configuration bit, but only if the Configuration bit has disabled the WDT.

## 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2220/2320/4220/4320 (Industrial) PIC18LF2220/2320/4220/4320 (Industrial) (Continued)

| PIC18LF2220/2320/4220/4320<br>(Industrial)<br>PIC18F2220/2320/4220/4320<br>(Industrial, Extended) |                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |    |        |                          |                                                                       |  |              |

|---------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------|-----|----|--------|--------------------------|-----------------------------------------------------------------------|--|--------------|

|                                                                                                   |                                       |                                                       |     |    |        |                          |                                                                       |  | Param<br>No. |

|                                                                                                   | Supply Current (IDD) <sup>(2,3)</sup> |                                                       |     |    |        |                          |                                                                       |  |              |

|                                                                                                   | PIC18LF2X20/4X20                      | 140                                                   | 275 | μA | -40°C  |                          |                                                                       |  |              |

|                                                                                                   |                                       | 140                                                   | 275 | μA | +25°C  | VDD = 2.0V               |                                                                       |  |              |

|                                                                                                   |                                       | 150                                                   | 275 | μA | +85°C  | 1                        |                                                                       |  |              |

|                                                                                                   | PIC18LF2X20/4X20                      | 220                                                   | 375 | μA | -40°C  |                          |                                                                       |  |              |

|                                                                                                   |                                       | 220                                                   | 375 | μA | +25°C  | VDD = 3.0V               | Fosc = 4 MHz<br>( <b>RC_IDLE</b> mode,<br>internal oscillator source) |  |              |

|                                                                                                   |                                       | 210                                                   | 375 | μA | +85°C  |                          |                                                                       |  |              |

|                                                                                                   | All devices                           | 390                                                   | 800 | μA | -40°C  |                          |                                                                       |  |              |

|                                                                                                   |                                       | 400                                                   | 800 | μA | +25°C  | VDD = 5.0V               |                                                                       |  |              |

|                                                                                                   |                                       | 380                                                   | 800 | μA | +85°C  | VDD - 5.0V               |                                                                       |  |              |

|                                                                                                   | Extended devices                      | 410                                                   | 800 | μA | +125°C |                          |                                                                       |  |              |

|                                                                                                   | PIC18LF2X20/4X20                      | 150                                                   | 250 | μA | -40°C  |                          |                                                                       |  |              |

|                                                                                                   |                                       | 150                                                   | 250 | μA | +25°C  | VDD = 2.0V               |                                                                       |  |              |

|                                                                                                   |                                       | 160                                                   | 250 | μA | +85°C  |                          |                                                                       |  |              |

|                                                                                                   | PIC18LF2X20/4X20                      | 340                                                   | 350 | μA | -40°C  |                          |                                                                       |  |              |

|                                                                                                   |                                       | 300                                                   | 350 | μA | +25°C  | VDD = 3.0V<br>VDD = 5.0V | Fosc = 1 MHz<br>( <b>PRI_RUN</b> ,                                    |  |              |

|                                                                                                   |                                       | 280                                                   | 350 | μA | +85°C  |                          | EC oscillator)                                                        |  |              |

|                                                                                                   | All devices                           | 0.72                                                  | 1.0 | mA | -40°C  |                          |                                                                       |  |              |

|                                                                                                   |                                       | 0.63                                                  | 1.0 | mA | +25°C  |                          |                                                                       |  |              |

|                                                                                                   |                                       | 0.57                                                  | 1.0 | mA | +85°C  |                          |                                                                       |  |              |

|                                                                                                   | Extended devices                      | 0.53                                                  | 1.0 | mA | +125°C |                          |                                                                       |  |              |

**Legend:** Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 4: Standard low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

#### С

| C Compilers                            |     |

|----------------------------------------|-----|

| MPLAB C18                              |     |

| MPLAB C30                              |     |

| CALL                                   |     |

| Capture (CCP Module)                   | 135 |

| Associated Registers                   |     |

| CCP Pin Configuration                  |     |

| CCPR1H:CCPR1L Registers                |     |

| Software Interrupt                     |     |

| Timer1/Timer3 Mode Selection           |     |

| Capture (ECCP Module)                  |     |

| Capture/Compare/PWM (CCP)              |     |

| Capture Mode. See Capture.             |     |

| CCP1                                   |     |

| CCPR1H Register                        |     |

| CCPR1L Register                        |     |

| CCP2                                   |     |

| CCPR2H Register                        |     |

| CCPR2L Register                        | 134 |

| Compare Mode. See Compare.             |     |

| Interaction of Two CCP Modules         | 134 |

| PWM Mode. See PWM.                     |     |

| Timer Resources                        |     |

| Clock Sources                          |     |

| Selection Using OSCCON Register        |     |

| Clocking Scheme/Instruction Cycle      |     |

| CLRF                                   |     |

| CLRWDT                                 |     |

| Code Examples                          |     |

| 16 x 16 Signed Multiply Routine        |     |

| 16 x 16 Unsigned Multiply Routine      |     |

| 8 x 8 Signed Multiply Routine          |     |

| 8 x 8 Unsigned Multiply Routine        |     |

| Changing Between Capture Prescalers    |     |

| Computed GOTO Using an Offset Value    |     |

| Data EEPROM Read                       |     |

| Data EEPROM Refresh Routine            |     |

| Data EEPROM Write                      |     |

| Erasing a Flash Program Memory Row     |     |

| Fast Register Stack                    |     |

| How to Clear RAM (Bank 1) Using        |     |

| Indirect Addressing                    |     |

| Implementing a Real-Time Clock Using a | 405 |

| Timer1 Interrupt Service               |     |

| Initializing PORTA                     |     |

| Initializing PORTB                     |     |

|                                        |     |

| Initializing PORTD                     |     |

|                                        |     |

| Loading the SSPBUF (SSPSR) Register    |     |

| Reading a Flash Program Memory Word    |     |

| Saving STATUS, WREG and BSR            | 00  |

| Registers in RAM                       |     |

| Writing to Flash Program Memory        |     |

| Code Protection                        | ,   |

| COMF                                   |     |

| Comparator                             |     |

| Analog Input Connection Considerations |     |

| Associated Registers                   |     |

| Configuration                          |     |

| Effects of a Reset                     |     |

| Interrupts                             |     |

| Operation                              |     |

| Operation in Power-Managed Modes       |     |

|                                        |     |

| Outputs                              | 223      |

|--------------------------------------|----------|

| Reference                            | 223      |

| Response Time                        | 223      |

| Comparator Specifications            |          |

| Comparator Voltage Reference         | 227      |

| Accuracy and Error                   |          |

| Associated Registers                 | 229      |

| Configuring                          | 227      |

| Connection Considerations            | 228      |

| Effects of a Reset                   | 228      |

| Operation in Power-Managed Modes     | 228      |

| Compare (CCP Module)                 | 136      |

| Associated Registers                 | 137      |

| CCP Pin Configuration                | 136      |

| CCPR1 Register                       |          |

| Software Interrupt                   | 136      |

| Special Event Trigger                | 136, 220 |

| Timer1/Timer3 Mode Selection         |          |

| Compare (ECCP Mode)                  | 142      |

| Computed GOTO                        |          |

| Configuration Bits                   |          |

| Configuration Register Protection    |          |

| Context Saving During Interrupts     |          |

| Control Registers                    |          |

| EECON1 and EECON2                    |          |

| Conversion Considerations            |          |

| CPFSEQ                               |          |

|                                      |          |

| CPFSLT                               |          |

| Crystal Oscillator/Ceramic Resonator |          |

| Customer Change Notification Service |          |

| Customer Notification Service        |          |

| Customer Support                     |          |

|                                      |          |

| D                                    |          |

| Data EEPROM Code Protection          | 255      |

| Data EEPROM Memory                   |          |

| Associated Registers                 |          |

| EEADR Register                       |          |

| EECON1 and EECON2 Registers          |          |

| Operation During Code-Protect        |          |

| Protection Against Spurious Write    |          |

| Reading                              |          |

| Using                                |          |

| Write Verify                         |          |

| Writing                              |          |

| Data Memory                          |          |

| General Purpose Registers            |          |

| Map for PIC18F2X20/4X20              |          |

| Special Function Registers           |          |

| DAW                                  |          |

| DC and AC Characteristics            |          |

| Graphs and Tables                    | 347      |

| DC Characteristics                   |          |

| Power-Down and Supply Current        |          |

|                                      |          |

Supply Voltage

308

DCFSNZ

277

DECF

276

DECFSZ

277

Development Support

301

Device Differences

376

Device Overview

7

Features (table)

8

New Core Features

7

Other Special Features

7

Direct Addressing

67