### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4220-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

## 2.0 OSCILLATOR CONFIGURATIONS

### 2.1 Oscillator Types

The PIC18F2X20 and PIC18F4X20 devices can be operated in ten different oscillator modes. The user can program the Configuration bits, FOSC3:FOSC0, in Configuration Register 1H to select one of these ten modes:

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. HSPLL High-Speed Crystal/Resonator with PLL Enabled

- 5. RC External Resistor/Capacitor with Fosc/4 Output on RA6

- 6. RCIO External Resistor/Capacitor with I/O on RA6

- 7. INTIO1 Internal Oscillator with Fosc/4 Output on RA6 and I/O on RA7

- 8. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 9. EC External Clock with Fosc/4 Output

- 10. ECIO External Clock with I/O on RA6

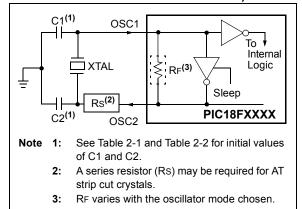

### 2.2 Crystal Oscillator/Ceramic Resonators

In XT, LP, HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 2-1 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

**Note:** Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications.

FIGURE 2-1:

### CRYSTAL/CERAMIC RESONATOR OPERATION (XT, LP, HS OR HSPLL CONFIGURATION)

## TABLE 2-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| ٦    | Typical Capacitor Values Used: |                |                |  |  |  |  |  |  |

|------|--------------------------------|----------------|----------------|--|--|--|--|--|--|

| Mode | Freq                           | OSC1           | OSC2           |  |  |  |  |  |  |

| XT   | 455 kHz                        | 56 pF          | 56 pF          |  |  |  |  |  |  |

|      | 2.0 MHz                        | 47 pF          | 47 pF          |  |  |  |  |  |  |

|      | 4.0 MHz                        | 33 pF          | 33 pF          |  |  |  |  |  |  |

| HS   | 8.0 MHz<br>16.0 MHz            | 27 pF<br>22 pF | 27 pF<br>22 pF |  |  |  |  |  |  |

### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes on page 20 for additional information.

| Resonators Used: |         |  |  |  |  |  |

|------------------|---------|--|--|--|--|--|

| 455 kHz          | 4.0 MHz |  |  |  |  |  |

| 2.0 MHz          | 8.0 MHz |  |  |  |  |  |

| 16.              | .0 MHz  |  |  |  |  |  |

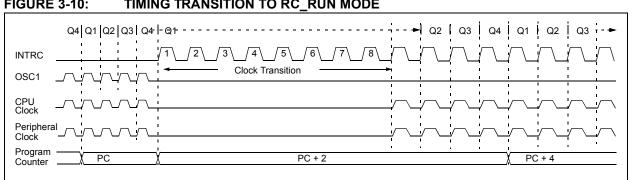

### 3.4.3 RC\_RUN MODE

In RC RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer and the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications which are not highly timing sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either of the INTIO1 or INTIO2 oscillators), there are no distinguishable differences between PRI RUN and RC RUN modes during execution. However, a clock switch delay will occur during entry to, and exit from, RC RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC RUN mode is not recommended.

This mode is entered by clearing the IDLEN bit, setting SCS1 (SCS0 is ignored) and executing a SLEEP instruction. The IRCF bits may select the clock frequency before the **SLEEP** instruction is executed. When the clock source is switched to the INTOSC multiplexer (see Figure 3-10), the primary oscillator is shut down and the OSTS bit is cleared.

The IRCF bits may be modified at any time to immediately change the system clock speed. Executing a SLEEP instruction is not required to select a new clock frequency from the INTOSC multiplexer.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

If the IRCF bits are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear: there will be no indication of the current clock source. The INTRC source is providing the system clocks.

If the IRCF bits are changed from all clear (thus enabling the INTOSC output), the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the system continue while the INTOSC source stabilizes in approximately 1 ms.

If the IRCF bits were previously at a non-zero value before the **SLEEP** instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set.

When a wake-up event occurs, the system continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 3-8). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### **FIGURE 3-10:** TIMING TRANSITION TO RC\_RUN MODE

| File Name | Bit 7                                                          | Bit 6          | Bit 5                 | Bit 4        | Bit 3         | Bit 2          | Bit 1           | Bit 0           | Value on<br>POR, BOR | Details on page: |

|-----------|----------------------------------------------------------------|----------------|-----------------------|--------------|---------------|----------------|-----------------|-----------------|----------------------|------------------|

| TOSU      | _                                                              |                |                       | Top-of-Stack | Upper Byte (1 | OS<20:16>)     |                 |                 | 0 0000               | 46, 54           |

| TOSH      | Top-of-Stack                                                   | High Byte (TO  | DS<15:8>)             | •            |               |                |                 |                 | 0000 0000            | 46, 54           |

| TOSL      | L Top-of-Stack Low Byte (TOS<7:0>)                             |                |                       |              |               |                |                 |                 | 0000 0000            | 46, 54           |

| STKPTR    | STKFUL STKUNF — Return Stack Pointer                           |                |                       |              |               |                |                 |                 | 00-0 0000            | 46, 55           |

| PCLATU    | _                                                              | _              | bit 21 <sup>(3)</sup> | Holding Regi | ster for PC<2 | D:16>          |                 |                 | 0 0000               | 46, 56           |

| PCLATH    |                                                                |                |                       |              |               |                |                 | 0000 0000       | 46, 56               |                  |

| PCL       | PC Low Byte                                                    | (PC<7:0>)      |                       |              |               |                |                 |                 | 0000 0000            | 46, 56           |

| TBLPTRU   | bit 21 Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |                |                       |              |               |                |                 | 00 0000         | 46, 74               |                  |

| TBLPTRH   | RH Program Memory Table Pointer High Byte (TBLPTR<15:8>)       |                |                       |              |               |                |                 | 0000 0000       | 46, 74               |                  |

| TBLPTRL   | Program Mer                                                    | mory Table Po  | inter Low Byt         | e (TBLPTR<7  | :0>)          |                |                 |                 | 0000 0000            | 46, 74           |

| TABLAT    | Program Mer                                                    | mory Table La  | tch                   |              |               |                |                 |                 | 0000 0000            | 46, 74           |

| PRODH     | Product Regi                                                   | ster High Byte | 9                     |              |               |                |                 |                 | XXXX XXXX            | 46, 85           |

| PRODL     | Product Regi                                                   | ster Low Byte  |                       |              |               |                |                 |                 | XXXX XXXX            | 46, 85           |

| INTCON    | GIE/GIEH                                                       | PEIE/GIEL      | TMR0IE                | INT0IE       | RBIE          | TMR0IF         | INT0IF          | RBIF            | 0000 000x            | 46, 89           |

| INTCON2   | RBPU                                                           | INTEDG0        | INTEDG1               | INTEDG2      | _             | TMR0IP         | _               | RBIP            | 1111 -1-1            | 46, 90           |

| INTCON3   | INT2IP                                                         | INT1IP         | -                     | INT2IE       | INT1IE        | _              | INT2IF          | INT1IF          | 11-0 0-00            | 46, 91           |

| INDF0     | Uses content                                                   | s of FSR0 to   | address data          | memory – val | ue of FSR0 no | ot changed (n  | ot a physical   | register)       | n/a                  | 46, 66           |

| POSTINC0  | Uses content                                                   | s of FSR0 to   | address data          | memory – val | ue of FSR0 po | ost-incremente | ed (not a phys  | sical register) | n/a                  | 46, 66           |

| POSTDEC0  | Uses content                                                   | s of FSR0 to a | address data          | memory – val | ue of FSR0 pc | st-decrement   | ed (not a phy   | sical register) | n/a                  | 46, 66           |

| PREINC0   | Uses content                                                   | s of FSR0 to   | address data          | memory – val | ue of FSR0 pr | e-incremente   | d (not a physi  | cal register)   | n/a                  | 46, 66           |

| PLUSW0    | Uses content                                                   | s of FSR0 to   | address data          | memory – val | ue of FSR0 of | fset by W (no  | t a physical re | egister)        | n/a                  | 46, 66           |

| FSR0H     | —                                                              | _              | _                     | _            | Indirect Data | Memory Add     | ress Pointer 0  | High            | 0000                 | 46, 66           |

| FSR0L     | Indirect Data                                                  | Memory Add     | ress Pointer 0        | Low Byte     |               |                |                 |                 | XXXX XXXX            | 46, 66           |

| WREG      | Working Reg                                                    | ister          |                       |              |               |                |                 |                 | XXXX XXXX            | 46               |

| INDF1     | Uses content                                                   | s of FSR1 to   | address data          | memory – val | ue of FSR1 no | ot changed (n  | ot a physical i | register)       | n/a                  | 46, 66           |

| POSTINC1  | Uses content                                                   | s of FSR1 to   | address data          | memory – val | ue of FSR1 po | ost-incremente | ed (not a phys  | sical register) | n/a                  | 46, 66           |

| POSTDEC1  | Uses content                                                   | s of FSR1 to a | address data          | memory – val | ue of FSR1 po | st-decrement   | ed (not a phy   | sical register) | n/a                  | 46, 66           |

| PREINC1   | Uses content                                                   | s of FSR1 to   | address data          | memory – val | ue of FSR1 pr | e-incremente   | d (not a physi  | cal register)   | n/a                  | 46, 66           |

| PLUSW1    | Uses content                                                   | s of FSR1 to   | address data          | memory – val | ue of FSR1 of | fset by W (no  | t a physical re | egister)        | n/a                  | 46, 66           |

| FSR1H     | —                                                              | _              | _                     | _            | Indirect Data | Memory Add     | ress Pointer 1  | High            | 0000                 | 47, 66           |

| FSR1L     | Indirect Data                                                  | Memory Add     | ress Pointer 1        | Low Byte     |               |                |                 |                 | XXXX XXXX            | 47, 66           |

| BSR       | _                                                              | _              | _                     | _            | Bank Select   | Register       |                 |                 | 0000                 | 47, 65           |

| INDF2     | Uses content                                                   | s of FSR2 to   | address data          | memory – val | ue of FSR2 no | ot changed (n  | ot a physical i | register)       | n/a                  | 47, 66           |

| POSTINC2  | Uses content                                                   | s of FSR2 to   | address data          | memory – val | ue of FSR2 po | ost-incremente | ed (not a phys  | sical register) | n/a                  | 47, 66           |

| POSTDEC2  | Uses content                                                   | s of FSR2 to a | address data          | memory – val | ue of FSR2 pc | st-decrement   | ed (not a phy   | sical register) | n/a                  | 47, 66           |

| PREINC2   | Uses content                                                   | s of FSR2 to   | address data          | memory – val | ue of FSR2 pr | e-incremente   | d (not a physi  | cal register)   | n/a                  | 47, 66           |

| PLUSW2    | Uses content                                                   | s of FSR2 to   | address data          | memory – val | ue of FSR2 of | fset by W (no  | t a physical re | egister)        | n/a                  | 47, 66           |

| FSR2H     | _                                                              | _              | _                     |              | Indirect Data | Memory Add     | ress Pointer 2  | High            | 0000                 | 47, 66           |

| FSR2L     | Indirect Data                                                  | Memory Add     | ress Pointer 2        | Low Byte     |               |                |                 |                 | XXXX XXXX            | 47, 66           |

| STATUS    | —                                                              | _              |                       | N            | OV            | Z              | DC              | С               | x xxxx               | 47, 68           |

| TMR0H     | Timer0 Regis                                                   | ter High Byte  |                       |              |               |                |                 |                 | 0000 0000            | 47, 119          |

| TMR0L     | Timer0 Regis                                                   | ter Low Byte   |                       |              |               |                |                 |                 | XXXX XXXX            | 47, 119          |

|           |                                                                |                |                       | 1            |               |                |                 |                 |                      | 1                |

### TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2220/2320/4220/4320)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO, ECIO and INTIO2 (with port function on RA6) Oscillator mode only and read as '0' in all other oscillator modes.

2: RA7 and associated bits are configured as port pins in INTIO2 Oscillator mode only and read as '0' in all other modes.

**3:** Bit 21 of the PC is only available in Test mode and Serial Programming modes.

4: If PBADEN = 0, PORTB<4:0> are configured as digital inputs and read unknown and if PBADEN = 1, PORTB<4:0> are configured as analog inputs and read as '0' following a Reset.

5: These registers and/or bits are not implemented on the PIC18F2X20 devices and read as 0x00.

6: The RE3 port bit is available as an input only pin only in 40-pin devices when Master Clear functionality is disabled (CONFIG3H<7>= 0).

NOTES:

| Name                   | Bit#  | Buffer | Function                                                                                                                                  |

|------------------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                | bit 0 | TTL    | Input/output or analog input.                                                                                                             |

| RA1/AN1                | bit 1 | TTL    | Input/output or analog input.                                                                                                             |

| RA2/AN2/VREF-/CVREF    | bit 2 | TTL    | Input/output, analog input, VREF- or comparator VREF output.                                                                              |

| RA3/AN3/VREF+          | bit 3 | TTL    | Input/output, analog input or VREF+.                                                                                                      |

| RA4/T0CKI/C1OUT        | bit 4 | ST     | Input/output, external clock input for Timer0 or Comparator 1 output. Output is open-drain type.                                          |

| RA5/AN4/SS/LVDIN/C2OUT | bit 5 | TTL    | Input/output, analog input, slave select input for Master<br>Synchronous Serial Port, Low-Voltage Detect input or<br>Comparator 2 output. |

| OSC2/CLKO/RA6          | bit 6 | TTL    | OSC2, clock output or I/O pin.                                                                                                            |

| OSC1/CLKI/RA7          | bit 7 | TTL    | OSC1, clock input or I/O pin.                                                                                                             |

### TABLE 10-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

### TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7                 | Bit 6                 | Bit 5     | Bit 4                   | Bit 3      | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------|-----------------------|-----------|-------------------------|------------|-------|-------|-------|----------------------|---------------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5       | RA4                     | RA3        | RA2   | RA1   | RA0   | xx0x 0000            | uu0u 0000                       |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA Data | ATA Data Latch Register |            |       |       |       |                      | uuuu uuuu                       |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA D   | ata Directio            | n Register |       |       |       | 1111 1111            | 1111 1111                       |

| ADCON1 | —                     | —                     | VCFG1     | VCFG0                   | PCFG3      | PCFG2 | PCFG1 | PCFG0 | 00 0000              | 00 0000                         |

| CMCON  | C2OUT                 | C10UT                 | C2INV     | C1INV                   | CIS        | CM2   | CM1   | CM0   | 0000 0111            | 0000 0111                       |

| CVRCON | CVREN                 | CVROE                 | CVRR      |                         | CVR3       | CVR2  | CVR1  | CVR0  | 000- 0000            | 000- 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA7:RA6 and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

| Name          | Bit#  | Buffer                                | Function                                                                                                                                                                                |

|---------------|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/AN12/INT0 | bit 0 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 0.<br>Internal software programmable weak pull-up.                                                                           |

| RB1/AN10/INT1 | bit 1 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 1.<br>Internal software programmable weak pull-up.                                                                           |

| RB2/AN8/INT2  | bit 2 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 2.<br>Internal software programmable weak pull-up.                                                                           |

| RB3/AN9/CCP2  | bit 3 | TTL <sup>(1)</sup> /ST <sup>(3)</sup> | Input/output pin or analog input. Capture 2 input/Compare 2 output/<br>PWM output when CCP2MX Configuration bit is set <sup>(4)</sup> .<br>Internal software programmable weak pull-up. |

| RB4/AN11/KBI0 | bit 4 | TTL                                   | Input/output pin (with interrupt-on-change) or analog input.<br>Internal software programmable weak pull-up.                                                                            |

| RB5/KBI1/PGM  | bit 5 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Low-voltage ICSP™ enable pin.                                                                 |

| RB6/KBI2/PGC  | bit 6 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                                                     |

| RB7/KBI3/PGD  | bit 7 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                                                      |

### TABLE 10-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a TTL input when configured as digital I/O.

- 2: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 3: This buffer is a Schmitt Trigger input when configured as the CCP2 input.

- 4: A device Configuration bit selects which I/O pin the CCP2 pin is multiplexed on.

- **5:** This buffer is a Schmitt Trigger input when used in Serial Programming mode.

| Name    | Bit 7                         | Bit 6        | Bit 5    | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------|--------------|----------|---------|--------|--------|--------|--------|----------------------|---------------------------------|

| PORTB   | RB7                           | RB6          | RB5      | RB4     | RB3    | RB2    | RB1    | RB0    | XXXX XXXX            | uuuu uuuu                       |

| LATB    | LATB LATB Data Latch Register |              |          |         |        |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| TRISB   | PORTB Da                      | ta Direction | Register |         |        |        |        |        | 1111 1111            | 1111 1111                       |

| INTCON  | GIE/GIEH                      | PEIE/GIEL    | TMR0IE   | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| INTCON2 | RBPU                          | INTEDG0      | INTEDG1  | INTEDG2 | _      | TMR0IP | _      | RBIP   | 1111 -1-1            | 1111 -1-1                       |

| INTCON3 | INT2IP                        | INT1IP       | _        | INT2IE  | INT1IE | —      | INT2IF | INT1IF | 11-0 0-00            | 11-0 0-00                       |

| ADCON1  | —                             | —            | VCFG1    | VCFG0   | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 00 0000              | 00 0000                         |

TABLE 10-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, — = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

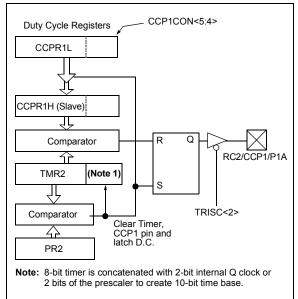

### 15.5 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force<br>the CCP1 PWM output latch to the default |

|-------|--------------------------------------------------------------------------------------|

|       | low level. This is not the PORTC I/O data latch.                                     |

Figure 15-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 15.5.3** "Setup for PWM Operation".

### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

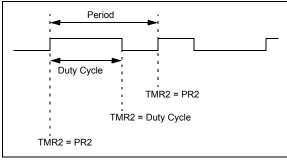

A PWM output (Figure 15-4) has a time base (*period*) and a time that the output is high (*duty cycle*). The frequency of the PWM is the inverse of the period (1/period).

### 15.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following equation.

### EQUATION 15-1:

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is copied from CCPR1L into CCPR1H

- Note: The Timer2 postscaler (see Section 13.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

### 15.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the following equation.

### **EQUATION 15-2:**

CCPR1L and CCP1CON<5:4> can be written to at any time but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

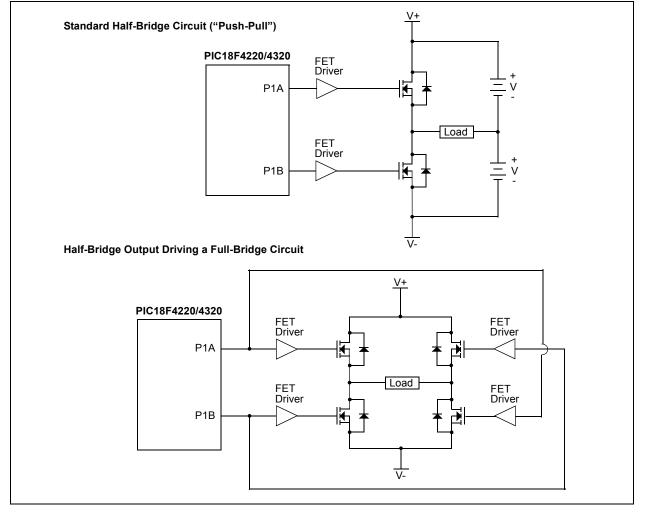

### 16.4.2 HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the RC2/CCP1/P1A pin, while the complementary PWM output signal is output on the RD5/ PSP5/P1B pin (Figure 16-4). This mode can be used for half-bridge applications, as shown in Figure 16-5, or for full-bridge applications where four power switches are being modulated with two PWM signals.

In Half-Bridge Output mode, the programmable dead band delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits PDC6:PDC0 sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 16.4.4 "Programmable Dead-Band Delay"** for more details of the dead band delay operations.

Since the P1A and P1B outputs are multiplexed with the PORTC<2> and PORTD<5> data latches, the TRISC<2> and TRISD<5> bits must be cleared to configure P1A and P1B as outputs.

# FIGURE 16-4: HALF-BRIDGE PWM OUTPUT

- **Note 1:** At this time, the TMR2 register is equal to the PR2 register.

- 2: Output signals are shown as active-high.

### FIGURE 16-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

## 16.4.4 PROGRAMMABLE DEAD-BAND DELAY

In half-bridge applications, where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shootthrough current*) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead band delay is available to avoid shootthrough current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 16-4 for illustration. The lower seven bits of the PWM1CON register (Register 16-2) set the delay period in terms of microcontroller instruction cycles (TCY or 4 TOSC).

### 16.4.5 ENHANCED PWM AUTO-SHUTDOWN

When the ECCP is programmed for any of the enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the enhanced PWM output pins into a defined shutdown state when a shutdown event occurs. A shutdown event can be caused by either of the two comparator modules or the INT0 pin (or any combination of these three sources). The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a digital signal on the INT0 pin can also trigger a shutdown. The autoshutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCPAS2:ECCPAS0 bits (ECCPAS<6:4>).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits (ECCPAS<3:0>). Each pin pair (P1A/P1C and P1B/ P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCPASE bit (ECCPAS<7>) is also set to hold the enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |

|-------------------|-------|------------------|-------|------------------|------------------|-----------------|-------|--|

| R = Readable bit  |       | W = Writable I   |       | U = Unimpler     | nented bit, read | as '0'          |       |  |

| Legend:           |       |                  |       |                  |                  |                 |       |  |

| bit 7             |       |                  |       |                  |                  |                 | bit 0 |  |

| PRSEN             | PDC6  | PDC5             | PDC4  | PDC3             | PDC2             | PDC1            | PDC0  |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |

### REGISTER 16-2: PWM1CON: PWM CONFIGURATION REGISTER

|         | the PWM restarts automatically                                                 |

|---------|--------------------------------------------------------------------------------|

|         | 0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM |

| bit 6-0 | PDC6:PDC0: PWM Delay Count bits                                                |

Delay time, in number of Fosc/4 (4 \* Tosc) cycles, between the scheduled time when a PWM signal should transition to active and the actual time it transitions active.

1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away;

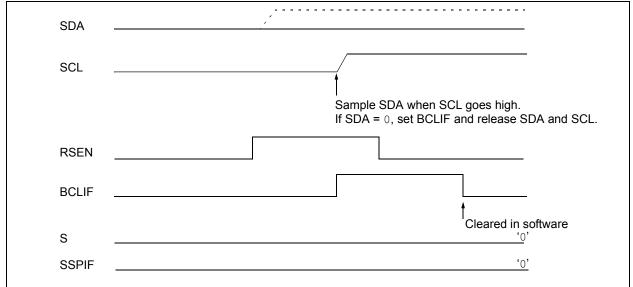

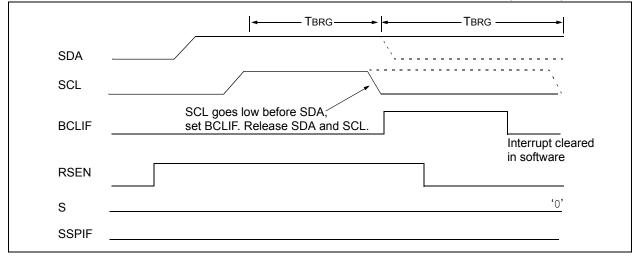

## 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 17-30).

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 17-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### FIGURE 17-30: BUS COLLISION DURING A REPEATED START CONDITION (CASE 2)

### REGISTER 18-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0         | R/W-0                                                                  | R/W-0                                                                              | R/W-0           | R/W-0             | R-0              | R-0               | R-x     |  |  |  |

|---------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-------------------|---------|--|--|--|

| SPEN          | RX9                                                                    | SREN                                                                               | CREN            | ADDEN             | FERR             | OERR              | RX9D    |  |  |  |

| bit 7         |                                                                        | L                                                                                  |                 |                   |                  |                   | bit     |  |  |  |

|               |                                                                        |                                                                                    |                 |                   |                  |                   |         |  |  |  |

| Legend:       |                                                                        |                                                                                    |                 |                   |                  |                   |         |  |  |  |

| R = Readabl   | e bit                                                                  | W = Writable                                                                       | bit             | U = Unimplen      | nented bit, read | d as '0'          |         |  |  |  |

| -n = Value at | POR                                                                    | '1' = Bit is set                                                                   |                 | '0' = Bit is clea | ared             | x = Bit is unkr   | nown    |  |  |  |

| bit 7         | SPEN: Seria                                                            | al Port Enable bi                                                                  | t               |                   |                  |                   |         |  |  |  |

|               |                                                                        | ort enabled (con                                                                   |                 | and TX/CK pir     | ns as serial por | t pins)           |         |  |  |  |

|               | •                                                                      | ort disabled (hel                                                                  | •               | ·                 |                  | . ,               |         |  |  |  |

| bit 6         | <b>RX9:</b> 9-Bit F                                                    | Receive Enable I                                                                   | oit             |                   |                  |                   |         |  |  |  |

|               |                                                                        | 9-bit reception<br>8-bit reception                                                 |                 |                   |                  |                   |         |  |  |  |

| bit 5         | SREN: Sing                                                             | le Receive Enat                                                                    | ole bit         |                   |                  |                   |         |  |  |  |

|               | <u>Asynchrono</u><br>Don't care.                                       | <u>us mode:</u>                                                                    |                 |                   |                  |                   |         |  |  |  |

|               | 1 = Enable<br>0 = Disable                                              | <u>is mode – Maste</u><br>s single receive<br>s single receive<br>eared after rece |                 | ete               |                  |                   |         |  |  |  |

|               |                                                                        | s mode – Slave:                                                                    |                 |                   |                  |                   |         |  |  |  |

| bit 4         | CREN: Con                                                              | tinuous Receive                                                                    | Enable bit      |                   |                  |                   |         |  |  |  |

|               | Asynchrono<br>1 = Enables<br>0 = Disables<br>Synchronou<br>1 = Enables | s receiver<br>s receiver                                                           | eive until enab | ble bit, CREN, is | s cleared (CRE   | N overrides SR    | EN)     |  |  |  |

|               | 0 = Disables                                                           | s continuous rec                                                                   | eive            |                   |                  |                   |         |  |  |  |

| bit 3         |                                                                        | Idress Detect En                                                                   |                 |                   |                  |                   |         |  |  |  |

|               | 1 = Enables                                                            | <u>us mode 9-bit (F</u><br>s address detect<br>s address detec                     | ion, enables i  |                   |                  |                   |         |  |  |  |

| bit 2         | FERR: Framing Error bit                                                |                                                                                    |                 |                   |                  |                   |         |  |  |  |

|               | 1 = Framing<br>0 = No fram                                             | ı error (can be u<br>ing error                                                     | odated by rea   | ding RCREG re     | egister and rece | eiving next valio | l byte) |  |  |  |

| bit 1         | OERR: Ove                                                              | rrun Error bit                                                                     |                 |                   |                  |                   |         |  |  |  |

|               | 1 = Overrun<br>0 = No over                                             | error (can be cl<br>run error                                                      | eared by clea   | ring bit CREN)    |                  |                   |         |  |  |  |

| bit 0         | <b>RX9D:</b> 9th b                                                     | oit of Received D                                                                  | )ata            |                   |                  |                   |         |  |  |  |

|               |                                                                        |                                                                                    |                 |                   |                  |                   |         |  |  |  |

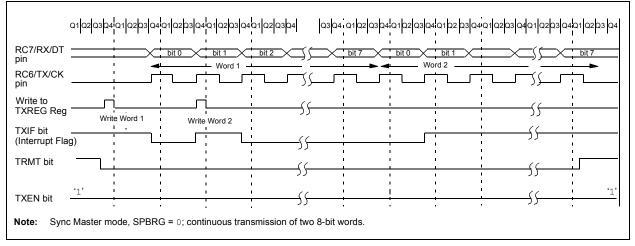

### 18.4 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit, CSRC (TXSTA<7>).

### 18.4.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 18-1. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit, TXIF (PIR1<4>), is set. The interrupt can be enabled/disabled by setting/clearing enable bit, TXIE

(PIE1<4>). Flag bit, TXIF, will be set regardless of the state of enable bit, TXIE, and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 18.2 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### FIGURE 18-6: SYNCHRONOUS TRANSMISSION

| NEGF                   | Negate f                                                                |                             |                                                            |  |  |  |  |  |

|------------------------|-------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|--|--|--|--|--|

| Syntax:                | [label]                                                                 | NEGF f[,a                   | a]                                                         |  |  |  |  |  |

| Operands:              | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                | 0 ≤ f ≤ 255<br>a ∈ [0,1]    |                                                            |  |  |  |  |  |

| Operation:             | $(\overline{f}) + 1 \rightarrow$                                        | f                           |                                                            |  |  |  |  |  |

| Status Affected:       | N, OV, C,                                                               | DC, Z                       |                                                            |  |  |  |  |  |

| Encoding:              | 0110                                                                    | 110a ff:                    | ff ffff                                                    |  |  |  |  |  |

| Description:           | compleme<br>the data m<br>is '0', the A<br>selected, c<br>If 'a' = 1, t | nemory locat<br>Access Bank | t is placed in<br>ion 'f'. If 'a'<br>will be<br>BSR value. |  |  |  |  |  |

| Words:                 | 1                                                                       |                             |                                                            |  |  |  |  |  |

| Cycles:                | 1                                                                       |                             |                                                            |  |  |  |  |  |

| Q Cycle Activity:      |                                                                         |                             |                                                            |  |  |  |  |  |

| Q1                     | Q2                                                                      | Q3                          | Q4                                                         |  |  |  |  |  |

| Decode                 | Read<br>register 'f'                                                    | Process<br>Data             | Write<br>register 'f'                                      |  |  |  |  |  |

| Example:               | NEGF R                                                                  | EG <b>,</b> 1               |                                                            |  |  |  |  |  |

| Before Instruc<br>REG  | = 0011 1                                                                | 010 <b>[0x3A]</b>           |                                                            |  |  |  |  |  |

| After Instructi<br>REG | on<br>= 1100 0                                                          | 110 <b>[0xC6]</b>           |                                                            |  |  |  |  |  |

| NOF                     | •              | No Opera  | No Operation        |           |  |      |  |  |

|-------------------------|----------------|-----------|---------------------|-----------|--|------|--|--|

| Synt                    | ax:            | [ label ] | NOP                 |           |  |      |  |  |

| Ope                     | rands:         | None      |                     |           |  |      |  |  |

| Operation: No operation |                |           |                     |           |  |      |  |  |

| Statu                   | us Affected:   | None      | None                |           |  |      |  |  |

| Enco                    | oding:         | 0000      | 0000                | 0000 000  |  | 0000 |  |  |

|                         |                | 1111      | XXXX                | XXXX XXXX |  |      |  |  |

| Desc                    | cription:      | No operat | tion.               |           |  |      |  |  |

| Wor                     | ds:            | 1         |                     |           |  |      |  |  |

| Cycl                    | es:            | 1         |                     |           |  |      |  |  |

| QC                      | ycle Activity: |           |                     |           |  |      |  |  |

|                         | Q1             | Q2        | Q3                  | 3         |  | Q4   |  |  |

|                         | Decode         | No        | No                  |           |  | No   |  |  |

|                         |                | operation | operation operation |           |  |      |  |  |

### Example:

None.

### **TABLE 26-2: COMPARATOR SPECIFICATIONS**

| Param<br>No. | Sym    | Characteristics                            | Min | Тур  | Мах        | Units    | Comments                  |

|--------------|--------|--------------------------------------------|-----|------|------------|----------|---------------------------|

| D300         | VIOFF  | Input Offset Voltage                       |     | ±5.0 | ±10        | mV       |                           |

| D301         | VICM   | Input Common Mode Voltage*                 | 0   | —    | Vdd - 1.5  | V        |                           |

| D302         | CMRR   | Common Mode Rejection Ratio*               | 55  | _    | _          | dB       |                           |

| 300<br>300A  | TRESP  | Response Time <sup>(1)*</sup>              |     | 150  | 400<br>600 | ns<br>ns | PIC18FXX20<br>PIC18LFXX20 |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid* | _   | —    | 10         | μS       |                           |

These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD.

### TABLE 26-3: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> $3.0V < VDD < 5.5V$ , $-40^{\circ}C < TA < +125^{\circ}C$ , unless otherwise stated. |      |                               |        |     |        |       |                      |

|-------------------------------------------------------------------------------------------------------------------|------|-------------------------------|--------|-----|--------|-------|----------------------|

| Param<br>No.                                                                                                      | Sym  | Characteristics               | Min    | Тур | Мах    | Units | Comments             |

| D310                                                                                                              | VRES | Resolution                    | VDD/24 | _   | VDD/32 | LSb   |                      |

| D311                                                                                                              | VRAA | Absolute Accuracy             | _      |     | 1/2    | LSb   | Low Range (VRR = 1)  |

|                                                                                                                   |      |                               | —      |     | 1/2    | LSb   | High Range (VRR = 0) |

| D312                                                                                                              | VRur | Unit Resistor Value (R)*      | —      | 2k  | _      | Ω     |                      |

| 310                                                                                                               | TSET | Settling Time <sup>(1)*</sup> | —      | _   | 10     | μS    |                      |

\* These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

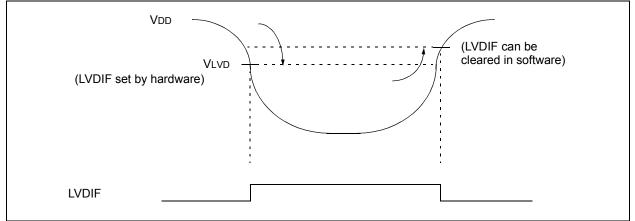

#### FIGURE 26-4: LOW-VOLTAGE DETECT CHARACTERISTICS

| Param.<br>No. | Symbol                | Characterist                                              | ic                   | Min           | Max | Units | Conditions |

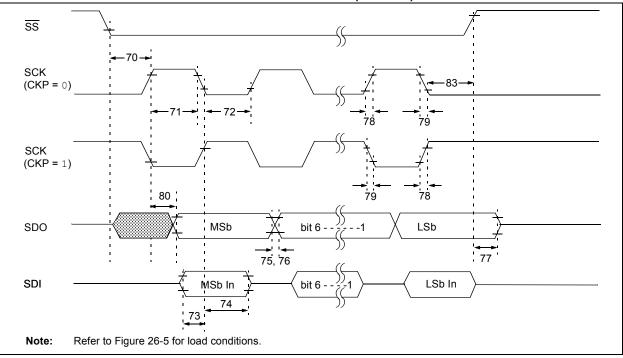

|---------------|-----------------------|-----------------------------------------------------------|----------------------|---------------|-----|-------|------------|

| 71            | TscH                  | SCK Input High Time Continuous                            |                      | 1.25 Tcy + 30 | _   | ns    |            |

| 71A           |                       | (Slave mode)                                              | Single Byte          | 40            |     | ns    | (Note 1)   |

| 72            | TscL                  | SCK Input Low Time                                        | Continuous           | 1.25 Tcy + 30 |     | ns    |            |

| 72A           |                       | (Slave mode)                                              | Single Byte          | 40            | _   | ns    | (Note 1)   |

| 73            | TDIV2scH,<br>TDIV2scL | Setup Time of SDI Data Input to SCK Edge                  |                      | 100           | —   | ns    |            |

| 73A           | Тв2в                  | Last Clock Edge of Byte 1 to the 1st Clock Edge of Byte 2 |                      | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74            | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edge                   |                      | 100           | _   | ns    |            |

| 75            | TDOR                  | SDO Data Output Rise Time PIC18FXX20                      |                      | —             | 25  | ns    |            |

|               |                       |                                                           | PIC18 <b>LF</b> XX20 |               | 45  | ns    |            |

| 76            | TDOF                  | SDO Data Output Fall Time                                 |                      | —             | 25  | ns    |            |

| 78            | TscR                  | SCK Output Rise Time                                      | PIC18FXX20           | —             | 25  | ns    |            |

|               |                       | (Master mode)                                             | PIC18 <b>LF</b> XX20 |               | 45  | ns    |            |

| 79            | TscF                  | SCK Output Fall Time (Maste                               | r mode)              | —             | 25  | ns    |            |

| 80            | TscH2doV,             | SDO Data Output Valid after                               | PIC18FXX20           | —             | 50  | ns    |            |

|               | TscL2DoV              | SCK Edge                                                  | PIC18 <b>LF</b> XX20 |               | 100 | ns    |            |

| 81            | TDOV2SCH,<br>TDOV2SCL | SDO Data Output Setup to SO                               | CK Edge              | Тсү           | —   | ns    |            |

| TABLE 26-15: | EXAMPLE SPI MODE REQUIREMENTS | (MASTER MODE, CKE = 1) |

|--------------|-------------------------------|------------------------|

|--------------|-------------------------------|------------------------|

**Note 1:** Requires the use of Parameter # 73A.

2: Only if Parameter # 71A and # 72A are used.

## FIGURE 26-15: EXAMPLE SPI SLAVE MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol  | Characte           | eristic                   | Min              | Мах  | Units | Conditions                   |

|---------------|---------|--------------------|---------------------------|------------------|------|-------|------------------------------|

| 100           | Тнідн   | Clock High Time    | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|               |         |                    | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                              |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |      | ms    |                              |

| 101           | TLOW    | Clock Low Time     | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                              |

|               |         |                    | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |      | ms    |                              |

| 102           | TR      | SDA and SCL        | 100 kHz mode              | —                | 1000 | ns    | CB is specified to be from   |

|               |         | Rise Time          | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns    | 10 to 400 pF                 |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | _                | 300  | ns    |                              |

| 103           | TF      | SDA and SCL        | 100 kHz mode              | _                | 300  | ns    | CB is specified to be from   |

|               |         | Fall Time          | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns    | 10 to 400 pF                 |

|               |         |                    | 1 MHz mode <sup>(1)</sup> |                  | 100  | ns    |                              |

| 90            | TSU:STA | Start Condition    | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | Only relevant for            |

|               |         | Setup Time         | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | Repeated Start condition     |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |

| 91            | THD:STA | Start Condition    | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | After this period, the first |

|               |         | Hold Time          | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | clock pulse is generated     |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |

| 106           | THD:DAT | Data Input         | 100 kHz mode              | 0                | _    | ns    |                              |

|               |         | Hold Time          | 400 kHz mode              | 0                | 0.9  | ms    |                              |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | TBD              | _    | ns    |                              |

| 107           | TSU:DAT | Data Input         | 100 kHz mode              | 250              | _    | ns    | (Note 2)                     |

|               |         | Setup Time         | 400 kHz mode              | 100              | _    | ns    |                              |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | TBD              | _    | ns    |                              |

| 92            | Tsu:sto | Stop Condition     | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|               |         | Setup Time         | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |

| 109           | ΤΑΑ     | Output Valid from  | 100 kHz mode              | —                | 3500 | ns    |                              |

|               |         | Clock              | 400 kHz mode              | —                | 1000 | ns    |                              |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | —                | _    | ns    |                              |

| 110           | TBUF    | Bus Free Time      | 100 kHz mode              | 4.7              | _    | ms    | Time the bus must be free    |

|               |         |                    | 400 kHz mode              | 1.3              | _    | ms    | before a new transmission    |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | TBD              |      | ms    | can start                    |

| D102          | Св      | Bus Capacitive Loa | dina                      | _                | 400  | pF    |                              |

| TABLE 26-21: MASTER SSP I <sup>2</sup> C™ BUS DATA REQUIREMENT |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A fast mode I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but parameter #107 ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line, parameter #102 + parameter #107 = 1000 + 250 = 1250 ns (for 100 kHz mode), before the SCL line is released.

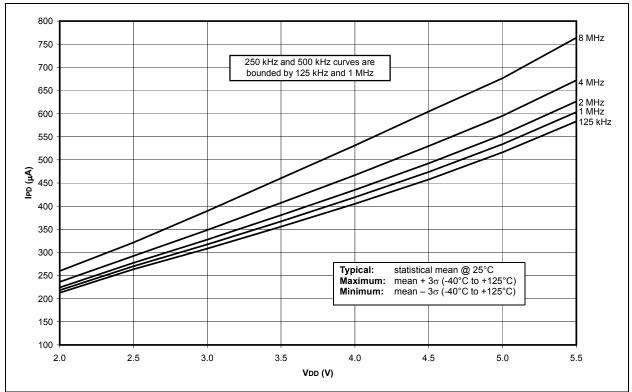

FIGURE 27-19: MAXIMUM IPD vs. VDD (-40°C TO +125°C), 125 kHz TO 8 MHz RC\_IDLE, ALL PERIPHERALS DISABLED

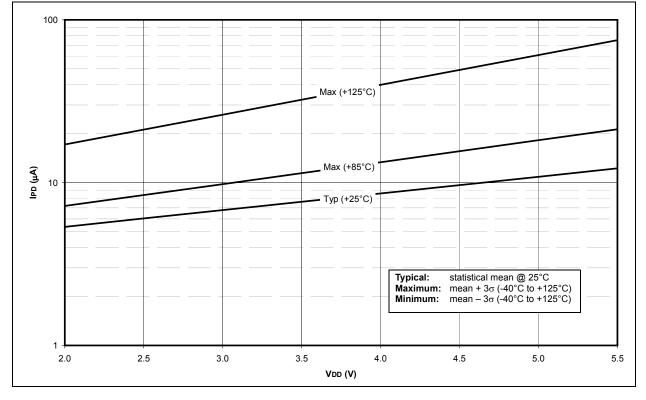

FIGURE 27-20: TYPICAL AND MAXIMUM IPD vs. VDD (-40°C TO +125°C), 31.25 kHz RC\_IDLE, ALL PERIPHERALS DISABLED

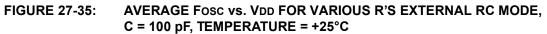

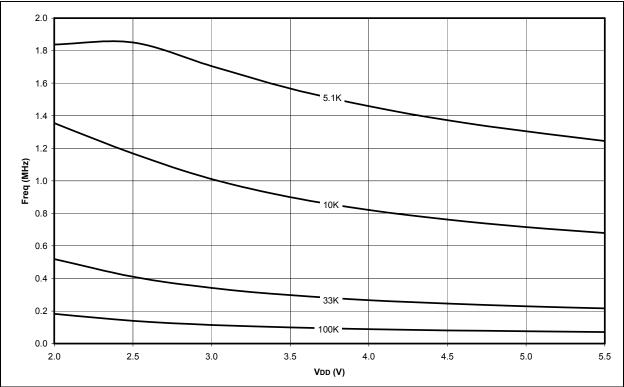

FIGURE 27-36: AVERAGE FOSC vs. VDD FOR VARIOUS R'S EXTERNAL RC MODE, C = 300 pF, TEMPERATURE = +25°C

| MPLINK Object Linker/MPLIB Object Librarian |     |

|---------------------------------------------|-----|

| MSSP                                        | 155 |

| Control Registers (General)                 | 155 |

| Enabling SPI I/O                            | 159 |

| I <sup>2</sup> C Master Mode                | 179 |

| I <sup>2</sup> C Mode                       |     |

| I <sup>2</sup> C Mode. See I <sup>2</sup> C |     |

| I <sup>2</sup> C Slave Mode                 | 168 |

| Operation                                   | 158 |

| Overview                                    | 155 |

| Slave Select Control                        |     |

| SPI Master Mode                             | 160 |

| SPI Master/Slave Connection                 | 159 |

| SPI Mode                                    |     |

| SPI Slave Mode                              |     |

| SSPBUF Register                             |     |

| SSPSR Register                              | 160 |

| TMR2 Output for Clock Shift                 |     |

| Typical Connection                          | 159 |

| MULLW                                       |     |

| MULWF                                       |     |

|                                             |     |

## Ν

| NEGF | 285 |

|------|-----|

| NOP  | 285 |

## 0

| Opcode Field Descriptions       |             |

|---------------------------------|-------------|

| Oscillator Configuration        |             |

| EC                              |             |

| ECIO                            |             |

| HS                              |             |

| HSPLL                           |             |

| Internal Oscillator Block       |             |

| INTIO1                          |             |

| INTIO2                          |             |

| LP                              |             |

| RC                              |             |

| RCIO                            |             |

| ХТ                              |             |

| Oscillator Selection            |             |

| Oscillator Start-up Timer (OST) | 28, 44, 237 |

| Oscillator Switching            |             |

| Oscillator Transitions          |             |

| Oscillator, Timer1              |             |

| Oscillator, Timer3              |             |

|                                 |             |

### Ρ

| Packaging Information                |

|--------------------------------------|

| Details                              |

| Marking                              |

| Parallel Slave Port (PSP) 109, 114   |

| Associated Registers                 |

| CS (Chip Select)                     |

| PORTD                                |

| RD (Read Input)                      |

| RE0/AN5/RD Pin                       |

| RE1/AN6/WR Pin113                    |

| RE2/AN7/CS Pin113                    |

| Select (PSPMODE Bit) 109, 114        |

| WR (Write Input) 113, 114            |

| PICSTART Plus Development Programmer |

| PIE Registers                        |

| Pin Functions                        |

| MCLR/Vpp/RE3                         |

| OSC1/CLKI/RA7 11, 14                 |

| OSC2/CLKO/RA611, 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| RA0/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                                  |

| RA1/AN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| RA2/AN2/Vref-/CVref11, 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                  |

| RA3/AN3/Vref+11, 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                  |

| RA4/T0CKI/C1OUT11, 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |