Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4220-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 28/40/44-Pin High-Performance, Enhanced Flash MCUs with 10-Bit A/D and nanoWatt Technology

#### Low-Power Features:

- Power-Managed modes:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- Power Consumption modes:

- PRI\_RUN: 150 μA, 1 MHz, 2V

- PRI\_IDLE: 37 μA, 1 MHz, 2V

- SEC\_RUN: 14 μA, 32 kHz, 2V

- SEC\_IDLE: 5.8 μA, 32 kHz, 2V

- RC\_RUN: 110 μA, 1 MHz, 2V

- RC\_IDLE: 52 μA, 1 MHz, 2V

- Sleep: 0.1 μA, 1 MHz, 2V

- Timer1 Oscillator: 1.1 μA, 32 kHz, 2V

- Watchdog Timer: 2.1 μA

- Two-Speed Oscillator Start-up

#### **Oscillators:**

- Four Crystal modes:

- LP, XT, HS: up to 25 MHz

- HSPLL: 4-10 MHz (16-40 MHz internal)

- · Two External RC modes, Up to 4 MHz

- Two External Clock modes, Up to 40 MHz

- Internal Oscillator Block:

- 8 user-selectable frequencies: 31 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz, 8 MHz

- 125 kHz-8 MHz calibrated to 1%

- Two modes select one or two I/O pins

- OSCTUNE Allows user to shift frequency

- Secondary Oscillator using Timer1 @ 32 kHz

- · Fail-Safe Clock Monitor

- Allows for safe shutdown if peripheral clock stops

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA

- Three External Interrupts

- Up to 2 Capture/Compare/PWM (CCP) modules:

- Capture is 16-bit, max. resolution is 6.25 ns (Tcy/16)

- Compare is 16-bit, max. resolution is 100 ns (TCY)

- PWM output: PWM resolution is 1 to 10-bit

- Enhanced Capture/Compare/PWM (ECCP) module:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-Shutdown and Auto-Restart

- Compatible 10-Bit, Up to 13-Channel Analog-to-Digital Converter (A/D) module with Programmable Acquisition Time

- Dual Analog Comparators

- · Addressable USART module:

- RS-232 operation using internal oscillator block (no external crystal required)

#### **Special Microcontroller Features:**

- 100,000 Erase/Write Cycle Enhanced Flash Program Memory Typical

- 1,000,000 Erase/Write Cycle Data EEPROM Memory Typical

- Flash/Data EEPROM Retention: > 40 Years

- Self-Programmable under Software Control

- · Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 41 ms to 131s

2% stability over VDD and Temperature

- Single-Supply 5V In-Circuit Serial Programming™ (ICSP™) via Two Pins

- In-Circuit Debug (ICD) via Two Pins

- Wide Operating Voltage Range: 2.0V to 5.5V

|            | Program Memory   |                               | Data Memory     |                   |     |                    | CCP/          | MSSP |                             |       | ors        |                    |  |

|------------|------------------|-------------------------------|-----------------|-------------------|-----|--------------------|---------------|------|-----------------------------|-------|------------|--------------------|--|

| Device     | Flash<br>(bytes) | # Single Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | 10-Bit<br>A/D (ch) | ECCP<br>(PWM) | SPI  | Master<br>I <sup>2</sup> C™ | USART | Comparator | Timers<br>8/16-bit |  |

| PIC18F2220 | 4096             | 2048                          | 512             | 256               | 25  | 10                 | 2/0           | Y    | Y                           | Y     | 2          | 2/3                |  |

| PIC18F2320 | 8192             | 4096                          | 512             | 256               | 25  | 10                 | 2/0           | Y    | Y                           | Y     | 2          | 2/3                |  |

| PIC18F4220 | 4096             | 2048                          | 512             | 256               | 36  | 13                 | 1/1           | Y    | Y                           | Y     | 2          | 2/3                |  |

| PIC18F4320 | 8192             | 4096                          | 512             | 256               | 36  | 13                 | 1/1           | Y    | Y                           | Y     | 2          | 2/3                |  |

### 5.10 Access Bank

The Access Bank is an architectural enhancement which is very useful for C compiler code optimization. The techniques used by the C compiler may also be useful for programs written in assembly.

This data memory region can be used for:

- · Intermediate computational values

- · Local variables of subroutines

- Faster context saving/switching of variables

- Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the last 128 bytes in Bank 15 (SFRs) and the first 128 bytes in Bank 0. These two sections will be referred to as Access RAM High and Access RAM Low, respectively. Figure 5-6 indicates the Access RAM areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register or in the Access Bank. This bit is denoted as the 'a' bit (for access bit).

When forced in the Access Bank (a = 0), the last address in Access RAM Low is followed by the first address in Access RAM High. Access RAM High maps the Special Function Registers, so these registers can be accessed without any software overhead. This is useful for testing status flags and modifying control bits.

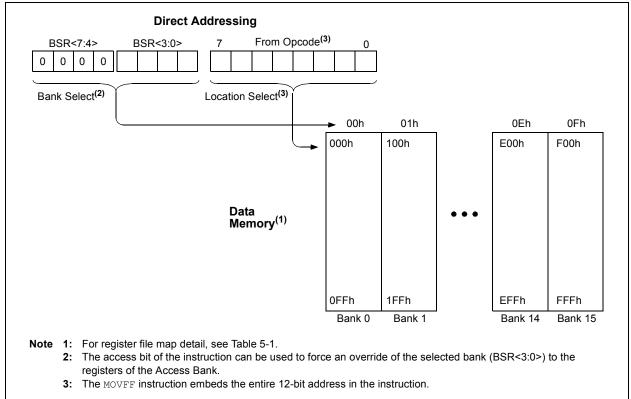

### 5.11 Bank Select Register (BSR)

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into as many as sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's and writes will have no effect (see Figure 5-7).

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The STATUS register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR since the 12-bit addresses are embedded into the instruction word.

Section 5.12 "Indirect Addressing, INDF and FSR Registers" provides a description of indirect addressing which allows linear addressing of the entire RAM space.

#### FIGURE 5-7: DIRECT ADDRESSING

## 5.13 STATUS Register

The STATUS register, shown in Register 5-2, contains the arithmetic status of the ALU. The STATUS register can be the operand for any instruction as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, then the write to these five bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register. For other instructions not affecting any Status bits (see Table 24-2).

| Note: | The C and DC bits operate as a borrow |  |

|-------|---------------------------------------|--|

|       | and digit borrow bit respectively, in |  |

|       | subtraction.                          |  |

## REGISTER 5-2: STATUS REGISTER

| U-0 U-0             |                                                                                                          | U-0                                                                                               | R/W-x                               | R/W-x                             | R/W-x                             | R/W-x                                | R/W-x                            |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------|-----------------------------------|--------------------------------------|----------------------------------|--|--|--|

| _                   | —                                                                                                        | —                                                                                                 | N                                   | OV                                | Z                                 | DC <sup>(1)</sup>                    | C <sup>(2)</sup>                 |  |  |  |

| bit 7               |                                                                                                          |                                                                                                   |                                     |                                   |                                   |                                      | bit 0                            |  |  |  |

|                     |                                                                                                          |                                                                                                   |                                     |                                   |                                   |                                      |                                  |  |  |  |

| Legend:<br>R = Read | labla bit                                                                                                | W = Writable                                                                                      | hit                                 | II – Unimplo                      | mented bit, rea                   | d aa 'O'                             |                                  |  |  |  |

| -n = Valu           |                                                                                                          | '1' = Bit is se                                                                                   |                                     | '0' = Bit is cle                  |                                   | x = Bit is unkr                      | NOW/D                            |  |  |  |

| n – valu            |                                                                                                          |                                                                                                   |                                     |                                   |                                   |                                      |                                  |  |  |  |

| bit 7-5             | Unimplemer                                                                                               | nted: Read as                                                                                     | <b>'</b> 0 <b>'</b>                 |                                   |                                   |                                      |                                  |  |  |  |

| bit 4               | N: Negative<br>This bit is us<br>(ALU MSB =<br>1 = Result w                                              | ed for signed a 1).                                                                               | rithmetic (2's o                    | complement). I                    | t indicates whe                   | ther the result w                    | as negative                      |  |  |  |

| bit 3               |                                                                                                          | v bit<br>ed for signed a                                                                          |                                     |                                   |                                   | verflow of the 7-                    | bit magnitude                    |  |  |  |

|                     |                                                                                                          |                                                                                                   |                                     | , .                               | tate.<br>netic operation          | )                                    |                                  |  |  |  |

| bit 2               |                                                                                                          | Ilt of an arithme                                                                                 |                                     |                                   | ero                               |                                      |                                  |  |  |  |

| bit 1               | DC: Digit Ca                                                                                             | rry/ <mark>Borrow</mark> bit <sup>(1</sup><br>Addlw, Sublw                                        | l)                                  |                                   |                                   |                                      |                                  |  |  |  |

|                     | 0 = No carry                                                                                             | out from the 4th<br>-out from the 4                                                               |                                     |                                   | curred                            |                                      |                                  |  |  |  |

| bit 0               |                                                                                                          | arry/ <mark>Borrow</mark> bit <sup>(2)</sup><br>DDWF, ADDLW, SUBLW <b>and</b> SUBWF instructions: |                                     |                                   |                                   |                                      |                                  |  |  |  |

|                     | 1 = A carry-c                                                                                            | out from the Mo<br>out from the Mo                                                                | st Significant                      | bit of the result                 |                                   |                                      |                                  |  |  |  |

| Note 1:<br>2:       | For Borrow, the po<br>operand. For rotat<br>For Borrow, the po<br>operand. For rotat<br>source register. | te (RRF, RLF) ir<br>plarity is revers                                                             | nstructions, thi<br>ed. A subtracti | s bit is loaded<br>on is executed | with either bit 4 by adding the 2 | or bit 3 of the so<br>2's complement | ource register.<br>of the second |  |  |  |

## 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

While writing or erasing program memory, instruction fetches cease until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

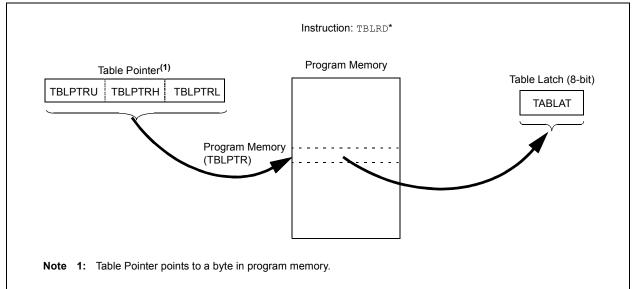

### 6.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

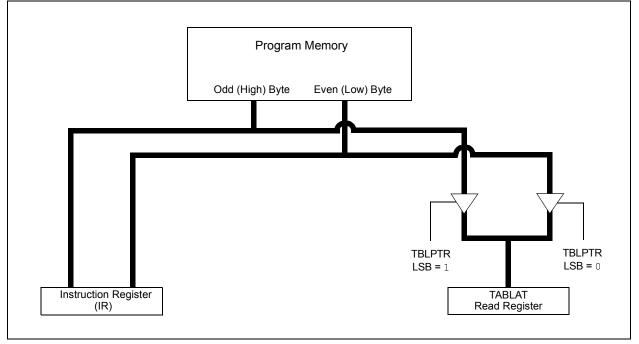

Table read operations retrieve data from program memory and place it into TABLAT in the data RAM space. Figure 6-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from TABLAT in the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 6.5 "Writing to Flash Program Memory"**. Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned (TBLPTRL<0> = 0).

The EEPROM on-chip timer controls the write and erase times. The write and erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

FIGURE 6-1: TABLE READ OPERATION

#### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and place it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing a TBLRD instruction places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

## FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base             |

|-----------|---------|-----------------|---|---------------------------------------|

|           | MOVWF   | TBLPTRU         | ; | address of the word                   |

|           | MOVLW   | CODE_ADDR_HIGH  |   |                                       |

|           | MOVWF   | TBLPTRH         |   |                                       |

|           | MOVLW   | CODE ADDR LOW   |   |                                       |

|           | MOVWF   | TBLPTRL         |   |                                       |

| READ_WORD |         |                 |   |                                       |

|           | TBLRD*+ |                 | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD EVEN       |   |                                       |

|           | TBLRD*+ | _               | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD_ODD        |   |                                       |

|           |         |                 |   |                                       |

## 8.0 8 X 8 HARDWARE MULTIPLIER

## 8.1 Introduction

An 8 x 8 hardware multiplier is included in the ALU of the PIC18F2X20/4X20 devices. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored into the 16-bit product register pair (PRODH:PRODL). The multiplier does not affect any flags in the STATUS register.

Making the 8 x 8 multiplier execute in a single-cycle gives the following advantages:

- Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in applications previously reserved for Digital Signal Processors.

Table 8-1 shows a performance comparison between enhanced devices using the single-cycle hardware multiply and performing the same function without the hardware multiply.

## 8.2 Operation

Example 8-1 shows the sequence to do an 8 x 8 unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiply. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF<br>MULWF | ARG1,<br>ARG2 | W | ;<br>; ARG1 * ARG2 -> |

|---------------|---------------|---|-----------------------|

|               |               |   | ; PRODH:PRODL         |

#### EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W  |                  |

|-------|----------|------------------|

| MULWF | ARG2     | ; ARG1 * ARG2 -> |

|       |          | ; PRODH:PRODL    |

| BTFSC | ARG2, SB | ; Test Sign Bit  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |

|       |          | ; – ARG1         |

| MOVF  | ARG2, W  |                  |

| BTFSC | ARG1, SB | ; Test Sign Bit  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |

|       |          | ; – ARG2         |

|       |          |                  |

|                  |                           | Program           | Cycles | Time     |          |         |  |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |  |

| 9 x 9 uppigpod   | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |  |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |  |

| 9 x 9 signed     | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |  |  |

| 16 x 16 unsigned | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |  |  |

| To x To unsigned | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs   |  |  |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs   |  |  |

## TABLE 8-1: PERFORMANCE COMPARISON

| Name          | Bit#  | Buffer                                | Function                                                                                                                                                                                |

|---------------|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/AN12/INT0 | bit 0 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 0.<br>Internal software programmable weak pull-up.                                                                           |

| RB1/AN10/INT1 | bit 1 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 1.<br>Internal software programmable weak pull-up.                                                                           |

| RB2/AN8/INT2  | bit 2 | TTL <sup>(1)</sup> /ST <sup>(2)</sup> | Input/output pin, analog input or external interrupt input 2.<br>Internal software programmable weak pull-up.                                                                           |

| RB3/AN9/CCP2  | bit 3 | TTL <sup>(1)</sup> /ST <sup>(3)</sup> | Input/output pin or analog input. Capture 2 input/Compare 2 output/<br>PWM output when CCP2MX Configuration bit is set <sup>(4)</sup> .<br>Internal software programmable weak pull-up. |

| RB4/AN11/KBI0 | bit 4 | TTL                                   | Input/output pin (with interrupt-on-change) or analog input.<br>Internal software programmable weak pull-up.                                                                            |

| RB5/KBI1/PGM  | bit 5 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Low-voltage ICSP™ enable pin.                                                                 |

| RB6/KBI2/PGC  | bit 6 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                                                     |

| RB7/KBI3/PGD  | bit 7 | TTL/ST <sup>(5)</sup>                 | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                                                      |

## TABLE 10-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a TTL input when configured as digital I/O.

- 2: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 3: This buffer is a Schmitt Trigger input when configured as the CCP2 input.

- 4: A device Configuration bit selects which I/O pin the CCP2 pin is multiplexed on.

- **5:** This buffer is a Schmitt Trigger input when used in Serial Programming mode.

| Name    | Bit 7     | Bit 6        | Bit 5    | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------|--------------|----------|---------|--------|--------|--------|--------|----------------------|---------------------------------|

| PORTB   | RB7       | RB6          | RB5      | RB4     | RB3    | RB2    | RB1    | RB0    | XXXX XXXX            | uuuu uuuu                       |

| LATB    | LATB Data | Latch Regis  | ter      |         |        |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| TRISB   | PORTB Da  | ta Direction | Register |         |        |        |        |        | 1111 1111            | 1111 1111                       |

| INTCON  | GIE/GIEH  | PEIE/GIEL    | TMR0IE   | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| INTCON2 | RBPU      | INTEDG0      | INTEDG1  | INTEDG2 | _      | TMR0IP | _      | RBIP   | 1111 -1-1            | 1111 -1-1                       |

| INTCON3 | INT2IP    | INT1IP       | _        | INT2IE  | INT1IE | —      | INT2IF | INT1IF | 11-0 0-00            | 11-0 0-00                       |

| ADCON1  | —         | —            | VCFG1    | VCFG0   | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 00 0000              | 00 0000                         |

TABLE 10-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, — = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

#### 16.4.5.1 Auto-Shutdown and Automatic Restart

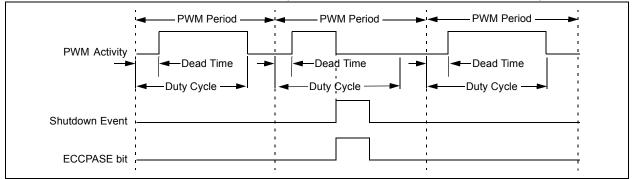

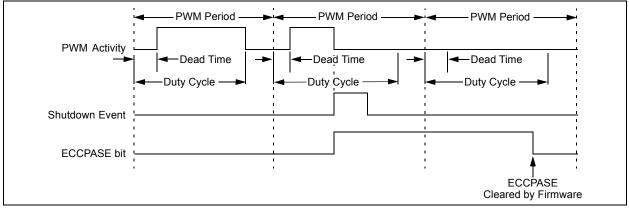

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the PRSEN bit of the PWM1CON register (PWM1CON<7>).

In Shutdown mode with PRSEN = 1 (Figure 16-10), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCPASE bit is cleared. If PRSEN = 0 (Figure 16-11), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, if the autoshutdown source is one of the comparators, the shutdown condition is a level. The ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

## 16.4.6 START-UP CONSIDERATIONS

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pullup and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the off state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

The CCP1M1:CCP1M0 bits (CCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP module may cause damage to the application circuit. The ECCP module must be enabled in the proper output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

#### FIGURE 16-10: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

| Name    | Bit 7      | Bit 6          | Bit 5      | Bit 4         | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, E | -    |      | e on<br>other<br>sets |

|---------|------------|----------------|------------|---------------|----------|--------|---------|---------|-----------------|------|------|-----------------------|

| INTCON  | GIE/GIEH   | PEIE/GIEL      | TMR0IE     | INT0IE        | RBIE     | TMR0IF | INT0IF  | RBIF    | 0000 0          | 000x | 0000 | 000u                  |

| RCON    | IPEN       | —              | _          | RI            | TO       | PD     | POR     | BOR     | 01 1            | L1q0 | 0q   | qquu                  |

| PIR1    | PSPIF      | ADIF           | RCIF       | TXIF          | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 0000 0          | 0000 | 0000 | 0000                  |

| PIE1    | PSPIE      | ADIE           | RCIE       | TXIE          | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 0000 0          | 0000 | 0000 | 0000                  |

| IPR1    | PSPIP      | ADIP           | RCIP       | TXIP          | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 1111 1          | 1111 | 1111 | 1111                  |

| TMR2    | Timer2 Mod | dule Register  |            |               |          |        |         |         | 0000 0          | 0000 | 0000 | 0000                  |

| PR2     | Timer2 Mod | dule Period R  | egister    |               |          |        |         |         | 1111 1          | 1111 | 1111 | 1111                  |

| T2CON   | —          | TOUTPS3        | TOUTPS2    | TOUTPS1       | TOUTPS0  | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0          | 0000 | -000 | 0000                  |

| TRISC   | PORTC Da   | ta Direction F | Register   |               |          |        |         |         | 1111 1          | 1111 | 1111 | 1111                  |

| TRISD   | PORTD Da   | ta Direction F | Register   |               |          |        |         |         | 1111 1          | 1111 | 1111 | 1111                  |

| CCPR1H  | Enhanced ( | Capture/Com    | pare/PWM F | Register 1 H  | igh Byte |        |         |         | XXXX X          | xxx  | uuuu | uuuu                  |

| CCPR1L  | Enhanced ( | Capture/Com    | pare/PWM F | Register 1 Lo | ow Byte  |        |         |         | XXXX X          | xxx  | uuuu | uuuu                  |

| CCP1CON | P1M1       | P1M0           | DC1B1      | DC1B0         | CCP1M3   | CCP1M2 | CCP1M1  | CCP1M0  | 0000 0          | 0000 | 0000 | 0000                  |

| ECCPAS  | ECCPASE    | ECCPAS2        | ECCPAS1    | ECCPAS0       | PSSAC1   | PSSAC0 | PSSBD1  | PSSBD0  | 0000 0          | 0000 | 0000 | 0000                  |

| PWM1CON | PRSEN      | PDC6           | PDC5       | PDC4          | PDC3     | PDC2   | PDC1    | PDC0    | 0000 0          | 0000 | 0000 | 0000                  |

| OSCCON  | IDLEN      | IRCF2          | IRCF1      | IRCF0         | OSTS     | IOFS   | SCS1    | SCS0    | 0000 q          | 1000 | 0000 | q000                  |

| TABLE 16-2: | REGISTERS ASSOCIATED WITH ENHANCED PWM AND TIMER2 |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the ECCP module in enhanced PWM mode.

| R/W-0      | R/W-0                              | R/W-0                                                                                                                                                                        | R/W-0         | R/W-0            | R/W-0                | R/W-0             | R/W-0  |  |  |  |

|------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|----------------------|-------------------|--------|--|--|--|

| GCEN       | ACKSTAT                            | ACKDT <sup>(1)</sup>                                                                                                                                                         | ACKEN         | RCEN             | PEN                  | RSEN              | SEN    |  |  |  |

| bit 7      |                                    |                                                                                                                                                                              |               |                  |                      |                   | bit    |  |  |  |

| Legend:    |                                    |                                                                                                                                                                              |               |                  |                      |                   |        |  |  |  |

| R = Reada  | ble bit                            | W = Writable                                                                                                                                                                 | bit           | U = Unimple      | mented bit, rea      | d as '0'          |        |  |  |  |

| -n = Value | at POR                             | '1' = Bit is set                                                                                                                                                             |               | '0' = Bit is cle |                      | x = Bit is unki   | nown   |  |  |  |

|            |                                    |                                                                                                                                                                              |               |                  |                      |                   |        |  |  |  |

| bit 7      |                                    | ral Call Enable                                                                                                                                                              | •             | • /              |                      |                   |        |  |  |  |

|            |                                    | •                                                                                                                                                                            | •             | ddress (0000h    | n) is received in    | the SSPSR         |        |  |  |  |

| bit 6      |                                    | all address dis<br>knowledge Sta                                                                                                                                             |               | or Transmit m    | ada anlu)            |                   |        |  |  |  |

| DILO       |                                    | dge was not re                                                                                                                                                               | -             |                  | Jue offiy)           |                   |        |  |  |  |

|            |                                    | dge was receiv                                                                                                                                                               |               |                  |                      |                   |        |  |  |  |

| bit 5      | ACKDT: Ackn                        | iowledge Data                                                                                                                                                                | bit (Master R | eceive mode c    | only) <sup>(1)</sup> |                   |        |  |  |  |

|            | 1 = Not Ackno                      | 0                                                                                                                                                                            |               |                  |                      |                   |        |  |  |  |

| bit 4      | 0 = Acknowle                       | •                                                                                                                                                                            | ionco Enablo  | hit (Mastar De   | nonivo modo or       | h.)               |        |  |  |  |

|            |                                    | <b>ACKEN:</b> Acknowledge Sequence Enable bit (Master Receive mode only)<br>1 = Initiate Acknowledge sequence on SDA and SCL pins and transmit ACKDT data bit. Automatically |               |                  |                      |                   |        |  |  |  |

|            | cleared b                          | y hardware.                                                                                                                                                                  |               |                  |                      |                   |        |  |  |  |

|            |                                    | edge sequence                                                                                                                                                                |               |                  |                      |                   |        |  |  |  |

| bit 3      |                                    | ve Enable bit (l                                                                                                                                                             |               | ve mode only)    |                      |                   |        |  |  |  |

|            |                                    | 1 = Enables Receive mode for I <sup>2</sup> C<br>0 = Receive Idle                                                                                                            |               |                  |                      |                   |        |  |  |  |

| bit 2      | PEN: Stop Co                       | ndition Enable                                                                                                                                                               | bit (Master m | node only)       |                      |                   |        |  |  |  |

|            | 1 = Initiate Sto                   | L = Initiate Stop condition on SDA and SCL pins. Automatically cleared by hardware.                                                                                          |               |                  |                      |                   |        |  |  |  |

|            | 0 = Stop cond                      |                                                                                                                                                                              |               |                  |                      |                   |        |  |  |  |

| bit 1      | -                                  | RSEN: Repeated Start Condition Enabled bit (Master mode only)                                                                                                                |               |                  |                      |                   |        |  |  |  |

|            |                                    | <ul> <li>1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = Repeated Start condition Idle</li> </ul>                 |               |                  |                      |                   |        |  |  |  |

| bit 0      | •                                  | SEN: Start Condition Enabled/Stretch Enabled bit                                                                                                                             |               |                  |                      |                   |        |  |  |  |

|            | In Master mod                      |                                                                                                                                                                              |               |                  |                      |                   |        |  |  |  |

|            | 1 = Initiate Sta<br>0 = Start cond |                                                                                                                                                                              | SDA and SC    | L pins. Autom    | atically cleared     | by hardware.      |        |  |  |  |

|            | In Slave mode                      |                                                                                                                                                                              |               |                  |                      |                   |        |  |  |  |

|            | 1 = Clock stre                     | tching is enabl                                                                                                                                                              |               | lave Transmit    | and Slave Reco       | eive (stretch ena | abled) |  |  |  |

|            | 0 = Clock stre                     | tching is disab                                                                                                                                                              | led           |                  |                      |                   |        |  |  |  |

## REGISTER 17-5: SSPCON2: MSSP CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE)

Note 1: Value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

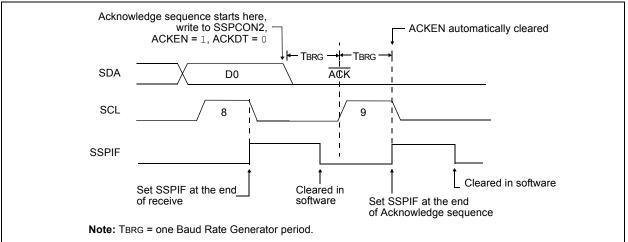

## 17.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 17-23).

#### 17.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

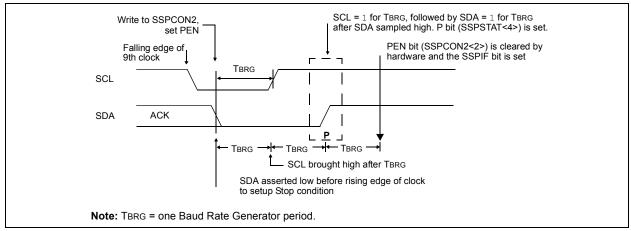

### 17.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 17-24).

#### 17.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 17-23: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 17-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

## 18.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules available in the PIC18F2X20/4X20 family of microcontrollers. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The USART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

The RC6/TX/CK and RC7/RX/DT pins must be configured as shown for use with the Universal Synchronous Asynchronous Receiver Transmitter:

- SPEN (RCSTA<7>) bit must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be cleared (= 0)

Register 18-1 shows the Transmit Status and Control register (TXSTA) and Register 18-2 shows the Receive Status and Control register (RCSTA).

## 18.1 Asynchronous Operation in Power-Managed Modes

The USART may operate in Asynchronous mode while the peripheral clocks are being provided by the internal oscillator block. This mode makes it possible to remove the crystal or resonator that is commonly connected as the primary clock on the OSC1 and OSC2 pins.

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz. However, this frequency may drift as VDD or temperature changes and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output back to 8 MHz. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source (see **Section 3.6 "INTOSC Frequency Drift**" for more information).

The other method adjusts the value in the Baud Rate Generator since there may be not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

| BTFSC                                                                  | Bit Test Fi                                                                                                                                                                                                                                                                                                                                                                                                                                                 | le, Skip if Cle                            | ear             | BTF       | SS                                                                                                                                                                   | Bit Test Fi                                                                                                                                                                                           | le, Skip if Se                                                                                                                            | t               |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Syntax:                                                                | [label] B1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FSC f,b[,a]                                |                 | Synt      | ax:                                                                                                                                                                  | [ <i>label</i> ] BT                                                                                                                                                                                   | FSS f,b[,a]                                                                                                                               |                 |

| Operands:                                                              | 0 ≤ f ≤ 255<br>0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |                 | Ope       | ands:                                                                                                                                                                | 0 ≤ f ≤ 255<br>0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                 |                                                                                                                                           |                 |

| Operation:                                                             | skip if (f <b< td=""><td>&gt;<b>) =</b> 0</td><td></td><td>One</td><td>ration:</td><td>skip if (f<b< td=""><td><b>) =</b> 1</td><td></td></b<></td></b<>                                                                                                                                                                                                                                                                                                    | > <b>) =</b> 0                             |                 | One       | ration:                                                                                                                                                              | skip if (f <b< td=""><td><b>) =</b> 1</td><td></td></b<>                                                                                                                                              | <b>) =</b> 1                                                                                                                              |                 |

| Status Affected:                                                       | None                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ) = 0                                      |                 | •         | is Affected:                                                                                                                                                         | None                                                                                                                                                                                                  | ) – 1                                                                                                                                     |                 |

| Encoding:                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | hhha ff                                    | ee eeee         |           | oding:                                                                                                                                                               | 1010                                                                                                                                                                                                  | bbba ffi                                                                                                                                  | ff ffff         |

| Description:                                                           | 1011bbbaffffffffIf bit 'b' in register 'f' is '0', then the<br>next instruction is skipped.If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded<br>and a NOP is executed instead, mak-<br>ing this a two-cycle instruction. If 'a'<br>is '0', the Access Bank will be<br>selected, overriding the BSR value. If<br>'a' = 1, then the bank will be selected<br>as per the BSR value (default). |                                            |                 | pription: | If bit 'b' in r<br>next instruct<br>If bit 'b' is '2<br>tion fetcheor<br>instruction<br>and a NOP<br>ing this a tw<br>is '0', the A<br>selected, or<br>'a' = 1, ther | egister 'f' is '1<br>ction is skippe<br>1', then the ne<br>d during the c<br>execution is c<br>is executed ir<br>vo-cycle instr<br>ccess Bank v<br>verriding the B<br>n the bank will<br>BSR value (d | L', then the<br>ed.<br>ext instruc-<br>urrent<br>discarded<br>nstead, mak-<br>uction. If 'a'<br>vill be<br>BSR value. If<br>I be selected |                 |

| Words:                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                            |                 | Word      | ds:                                                                                                                                                                  | 1                                                                                                                                                                                                     |                                                                                                                                           |                 |

| Cycles:                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ycles if skip a<br>a 2-word inst           |                 | Cycl      | es:                                                                                                                                                                  |                                                                                                                                                                                                       | cycles if skip a<br>a 2-word inst                                                                                                         |                 |

| Q Cycle Activity                                                       | :                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                            |                 | QC        | ycle Activity:                                                                                                                                                       |                                                                                                                                                                                                       |                                                                                                                                           |                 |

| Q1                                                                     | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q3                                         | Q4              |           | Q1                                                                                                                                                                   | Q2                                                                                                                                                                                                    | Q3                                                                                                                                        | Q4              |

| Decode                                                                 | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                        | Process Data                               | No<br>operation |           | Decode                                                                                                                                                               | Read<br>register 'f'                                                                                                                                                                                  | Process Data                                                                                                                              | No<br>operation |

| lf skip:                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |                 | lf sk     | •                                                                                                                                                                    |                                                                                                                                                                                                       |                                                                                                                                           |                 |

| Q1                                                                     | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q3                                         | Q4              |           | Q1                                                                                                                                                                   | Q2                                                                                                                                                                                                    | Q3                                                                                                                                        | Q4              |

| No<br>operation                                                        | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                             | No<br>operation                            | No<br>operation |           | No<br>operation                                                                                                                                                      | No<br>operation                                                                                                                                                                                       | No<br>operation                                                                                                                           | No<br>operation |

| If skip and follow                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |                 | lf sk     |                                                                                                                                                                      | ed by 2-word                                                                                                                                                                                          |                                                                                                                                           |                 |

| Q1                                                                     | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q3                                         | Q4              |           | Q1                                                                                                                                                                   | Q2                                                                                                                                                                                                    | Q3                                                                                                                                        | Q4              |

| No<br>operation                                                        | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                             | No<br>operation                            | No<br>operation |           | No<br>operation                                                                                                                                                      | No<br>operation                                                                                                                                                                                       | No<br>operation                                                                                                                           | No<br>operation |

| No<br>operation                                                        | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                             | No<br>operation                            | No<br>operation |           | No<br>operation                                                                                                                                                      | No<br>operation                                                                                                                                                                                       | No<br>operation                                                                                                                           | No<br>operation |

| Example:                                                               | HERE B'<br>FALSE :<br>TRUE :                                                                                                                                                                                                                                                                                                                                                                                                                                | FFSC FLAG                                  | , 1             | Exar      | nple:                                                                                                                                                                | HERE BI<br>FALSE :<br>TRUE :                                                                                                                                                                          | TFSS FLAG                                                                                                                                 | , 1             |

| Before Instru<br>PC<br>After Instruc<br>If FLAG<br>PC<br>If FLAG<br>PC | uction<br>= add<br>tion<br><1> = 0;<br>= add<br><1> = 1;                                                                                                                                                                                                                                                                                                                                                                                                    | ress (HERE)<br>ress (TRUE)<br>ress (FALSE) |                 |           | Before Instru<br>PC<br>After Instruct<br>If FLAG<<br>PC<br>If FLAG<<br>PC                                                                                            | ction<br>= add<br>ion<br>1> = 0;<br>= add<br>1> = 1;                                                                                                                                                  | ress (HERE)<br>ress (FALSE)<br>ress (TRUE)                                                                                                |                 |

| GOT   | GOTO Unconditional Branch                                                                                                                                                                        |                      |                             |                          |                                                 |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|--------------------------|-------------------------------------------------|--|--|--|

| Synt  | ax:                                                                                                                                                                                              | [ label ]            | GOTO                        | k                        |                                                 |  |  |  |

| Ope   | rands:                                                                                                                                                                                           | $0 \le k \le 10$     | $0 \leq k \leq 1048575$     |                          |                                                 |  |  |  |

| Ope   | ration:                                                                                                                                                                                          | $k \rightarrow PC<2$ | 20:1>                       |                          |                                                 |  |  |  |