Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4320-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| R/W-1         | R/W-1                                                                                                         | U-0                                                      | R/W-0           | R/W-0          | U-0             | R/W-0              | R/W-0         |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------|----------------|-----------------|--------------------|---------------|--|--|--|--|--|

| INT2IP        | INT1IP                                                                                                        | —                                                        | INT2IE          | INT1IE         |                 | INT2IF             | INT1IF        |  |  |  |  |  |

| bit 7         |                                                                                                               |                                                          |                 |                |                 |                    | bit (         |  |  |  |  |  |

|               |                                                                                                               |                                                          |                 |                |                 |                    |               |  |  |  |  |  |

| Legend:       |                                                                                                               |                                                          |                 |                |                 |                    |               |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                         | W = Writable                                             | bit             | •              | mented bit, rea | id as '0'          |               |  |  |  |  |  |

| -n = Value at | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk                                        |                                                          |                 |                |                 |                    | nown          |  |  |  |  |  |

| bit 7         |                                                                                                               | External Interr                                          | unt Driarity hi |                |                 |                    |               |  |  |  |  |  |

|               | 1 = High prio                                                                                                 | External Interro                                         | upt Phonity bi  | L              |                 |                    |               |  |  |  |  |  |

|               | 0 = Low prior                                                                                                 | -                                                        |                 |                |                 |                    |               |  |  |  |  |  |

| bit 6         | •                                                                                                             | External Interro                                         | upt Priority bi | t              |                 |                    |               |  |  |  |  |  |

|               | 1 = High prio                                                                                                 | ority                                                    |                 |                |                 |                    |               |  |  |  |  |  |

|               | 0 = Low prior                                                                                                 | rity                                                     |                 |                |                 |                    |               |  |  |  |  |  |

| bit 5         | Unimplemen                                                                                                    | ted: Read as '                                           | )'              |                |                 |                    |               |  |  |  |  |  |

| bit 4         | INT2IE: INT2                                                                                                  | External Interre                                         | upt Enable bi   | t              |                 |                    |               |  |  |  |  |  |

|               |                                                                                                               | the INT2 extern                                          |                 |                |                 |                    |               |  |  |  |  |  |

|               |                                                                                                               | <ul> <li>Disables the INT2 external interrupt</li> </ul> |                 |                |                 |                    |               |  |  |  |  |  |

| bit 3         |                                                                                                               | INT1IE: INT1 External Interrupt Enable bit               |                 |                |                 |                    |               |  |  |  |  |  |

|               | <ul> <li>1 = Enables the INT1 external interrupt</li> <li>0 = Disables the INT1 external interrupt</li> </ul> |                                                          |                 |                |                 |                    |               |  |  |  |  |  |

| bit 2         |                                                                                                               | ted: Read as '                                           | •               |                |                 |                    |               |  |  |  |  |  |

| bit 1         | -                                                                                                             | External Interro                                         |                 |                |                 |                    |               |  |  |  |  |  |

|               |                                                                                                               | 2 external interr                                        |                 | (must be clear | ed in software  | N N                |               |  |  |  |  |  |

|               |                                                                                                               | 2 external interr                                        |                 |                |                 | /                  |               |  |  |  |  |  |

| bit 0         |                                                                                                               | External Interro                                         |                 |                |                 |                    |               |  |  |  |  |  |

|               |                                                                                                               | 1 external interr                                        |                 | (must be clear | ed in software  | )                  |               |  |  |  |  |  |

|               | 0 = The INT1                                                                                                  | 1 external interr                                        | upt did not oo  | cur            |                 |                    |               |  |  |  |  |  |

|               |                                                                                                               |                                                          |                 |                |                 |                    |               |  |  |  |  |  |

| Note: In      | terrupt flag bits                                                                                             | are set when a                                           | n interrunt co  | ndition occurs | regardless of   | the state of its ( | corresponding |  |  |  |  |  |

|               | hable bit or the g                                                                                            |                                                          |                 |                |                 |                    |               |  |  |  |  |  |

prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3

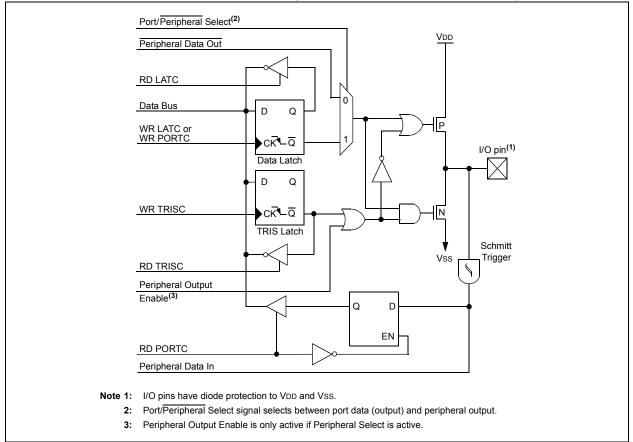

### 10.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-5). The pins have Schmitt Trigger input buffers. RC1 is normally configured by Configuration bit, CCP2MX (CONFIG3H<0>), as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

# Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents even though a peripheral device may be overriding one or more of the pins.

#### EXAMPLE 10-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | OxCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs |

|       |       | ; RC<5:4> as outputs    |

|       |       | ; RC<7:6> as inputs     |

|       |       |                         |

### FIGURE 10-10: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

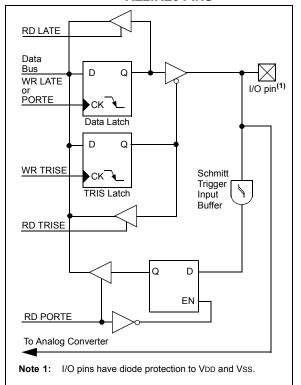

### 10.5 PORTE, TRISE and LATE Registers

PORTE is available only in PIC18F4X20 devices. PIC18F2X20 devices always will read back 0x00 from PORTE.

For PIC18F4X20 devices, PORTE is a <u>4-bit wide port.</u> Three pins (RE0/AN5/RD, RE1/AN6/WR and RE2/ AN7/CS) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On a   | Power-on                     | Reset, | RE2:RE0 | are |  |  |  |  |  |  |  |

|-------|--------|------------------------------|--------|---------|-----|--|--|--|--|--|--|--|

|       | config | configured as analog inputs. |        |         |     |  |  |  |  |  |  |  |

The upper four bits of the TRISE register also control the operation of the Parallel Slave Port. Their operation is explained in Register 10-1.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

The fourth pin of PORTE (MCLR/VPP/RE3) is an input only pin. Its operation is controlled by the MCLRE Configuration bit in Configuration Register 3H (CONFIG3H<7>). When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RE3 is enabled as |  |  |  |  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|       | a digital input only if Master Clear   |  |  |  |  |  |  |  |  |  |  |  |

|       | functionality is disabled.             |  |  |  |  |  |  |  |  |  |  |  |

### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE  |   | Initialize PORTE by clearing output |

|-------|--------|---|-------------------------------------|

|       |        | ; | data latches                        |

| CLRF  | LATE   | ; | Alternate method                    |

|       |        | ; | to clear output                     |

|       |        | ; | data latches                        |

| MOVLW | 0x0A   | ; | Configure A/D                       |

| MOVWF | ADCON1 | ; | for digital inputs                  |

| MOVLW | 0x03   | ; | Value used to                       |

|       |        | ; | initialize data                     |

|       |        | ; | direction                           |

| MOVWF | TRISC  | ; | Set RE <o> as inputs</o>            |

|       |        | ; | RE<1> as outputs                    |

|       |        | ; | RE<2> as inputs                     |

|       |        |   |                                     |

FIGURE 10-13:

BLOCK DIAGRAM OF RE2:RE0 PINS

## 15.0 CAPTURE/COMPARE/PWM (CCP) MODULES

The standard CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. Table 15-1 shows the timer resources required for each of the CCP module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the Special Event Trigger. Therefore, operation of a CCP module is described with respect to CCP1 except where noted. Table 15-2 shows the interaction of the CCP modules. Note: In 28-pin devices, both CCP1 and CCP2 function as standard CCP modules. In 40-pin devices, CCP1 is implemented as an Enhanced CCP module, offering additional capabilities in PWM mode. Capture and Compare modes are identical in all modules regardless of the device.

> Please see Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module" for a discussion of the enhanced PWM capabilities of the CCP1 module.

### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

| U-0          | U-0                                  | R/W-0                                                                                                                                       | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0          |  |  |  |  |  |  |

|--------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|----------------|--|--|--|--|--|--|

| _            | _                                    | DCxB1                                                                                                                                       | DCxB0          | CCPxM3           | CCPxM2          | CCPxM1          | CCPxM0         |  |  |  |  |  |  |

| bit 7        |                                      |                                                                                                                                             |                |                  |                 |                 | bit 0          |  |  |  |  |  |  |

| Legend:      |                                      |                                                                                                                                             |                |                  |                 |                 |                |  |  |  |  |  |  |

| R = Readal   | ble bit                              | W = Writable                                                                                                                                | bit            | U = Unimpler     | mented bit, rea | d as '0'        |                |  |  |  |  |  |  |

| -n = Value a | at POR                               | R '1' = Bit is set '0' = Bit is cleared x = Bit is unknow                                                                                   |                |                  |                 |                 | nown           |  |  |  |  |  |  |

| bit 7-6      | Unimplemen                           | ited: Read as '                                                                                                                             | 0'             |                  |                 |                 |                |  |  |  |  |  |  |

| bit 5-4      | -                                    | B0: PWM Duty                                                                                                                                |                | nd Bit 0 for CCI | Px Module       |                 |                |  |  |  |  |  |  |

|              |                                      |                                                                                                                                             | (bit 1 and bit | 0) of the 10-bit | PWM duty cyc    | le. The eight M | Sbs of the dut |  |  |  |  |  |  |

| bit 3-0      | CCPxM3:CCPxM0: CCPx Mode Select bits |                                                                                                                                             |                |                  |                 |                 |                |  |  |  |  |  |  |

|              | 0001 = Rese                          | 0000 = Capture/Compare/PWM disabled (resets CCPx module)<br>0001 = Reserved                                                                 |                |                  |                 |                 |                |  |  |  |  |  |  |

|              | 0011 = Rese                          | 0010 = Compare mode: toggle output on match (CCPxIF bit is set)<br>0011 = Reserved                                                          |                |                  |                 |                 |                |  |  |  |  |  |  |

|              |                                      | 0100 = Capture mode: every falling edge                                                                                                     |                |                  |                 |                 |                |  |  |  |  |  |  |

|              |                                      | 0101 = Capture mode: every rising edge<br>0110 = Capture mode: every 4th rising edge                                                        |                |                  |                 |                 |                |  |  |  |  |  |  |

|              |                                      | ure mode: ever                                                                                                                              |                |                  |                 |                 |                |  |  |  |  |  |  |

|              |                                      | pare mode: init                                                                                                                             |                |                  | pare match, for | ce CCPx pin hi  | gh (CCPxIF bi  |  |  |  |  |  |  |

|              |                                      | Compare mode: initialize CCPx pin high; on compare match, force CCPx pin low<br>s set)                                                      |                |                  |                 |                 |                |  |  |  |  |  |  |

|              |                                      | 1010 = Compare mode: generate software interrupt on compare match (CCPxIF bit is set, CCPx pin operates as a port pin for input and output) |                |                  |                 |                 |                |  |  |  |  |  |  |

|              | 1011 = Com<br>11xx = PWN             | pare mode: trig<br>/ mode                                                                                                                   | ger special e  | vent (CCPxIF b   | oit is set)     |                 |                |  |  |  |  |  |  |

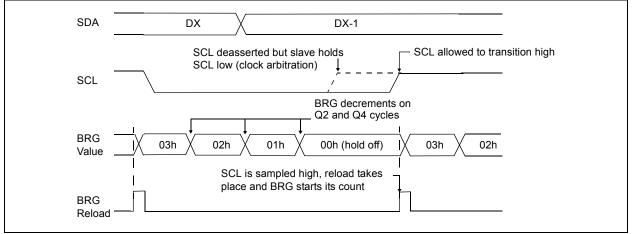

### 17.4.7.2 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 17-18).

### 17.4.14 POWER-MANAGED MODE OPERATION

While in any power-managed mode, the I<sup>2</sup>C module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

### 17.4.15 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 17.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- · An Acknowledge Condition

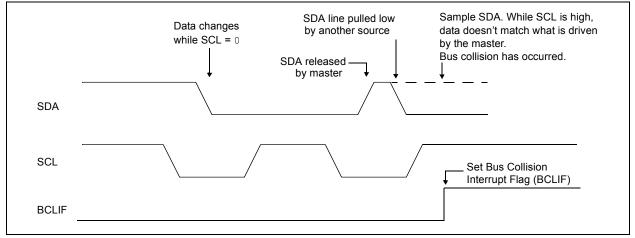

### 17.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the  $I^2C$  port to its Idle state (Figure 17-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register or the bus is Idle and the S and P bits are cleared.

### FIGURE 17-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### REGISTER 18-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0         | R/W-0                                                                  | R/W-0                                                                              | R/W-0           | R/W-0             | R-0              | R-0               | R-x     |  |  |  |  |  |

|---------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-------------------|---------|--|--|--|--|--|

| SPEN          | RX9                                                                    | SREN                                                                               | CREN            | ADDEN             | FERR             | OERR              | RX9D    |  |  |  |  |  |

| bit 7         |                                                                        | L                                                                                  |                 |                   |                  |                   | bit     |  |  |  |  |  |

|               |                                                                        |                                                                                    |                 |                   |                  |                   |         |  |  |  |  |  |

| Legend:       |                                                                        |                                                                                    |                 |                   |                  |                   |         |  |  |  |  |  |

| R = Readabl   | e bit                                                                  | W = Writable                                                                       | bit             | U = Unimplen      | nented bit, read | d as '0'          |         |  |  |  |  |  |

| -n = Value at | POR                                                                    | '1' = Bit is set                                                                   |                 | '0' = Bit is clea | ared             | x = Bit is unkr   | nown    |  |  |  |  |  |

| bit 7         | SPEN: Seria                                                            | al Port Enable bi                                                                  | t               |                   |                  |                   |         |  |  |  |  |  |

|               |                                                                        | ort enabled (con                                                                   |                 | and TX/CK pir     | ns as serial por | t pins)           |         |  |  |  |  |  |

|               | •                                                                      | ort disabled (hel                                                                  | •               | ·                 |                  | . ,               |         |  |  |  |  |  |

| bit 6         | <b>RX9:</b> 9-Bit F                                                    | Receive Enable I                                                                   | oit             |                   |                  |                   |         |  |  |  |  |  |

|               |                                                                        | 9-bit reception<br>8-bit reception                                                 |                 |                   |                  |                   |         |  |  |  |  |  |

| bit 5         | SREN: Sing                                                             | le Receive Enat                                                                    | ole bit         |                   |                  |                   |         |  |  |  |  |  |

|               | <u>Asynchrono</u><br>Don't care.                                       | <u>us mode:</u>                                                                    |                 |                   |                  |                   |         |  |  |  |  |  |

|               | 1 = Enable<br>0 = Disable                                              | <u>is mode – Maste</u><br>s single receive<br>s single receive<br>eared after rece |                 | ete               |                  |                   |         |  |  |  |  |  |

|               |                                                                        | s mode – Slave:                                                                    |                 |                   |                  |                   |         |  |  |  |  |  |

| bit 4         | CREN: Continuous Receive Enable bit                                    |                                                                                    |                 |                   |                  |                   |         |  |  |  |  |  |

|               | Asynchrono<br>1 = Enables<br>0 = Disables<br>Synchronou<br>1 = Enables | s receiver<br>s receiver                                                           | eive until enab | ble bit, CREN, is | s cleared (CRE   | N overrides SR    | EN)     |  |  |  |  |  |

|               | 0 = Disables                                                           | s continuous rec                                                                   | eive            |                   |                  |                   |         |  |  |  |  |  |

| bit 3         |                                                                        | Idress Detect En                                                                   |                 |                   |                  |                   |         |  |  |  |  |  |

|               | 1 = Enables                                                            | <u>us mode 9-bit (F</u><br>s address detect<br>s address detec                     | ion, enables i  |                   |                  |                   |         |  |  |  |  |  |

| bit 2         | FERR: Fran                                                             | ning Error bit                                                                     |                 |                   |                  |                   |         |  |  |  |  |  |

|               | 1 = Framing<br>0 = No fram                                             | ı error (can be u<br>ing error                                                     | odated by rea   | ding RCREG re     | egister and rece | eiving next valio | l byte) |  |  |  |  |  |

| bit 1         | OERR: Ove                                                              | rrun Error bit                                                                     |                 |                   |                  |                   |         |  |  |  |  |  |

|               | 1 = Overrun<br>0 = No over                                             | error (can be cl<br>run error                                                      | eared by clea   | ring bit CREN)    |                  |                   |         |  |  |  |  |  |

| bit 0         | <b>RX9D:</b> 9th b                                                     | oit of Received D                                                                  | )ata            |                   |                  |                   |         |  |  |  |  |  |

|               |                                                                        |                                                                                    |                 |                   |                  |                   |         |  |  |  |  |  |

|             |                       |            | -                           |                       |            |                             |                       |            |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 16.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     |            |                             | _                     | _          | _                           | 0.98                  | 225.52     | 255                         | 0.61                  | 103.45     | 255                         |

| 1.2         | _                     | _          | _                           | 1.22                  | 1.73       | 255                         | 1.20                  | 0.16       | 207                         | 1.20                  | 0.16       | 129                         |

| 2.4         | 2.44                  | 1.73       | 255                         | 2.40                  | 0.16       | 129                         | 2.40                  | 0.16       | 103                         | 2.40                  | 0.16       | 64                          |

| 9.6         | 9.62                  | 0.16       | 64                          | 9.47                  | -1.36      | 32                          | 9.62                  | 0.16       | 25                          | 9.77                  | 1.73       | 15                          |

| 19.2        | 18.94                 | -1.36      | 32                          | 19.53                 | 1.73       | 15                          | 19.23                 | 0.16       | 12                          | 19.53                 | 1.73       | 7                           |

| 38.4        | 39.06                 | 1.73       | 15                          | 39.06                 | 1.73       | 7                           | 35.71                 | -6.99      | 6                           | 39.06                 | 1.73       | 3                           |

| 57.6        | 56.82                 | -1.36      | 10                          | 62.50                 | 8.51       | 4                           | 62.50                 | 8.51       | 3                           | 52.08                 | -9.58      | 2                           |

| 76.8        | 78.13                 | 1.73       | 7                           | 78.13                 | 1.73       | 3                           | 83.33                 | 8.51       | 2                           | 78.13                 | 1.73       | 1                           |

| 96.0        | 89.29                 | -6.99      | 6                           | 104.17                | 8.51       | 2                           | _                     | _          | —                           | —                     | _          | —                           |

| 115.2       | 125.00                | 8.51       | 4                           | —                     | —          | —                           | 125.00                | 8.51       | 1                           | 78.13                 | -32.18     | 1                           |

| 250.0       | 208.33                | -16.67     | 2                           | —                     | —          |                             | 250.00                | 0.00       | 0                           | —                     | _          | —                           |

| 300.0       | 312.50                | 4.17       | 1                           | 312.50                | 4.17       | 0                           | —                     |            | —                           | —                     | —          | —                           |

| 625.0       | 625.00                | 0.00       | 0                           | —                     | —          | —                           | _                     |            | —                           | —                     |            | —                           |

### TABLE 18-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0, LOW SPEED)

| BAUD        | Fosc = 8.000000 MHz   |            |                             | Fosc = 7.159090 MHz   |            |                             | Fosc = 5.068800 MHz   |            |                             | Fosc = 4.000000 MHz   |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.49                  | 62.76      | 255                         | 0.44                  | 45.65      | 255                         | 0.31                  | 3.13       | 255                         | 0.30                  | 0.16       | 207                         |

| 1.2         | 1.20                  | 0.16       | 103                         | 1.20                  | 0.23       | 92                          | 1.20                  | 0.00       | 65                          | 1.20                  | 0.16       | 51                          |

| 2.4         | 2.40                  | 0.16       | 51                          | 2.38                  | -0.83      | 46                          | 2.40                  | 0.00       | 32                          | 2.40                  | 0.16       | 25                          |

| 9.6         | 9.62                  | 0.16       | 12                          | 9.32                  | -2.90      | 11                          | 9.90                  | 3.13       | 7                           | 8.93                  | -6.99      | 6                           |

| 19.2        | 17.86                 | -6.99      | 6                           | 18.64                 | -2.90      | 5                           | 19.80                 | 3.13       | 3                           | 20.83                 | 8.51       | 2                           |

| 38.4        | 41.67                 | 8.51       | 2                           | 37.29                 | -2.90      | 2                           | 39.60                 | 3.13       | 1                           | 31.25                 | -18.62     | 1                           |

| 57.6        | 62.50                 | 8.51       | 1                           | 55.93                 | -2.90      | 1                           | _                     | _          | _                           | 62.50                 | 8.51       | 0                           |

| —           | —                     | _          | —                           | —                     | _          | _                           | 79.20                 | 3.13       | 0                           | —                     | —          | —                           |

| 115.2       | 125.00                | 8.51       | 0                           | 111.86                | -2.90      | 0                           | _                     | _          | —                           | —                     | _          | —                           |

| DAUD                | Fosc = 3.579545 MHz   |            |                             | Fosc = 2.000000 MHz   |            |                             | Fosc = 1.000000 MHz   |            |                             | Fosc = 0.032768 MHz   |            |                             |

|---------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.30                  | 0.23       | 185                         | 0.30                  | 0.16       | 103                         | 0.30                  | 0.16       | 51                          | 0.26                  | -14.67     | 1                           |

| 1.2                 | 1.19                  | -0.83      | 46                          | 1.20                  | 0.16       | 25                          | 1.20                  | 0.16       | 12                          | —                     | _          | _                           |

| 2.4                 | 2.43                  | 1.32       | 22                          | 2.40                  | 0.16       | 12                          | 2.23                  | -6.99      | 6                           | —                     | _          | _                           |

| 9.6                 | 9.32                  | -2.90      | 5                           | 10.42                 | 8.51       | 2                           | 7.81                  | -18.62     | 1                           | —                     | _          | _                           |

| 19.2                | 18.64                 | -2.90      | 2                           | 15.63                 | -18.62     | 1                           | 15.63                 | -18.62     | 0                           | —                     | _          | _                           |

| 38.4                | _                     | _          | _                           | 31.25                 | -18.62     | 0                           | _                     | _          | _                           | —                     | _          | _                           |

| 57.6                | 55.93                 | -2.90      | 0                           | —                     | _          | _                           | —                     | _          | —                           | —                     | —          | _                           |

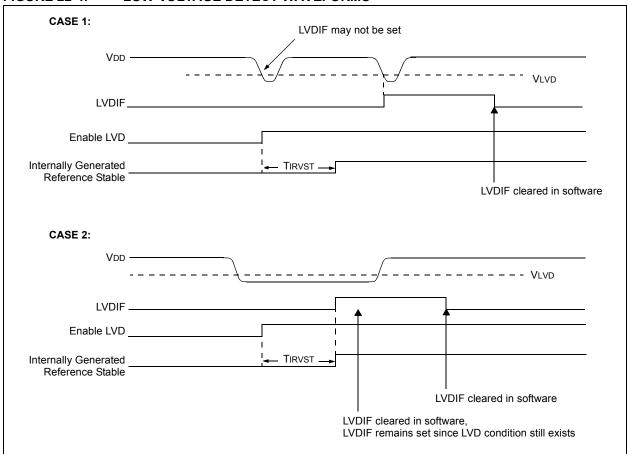

### 22.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- Write the value to the LVDL3:LVDL0 bits (LVDCON register) which selects the desired LVD trip point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- 5. Clear the LVD interrupt flag, which may have falsely become set, until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 22-4 shows typical waveforms that the LVD module may be used to detect.

### FIGURE 22-4: LOW-VOLTAGE DETECT WAVEFORMS

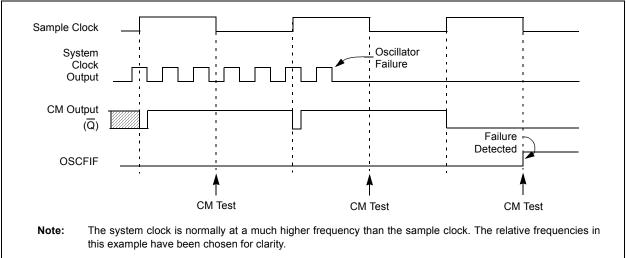

### 23.4.2 EXITING FAIL-SAFE OPERATION

The fail-safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTOSC multiplexer provides the system clock until the primary clock source becomes ready (similar to a Two-speed Start-up). The clock system source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock. The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

Entering a power-managed mode by loading the OSCCON register and executing a SLEEP instruction will clear the fail-safe condition. When the fail-safe condition is cleared, the clock monitor will resume monitoring the peripheral clock.

### FIGURE 23-4: FSCM TIMING DIAGRAM

| LFS   | R              | Load FSF                                                           | R                                 |                                         | MOVF                          | Move f                                                          |                                                     |                   |

|-------|----------------|--------------------------------------------------------------------|-----------------------------------|-----------------------------------------|-------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|-------------------|

| Synt  | ax:            | [ label ]                                                          | LFSR f,k                          |                                         | Syntax:                       | [label]                                                         | MOVF f[,c                                           | l [,a]]           |

| Ope   | rands:         | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | 95                                |                                         | Operands:                     | $\begin{array}{l} 0 \leq f \leq 258 \\ d \in [0,1] \end{array}$ | 5                                                   |                   |

| Ope   | ration:        | $k \rightarrow FSRf$                                               |                                   |                                         |                               | a ∈ [0,1]                                                       |                                                     |                   |

| Statu | us Affected:   | None                                                               |                                   |                                         | Operation:                    | $f \rightarrow dest$                                            |                                                     |                   |

| Enco  | oding:         | 1110<br>1111                                                       |                                   | )ff k <sub>11</sub> kkk<br>kkk kkkk     | Status Affected:<br>Encoding: | N, Z                                                            | 00da ff                                             | ff ffff           |

| Deso  | cription:      |                                                                    | literal 'k' is l<br>lect register |                                         | Description:                  | moved to                                                        | nts of registe<br>a destinatior<br>status of 'd'. I |                   |

| Wor   | ds:            | 2                                                                  |                                   |                                         |                               |                                                                 |                                                     | f 'd' is '1', the |

| Cycl  | es:            | 2                                                                  |                                   |                                         |                               |                                                                 | aced back ir<br>Location 'f' c                      |                   |

| QC    | ycle Activity  | :                                                                  |                                   |                                         |                               | . ,                                                             |                                                     | bank. If 'a' is   |

|       | Q1             | Q2                                                                 | Q3                                | Q4                                      |                               | •                                                               | cess Bank w                                         |                   |

|       | Decode         | Read literal<br>'k' MSB                                            | Process<br>Data                   | Write<br>literal 'k'<br>MSB to<br>FSRfH |                               | lf 'a' = 1, t                                                   | overriding the<br>hen the banl<br>is per the BS     |                   |

|       | Decode         | Read literal                                                       | Process                           | Write literal                           | Words:                        | 1                                                               |                                                     |                   |

|       |                | ʻk' LSB                                                            | Data                              | 'k' to FSRfL                            | Cycles:                       | 1                                                               |                                                     |                   |

| Exar  | nple:          | LFSR 2,                                                            | 0x3AB                             |                                         | Q Cycle Activity              | :                                                               |                                                     |                   |

|       | After Instruc  | tion                                                               |                                   |                                         | Q1                            | Q2                                                              | Q3                                                  | Q4                |

|       | FSR2H<br>FSR2L | = 0x                                                               | 03<br>AB                          |                                         | Decode                        | Read<br>register 'f'                                            | Process<br>Data                                     | Write W           |

|       |                |                                                                    |                                   |                                         | Example:                      | MOVF RI                                                         | EG, W                                               |                   |

|       |                |                                                                    |                                   |                                         | Before Instru<br>REG<br>W     |                                                                 | 22<br>FF                                            |                   |

|       |                |                                                                    |                                   |                                         | After Instruc<br>REG          | tion<br>= 0x                                                    | 22                                                  |                   |

W

=

0x22

# 25.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK™ Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART® Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

### 25.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

### 26.1 DC Characteristics: Supply Voltage PIC18F2220/2320/4220/4320 (Industrial) PIC18LF2220/2320/4220/4320 (Industrial) (Continued)

| PIC18LF2220/2320/4220/4320<br>(Industrial)          |        |                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                             |          |          |                                                                                           |

|-----------------------------------------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------|----------|-------------------------------------------------------------------------------------------|

| PIC18F2220/2320/4220/4320<br>(Industrial, Extended) |        |                         | Standard Operating Condition                                                                                                       |                             |          |          | -40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |

| Param<br>No.                                        | Symbol | Characteristic          | Min                                                                                                                                | Тур                         | Max      | Units    | Conditions                                                                                |

|                                                     | VBOR   | Brown-out Reset Voltage | — Date                                                                                                                             | codes                       | above    | 0417xx   | x                                                                                         |

| D005D                                               |        | PIC18LF2X20/4X20        | Indust                                                                                                                             | rial Low                    | Voltage  | e (-10°C | to +85°C)                                                                                 |

|                                                     |        | BORV1:BORV0 = 11        | N/A                                                                                                                                | N/A                         | N/A      | V        | Reserved                                                                                  |

|                                                     |        | BORV1:BORV0 = 10        | 2.50                                                                                                                               | 2.72                        | 2.94     | V        |                                                                                           |

|                                                     |        | BORV1:BORV0 = 01        | 3.88                                                                                                                               | 4.22                        | 4.56     | V        |                                                                                           |

|                                                     |        | BORV1:BORV0 = 00        | 4.18                                                                                                                               | 4.54                        | 4.90     | V        |                                                                                           |

| D005F                                               |        | PIC18LF2X20/4X20        | Indust                                                                                                                             | rial Low                    | Voltage  | e (-40°C | to -10°C)                                                                                 |

|                                                     |        | BORV1:BORV0 = 11        | N/A                                                                                                                                | N/A                         | N/A      | V        | Reserved                                                                                  |

|                                                     |        | BORV1:BORV0 = 10        | 2.34                                                                                                                               | 2.72                        | 3.10     | V        |                                                                                           |

|                                                     |        | BORV1:BORV0 = 01        | 3.63                                                                                                                               | 4.22                        | 4.81     | V        |                                                                                           |

|                                                     |        | BORV1:BORV0 = 00        | 3.90                                                                                                                               | 4.54                        | 5.18     | V        |                                                                                           |

| D005G                                               |        | PIC18F2X20/4X20         | Indust                                                                                                                             | rial (-10°                  | C to +8  | 85°C)    |                                                                                           |

|                                                     |        | BORV1:BORV0 = 1x        | N/A                                                                                                                                | N/A                         | N/A      | V        | Reserved                                                                                  |

|                                                     |        | BORV1:BORV0 = 01        | 3.88                                                                                                                               | 4.22                        | 4.56     | V        | (Note 2)                                                                                  |

|                                                     |        | BORV1:BORV0 = 00        | 4.18                                                                                                                               | 4.54                        | 4.90     | V        | (Note 2)                                                                                  |

| D005H                                               |        | PIC18F2X20/4X20         | Indust                                                                                                                             | Industrial (-40°C to -10°C) |          |          |                                                                                           |

|                                                     |        | BORV1:BORV0 = 1x        | N/A                                                                                                                                | N/A                         | N/A      | V        | Reserved                                                                                  |

|                                                     |        | BORV1:BORV0 = 01        | N/A                                                                                                                                | N/A                         | N/A      | V        | Reserved                                                                                  |

|                                                     |        | BORV1:BORV0 = 00        | 3.90                                                                                                                               | 4.54                        | 5.18     | V        | (Note 2)                                                                                  |

| D005J                                               |        | PIC18F2X20/4X20         | Extended (-10°C to +85°C)                                                                                                          |                             |          |          |                                                                                           |

|                                                     |        | BORV1:BORV0 = 1x        | N/A                                                                                                                                | N/A                         | N/A      | V        | Reserved                                                                                  |

|                                                     |        | BORV1:BORV0 = 01        | 3.88                                                                                                                               | 4.22                        | 4.56     | V        | (Note 2)                                                                                  |

|                                                     |        | BORV1:BORV0 = 00        | 4.18                                                                                                                               | 4.54                        | 4.90     | V        | (Note 2)                                                                                  |

| D005K                                               |        | PIC18F2X20/4X20         | Extend                                                                                                                             | ded (-40°                   | °C to -1 | 0°C, +8  | 5°C to +125°C)                                                                            |

|                                                     |        | BORV1:BORV0 = 1x        | N/A                                                                                                                                | N/A                         | N/A      | V        | Reserved                                                                                  |

|                                                     |        | BORV1:BORV0 = 01        | N/A                                                                                                                                | N/A                         | N/A      | V        | Reserved                                                                                  |

|                                                     |        | BORV1:BORV0 = 00        | 3.90                                                                                                                               | 4.54                        | 5.18     | V        | (Note 2)                                                                                  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

2: When BOR is on and BORV<1:0> = 0x, the device will operate correctly at 40 MHz for any VDD at which the BOR allows execution.

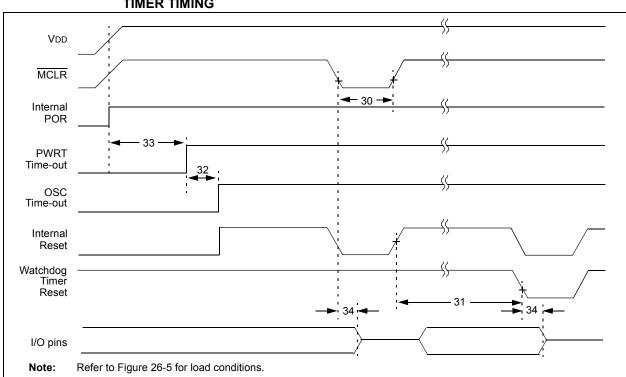

# FIGURE 26-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

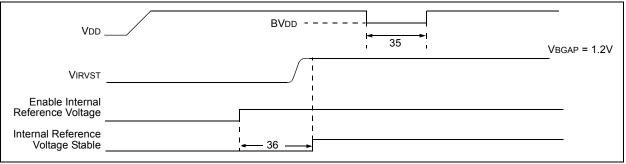

### FIGURE 26-9: BROWN-OUT RESET TIMING

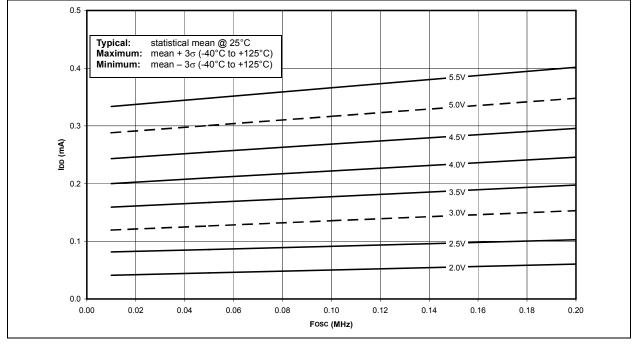

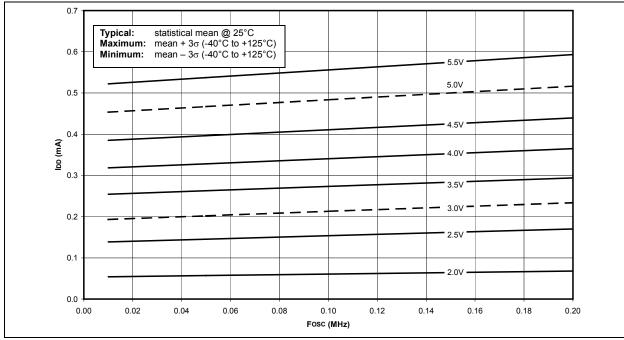

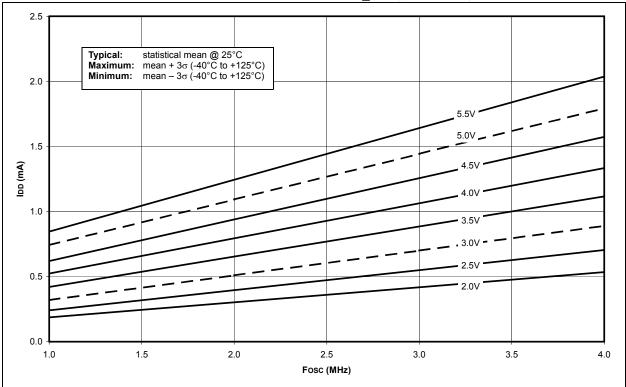

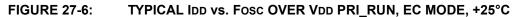

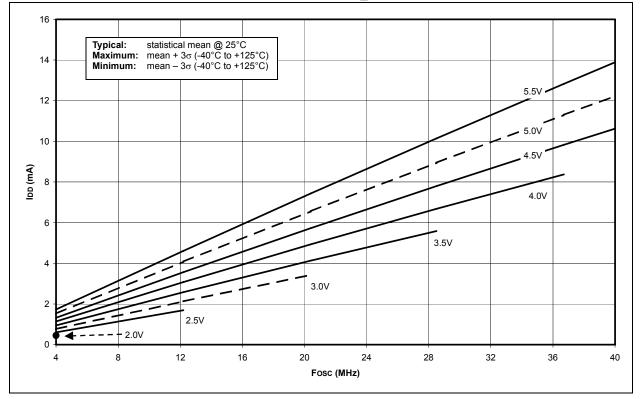

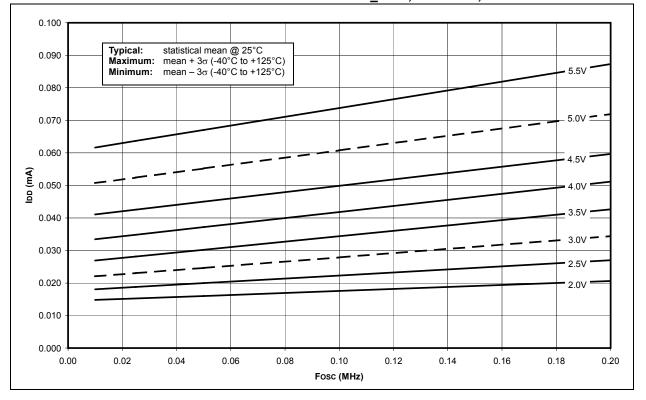

# 27.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

# PORTD

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| LATD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |

| Parallel Slave Port (PSP) Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                               |

| PORTD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                               |

| TRISD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                               |

| PORTE<br>Analog Port Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 110                                                                                                           |