Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

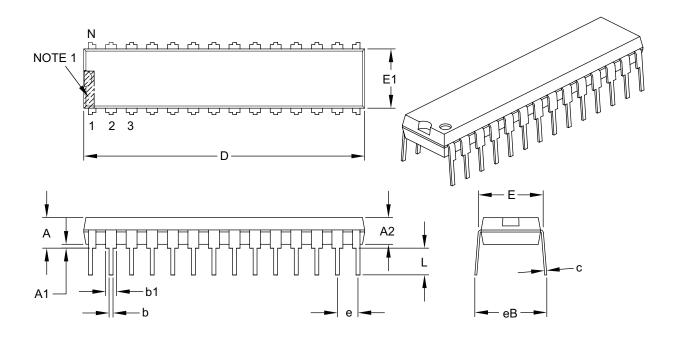

| Mounting Type              | Surface Mount                                                              |

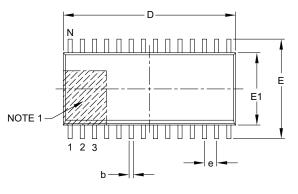

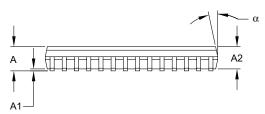

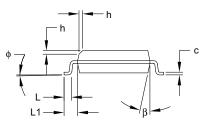

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4320-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

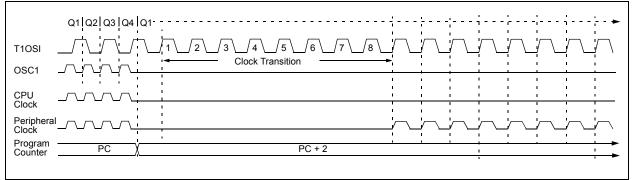

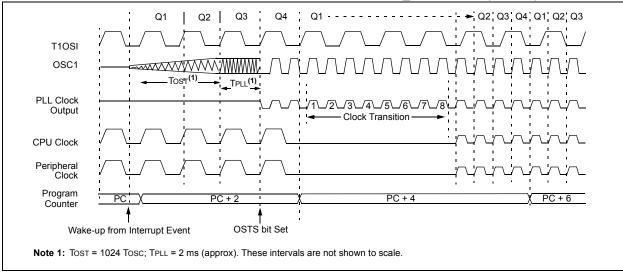

# 3.3.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered by setting the IDLEN bit, modifying to SCS1:SCS0 = 01 and executing a SLEEP instruction. When the clock source is switched to the Timer1 oscillator (see Figure 3-5), the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when trying to set the SCS0 bit (OSCCON<0>), the write to SCS0 will not occur. If the Timer1 oscillator is enabled but not yet running, peripheral clocks will be delayed until the oscillator has started; in such situations, initial oscillator operation is far from stable and unpredictable operation may result. When a wake-up event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After a 10  $\mu$ s delay following the wake-up event, the CPU begins executing code, being clocked by the Timer1 oscillator. The microcontroller operates in SEC\_RUN mode until the primary clock becomes ready. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 3-6). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

# FIGURE 3-5: TIMING TRANSITION FOR ENTRY TO SEC\_IDLE MODE

### FIGURE 3-6: TIMING TRANSITION FOR WAKE FROM SEC\_RUN MODE (HSPLL)

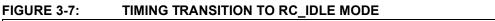

# 3.3.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

This mode is entered by setting the IDLEN bit, setting SCS1 (SCS0 is ignored) and executing a SLEEP instruction. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer (see Figure 3-7), the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to a non-zero value (thus enabling the INTOSC output), the IOFS bit becomes set after the INTOSC output becomes stable, in about 1 ms. Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source.

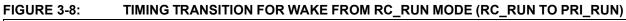

When a wake-up event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a 10  $\mu$ s delay following the wake-up event, the CPU begins executing code, being clocked by the INTOSC multiplexer. The microcontroller operates in RC\_RUN mode until the primary clock becomes ready. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 3-8). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

| Q1 Q2 Q3 Q4          | Q1               |

|----------------------|------------------|

| INTRC                |                  |

|                      | Clock Transition |

|                      |                  |

| Peripheral           |                  |

| Program<br>CounterPC | PC + 2           |

#### 3.4.3 RC\_RUN MODE

In RC RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer and the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications which are not highly timing sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either of the INTIO1 or INTIO2 oscillators), there are no distinguishable differences between PRI RUN and RC RUN modes during execution. However, a clock switch delay will occur during entry to, and exit from, RC RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC RUN mode is not recommended.

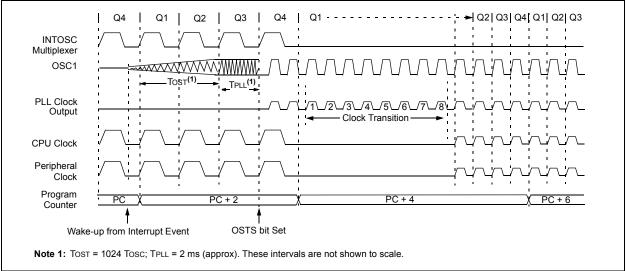

This mode is entered by clearing the IDLEN bit, setting SCS1 (SCS0 is ignored) and executing a SLEEP instruction. The IRCF bits may select the clock frequency before the **SLEEP** instruction is executed. When the clock source is switched to the INTOSC multiplexer (see Figure 3-10), the primary oscillator is shut down and the OSTS bit is cleared.

The IRCF bits may be modified at any time to immediately change the system clock speed. Executing a SLEEP instruction is not required to select a new clock frequency from the INTOSC multiplexer.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

If the IRCF bits are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear: there will be no indication of the current clock source. The INTRC source is providing the system clocks.

If the IRCF bits are changed from all clear (thus enabling the INTOSC output), the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the system continue while the INTOSC source stabilizes in approximately 1 ms.

If the IRCF bits were previously at a non-zero value before the **SLEEP** instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set.

When a wake-up event occurs, the system continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 3-8). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

#### **FIGURE 3-10:** TIMING TRANSITION TO RC\_RUN MODE

| File Name            | Bit 7                  | Bit 6                                               | Bit 5          | Bit 4                | Bit 3              | Bit 2                     | Bit 1          | Bit 0  | Value on<br>POR, BOR | Details on<br>page: |  |

|----------------------|------------------------|-----------------------------------------------------|----------------|----------------------|--------------------|---------------------------|----------------|--------|----------------------|---------------------|--|

| EEADR                | EEPROM Ad              | Idress Registe                                      | er             |                      |                    |                           |                |        | 0000 0000            | 48, 81              |  |

| EEDATA               | EEPROM Da              | 0000 0000                                           | 48, 84         |                      |                    |                           |                |        |                      |                     |  |

| EECON2               | EEPROM Co              | EEPROM Control Register 2 (not a physical register) |                |                      |                    |                           |                |        |                      |                     |  |

| EECON1               | EEPGD                  | CFGS                                                | —              | FREE                 | WRERR              | WREN                      | WR             | RD     | xx-0 x000            | 48, 73, 82          |  |

| IPR2                 | OSCFIP                 | CMIP                                                | —              | EEIP                 | BCLIP              | LVDIP                     | TMR3IP         | CCP2IP | 11-1 1111            | 49, 97              |  |

| PIR2                 | OSCFIF                 | CMIF                                                | _              | EEIF                 | BCLIF              | LVDIF                     | TMR3IF         | CCP2IF | 00-0 0000            | 49, 93              |  |

| PIE2                 | OSCFIE                 | CMIE                                                | _              | EEIE                 | BCLIE              | LVDIE                     | TMR3IE         | CCP2IE | 00-0 0000            | 49, 95              |  |

| IPR1                 | PSPIP <sup>(5)</sup>   | ADIP                                                | RCIP           | TXIP                 | SSPIP              | CCP1IP                    | TMR2IP         | TMR1IP | 1111 1111            | 49, 96              |  |

| PIR1                 | PSPIF <sup>(5)</sup>   | ADIF                                                | RCIF           | TXIF                 | SSPIF              | CCP1IF                    | TMR2IF         | TMR1IF | 0000 0000            | 49, 92              |  |

| PIE1                 | PSPIE <sup>(5)</sup>   | ADIE                                                | RCIE           | TXIE                 | SSPIE              | CCP1IE                    | TMR2IE         | TMR1IE | 0000 0000            | 49, 94              |  |

| OSCTUNE              | —                      | _                                                   | TUN5           | TUN4                 | TUN3               | TUN2                      | TUN1           | TUN0   | 00 0000              | 23, 49              |  |

| TRISE <sup>(5)</sup> | IBF                    | OBF                                                 | IBOV           | PSPMODE              | _                  | Data Directio             | n bits for POF | RTE    | 0000 -111            | 49, 112             |  |

| TRISD <sup>(5)</sup> | Data Directio          | n Control Reg                                       | gister for POR | RTD                  |                    |                           |                |        | 1111 1111            | 49, 110             |  |

| TRISC                | Data Directio          | n Control Reg                                       | gister for POR | RTC                  |                    |                           |                |        | 1111 1111            | 49, 108             |  |

| TRISB                | Data Directio          | n Control Reg                                       | gister for POR | RTB                  |                    |                           |                |        | 1111 1111            | 49, 106             |  |

| TRISA                | TRISA7 <sup>(2)</sup>  | TRISA6 <sup>(1)</sup>                               | Data Directio  | on Control Reg       | ister for POR      | TA                        |                |        | 1111 1111            | 49, 103             |  |

| LATE <sup>(5)</sup>  | —                      | _                                                   | _              | —                    | —                  | Read/Write F              | PORTE Data L   | atch   | xxx                  | 49, 113             |  |

| LATD <sup>(5)</sup>  | Read/Write F           | PORTD Data I                                        | atch           |                      |                    |                           |                |        | XXXX XXXX            | 49, 110             |  |

| LATC                 | Read/Write F           | PORTC Data I                                        | atch           |                      |                    |                           |                |        | XXXX XXXX            | 49, 108             |  |

| LATB                 | Read/Write F           | PORTB Data L                                        | atch           |                      |                    |                           |                |        | XXXX XXXX            | 49, 106             |  |

| LATA                 | LATA<7> <sup>(2)</sup> | LATA<6>(1)                                          | Read/Write I   | PORTA Data L         | atch               |                           |                |        | XXXX XXXX            | 49, 103             |  |

| PORTE <sup>(5)</sup> | _                      | _                                                   | _              | —                    | RE3 <sup>(6)</sup> | Read PORTE<br>Write PORTE |                |        | дххх                 | 49, 113             |  |

| PORTD <sup>(5)</sup> | Read PORT              | D pins, Write I                                     | PORTD Data     | Latch                |                    | •                         |                |        | XXXX XXXX            | 49, 110             |  |

| PORTC                | Read PORT              | C pins, Write I                                     | PORTC Data     | Latch                |                    |                           |                |        | XXXX XXXX            | 49, 108             |  |

| PORTB                | Read PORTE             | B pins, Write F                                     | PORTB Data     | Latch <sup>(4)</sup> |                    |                           |                |        | XXXX XXXX            | 49, 106             |  |

| PORTA                | RA7 <sup>(2)</sup>     | RA6 <sup>(1)</sup>                                  | Read PORT      | A pins, Write F      | ORTA Data I        | _atch                     |                |        | xx0x 0000            | 49, 103             |  |

### TABLE 5-2:REGISTER FILE SUMMARY (PIC18F2220/2320/4220/4320) (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO, ECIO and INTIO2 (with port function on RA6) Oscillator mode only and read as '0' in all other oscillator modes.

2: RA7 and associated bits are configured as port pins in INTIO2 Oscillator mode only and read as '0' in all other modes.

3: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

4: If PBADEN = 0, PORTB<4:0> are configured as digital inputs and read unknown and if PBADEN = 1, PORTB<4:0> are configured as analog inputs and read as '0' following a Reset.

5: These registers and/or bits are not implemented on the PIC18F2X20 devices and read as 0x00.

6: The RE3 port bit is available as an input only pin only in 40-pin devices when Master Clear functionality is disabled (CONFIG3H<7> = 0).

# 9.0 INTERRUPTS

The PIC18F2320/4320 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 000008h and the low-priority interrupt vector is at 000018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority (most interrupt sources have priority bits)

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

## 17.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### REGISTER 17-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/Ā | Р   | S   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:    |                                             |                                                                                         |                       |                    |

|------------|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------|--------------------|

| R = Reada  | able bit                                    | W = Writable bit                                                                        | U = Unimplemented bit | , read as '0'      |

| -n = Value | at POR                                      | '1' = Bit is set                                                                        | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7      | <b>SMP</b> : Sa<br><u>SPI Mast</u>          | er mode:                                                                                |                       |                    |

|            | 0 = Input                                   | data sampled at end of dat<br>data sampled at middle of                                 |                       |                    |

|            | <u>SPI Slave</u><br>SMP mus                 | <u>e mode:</u><br>st be cleared when SPI is u                                           | sed in Slave mode.    |                    |

| bit 6      | CKE: SP                                     | I Clock Edge Select bit                                                                 |                       |                    |

|            |                                             | <u>(P = 0:</u><br>transmitted on rising edge of<br>transmitted on falling edge          |                       |                    |

|            |                                             | <u>⟨P = 1:</u><br>transmitted on falling edge<br>transmitted on rising edge o           |                       |                    |

| bit 5      |                                             | a/Address bit<br><sup>2</sup> C mode only.                                              |                       |                    |

| bit 4      | <b>P:</b> Stop b<br>Used in I <sup>2</sup>  | it<br><sup>2</sup> C mode only.                                                         |                       |                    |

| bit 3      | <b>S:</b> Start b<br>Used in I <sup>2</sup> | it<br><sup>2</sup> C mode only.                                                         |                       |                    |

| bit 2      | <b>R/W</b> : Rea                            | ad/Write Information bit <sup>2</sup> C mode only.                                      |                       |                    |

| bit 1      |                                             | ate Address bit<br><sup>2</sup> C mode only.                                            |                       |                    |

| bit 0      | 1 = Rece                                    | er Full Status bit (Receive m<br>ive complete, SSPBUF is fu<br>ive not complete, SSPBUF | ull                   |                    |

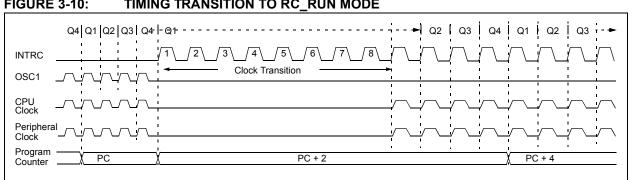

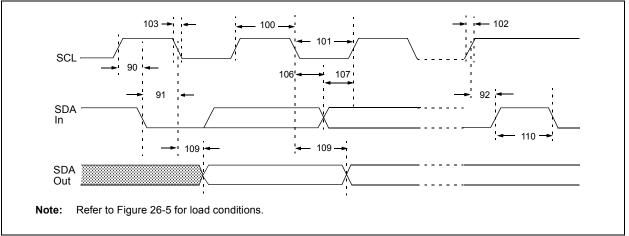

### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  ${\rm I}^2{\rm C}$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt if enabled):

- Start Condition

- Stop Condition

- · Data Transfer Byte Transmitted/Received

- Acknowledge Transmit

- Repeated Start

© 2007 Microchip Technology Inc.

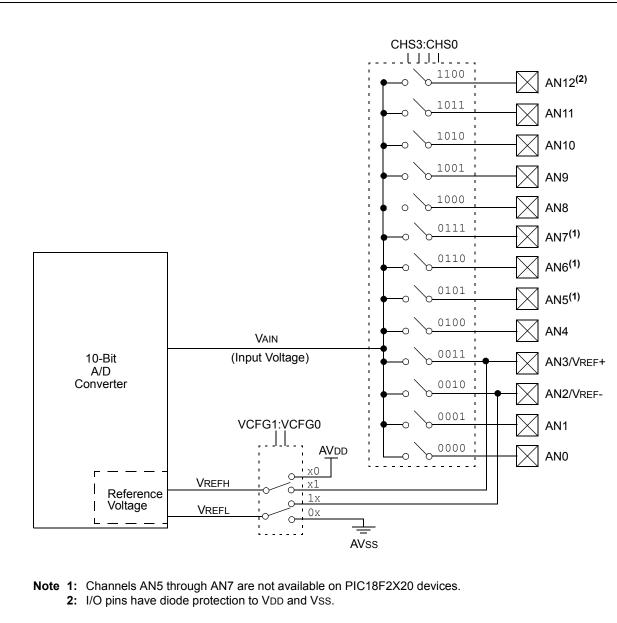

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (AVDD and AVss), or the voltage level on the RA3/AN3/ VREF+ and RA2/AN2/VREF-/CVREF pins.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter which generates the result via successive approximation.

### FIGURE 19-1: A/D BLOCK DIAGRAM

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted.

Each port pin associated with the A/D converter can be configured as an analog input or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0 register) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 19-1.

NOTES:

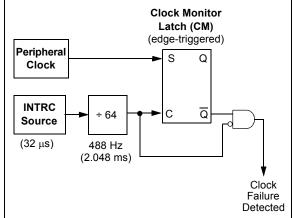

# 23.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation, in the event of an external oscillator failure, by automatically switching the system clock to the internal oscillator block. The FSCM function is enabled by setting the Fail-Safe Clock Monitor Enable bit, FCMEN (CONFIG1H<6>).

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide an instant backup clock in the event of a clock failure. Clock monitoring (shown in Figure 23-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral system clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the system clock source but cleared on the rising edge of the sample clock.

Clock failure is tested on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 23-4). This causes the following:

- The FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>)

- The system clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source this is the fail-safe condition)

- The WDT is reset

Since the postscaler frequency from the internal oscillator block may not be sufficiently stable, it may be desirable to select another clock configuration and enter an alternate power-managed mode (see Section 23.3.1 "Special Considerations for Using Two-Speed Start-up" and Section 3.1.3 "Multiple Sleep Commands" for more details). This can be done to attempt a partial recovery or execute a controlled shutdown. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits IFRC2:IFRC0 immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IFRC2:IFRC0 prior to entering Sleep mode.

Adjustments to the internal oscillator block using the OSCTUNE register also affect the period of the FSCM by the same factor. This can usually be neglected, as the clock frequency being monitored is generally much higher than the sample clock frequency.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 23.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF2:IRCF0 bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, fail-safe clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

| LFS   | R              | Load FSF                                                           | R                                 |                                         | MOVF                          | Move f                                                          |                                                     |                   |

|-------|----------------|--------------------------------------------------------------------|-----------------------------------|-----------------------------------------|-------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|-------------------|

| Synt  | ax:            | [ label ]                                                          | LFSR f,k                          |                                         | Syntax:                       | [label]                                                         | MOVF f[,c                                           | l [,a]]           |

| Ope   | rands:         | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | 95                                |                                         | Operands:                     | $\begin{array}{l} 0 \leq f \leq 258 \\ d \in [0,1] \end{array}$ | 5                                                   |                   |

| Ope   | ration:        | $k \rightarrow FSRf$                                               |                                   |                                         |                               | a ∈ [0,1]                                                       |                                                     |                   |

| Statu | us Affected:   | None                                                               |                                   |                                         | Operation:                    | $f \rightarrow dest$                                            |                                                     |                   |

| Enco  | oding:         | 1110<br>1111                                                       |                                   | )ff k <sub>11</sub> kkk<br>kkk kkkk     | Status Affected:<br>Encoding: | N, Z                                                            | 00da ff                                             | ff ffff           |

| Deso  | cription:      |                                                                    | literal 'k' is l<br>lect register |                                         | Description:                  | moved to                                                        | nts of registe<br>a destinatior<br>status of 'd'. I |                   |

| Wor   | ds:            | 2                                                                  |                                   |                                         |                               |                                                                 |                                                     | f 'd' is '1', the |

| Cycl  | es:            | 2                                                                  |                                   |                                         |                               |                                                                 | aced back ir<br>Location 'f' c                      |                   |

| QC    | ycle Activity  | :                                                                  |                                   |                                         |                               | . ,                                                             |                                                     | bank. If 'a' is   |

|       | Q1             | Q2                                                                 | Q3                                | Q4                                      |                               | •                                                               | cess Bank w                                         |                   |

|       | Decode         | Read literal<br>'k' MSB                                            | Process<br>Data                   | Write<br>literal 'k'<br>MSB to<br>FSRfH |                               | lf 'a' = 1, t                                                   | overriding the<br>hen the banl<br>is per the BS     |                   |

|       | Decode         | Read literal                                                       | Process                           | Write literal                           | Words:                        | 1                                                               |                                                     |                   |

|       |                | ʻk' LSB                                                            | Data                              | 'k' to FSRfL                            | Cycles:                       | 1                                                               |                                                     |                   |

| Exar  | nple:          | LFSR 2,                                                            | 0x3AB                             |                                         | Q Cycle Activity              | :                                                               |                                                     |                   |

|       | After Instruc  | tion                                                               |                                   |                                         | Q1                            | Q2                                                              | Q3                                                  | Q4                |

|       | FSR2H<br>FSR2L | = 0x                                                               | 03<br>AB                          |                                         | Decode                        | Read<br>register 'f'                                            | Process<br>Data                                     | Write W           |

|       |                |                                                                    |                                   |                                         | Example:                      | MOVF RI                                                         | EG, W                                               |                   |

|       |                |                                                                    |                                   |                                         | Before Instru<br>REG<br>W     |                                                                 | 22<br>FF                                            |                   |

|       |                |                                                                    |                                   |                                         | After Instruc<br>REG          | tion<br>= 0x                                                    | 22                                                  |                   |

W

=

0x22

| SUBLW Subtract W from Literal                 |                     |                  |            |  |  |  |  |  |  |

|-----------------------------------------------|---------------------|------------------|------------|--|--|--|--|--|--|

| Syntax:                                       | [label] S           | SUBLW k          |            |  |  |  |  |  |  |

| Operands: $0 \le k \le 255$                   |                     |                  |            |  |  |  |  |  |  |

| Operation:                                    | k – (W) –           | → W              |            |  |  |  |  |  |  |

| Status Affected:                              | N, OV, C,           | DC, Z            |            |  |  |  |  |  |  |

| Encoding:                                     | 0000                |                  |            |  |  |  |  |  |  |

| Description: W is subtracted from the eight-b |                     |                  |            |  |  |  |  |  |  |

| ·                                             |                     | The result is    |            |  |  |  |  |  |  |

| Words:                                        | 1                   |                  |            |  |  |  |  |  |  |

| Cycles:                                       | 1                   |                  |            |  |  |  |  |  |  |

| Q Cycle Activity:                             |                     |                  |            |  |  |  |  |  |  |

| Q1                                            | Q2                  | Q3               | Q4         |  |  |  |  |  |  |

| Decode                                        | Read<br>literal 'k' | Process<br>Data  | Write to W |  |  |  |  |  |  |

| Example 1:                                    | SUBLW (             | x02              |            |  |  |  |  |  |  |

| Before Instru                                 | iction              |                  |            |  |  |  |  |  |  |

| W                                             | = 1                 |                  |            |  |  |  |  |  |  |

| С                                             | = ?                 |                  |            |  |  |  |  |  |  |

| After Instruct                                |                     |                  |            |  |  |  |  |  |  |

| W<br>C                                        | = 1<br>= 1 :re      | sult is positive | 9          |  |  |  |  |  |  |

| C<br>Z<br>N                                   | = 0<br>= 0          |                  |            |  |  |  |  |  |  |

| Example 2:                                    | -                   | x02              |            |  |  |  |  |  |  |

| Before Instru                                 | iction              |                  |            |  |  |  |  |  |  |

| W                                             | = 2                 |                  |            |  |  |  |  |  |  |

| С                                             | = ?                 |                  |            |  |  |  |  |  |  |

| After Instruct                                | ion                 |                  |            |  |  |  |  |  |  |

| W                                             | = 0<br>= 1 ; re     | sult is zero     |            |  |  |  |  |  |  |

| Z                                             | = 1                 | Sult 15 2010     |            |  |  |  |  |  |  |

| Example 3:                                    | = 0<br>SUBLW (      | x02              |            |  |  |  |  |  |  |

| Before Instru                                 |                     | X02              |            |  |  |  |  |  |  |

| W                                             | = 3                 |                  |            |  |  |  |  |  |  |

| C                                             | = ?                 |                  |            |  |  |  |  |  |  |

| After Instruct                                | ion                 |                  |            |  |  |  |  |  |  |

| W                                             |                     | 's complemen     |            |  |  |  |  |  |  |

| C<br>Z<br>N                                   | = 0 ; re<br>= 0     | sult is negativ  | e          |  |  |  |  |  |  |

| Ν                                             | = 1                 |                  |            |  |  |  |  |  |  |

|                                               |                     |                  |            |  |  |  |  |  |  |

|                                               |                     |                  |            |  |  |  |  |  |  |

|                                               |                     |                  |            |  |  |  |  |  |  |

|                                               |                     |                  |            |  |  |  |  |  |  |

| SUBWF                                                                               | Subtract                                                                                   | W from f                                                                                                                                                                                                                                                                                                                     |                      |  |  |  |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Syntax:                                                                             | [ label ] S                                                                                | SUBWF f[,                                                                                                                                                                                                                                                                                                                    | d [,a]]              |  |  |  |

| Operands:                                                                           | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                                       | 5                                                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| Operation:                                                                          | (f) – (W)                                                                                  | $\rightarrow$ dest                                                                                                                                                                                                                                                                                                           |                      |  |  |  |

| Status Affected:                                                                    | N, OV, C                                                                                   | , DC, Z                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Encoding:                                                                           | 0101                                                                                       | 11da ff                                                                                                                                                                                                                                                                                                                      | ff ffff              |  |  |  |

| Description:                                                                        | complem<br>the result<br>'1', the re<br>register 'f<br>the Acce<br>overriding<br>'1', then | Subtract W from register 'f' (2's complement method). If 'd' is '0' the result is stored in W. If 'd' is '1', the result is stored back in register 'f' (default). If = 'a' is '0', the Access Bank will be selected overriding the BSR value. If 'a' is '1', then the bank will be selected as per the BSR value (default). |                      |  |  |  |

| Words:                                                                              | 1                                                                                          |                                                                                                                                                                                                                                                                                                                              | . ,                  |  |  |  |

| Cycles:                                                                             | 1                                                                                          |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Q Cycle Activity:                                                                   |                                                                                            |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Q1                                                                                  | Q2                                                                                         | Q3                                                                                                                                                                                                                                                                                                                           | Q4                   |  |  |  |

| Decode                                                                              | Read<br>register 'f'                                                                       | Process<br>Data                                                                                                                                                                                                                                                                                                              | Write to destination |  |  |  |

| Example 1:                                                                          | SUBWF I                                                                                    | REG                                                                                                                                                                                                                                                                                                                          |                      |  |  |  |

| Before Instru                                                                       |                                                                                            |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| REG<br>W                                                                            | = 3<br>= 2                                                                                 |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| C                                                                                   | = ?                                                                                        |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| After Instruct<br>REG                                                               | = 1                                                                                        |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| W                                                                                   | = 2                                                                                        |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| C<br>Z<br>N                                                                         | = 0                                                                                        | sult is positive                                                                                                                                                                                                                                                                                                             |                      |  |  |  |

|                                                                                     | = 0                                                                                        |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Example 2:                                                                          |                                                                                            | REG, W                                                                                                                                                                                                                                                                                                                       |                      |  |  |  |

| Before Instru<br>REG                                                                | = 2                                                                                        |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| W                                                                                   | = 2                                                                                        |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| C<br>After Instruct                                                                 | = ?<br>tion                                                                                |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| REG                                                                                 | = 2                                                                                        |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

|                                                                                     |                                                                                            |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| W                                                                                   | = 0                                                                                        |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| C                                                                                   |                                                                                            | sult is zero                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |

| C<br>Z<br>N                                                                         | = 1 ; re<br>= 1<br>= 0                                                                     |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| C<br>Z<br>N<br><u>Example 3</u> :                                                   | = 1 ; re<br>= 1<br>= 0<br>SUBWF H                                                          | <b>sult is zero</b><br>REG                                                                                                                                                                                                                                                                                                   |                      |  |  |  |

| Example 3:<br>Before Instru                                                         | = 1 ; re<br>= 1<br>= 0<br>SUBWF I                                                          |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| C<br>Z<br>N<br><u>Example 3</u> :                                                   | = 1 ; re<br>= 1<br>= 0<br>SUBWF H                                                          |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Example 3:<br>Before Instru<br>REG<br>W<br>C                                        | = 1 ; re<br>= 1<br>= 0<br>SUBWF I<br>uction<br>= 0x01<br>= 0x02<br>= ?                     |                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Example 3:<br>Example 3:<br>Before Instru-<br>REG<br>W<br>C<br>After Instruct       | = 1 ; re<br>= 1<br>= 0<br>SUBWF I<br>uction<br>= 0x01<br>= 0x02<br>= ?<br>tion             | REG                                                                                                                                                                                                                                                                                                                          | pent)                |  |  |  |

| Example 3:<br>Before Instru<br>REG<br>W<br>C                                        | = 1 ; re<br>= 1<br>= 0<br>SUBWF I<br>uction<br>= 0x01<br>= 0x02<br>= ?                     | REG                                                                                                                                                                                                                                                                                                                          | nent)                |  |  |  |

| Example 3:<br>Example 3:<br>Before Instru<br>REG<br>W<br>C<br>After Instruct<br>REG | = 1 ; re<br>= 1<br>= 0<br>SUBWF I<br>= 0x01<br>= 0x02<br>= ?<br>tion<br>= 0xFFh            | REG                                                                                                                                                                                                                                                                                                                          | ,                    |  |  |  |

| SUBWFB Subtract W from f with Borrow |                |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |     |                      |  |  |  |  |  |

|--------------------------------------|----------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|--|--|--|--|--|

| Synt                                 | ax:            | [ <i>label</i> ] SUBWFB f[,d[,a]]                                                                       |                                                                                                                                                                                                                                                                                                                                                                                       |     |                      |  |  |  |  |  |

| Ope                                  | rands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                     |                                                                                                                                                                                                                                                                                                                                                                                       |     |                      |  |  |  |  |  |

| Ope                                  | ration:        | $(f) - (W) - (\overline{C}) \rightarrow dest$                                                           |                                                                                                                                                                                                                                                                                                                                                                                       |     |                      |  |  |  |  |  |

| Statu                                | us Affected:   | N, OV, C,                                                                                               | DC, Z                                                                                                                                                                                                                                                                                                                                                                                 |     |                      |  |  |  |  |  |

| Enco                                 | oding:         | 0101                                                                                                    | 10da                                                                                                                                                                                                                                                                                                                                                                                  | fff | f ffff               |  |  |  |  |  |

| Desi                                 | cription:      | row) from<br>method). I<br>stored in N<br>stored bac<br>'a' is '0', th<br>selected, c<br>'a' is '1', th | Subtract W and the Carry flag (bor-<br>row) from register 'f' (2's complement<br>method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default). If<br>'a' is '0', the Access Bank will be<br>selected, overriding the BSR value. If<br>'a' is '1', then the bank will be<br>selected as per the BSR value<br>(default). |     |                      |  |  |  |  |  |

| Wor                                  | ds:            | 1                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                       |     |                      |  |  |  |  |  |

| Cycl                                 | es:            | 1                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                       |     |                      |  |  |  |  |  |

| QC                                   | ycle Activity: |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |     |                      |  |  |  |  |  |

|                                      | Q1             | Q2                                                                                                      | Q                                                                                                                                                                                                                                                                                                                                                                                     | 3   | Q4                   |  |  |  |  |  |

|                                      | Decode         | Read<br>register 'f'                                                                                    | Proce<br>Dat                                                                                                                                                                                                                                                                                                                                                                          |     | Write to destination |  |  |  |  |  |

| Example 1:        | S     | UBWFB        | REG,  | 1,   | 0            |

|-------------------|-------|--------------|-------|------|--------------|

| Before Instruc    | ctior | า            |       |      |              |

| REG               | =     | 0x19         | (00   | 01   | 1001)        |

|                   | =     | 0x0D         | (00   | 00   | 1101)        |

| 0                 | =     | 0x01         |       |      |              |

| After Instruction | on    |              |       |      |              |

| NEO               | =     | 0x0C         | (00   | 000  | 1011)        |

| **                | =     | 0x0D         | (00   | 000  | 1101)        |

| 0                 | =     | 0x01<br>0x00 |       |      |              |

| N                 | =     | 0x00<br>0x00 | ; res | sult | is positive  |

| Example 2:        | S     | UBWFB        | REG,  | Ο,   | 0            |

| Before Instruc    | ctior | า            |       |      |              |

| REG               | =     | 0x1B         | (00   | 01   | 1011)        |

|                   | =     | 0x1A         | (00   | 01   | 1010)        |

| 0                 | =     | 0x00         |       |      |              |

| After Instruction | on    |              |       |      |              |

| NEO               | =     | 0x1B         | (00   | 01   | 1011)        |

|                   | =     | 0x00         |       |      |              |

| 2                 | =     | 0x01<br>0x01 | · roo | sult | is zero      |

| Ň                 | =     | 0x00         | , 100 | Suit | 13 2010      |

| Example 3:        | S     | UBWFB        | REG,  | 1,   | 0            |

| Before Instruc    | ctior | ו            |       |      |              |

| REG               | =     | 0x03         | (00   | 000  | 0011)        |

| **                | =     | 0x0E         | (00   | 000  | 1101)        |

| 0                 | =     | 0x01         |       |      |              |

| After Instruction |       |              |       |      |              |

| REG               | =     | 0xF5         |       |      | 0100)<br>mp] |

| W                 | =     | 0x0E         |       |      | 1101)        |

|                   | =     | 0x00         | ,00   |      |              |

| <u>_</u>          | =     | 0x00         |       | •    |              |

| N                 | =     | 0x01         | ; res | sult | is negative  |

# 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2220/2320/4220/4320 (Industrial) PIC18LF2220/2320/4220/4320 (Industrial) (Continued)

|              | 2220/2320/4220/4320<br>(strial)         |      | rd Oper                                              |       |            | s otherwise stated $A \leq +85^{\circ}C$ for industr |                                      |  |  |  |  |  |

|--------------|-----------------------------------------|------|------------------------------------------------------|-------|------------|------------------------------------------------------|--------------------------------------|--|--|--|--|--|

|              | 220/2320/4220/4320<br>strial, Extended) |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |            |                                                      |                                      |  |  |  |  |  |

| Param<br>No. | Device                                  | Тур  | Max                                                  | Units | Conditions |                                                      |                                      |  |  |  |  |  |

|              | Supply Current (IDD) <sup>(2,3)</sup>   |      |                                                      |       |            |                                                      |                                      |  |  |  |  |  |

|              | PIC18LF2X20/4X20                        | 440  | 600                                                  | μA    | -40°C      |                                                      |                                      |  |  |  |  |  |

|              |                                         | 450  | 600                                                  | μA    | +25°C      | VDD = 2.0V                                           |                                      |  |  |  |  |  |

|              |                                         | 460  | 600                                                  | μA    | +85°C      |                                                      |                                      |  |  |  |  |  |

|              | PIC18LF2X20/4X20                        | 0.80 | 1.0                                                  | mA    | -40°C      |                                                      |                                      |  |  |  |  |  |

|              |                                         | 0.78 | 1.0                                                  | mA    | +25°C      | VDD = 3.0V                                           | Fosc = 4 MHz                         |  |  |  |  |  |

|              |                                         | 0.77 | 1.0                                                  | mA    | +85°C      |                                                      | ( <b>PRI_RUN</b> ,<br>EC oscillator) |  |  |  |  |  |

|              | All devices                             | 1.6  | 2.0                                                  | mA    | -40°C      |                                                      |                                      |  |  |  |  |  |

|              |                                         | 1.5  | 2.0                                                  | mA    | +25°C      | VDD = 5.0V                                           |                                      |  |  |  |  |  |

|              |                                         | 1.5  | 2.0                                                  | mA    | +85°C      | VDD = 5.0V                                           |                                      |  |  |  |  |  |