Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4320t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F2220 PIC18F4220

- PIC18F2320 PIC18F4320

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price with the addition of highendurance Enhanced Flash program memory. On top of these features, the PIC18F2220/2320/4220/4320 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2220/2320/4220/4320 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled, but the peripherals are still active. In these states, power consumption can be reduced even further, to as little as 4%, of normal operation requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Lower Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer have been reduced by up to 80%, with typical values of 1.8 and 2.2  $\mu$ A, respectively.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2220/2320/4220/4320 family offer nine different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes using crystals or ceramic resonators.

- Two External Clock modes offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input with the second pin reassigned as general I/O).

- Two External RC Oscillator modes with the same pin options as the External Clock modes.

- An internal oscillator block, which provides a 31 kHz INTRC clock and an 8 MHz clock with 6 program selectable divider ratios (4 MHz to 125 kHz) for a total of 8 clock frequencies.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available. This allows for code execution during what would otherwise be the clock start-up interval and can even allow an application to perform routine back-ground activities and return to Sleep without returning to full power operation.

## 1.2 Other Special Features

- **Memory Endurance:** The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-Programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Enhanced CCP Module: In PWM mode, this module provides 1, 2 or 4 modulated outputs for controlling half-bridge and full-bridge drivers. Other features include Auto-Shutdown for disabling PWM outputs on interrupt or other select conditions and Auto-Restart to reactivate outputs once the condition has cleared.

- Addressable USART: This serial communication module is capable of standard RS-232 operation using the internal oscillator block, removing the need for an external crystal (and its accompanying power requirement) in applications that talk to the outside world.

- 10-Bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing a time-out range from 4 ms to over 2 minutes, that is stable across operating voltage and temperature.

| Dig Nome                                                     | Pin N               | umber  | Pin             | Buffer               | Description                                                                                                      |

|--------------------------------------------------------------|---------------------|--------|-----------------|----------------------|------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                     | PDIP                | SOIC   | Туре            | Туре                 | Description                                                                                                      |

|                                                              |                     |        |                 |                      | PORTB is a bidirectional I/O port. PORTB can be software<br>programmed for internal weak pull-ups on all inputs. |

| RB0/AN12/INT0<br>RB0<br>AN12<br>INT0                         | 21                  | 21     | I/O<br>I<br>I   | TTL<br>Analog<br>ST  | Digital I/O.<br>Analog input 12.<br>External interrupt 0.                                                        |

| RB1/AN10/INT1<br>RB1<br>AN10<br>INT1                         | 22                  | 22     | I/O<br>I<br>I   | TTL<br>Analog<br>ST  | Digital I/O.<br>Analog input 10.<br>External interrupt 1.                                                        |

| RB2/AN8/INT2<br>RB2<br>AN8<br>INT2                           | 23                  | 23     | I/O<br>I<br>I   | TTL<br>Analog<br>ST  | Digital I/O.<br>Analog input 8.<br>External interrupt 2.                                                         |

| RB3/AN9/CCP2<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup>            | 24                  | 24     | I/O<br>I<br>I/O | TTL<br>Analog<br>ST  | Digital I/O.<br>Analog input 9.<br>Capture 2 input, Compare 2 output, PWM2 output.                               |

| RB4/AN11/KBI0<br>RB4<br>AN11<br>KBI0                         | 25                  | 25     | I/O<br>I<br>I   | TTL<br>Analog<br>TTL | Digital I/O.<br>Analog input 11.<br>Interrupt-on-change pin.                                                     |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                           | 26                  | 26     | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>Low-voltage ICSP™ programming enable pin.                            |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                           | 27                  | 27     | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.                  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                           | 28                  | 28     | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                   |

| Legend: TTL = TTL c<br>ST = Schmi<br>O = Outpu<br>OD = Open- | itt Trigger i<br>It | nput w |                 | OS levels            | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                 |

## TABLE 1-2: PIC18F2220/2320 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when CCP2MX is cleared.

2: Default assignment for CCP2 when CCP2MX (CONFIG3H<0>) is set.

#### 3.1.2 ENTERING POWER-MANAGED MODES

In general, entry, exit and switching between powermanaged clock sources requires clock source switching. In each case, the sequence of events is the same.

Any change in the power-managed mode begins with loading the OSCCON register and executing a SLEEP instruction. The SCS1:SCS0 bits select one of three power-managed clock sources; the primary clock (as defined in Configuration Register 1H), the secondary clock (the Timer1 oscillator) and the internal oscillator block (used in RC modes). Modifying the SCS bits will have no effect until a SLEEP instruction is executed. Entry to the power-managed mode is triggered by the execution of a SLEEP instruction.

Figure 3-5 shows how the system is clocked while switching from the primary clock to the Timer1 oscillator. When the SLEEP instruction is executed, clocks to the device are stopped at the beginning of the next instruction cycle. Eight clock cycles from the new clock source are counted to synchronize with the new clock source are counted, clocks from the new clock source are counted, clocks from the new clock source are counted, clocks from the new clock source resume clocking the system. The actual length of the pause is between eight and nine clock periods from the new clock source. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

Three bits indicate the current clock source: OSTS and IOFS in the OSCCON register and T1RUN in the T1CON register. Only one of these bits will be set while in a power-managed mode other than PRI\_RUN. When the OSTS bit is set, the primary clock is providing the system clock. When the IOFS bit is set, the INTOSC output is providing a stable 8 MHz clock source and is providing the system clock. When the T1RUN bit is set, the Timer1 oscillator is providing the system clock. If none of these bits are set, then either the INTRC clock source is clocking the system or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source in Configuration Register 1H, then both the OSTS and IOFS bits may be set when in PRI\_RUN or PRI\_IDLE modes. This indicates that the primary clock (INTOSC output) is generating a stable 8 MHz output. Entering a power-managed RC mode (same frequency) would clear the OSTS bit.

- Note 1: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

- 2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode; executing a SLEEP instruction is simply a trigger to place the controller into a power-managed mode selected by the OSCCON register, one of which is Sleep mode.

#### 3.1.3 MULTIPLE SLEEP COMMANDS

The power-managed mode that is invoked with the SLEEP instruction is determined by the settings of the IDLEN and SCS bits at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by these same bits at that time. If the bits have changed, the device will enter the new power-managed mode specified by the new bit settings.

#### 3.1.4 COMPARISONS BETWEEN RUN AND IDLE MODES

Clock source selection for the Run modes is identical to the corresponding Idle modes. When a SLEEP instruction is executed, the SCS bits in the OSCCON register are used to switch to a different clock source. As a result, if there is a change of clock source at the time a SLEEP instruction is executed, a clock switch will occur.

In Idle modes, the CPU is not clocked and is not running. In Run modes, the CPU is clocked and executing code. This difference modifies the operation of the WDT when it times out. In Idle modes, a WDT time-out results in a wake from power-managed modes. In Run modes, a WDT time-out results in a WDT Reset (see Table 3-2).

During a wake-up from an Idle mode, the CPU starts executing code by entering the corresponding Run mode until the primary clock becomes ready. When the primary clock becomes ready, the clock source is automatically switched to the primary clock. The IDLEN and SCS bits are unchanged during and after the wake-up.

Figure 3-2 shows how the system is clocked during the clock source switch. The example assumes the device was in SEC\_IDLE or SEC\_RUN mode when a wake is triggered (the primary clock was configured in HSPLL mode).

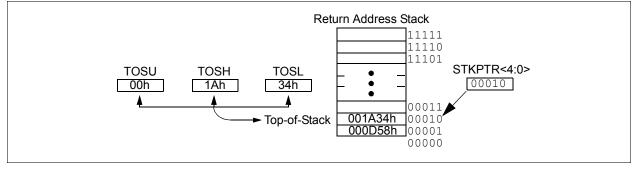

## 5.2 Return Address Stack

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC (Program Counter) is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, with the Stack Pointer initialized to 00000b after all Resets. There is no RAM associated with Stack Pointer, 00000b. This is only a Reset value. During a CALL type instruction, causing a push onto the stack, the Stack Pointer is first incremented and the RAM location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction, causing a pop from the stack, the contents of the RAM location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the top-of-stack Special File Registers. Data can also be pushed to, or popped from, the stack using the top-of-stack SFRs. Status bits indicate if the stack is full, has overflowed or underflowed.

#### 5.2.1 TOP-OF-STACK ACCESS

The top of the stack is readable and writable. Three register locations, TOSU, TOSH and TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 5-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU, TOSH and TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can replace the TOSU, TOSH and TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

#### 5.2.2 RETURN STACK POINTER (STKPTR)

The STKPTR register (Register 5-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. At Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 23.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push, and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or a POR occurs.

### FIGURE 5-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

**Note:** Returning a value of zero to the PC on an underflow has the effect of vectoring the program to the Reset vector, where the stack conditions can be verified and appropriate actions can be taken. This is not the same as a Reset, as the contents of the SFRs are not affected.

## 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

While writing or erasing program memory, instruction fetches cease until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

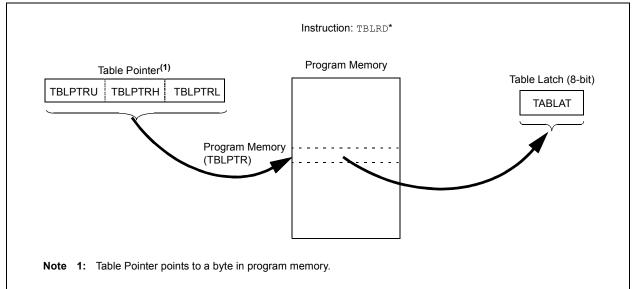

#### 6.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into TABLAT in the data RAM space. Figure 6-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from TABLAT in the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 6.5 "Writing to Flash Program Memory"**. Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned (TBLPTRL<0> = 0).

The EEPROM on-chip timer controls the write and erase times. The write and erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

FIGURE 6-1: TABLE READ OPERATION

## 7.0 DATA EEPROM MEMORY

The data EEPROM is readable and writable during normal operation over the entire VDD range. The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are four SFRs used to read and write the program and data EEPROM memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADR

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 256 bytes of data EEPROM with an address range from 00h to FFh.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip to chip. Please refer to parameter D122 (Table 26-1 in **Section 26.0 "Electrical Characteristics"**) for exact limits.

## 7.1 EEADR

The address register can address 256 bytes of data EEPROM.

### 7.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed. Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either Flash program or data EEPROM memory.

The WREN bit enables and disables erase and write operations. When set, erase and write operations are allowed. When clear, erase and write operations are disabled; the WR bit cannot be set while the WREN bit is clear. This mechanism helps to prevent accidental writes to memory due to errant (unexpected) code execution.

Firmware should keep the WREN bit clear at all times except when starting erase or write operations. Once firmware has set the WR bit, the WREN bit may be cleared. Clearing the WREN bit will not affect the operation in progress.

The WRERR bit is set when a write operation is interrupted by a Reset. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), as these registers have cleared as a result of the Reset.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 6.1 "Table Reads and Table Writes"** regarding table reads.

Note: Interrupt flag bit, EEIF in the PIR2 register, is set when write is complete. It must be cleared in software.

## 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 9-6: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|-------|--------|--------|--------|

| PSPIE <sup>(1)</sup> | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7                |       |       |       |       |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>BEDIE:</b> Derallel Slave Dort Bood/Mrite Interrupt Enable hit(1)             |

|-------|----------------------------------------------------------------------------------|

| DIL 7 | <b>PSPIE:</b> Parallel Slave Port Read/Write Interrupt Enable bit <sup>(1)</sup> |

|       | 1 = Enables the PSP read/write interrupt                                         |

|       | 0 = Disables the PSP read/write interrupt                                        |

| bit 6 | ADIE: A/D Converter Interrupt Enable bit                                         |

|       | 1 = Enables the A/D interrupt                                                    |

|       | 0 = Disables the A/D interrupt                                                   |

| bit 5 | RCIE: USART Receive Interrupt Enable bit                                         |

|       | 1 = Enables the USART receive interrupt                                          |

|       | 0 = Disables the USART receive interrupt                                         |

| bit 4 | TXIE: USART Transmit Interrupt Enable bit                                        |

|       | 1 = Enables the USART transmit interrupt                                         |

|       | 0 = Disables the USART transmit interrupt                                        |

| bit 3 | SSPIE: Master Synchronous Serial Port Interrupt Enable bit                       |

|       | 1 = Enables the MSSP interrupt                                                   |

|       | 0 = Disables the MSSP interrupt                                                  |

| bit 2 | CCP1IE: CCP1 Interrupt Enable bit                                                |

|       | 1 = Enables the CCP1 interrupt                                                   |

|       | 0 = Disables the CCP1 interrupt                                                  |

| bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit                                   |

|       | 1 = Enables the TMR2 to PR2 match interrupt                                      |

|       | 0 = Disables the TMR2 to PR2 match interrupt                                     |

| bit 0 | TMR1IE: TMR1 Overflow Interrupt Enable bit                                       |

|       | 1 = Enables the TMR1 overflow interrupt                                          |

|       | 0 = Disables the TMR1 overflow interrupt                                         |

|       |                                                                                  |

**Note 1:** This bit is reserved on PIC18F2X20 devices; always maintain this bit clear.

NOTES:

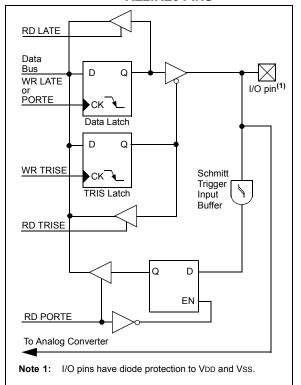

#### 10.5 PORTE, TRISE and LATE Registers

PORTE is available only in PIC18F4X20 devices. PIC18F2X20 devices always will read back 0x00 from PORTE.

For PIC18F4X20 devices, PORTE is a <u>4-bit wide port.</u> Three pins (RE0/AN5/RD, RE1/AN6/WR and RE2/ AN7/CS) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On a                         | Power-on | Reset, | RE2:RE0 | are |  |  |

|-------|------------------------------|----------|--------|---------|-----|--|--|

|       | configured as analog inputs. |          |        |         |     |  |  |

The upper four bits of the TRISE register also control the operation of the Parallel Slave Port. Their operation is explained in Register 10-1.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

The fourth pin of PORTE (MCLR/VPP/RE3) is an input only pin. Its operation is controlled by the MCLRE Configuration bit in Configuration Register 3H (CONFIG3H<7>). When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RE3 is enabled as |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|

|       | a digital input only if Master Clear   |  |  |  |  |  |  |

|       | functionality is disabled.             |  |  |  |  |  |  |

#### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE  |   | Initialize PORTE by clearing output |

|-------|--------|---|-------------------------------------|

|       |        | ; | data latches                        |

| CLRF  | LATE   | ; | Alternate method                    |

|       |        | ; | to clear output                     |

|       |        | ; | data latches                        |

| MOVLW | 0x0A   | ; | Configure A/D                       |

| MOVWF | ADCON1 | ; | for digital inputs                  |

| MOVLW | 0x03   | ; | Value used to                       |

|       |        | ; | initialize data                     |

|       |        | ; | direction                           |

| MOVWF | TRISC  | ; | Set RE <o> as inputs</o>            |

|       |        | ; | RE<1> as outputs                    |

|       |        | ; | RE<2> as inputs                     |

|       |        |   |                                     |

FIGURE 10-13:

BLOCK DIAGRAM OF RE2:RE0 PINS

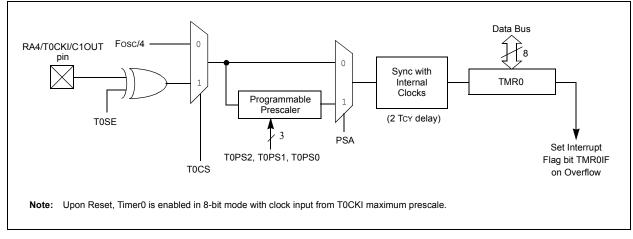

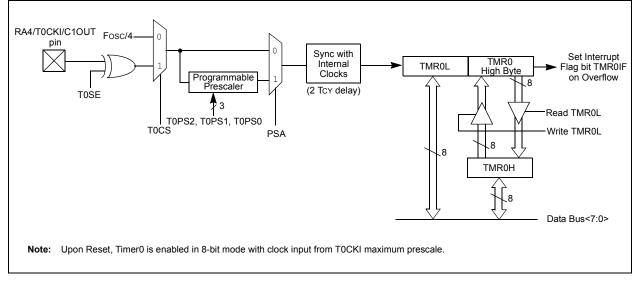

### FIGURE 11-1: TIMER0 BLOCK DIAGRAM IN 8-BIT MODE

## 15.0 CAPTURE/COMPARE/PWM (CCP) MODULES

The standard CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. Table 15-1 shows the timer resources required for each of the CCP module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the Special Event Trigger. Therefore, operation of a CCP module is described with respect to CCP1 except where noted. Table 15-2 shows the interaction of the CCP modules. Note: In 28-pin devices, both CCP1 and CCP2 function as standard CCP modules. In 40-pin devices, CCP1 is implemented as an Enhanced CCP module, offering additional capabilities in PWM mode. Capture and Compare modes are identical in all modules regardless of the device.

> Please see Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module" for a discussion of the enhanced PWM capabilities of the CCP1 module.

#### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

| U-0                                                                                                                                                                                                                 | U-0                                                                                              | R/W-0                              | R/W-0           | R/W-0            | R/W-0           | R/W-0            | R/W-0        |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------|-----------------|------------------|-----------------|------------------|--------------|--|

| _                                                                                                                                                                                                                   | _                                                                                                | DCxB1                              | DCxB0           | CCPxM3           | CCPxM2          | CCPxM1           | CCPxM0       |  |

| bit 7                                                                                                                                                                                                               |                                                                                                  |                                    |                 |                  |                 |                  | bit 0        |  |

| Legend:                                                                                                                                                                                                             |                                                                                                  |                                    |                 |                  |                 |                  |              |  |

| R = Readal                                                                                                                                                                                                          | ble bit                                                                                          | W = Writable                       | bit             | U = Unimpler     | mented bit, rea | d as '0'         |              |  |

| -n = Value a                                                                                                                                                                                                        | at POR                                                                                           | '1' = Bit is set                   |                 | '0' = Bit is cle | ared            | x = Bit is unk   | nown         |  |

| bit 7-6                                                                                                                                                                                                             | Unimplemen                                                                                       | ited: Read as '                    | 0'              |                  |                 |                  |              |  |

| bit 5-4                                                                                                                                                                                                             | -                                                                                                | B0: PWM Duty                       |                 | nd Bit 0 for CCI | Px Module       |                  |              |  |

| Capture mode:<br>Unused.<br><u>Compare mode</u> :<br>Unused.<br><u>PWM mode:</u><br>These bits are the two LSbs (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight MSbs of the<br>cycle are found in CCPR1L. |                                                                                                  |                                    |                 |                  |                 |                  |              |  |

| bit 3-0                                                                                                                                                                                                             | ,                                                                                                | PxM0: CCPx M                       | lode Select b   | its              |                 |                  |              |  |

|                                                                                                                                                                                                                     | 0001 = Rese                                                                                      |                                    |                 |                  | ,               |                  |              |  |

| 0010 = Compare mode: toggle output on match (CCPxIF bit is set)<br>0011 = Reserved                                                                                                                                  |                                                                                                  |                                    |                 |                  |                 |                  |              |  |

|                                                                                                                                                                                                                     |                                                                                                  | ure mode: ever                     |                 |                  |                 |                  |              |  |

| 0101 = Capture mode: every rising edge<br>0110 = Capture mode: every 4th rising edge                                                                                                                                |                                                                                                  |                                    |                 |                  |                 |                  |              |  |

|                                                                                                                                                                                                                     | 0111 = Capture mode: every 16th rising edge                                                      |                                    |                 |                  |                 |                  |              |  |

|                                                                                                                                                                                                                     | 1000 = Compare mode: initialize CCPx pin low; on compare match, force CCPx pin high (CCF is set) |                                    |                 |                  |                 |                  |              |  |

|                                                                                                                                                                                                                     | 1001 = Com<br>is se                                                                              | ,<br>pare mode: init<br>t)         | in high; on com | pare match, fo   | rce CCPx pin lo | ow (CCPxIF bi    |              |  |

|                                                                                                                                                                                                                     |                                                                                                  | pare mode: ger<br>ates as a port p |                 | •                | compare match   | n (CCPxIF bit is | set, CCPx pi |  |

|                                                                                                                                                                                                                     | 1011 = Com<br>11xx = PWN                                                                         | pare mode: trig<br>/ mode          | ger special e   | vent (CCPxIF b   | oit is set)     |                  |              |  |

| Name    | Bit 7                                                                      | Bit 6          | Bit 5        | Bit 4                            | Bit 3         | Bit 2    | Bit 1  | Bit 0  | Value<br>POR, B | -   | all o | e on<br>other<br>sets |

|---------|----------------------------------------------------------------------------|----------------|--------------|----------------------------------|---------------|----------|--------|--------|-----------------|-----|-------|-----------------------|

| INTCON  | GIE/GIEH                                                                   | PEIE/GIEL      | TMR0IE       | INT0IE                           | RBIE          | TMR0IF   | INT0IF | RBIF   | 0000 0          | 00x | 0000  | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup>                                                       | ADIF           | RCIF         | TXIF                             | SSPIF         | CCP1IF   | TMR2IF | TMR1IF | 0000 0          | 000 | 0000  | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup>                                                       | ADIE           | RCIE         | TXIE                             | SSPIE         | CCP1IE   | TMR2IE | TMR1IE | 0000 0          | 000 | 0000  | 0000                  |

| IPR1    | PSPIP <sup>(1)</sup>                                                       | ADIP           | RCIP         | TXIP                             | SSPIP         | CCP1IP   | TMR2IP | TMR1IP | 1111 1          | 111 | 1111  | 1111                  |

| TRISC   | PORTC Da                                                                   | ata Direction  | Register     |                                  |               |          |        |        | 1111 1          | 111 | 1111  | 1111                  |

| TMR1L   | Holding Re                                                                 | egister for th | e Least Sigr | nificant Byte                    | of the 16-bit | TMR1 Reg | gister |        | XXXX X          | xxx | uuuu  | uuuu                  |

| TMR1H   | Holding Re                                                                 | egister for th | e Most Sign  | ificant Byte                     | of the 16-bit | TMR1 Reg | ister  |        | XXXX X          | xxx | uuuu  | uuuu                  |

| T1CON   | RD16                                                                       | T1RUN          | T1CKPS1      | T1CKPS0                          | T10SCEN       | T1SYNC   | TMR1CS | TMR10N | 0000 0          | 000 | uuuu  | uuuu                  |

| CCPR1L  | Capture/C                                                                  | ompare/PWI     | M Register ? | I (LSB)                          |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCPR1H  | Capture/C                                                                  | ompare/PWI     | M Register ? | 1 (MSB)                          |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCP1CON | _                                                                          |                | DC1B1        | DC1B0                            | CCP1M3        | CCP1M2   | CCP1M1 | CCP1M0 | 00 0            | 000 | 00    | 0000                  |

| CCPR2L  | Capture/C                                                                  | ompare/PWI     | M Register 2 | 2 (LSB)                          |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCPR2H  | Capture/C                                                                  | ompare/PWI     | M Register 2 | 2 (MSB)                          |               |          |        |        | XXXX X          | xxx | uuuu  | uuuu                  |

| CCP2CON | _                                                                          | —              | DC2B1        | DC2B0                            | CCP2M3        | CCP2M2   | CCP2M1 | CCP2M0 | 00 0            | 000 | 00    | 0000                  |

| PIR2    | OSCFIF                                                                     | CMIF           | _            | EEIF                             | BCLIF         | LVDIF    | TMR3IF | CCP2IF | 00-0 0          | 000 | 00-0  | 0000                  |

| PIE2    | OSCFIE                                                                     | CMIE           | _            | EEIE                             | BCLIE         | LVDIE    | TMR3IE | CCP2IE | 00-0 0          | 000 | 00-0  | 0000                  |

| IPR2    | OSCFIP                                                                     | CMIP           | —            | - EEIP BCLIP LVDIP TMR3IP CCP2IP |               |          |        |        |                 | 111 | 11-1  | 1111                  |

| TMR3L   | Holding Re                                                                 | egister for th | e Least Sigr | nificant Byte                    | of the 16-bit | TMR3 Reg | gister |        | XXXX X          | xxx | uuuu  | uuuu                  |

| TMR3H   | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register |                |              |                                  |               |          |        |        |                 | xxx | uuuu  | uuuu                  |

| T3CON   | RD16                                                                       | T3CCP2         | T3CKPS1      | T3CKPS0                          | T3CCP1        | T3SYNC   | TMR3CS | TMR3ON | 0000 0          | 000 | uuuu  | uuuu                  |

#### TABLE 15-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: These bits are reserved on the PIC18F2X20 devices; always maintain these bits clear.

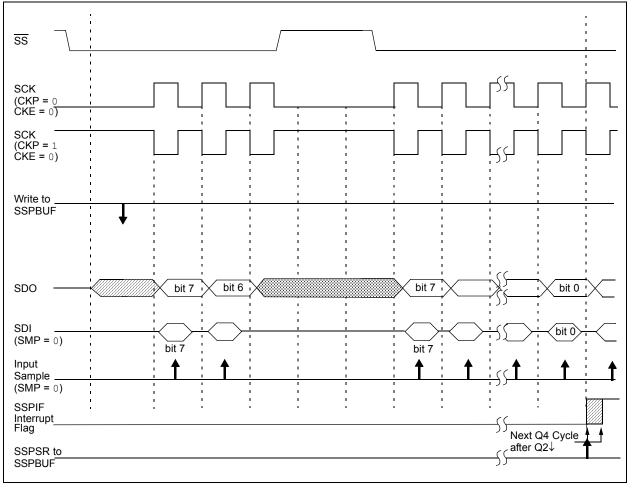

#### 17.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in power-managed modes, the slave can transmit/receive data. When a byte is received, the device will wake-up from power-managed modes.

#### 17.3.7 SLAVE SELECT CONTROL

The  $\overline{SS}$  pin allows a master controller to select one of several slave controllers for communications in systems with more than one slave. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). The SS pin is configured for input by setting TRISA<5>. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin

is tri-stated, even if in the middle of a transmitted byte. External pull-up/pull-down resistors may be desirable, depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100), the SPI module will reset when the  $\overline{SS}$  pin is set high.

- 2: If the SPI is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, SSPSR is cleared. This can be done by either driving the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

FIGURE 17-4: SLAVE SYNCHRONIZATION WAVEFORM

NOTES:

#### 23.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

#### 23.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

## 23.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code-protected.

## 23.7 In-Circuit Serial Programming

PIC18F2X20/4X20 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed (see Table 23-5).

### 23.8 In-Circuit Debugger

When the DEBUG bit in Configuration register, CONFIG4L, is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 23-4 shows which resources are required by the background debugger.

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, VSS, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

## 23.9 Low-Voltage ICSP Programming

The LVP bit in Configuration Register 4L (CONFIG4L<2>) enables Low-Voltage ICSP Programming (LVP). When LVP is enabled, the microcontroller can be programmed without requiring high voltage being applied to the MCLR/VPP pin, but the RB5/PGM pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

LVP is enabled in erased devices.

While programming using LVP, VDD is applied to the MCLR/VPP pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

| Note 1: | High-voltage programming is always<br>available, regardless of the state of the<br>LVP bit or the PGM pin, by applying VIHH |

|---------|-----------------------------------------------------------------------------------------------------------------------------|

|         | to the MCLR pin.                                                                                                            |

| •       |                                                                                                                             |

- 2: When Low-Voltage Programming is enabled, the RB5 pin can no longer be used as a general purpose I/O pin.

- **3:** When LVP is enabled, externally pull the PGM pin to Vss to allow normal program execution.

If Low-Voltage ICSP Programming mode will not be used, the LVP bit can be cleared and RB5/PGM becomes available as the digital I/O pin, RB5. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the MCLR/ VPP pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased using either a block erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a block erase is required. If a block erase is to be performed when using Low-Voltage Programming, the device must be supplied with VDD of 4.5V to 5.5V.

TABLE 23-5: ICSP™/ICD CONNECTIONS

| Signal | Pin  | Notes                                              |  |  |  |

|--------|------|----------------------------------------------------|--|--|--|

| PGD    | RB7  |                                                    |  |  |  |

| PGC    | RB6  |                                                    |  |  |  |

| MCLR   | MCLR | May require isolation from<br>application circuits |  |  |  |

| Vdd    | Vdd  |                                                    |  |  |  |

| Vss    | Vss  |                                                    |  |  |  |

| PGM    | RB5  | Pull RB5 low if LVP is enabled                     |  |  |  |

| Mnemonic,<br>Operands |       | Description                    |        | 16-Bit Instruction Word |      |              |      | Status            |       |

|-----------------------|-------|--------------------------------|--------|-------------------------|------|--------------|------|-------------------|-------|

|                       |       | Description                    | Cycles | MSb                     |      |              | LSb  | Affected          | Notes |

| CONTROL               | OPER/ | ATIONS                         |        |                         |      |              |      |                   |       |

| BC                    | n     | Branch if Carry                | 1 (2)  | 1110                    | 0010 | nnnn         | nnnn | None              |       |

| BN                    | n     | Branch if Negative             | 1 (2)  | 1110                    | 0110 | nnnn         | nnnn | None              |       |

| BNC                   | n     | Branch if Not Carry            | 1 (2)  | 1110                    | 0011 | nnnn         | nnnn | None              |       |

| BNN                   | n     | Branch if Not Negative         | 1 (2)  | 1110                    | 0111 | nnnn         | nnnn | None              |       |

| BNOV                  | n     | Branch if Not Overflow         | 1 (2)  | 1110                    | 0101 | nnnn         | nnnn | None              |       |

| BNZ                   | n     | Branch if Not Zero             | 1 (2)  | 1110                    | 0001 | nnnn         | nnnn | None              |       |

| BOV                   | n     | Branch if Overflow             | 1 (2)  | 1110                    | 0100 | nnnn         | nnnn | None              |       |

| BRA                   | n     | Branch Unconditionally         | 2      | 1101                    | 0nnn | nnnn         | nnnn | None              |       |

| BZ                    | n     | Branch if Zero                 | 1 (2)  | 1110                    | 0000 | nnnn         | nnnn | None              |       |

| CALL                  | n, s  | Call Subroutine1st word        | 2      | 1110                    | 110s | kkkk         | kkkk | None              |       |

|                       |       | 2nd word                       |        | 1111                    | kkkk | kkkk         | kkkk |                   |       |

| CLRWDT                | —     | Clear Watchdog Timer           | 1      | 0000                    | 0000 | 0000         | 0100 | TO, PD            |       |

| DAW                   | —     | Decimal Adjust WREG            | 1      | 0000                    | 0000 | 0000         | 0111 | C, DC             |       |

| GOTO                  | n     | Go to Address 1st word         | 2      | 1110                    | 1111 | kkkk         | kkkk | None              |       |

|                       |       | 2nd word                       |        | 1111                    | kkkk | kkkk         | kkkk |                   |       |

| NOP                   | _     | No Operation                   | 1      | 0000                    | 0000 | 0000         | 0000 | None              |       |

| NOP                   | _     | No Operation (Note 4)          | 1      | 1111                    | XXXX | XXXX         | XXXX | None              |       |

| POP                   | _     | Pop Top of Return Stack (TOS)  | 1      | 0000                    | 0000 | 0000         | 0110 | None              |       |

| PUSH                  | _     | Push Top of Return Stack (TOS) | 1      | 0000                    | 0000 | 0000         | 0101 | None              |       |

| RCALL                 | n     | Relative Call                  | 2      | 1101                    | 1nnn | nnnn         | nnnn | None              |       |

| RESET                 |       | Software Device Reset          | 1      | 0000                    | 0000 | 1111         | 1111 | All               |       |

| RETFIE                | S     | Return from Interrupt Enable   | 2      | 0000                    | 0000 | 0001         | 000s | GIE/GIEH,         |       |

| RETLW                 | k     | Return with Literal in WREG    | 2      | 0000                    | 1100 | kkkk         | kkkk | PEIE/GIEL<br>None |       |

| RETURN                |       | Return from Subroutine         | 2      | 0000                    | 0000 | кккк<br>0001 | 001s |                   |       |

| SLEEP                 | S     | Go into Standby mode           | 2      | 0000                    | 0000 | 0000         |      | TO, PD            |       |

|                       | _     | Go Into Standby mode           | •      | 0000                    |      |              | UUII | 10, FD            |       |

#### TABLE 24-2: PIC18FXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| BNC                                                                                             | :                     | Branch if                                                                                                                                                                                                                                                                               | Not Carry       |             | BNN                                                                                                                                                                        | I                                                          | Branch if                                                 | Not Negativ                                                                     | Ve          |

|-------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|-------------|

| Synt                                                                                            |                       | [ label ] B                                                                                                                                                                                                                                                                             |                 |             | Synt                                                                                                                                                                       | -                                                          | [ label ] B                                               |                                                                                 |             |

| •                                                                                               | rands:                |                                                                                                                                                                                                                                                                                         | -128 ≤ n ≤ 127  |             | •                                                                                                                                                                          | rands:                                                     |                                                           | -128 ≤ n ≤ 127                                                                  |             |

| •                                                                                               | ration:               | if Carry bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                  |                 | •           | ration:                                                                                                                                                                    | if Negative                                                | if Negative bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC |                                                                                 |             |

| Statu                                                                                           | us Affected:          | None                                                                                                                                                                                                                                                                                    |                 |             | Statu                                                                                                                                                                      | us Affected: None                                          |                                                           |                                                                                 |             |

| Enco                                                                                            | oding:                | 1110                                                                                                                                                                                                                                                                                    | 0011 nni        | nn nnnn     | Enco                                                                                                                                                                       | oding:                                                     | 1110                                                      | 1110 0111 nnnn                                                                  |             |

| Desc                                                                                            | cription:             | If the Carry bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is<br>then a two-cycle instruction. |                 | Dese        | Description: If the Negative b<br>program will brai<br>The 2's complem<br>added to the PC<br>have incremente<br>instruction, the n<br>PC + 2 + 2n. Thi<br>then a two-cycle |                                                            |                                                           | umber '2n' is<br>e the PC will<br>etch the next<br>ldress will be<br>ruction is |             |

| Word                                                                                            | ds:                   | 1                                                                                                                                                                                                                                                                                       |                 |             | Wor                                                                                                                                                                        | ds:                                                        | 1                                                         |                                                                                 |             |

| Cycl                                                                                            | es:                   | 1(2)                                                                                                                                                                                                                                                                                    |                 |             | Cycl                                                                                                                                                                       | es:                                                        | 1(2)                                                      |                                                                                 |             |

|                                                                                                 | ycle Activity:<br>mp: | :                                                                                                                                                                                                                                                                                       |                 |             |                                                                                                                                                                            | ycle Activity                                              | :                                                         |                                                                                 |             |

|                                                                                                 | Q1                    | Q2                                                                                                                                                                                                                                                                                      | Q3              | Q4          | _                                                                                                                                                                          | Q1                                                         | Q2                                                        | Q3                                                                              | Q4          |

|                                                                                                 | Decode                | Read literal<br>'n'                                                                                                                                                                                                                                                                     | Process<br>Data | Write to PC |                                                                                                                                                                            | Decode                                                     | Read literal<br>'n'                                       | Process<br>Data                                                                 | Write to PC |

|                                                                                                 | No                    | No                                                                                                                                                                                                                                                                                      | No              | No          |                                                                                                                                                                            | No                                                         | No                                                        | No                                                                              | No          |

| IF NI                                                                                           | operation             | operation                                                                                                                                                                                                                                                                               | operation       | operation   |                                                                                                                                                                            | operation                                                  | operation                                                 | operation                                                                       | operation   |

| ITING                                                                                           | o Jump:<br>Q1         | Q2                                                                                                                                                                                                                                                                                      | Q3              | Q4          | IT IN                                                                                                                                                                      | o Jump:<br>Q1                                              | Q2                                                        | Q3                                                                              | Q4          |

|                                                                                                 | Decode                | Read literal                                                                                                                                                                                                                                                                            | Process         | No<br>No    | 1                                                                                                                                                                          | Decode                                                     | Read literal                                              | Process                                                                         | No          |

|                                                                                                 | Decode                | ʻn'                                                                                                                                                                                                                                                                                     | Data            | operation   |                                                                                                                                                                            | Decode                                                     | ʻn'                                                       | Data                                                                            | operation   |

| Example:HEREBNCJumpBefore Instruction=address(HERE)After InstructionIf Carry=0;PC=address(Jump) |                       |                                                                                                                                                                                                                                                                                         |                 |             |                                                                                                                                                                            | nple:<br>Before Instru<br>PC<br>After Instruc<br>If Negati | = adv<br>tion<br>ve = 0;<br>= adv                         | BNN Jump<br>dress (HERE<br>dress (Jump                                          | )           |

|                                                                                                 | If Carry<br>PC        | = 1;<br>= ade                                                                                                                                                                                                                                                                           | dress (HERE     | + 2)        |                                                                                                                                                                            | lf Negati<br>PC                                            |                                                           | dress (HERE                                                                     | + 2)        |

## TABLE 26-4: LOW-VOLTAGE DETECT CHARACTERISTICS (CONTINUED)