Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 45                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16К х 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560d40l1b3e0x |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | 4.9   | Power n   | nanagement electrical characteristics                                |

|----------|-------|-----------|----------------------------------------------------------------------|

|          |       | 4.9.1     | Voltage regulator electrical characteristics                         |

|          |       | 4.9.2     | Low voltage detector electrical characteristics                      |

|          | 4.10  | Power of  | consumption                                                          |

|          | 4.11  | Flash m   | emory electrical characteristics 49                                  |

|          |       | 4.11.1    | Program/Erase characteristics                                        |

|          |       | 4.11.2    | Flash power supply DC characteristics51                              |

|          |       | 4.11.3    | Start-up/Switch-off timings                                          |

|          | 4.12  | Electror  | nagnetic compatibility (EMC) characteristics                         |

|          |       | 4.12.1    | Designing hardened software to avoid noise problems                  |

|          |       | 4.12.2    | Electromagnetic interference (EMI)52                                 |

|          |       | 4.12.3    | Absolute maximum ratings (electrical sensitivity)53                  |

|          | 4.13  | Fast ext  | ernal crystal oscillator (4 to 16 MHz) electrical characteristics 55 |

|          | 4.14  | FMPLL     | electrical characteristics 58                                        |

|          | 4.15  | Fast inte | ernal RC oscillator (16 MHz) electrical characteristics 58           |

|          | 4.16  | Slow int  | ernal RC oscillator (128 kHz) electrical characteristics 59          |

|          | 4.17  | ADC ele   | ectrical characteristics61                                           |

|          |       | 4.17.1    | Introduction                                                         |

|          |       | 4.17.2    | Input impedance and ADC accuracy62                                   |

|          |       | 4.17.3    | ADC electrical characteristics                                       |

|          | 4.18  | On-chip   | peripherals                                                          |

|          |       | 4.18.1    | Current consumption                                                  |

|          |       | 4.18.2    | DSPI characteristics                                                 |

|          |       | 4.18.3    | JTAG characteristics                                                 |

| 5        | Packa | ige cha   | racteristics                                                         |

|          | 5.1   | ECOPA     | CK®                                                                  |

|          | 5.2   | Package   | e mechanical data                                                    |

|          |       | 5.2.1     | LQFP100                                                              |

|          |       | 5.2.2     | LQFP64                                                               |

| 6        | Order | ina info  | ormation                                                             |

| U        | Juer  | ing init  |                                                                      |

| Appendix |       | bbrevia   | tions                                                                |

6

*Table 3* summarizes the functions of all blocks present in the Pictus 512K series of microcontrollers. Please note that the presence and number of blocks varies by device and package.

| Block                                             | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                 | Multi-channel, 12-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                          | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock generation module<br>(MC_CGM)               | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Clock monitor unit (CMU)                          | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                       | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Crossbar switch (XBAR)                            | Supports simultaneous connections between two master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.                                                                                                                                                   |

| Deserial serial peripheral interface (DSPI)       | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Enhanced direct memory access (eDMA)              | Performs complex data transfers with minimal intervention from a host processor via "n" programmable channels.                                                                                                                                                                                                    |

| Enhanced modular input output system (eMIOS)      | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Error correction status module (ECSM)             | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Flash memory                                      | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                 | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Frequency-modulated phase-<br>locked loop (FMPLL) | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Internal multiplexer (IMUX) SIU subblock          | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Interrupt controller (INTC)                       | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller (JTAGC)                           | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Mode entry module (MC_ME)                         | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Non-maskable interrupt (NMI)                      | Handles external events that must produce an immediate response, such as power down detection                                                                                                                                                                                                                     |

#### Table 3. Pictus 512K series block summary

# 3 Package pinouts and signal descriptions

## 3.1 Package pinouts

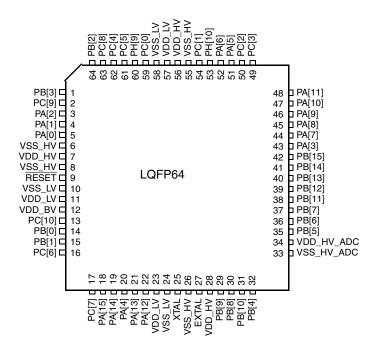

The available LQFP pinouts are provided in the following figures. For pin signal descriptions, please refer to *Table 6*.

*Figure 3* shows the Pictus 512K in the LQFP64 package.

Figure 3. LQFP64 pin configuration (top view)

## 3.2 Pad configuration during reset phases

All pads have a fixed configuration under reset.

During the power-up phase, all pads are forced to tristate.

After power-up phase, all pads are forced to tristate with the following exceptions:

- PA[9] (FAB) is pull-down. Without external strong pull-up the device starts fetching from flash.

- PA[8] (ABS[0]) is pull-up.

- RESET pad is driven low. This is pull-up only after PHASE2 reset completion.

- JTAG pads (TCK, TMS and TDI) are pull-up while TDO remains tristate.

- Precise ADC pads (PB[7:4] and PD[11:0]) are left tristate (no output buffer available).

- Main oscillator pads (EXTAL, XTAL) are tristate.

## 3.3 Voltage supply pins

Voltage supply pins are used to provide power to the device. Two dedicated pins are used for 1.2 V regulator stabilization.

|          |         | A.U                                  |                                 |                 | I/O              |             | T<br>ation             | Pin n  | umber   |

|----------|---------|--------------------------------------|---------------------------------|-----------------|------------------|-------------|------------------------|--------|---------|

| Port pin | PCR     | Alternate<br>function <sup>(1)</sup> | Function                        | Peripheral      | direction<br>(2) | Pad<br>type | RESET<br>configuration | LQFP64 | LQFP100 |

|          |         | AF0                                  | GPIO[39]                        | SIUL            | I/O              |             |                        |        |         |

|          |         | AF1                                  | —                               | —               | —                |             |                        |        |         |

| PC[7]    | PCR[39] | AF2<br>AF3                           | _                               | _               | —                | S           | Tristate               | 17     | 26      |

|          |         | AF5<br>—                             | LIN1RX                          | LINFlex_1       |                  |             |                        |        |         |

|          |         | _                                    | WKPU[12] <sup>(3)</sup>         | WKPU            | I                |             |                        |        |         |

|          |         | AF0                                  | GPIO[40]                        | SIUL            | I/O              |             |                        |        |         |

| PC[8]    | PCR[40] | AF1                                  | LIN2TX                          | LINFlex_2       | 0                | s           | Tristate               | 63     | 99      |

| FC[0]    |         | AF2                                  | E0UC[3]                         | eMIOS_0         | I/O              | 3           | mstate                 | 03     | 99      |

|          |         | AF3                                  | _                               | _               | _                |             |                        |        |         |

|          |         | AF0                                  | GPIO[41]                        | SIUL            | I/O              |             |                        |        |         |

|          |         | AF1                                  | -                               | —               | —                |             | Tristate               | 2      |         |

| PC[9]    | PCR[41] | AF2                                  | E0UC[7]                         | eMIOS_0         | I/O              | S           |                        |        | 2       |

|          |         | AF3                                  | LIN2RX                          | LINFlex_2       |                  |             |                        |        |         |

|          |         | _                                    | WKPU[13] <sup>(3)</sup>         |                 |                  |             |                        |        |         |

|          | PCR[42] | AF0                                  | GPIO[42]                        | SIUL            | I/O              |             |                        |        |         |

| DOI101   |         | AF1                                  | _                               | —               | —                | 5.4         | Triatata               | 10     | 00      |

| PC[10]   |         | AF2                                  | —                               | —               | —                | М           | Tristate               | 13     | 22      |

|          |         | AF3                                  | MA[1]                           | ADC             | 0                |             |                        |        |         |

|          |         | AF0                                  | GPIO[43]                        | SIUL            | I/O              |             | S Tristate             |        |         |

|          |         | AF1                                  | —                               | —               | —                |             |                        | e —    | 21      |

| PC[11]   | PCR[43] | AF2                                  | —                               | _               | _                | S           |                        |        |         |

|          |         | AF3                                  | MA[2]<br>WKPU[5] <sup>(3)</sup> | ADC             | 0                |             |                        |        |         |

|          |         |                                      |                                 | WKPU            |                  |             |                        |        |         |

|          |         | AF0<br>AF1                           | GPIO[44]<br>E0UC[12]            | SIUL<br>eMIOS_0 | I/O<br>I/O       |             |                        |        |         |

| PC[12]   | PCR[44] | AF2                                  |                                 | enviro          |                  | м           | Tristate               | _      | 97      |

| . 0[]    |         | AF3                                  | _                               | _               | _                |             | motato                 |        | 07      |

|          |         | —                                    | EIRQ[19]                        | SIUL            | I                |             |                        |        |         |

|          |         | AF0                                  | GPIO[45]                        | SIUL            | I/O              |             |                        |        |         |

| PC[13]   | PCR[45] | AF1                                  | E0UC[13]                        | eMIOS_0         | I/O              | s           | Tristate               |        | 98      |

|          |         | AF2                                  | —                               | —               | —                | Ŭ           | motato                 |        |         |

|          |         | AF3                                  |                                 |                 |                  |             |                        |        |         |

|          |         | AF0                                  | GPIO[46]                        | SIUL            | I/O              |             |                        |        |         |

|          |         | AF1                                  | E0UC[14]                        | eMIOS_0         | I/O              |             | Triatate               |        | 3       |

| PC[14]   | PCR[46] | AF2<br>AF3                           | _                               | _               | _                | S           | Tristate               | —      |         |

|          |         | — AFS                                | EIRQ[8]                         | SIUL            |                  |             |                        |        |         |

|          |         |                                      |                                 | 0.02            | ı                |             |                        |        |         |

Table 6.

Functional port pin descriptions (continued)

|          |         | A 14 4                               |                                                               |                                          | I/O                          | Deal        | T<br>ation             | Pin n  | umber   |

|----------|---------|--------------------------------------|---------------------------------------------------------------|------------------------------------------|------------------------------|-------------|------------------------|--------|---------|

| Port pin | PCR     | Alternate<br>function <sup>(1)</sup> | Function                                                      | Peripheral                               | direction<br>(2)             | Pad<br>type | RESET<br>configuration | LQFP64 | LQFP100 |

| PE[6]    | PCR[70] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[70]<br>E0UC[22]<br>CS3_0<br>MA[1]<br>EIRQ[22]            | SIUL<br>eMIOS_0<br>DSPI_0<br>ADC<br>SIUL | I/O<br>I/O<br>O<br>I         | М           | Tristate               | _      | 95      |

| PE[7]    | PCR[71] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[71]<br>E0UC[23]<br>CS2_0<br>MA[0]<br>EIRQ[23]            | SIUL<br>eMIOS_0<br>DSPI_0<br>ADC<br>SIUL | I/O<br>I/O<br>O<br>I         | М           | Tristate               | _      | 96      |

| PE[8]    | PCR[72] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[72]<br>—<br>E0UC[22]<br>—                                | SIUL<br>—<br>eMIOS_0<br>—                | I/O<br>—<br>I/O<br>—         | М           | Tristate               | _      | 9       |

| PE[9]    | PCR[73] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[73]<br>—<br>E0UC[23]<br>—<br>WKPU[7] <sup>(3)</sup>      | SIUL<br><br>eMIOS_0<br><br>WKPU          | I/O<br>—<br>I/O<br>—<br>I    | S           | Tristate               | _      | 10      |

| PE[10]   | PCR[74] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[74]<br>—<br>CS3_1<br>—<br>EIRQ[10]                       | SIUL<br>—<br>DSPI_1<br>—<br>SIUL         | I/O   -<br>-                 | S           | Tristate               | _      | 11      |

| PE[11]   | PCR[75] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[75]<br>E0UC[24]<br>CS4_1<br>—<br>WKPU[14] <sup>(3)</sup> | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>WKPU   | 1/0<br>1/0   -               | S           | Tristate               | _      | 13      |

| PE[12]   | PCR[76] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[76]<br>—<br>—<br>ADC1_S[7]<br>EIRQ[11]                   | SIUL<br>—<br>—<br>ADC<br>SIUL            | I/O<br>—<br>—<br>—<br>—<br>— | S           | Tristate               | _      | 76      |

|          |         | I                                    |                                                               | Port                                     | Н                            | I           |                        | I      | I       |

Table 6.

Functional port pin descriptions (continued)

### Equation 1 $T_J = T_A + (P_D \times R_{\theta JA})$

Where:

$T_A$  is the ambient temperature in °C.

$R_{\theta JA}$  is the package junction-to-ambient thermal resistance, in °C/W.

$P_D$  is the sum of  $P_{INT}$  and  $P_{I/O}$  ( $P_D = P_{INT} + P_{I/O}$ ).

$\mathsf{P}_{\mathsf{INT}}$  is the product of  $\mathsf{I}_{\mathsf{DD}}$  and  $\mathsf{V}_{\mathsf{DD}}$ , expressed in watts. This is the chip internal power.

$P_{I/O}$  represents the power dissipation on input and output pins; user determined.

Most of the time for the applications,  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant, if the device is configured to continuously drive external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

#### Equation 2 $P_D = K / (T_J + 273 °C)$

Therefore, solving equations 1 and 2:

#### Equation 3 K = $P_D x (T_A + 273 °C) + R_{\theta JA} x P_D^2$

Where:

K is a constant for the particular part, which may be determined from *Equation 3* by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  may be obtained by solving equations *1* and *2* iteratively for any value of  $T_A$ .

## 4.7 I/O pad electrical characteristics

### 4.7.1 I/O pad types

The device provides four main I/O pad types depending on the associated alternate functions:

- Slow pads—These pads are the most common pads, providing a good compromise between transition time and low electromagnetic emission.

- Medium pads—These pads provide transition fast enough for the serial communication channels with controlled current to reduce electromagnetic emission.

- Input only pads—These pads are associated to ADC channels (ADC\_P[X]) providing low input leakage.

Medium pads can use slow configuration to reduce electromagnetic emission except for PC[1], that is medium only, at the cost of reducing AC performance.

### 4.7.2 I/O input DC characteristics

Table 15 provides input DC electrical characteristics as described in Figure 4.

### 4.7.3 I/O output DC characteristics

The following tables provide DC characteristics for bidirectional pads:

- *Table 16* provides weak pull figures. Both pull-up and pull-down resistances are supported.

- *Table 17* provides output driver characteristics for I/O pads when in SLOW configuration.

- *Table 18* provides output driver characteristics for I/O pads when in MEDIUM configuration.

| Symbol              |    | O Demonster |                                          | Conditions <sup>(1)</sup>                                         |                     |    | Value |     |      |

|---------------------|----|-------------|------------------------------------------|-------------------------------------------------------------------|---------------------|----|-------|-----|------|

|                     |    | С           | Parameter                                | Conditions                                                        |                     |    | Тур   | Max | Unit |

| P                   | Ρ  |             |                                          | PAD3V5V = 0                                                       | 10                  | —  | 150   |     |      |

| ll <sub>WPU</sub> l |    | С           | absolute value                           | $V_{IN} = V_{IL}, V_{DD} = 5.0 V \pm 10\%$                        | $PAD3V5V = 1^{(2)}$ | 10 | —     | 250 | μA   |

|                     |    | Ρ           |                                          | $V_{IN} = V_{IL}, V_{DD} = 3.3 \text{ V} \pm 10\%$                | PAD3V5V = 1         | 10 | —     | 150 |      |

|                     |    | Ρ           |                                          | V <sub>IN</sub> = V <sub>IH</sub> , V <sub>DD</sub> = 5.0 V ± 10% | PAD3V5V = 0         | 10 | —     | 150 |      |

| ll <sub>wpd</sub> l | сс | С           | Weak pull-down current<br>absolute value | $V_{\rm IN} - V_{\rm IH}, V_{\rm DD} = 5.0 V \pm 10.8$            | $PAD3V5V = 1^{(2)}$ | 10 | _     | 250 | μA   |

|                     |    | Ρ           |                                          | $V_{IN} = V_{IH}, V_{DD} = 3.3 \text{ V} \pm 10\%$                | PAD3V5V = 1         | 10 | —     | 150 |      |

Table 16.

I/O pull-up/pull-down DC electrical characteristics

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET are configured in input or in high impedance state.

| Sum             | Symbol |   | Parameter                               |           | Conditions <sup>(1)</sup>                                                                            |                       |     | Value              |      |  |  |

|-----------------|--------|---|-----------------------------------------|-----------|------------------------------------------------------------------------------------------------------|-----------------------|-----|--------------------|------|--|--|

| Sym             | 1001   | C | Falameter                               |           | Conditions                                                                                           | Min                   | Тур | Max                | Unit |  |  |

|                 |        | Ρ |                                         |           | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | 0.8V <sub>DD</sub>    | _   | _                  |      |  |  |

| V <sub>OH</sub> | сс     | С | Output high level<br>SLOW configuration | Push Pull | I <sub>OH</sub> = −2 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(2)</sup>                | 0.8V <sub>DD</sub>    | _   | _                  | v    |  |  |

|                 |        | С |                                         |           | $I_{OH} = -1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$<br>(recommended) | V <sub>DD</sub> - 0.8 | _   | _                  |      |  |  |

|                 |        | Ρ | Р                                       |           | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended)  | _                     | _   | 0.1V <sub>DD</sub> |      |  |  |

| V <sub>OL</sub> | сс     | С | Output low level<br>SLOW configuration  | Push Pull | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^{(2)}$             | _                     |     | 0.1V <sub>DD</sub> | v    |  |  |

|                 |        | С |                                         |           | $I_{OL} = 1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$<br>(recommended)  | _                     |     | 0.5                |      |  |  |

| Table 17. | SLOW configuration output buffer electrical characteristics |

|-----------|-------------------------------------------------------------|

|-----------|-------------------------------------------------------------|

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

| Table 22. I/O weight <sup>(1)</sup> (continu |

|----------------------------------------------|

|----------------------------------------------|

|        | LQFP100/LQFP64  |         |         |         |  |  |  |

|--------|-----------------|---------|---------|---------|--|--|--|

| Pad    | Weigh           | nt 5 V  | Weigh   | t 3.3 V |  |  |  |

|        | $SRC^{(2)} = 0$ | SRC = 1 | SRC = 0 | SRC = 1 |  |  |  |

| PC[14] | 8%              | 8%      | 10%     | 10%     |  |  |  |

| PC[15] | 8%              | 11%     | 9%      | 10%     |  |  |  |

| PA[2]  | 8%              | 8%      | 9%      | 9%      |  |  |  |

| PE[0]  | 7%              | 7%      | 9%      | 9%      |  |  |  |

| PA[1]  | 7%              | 7%      | 8%      | 8%      |  |  |  |

| PE[1]  | 7%              | 10%     | 8%      | 8%      |  |  |  |

| PE[8]  | 6%              | 9%      | 8%      | 8%      |  |  |  |

| PE[9]  | 6%              | 6%      | 7%      | 7%      |  |  |  |

| PE[10] | 6%              | 6%      | 7%      | 7%      |  |  |  |

| PA[0]  | 5%              | 7%      | 6%      | 7%      |  |  |  |

| PE[11] | 5%              | 5%      | 6%      | 6%      |  |  |  |

| PC[11] | 7%              | 7%      | 9%      | 9%      |  |  |  |

| PC[10] | 8%              | 11%     | 9%      | 10%     |  |  |  |

| PB[0]  | 8%              | 11%     | 9%      | 10%     |  |  |  |

| PB[1]  | 8%              | 8%      | 10%     | 10%     |  |  |  |

| PC[6]  | 8%              | 8%      | 10%     | 10%     |  |  |  |

| PC[7]  | 8%              | 8%      | 10%     | 10%     |  |  |  |

| PA[15] | 8%              | 11%     | 9%      | 10%     |  |  |  |

| PA[14] | 7%              | 11%     | 9%      | 9%      |  |  |  |

| PA[4]  | 7%              | 7%      | 8%      | 8%      |  |  |  |

| PA[13] | 7%              | 10%     | 8%      | 9%      |  |  |  |

| PA[12] | 7%              | 7%      | 8%      | 8%      |  |  |  |

| PB[9]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| PB[8]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| PB[10] | 5%              | 5%      | 6%      | 6%      |  |  |  |

| PD[0]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| PD[1]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| PD[2]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| PD[3]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| PD[4]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| PD[5]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| PD[6]  | 1%              | 1%      | 1%      | 1%      |  |  |  |

| Symbol             |    | ~ | Deveneter                                                             | Conditions <sup>(1)</sup>                                              | Value |     |                                                                        | Unit |   |    |

|--------------------|----|---|-----------------------------------------------------------------------|------------------------------------------------------------------------|-------|-----|------------------------------------------------------------------------|------|---|----|

| Symbo              | DI | С | Parameter                                                             | Conditions                                                             | Min   | Тур | Max                                                                    | Unit |   |    |

|                    |    |   |                                                                       | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  |       | _   | 10                                                                     |      |   |    |

|                    |    |   | C <sub>L</sub> = 50 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | _                                                                      | —     | 20  |                                                                        |      |   |    |

| ÷                  |    |   | Output transition time<br>output pin <sup>(3)</sup>                   | C <sub>L</sub> = 100 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 |       | _   | 40                                                                     |      |   |    |

| t <sub>tr</sub> C  | СС |   | MEDIUM configuration                                                  | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | _     | —   | 12                                                                     | - ns |   |    |

|                    |    |   |                                                                       | C <sub>L</sub> = 50 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | _     | —   | 25                                                                     |      |   |    |

|                    |    |   |                                                                       |                                                                        |       |     | C <sub>L</sub> = 100 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | _    | — | 40 |

| W <sub>FRST</sub>  | SR |   | RESET input filtered pulse                                            | _                                                                      | _     | _   | 40                                                                     | ns   |   |    |

| W <sub>NFRST</sub> | SR |   | RESET input not filtered pulse                                        | —                                                                      | 1000  | —   | _                                                                      | ns   |   |    |

|                    |    |   |                                                                       | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                             | 10    | —   | 150                                                                    |      |   |    |

| I <sub>WPU</sub>   | сс | Р | Weak pull-up current<br>absolute value                                | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                             | 10    | —   | 150                                                                    | 0 µA |   |    |

|                    |    |   |                                                                       | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^{(4)}$           | 10    | —   | 250                                                                    |      |   |    |

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

2. This is a transient configuration during power-up, up to the end of reset PHASE2 (refer to RGM module section of the device reference manual).

3.  $C_L$  includes device and package capacitance ( $C_{PKG} < 5 \text{ pF}$ ).

The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only transient configuration during power-up. All pads but RESET are configured in input or in high impedance state.

## 4.9 **Power management electrical characteristics**

### 4.9.1 Voltage regulator electrical characteristics

The device implements an internal voltage regulator to generate the low voltage core supply  $V_{DD\_LV}$  from the high voltage ballast supply  $V_{DD\_BV}$ . The regulator itself is supplied by the common I/O supply  $V_{DD}$ . The following supplies are involved:

- HV: High voltage external power supply for voltage regulator module. This must be provided externally through V<sub>DD</sub> power pin.

- BV: High voltage external power supply for internal ballast module. This must be provided externally through V<sub>DD\_BV</sub> power pin. Voltage values should be aligned with V<sub>DD</sub>.

- LV: Low voltage internal power supply for core, FMPLL and flash digital logic. This is generated by the internal voltage regulator but provided outside to connect stability

The duration of the in-rush current depends on the capacitance placed on LV pins. BV decoupling capacitors must be sized accordingly. Refer to I<sub>MREG</sub> value for minimum amount of current to be provided in cc.

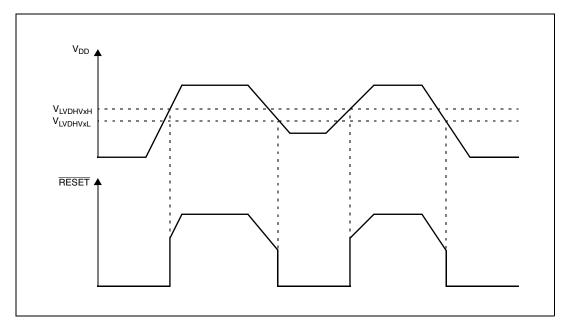

### 4.9.2 Low voltage detector electrical characteristics

The device implements a power-on reset (POR) module to ensure correct power-up initialization, as well as five low voltage detectors (LVDs) to monitor the  $V_{DD}$  and the  $V_{DD_{LV}}$  voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_POR in device reference manual)

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27 in device reference manual)

- LVDHV3B monitors V<sub>DD\_BV</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27\_VREG in device reference manual)

- LVDHV5 monitors V<sub>DD</sub> when application uses device in the 5.0 V ± 10% range (refer to RGM Functional Event Status (RGM\_FES) Register flag F\_LVD45 in device reference manual)

- LVDLVCOR monitors power domain No. 1 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD1 in device reference manual)

- LVDLVBKP monitors power domain No. 0 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD0 in device reference manual)

Figure 8. Low voltage detector vs reset

5/

| Table 26. Pow | ver consumption | on VDD_ | BV and VDD | _HV ( | (continued) |

|---------------|-----------------|---------|------------|-------|-------------|

|---------------|-----------------|---------|------------|-------|-------------|

| Symbol               | wind a l |   | Parameter                           | Conditions <sup>(1)</sup>   |                         |     | Value |      | Unit |

|----------------------|----------|---|-------------------------------------|-----------------------------|-------------------------|-----|-------|------|------|

| Symbol               |          | С | Farameter                           |                             |                         | Min | Тур   | Max  | Unit |

|                      |          | Ρ |                                     | Claw internal DC assillator | T <sub>A</sub> = 25 °C  | _   | 30    | 100  |      |

|                      |          | D |                                     |                             | T <sub>A</sub> = 55 °C  | _   | 75    | _    |      |

| I <sub>DDSTDBY</sub> | сс       | D | STANDBY mode current <sup>(9)</sup> |                             | T <sub>A</sub> = 85 °C  | _   | 180   | 700  | μA   |

|                      |          | D |                                     |                             | T <sub>A</sub> = 105 °C |     | 315   | 1000 |      |

|                      |          | Ρ |                                     |                             | T <sub>A</sub> = 125 °C | _   | 560   | 1700 |      |

1.  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C, unless otherwise specified

2. Running consumption does not include I/Os toggling which is highly dependent on the application. The given value is thought to be a worst case value with all peripherals running, and code fetched from code flash while modify operation ongoing on data flash. Notice that this value can be significantly reduced by application: switch off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

- 3. Higher current may be sinked by device during power-up and standby exit. Please refer to in-rush average current on *Table 24*.

- 4. RUN current measured with typical application with accesses on both flash memory and SRAM.

- Only for the "P" classification: Code fetched from SRAM: serial IPs CAN and LIN in loop-back mode, DSPI as Master, PLL as system clock (3 × Multiplier) peripherals on (eMIOS/CTU/ADC) and running at maximum frequency, periodic SW/WDG timer reset enabled.

- 6. Data flash power down. Code flash in low power. SIRC (128 kHz) and FIRC (16 MHz) on. 10 MHz XTAL clock. FlexCAN: 0 ON (clocked but no reception or transmission). LINFlex: instances: 0, 1, 2 ON (clocked but no reception or transmission), instance: 3 clocks gated. eMIOS: instance: 0 ON (16 channels on PA[0]–PA[11] and PC[12]–PC[15]) with PWM 20 kHz, instance: 1 clock gated. DSPI: instance: 0 (clocked but no communication). RTC/API ON.PIT ON. STM ON. ADC ON but no conversion except 2 analog watchdogs.

- 7. Only for the "P" classification: No clock, FIRC (16 MHz) off, SIRC (128 kHz) on, PLL off, HPVreg off, ULPVreg/LPVreg on. All possible peripherals off and clock gated. Flash in power down mode.

- 8. When going from RUN to STOP mode and the core consumption is > 6 mA, it is normal operation for the main regulator module to be kept on by the on-chip current monitoring circuit. This is most likely to occur with junction temperatures exceeding 125 °C and under these circumstances, it is possible for the current to initially exceed the maximum STOP specification by up to 2 mA. After entering stop, the application junction temperature will reduce to the ambient level and the main regulator will be automatically switched off when the load current is below 6 mA.

- 9. Only for the "P" classification: ULPVreg on, HP/LPVreg off, 16 KB SRAM on, device configured for minimum consumption, all possible modules switched off.

## 4.11 Flash memory electrical characteristics

The data flash operation depends strongly on the code flash operation. If code flash is switched-off, the data flash is disabled.

#### 4.11.1 **Program/Erase characteristics**

Table 27 shows the program and erase characteristics.

#### Table 27. Program and erase specifications (code flash)

|                         |    |   |                                                   | Value |                    |                               |                    |      |      |

|-------------------------|----|---|---------------------------------------------------|-------|--------------------|-------------------------------|--------------------|------|------|

| Symbol                  |    | С | Parameter                                         | Min   | Typ <sup>(1)</sup> | Initial<br>max <sup>(2)</sup> | Max <sup>(3)</sup> | Unit | Unit |

| t <sub>dwprogram</sub>  | СС | С | Double word (64 bits) program time <sup>(4)</sup> |       | 22                 | 50                            | 500                | μs   |      |

| t <sub>16Kpperase</sub> | СС | С | 16 KB block preprogram and erase time             |       | 300                | 500                           | 5000               | ms   | ]    |

| Symb               | Symbol |   | Parameter             | Conditions                                                                            |                               |   | Unit |     |      |

|--------------------|--------|---|-----------------------|---------------------------------------------------------------------------------------|-------------------------------|---|------|-----|------|

| Synib              |        | С | Falameter             |                                                                                       |                               |   | Тур  | Max | Unit |

| —                  | SR     |   | Scan range            | —                                                                                     | 0.150                         | — | 1000 | MHz |      |

| f <sub>CPU</sub>   | SR     |   | Operating frequency   | _                                                                                     |                               |   | 48   | —   | MHz  |

| V <sub>DD_LV</sub> | SR     |   | LV operating voltages | _                                                                                     | —                             |   |      | —   | V    |

| e                  |        |   | Deals lavel           | LQFP100 package                                                                       | No PLL frequency modulation   | _ | _    | 18  | dBµV |

| S <sub>EMI</sub>   |        | - |                       | Test conforming to IEC 61967-2,<br>f <sub>OSC</sub> = 8 MHz/f <sub>CPU</sub> = 48 MHz | ± 2% PLL frequency modulation | _ | _    | 14  | dBµV |

| Table 33. | EMI radiated | emission | measurement <sup>(1)(2)</sup> |

|-----------|--------------|----------|-------------------------------|

|-----------|--------------|----------|-------------------------------|

1. EMI testing and I/O port waveforms per IEC 61967-1, -2, -4

2. For information on conducted emission and susceptibility measurement (norm IEC 61967-4), please contact your local marketing representative.

### 4.12.3 Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n + 1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard. For more details, refer to the application note *Electrostatic Discharge Sensitivity Measurement* (AN1181).

| Table 34. | ESD absolute maximum ratings <sup>(</sup> | 1) (2) |

|-----------|-------------------------------------------|--------|

|-----------|-------------------------------------------|--------|

| Symbol                | Symbol |        | Ratings                                                   | Conditions                                         | Class | Max value     | Unit |

|-----------------------|--------|--------|-----------------------------------------------------------|----------------------------------------------------|-------|---------------|------|

| V <sub>ESD(HBM)</sub> | C<br>C | Т      | Electrostatic discharge voltage<br>(Human Body Model)     | $T_A = 25 \degree C$<br>conforming to AEC-Q100-002 | H1C   | 2000          | V    |

| V <sub>ESD(MM)</sub>  | C<br>C | Т      | Electrostatic discharge voltage (Machine Model)           | $T_A = 25 \degree C$<br>conforming to AEC-Q100-003 | M2    | 200           | V    |

| V                     | С      | с<br>с | Electrostatic discharge voltage<br>(Charged Device Model) | T <sub>A</sub> = 25 °C                             | СЗА   | 500           | V    |

| V <sub>ESD(CDM)</sub> | С      |        | (Charged Device Model)                                    | conforming to AEC-Q100-011                         | USA   | 750 (corners) | V    |

1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

2. A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Nominal<br>frequency<br>(MHz) | NDK crystal<br>reference | Crystal<br>equivalent<br>series<br>resistance<br>(ESR) Ω | Crystal<br>motional<br>capacitance<br>(C <sub>m</sub> ) fF | Crystal<br>motional<br>inductance<br>(L <sub>m</sub> ) mH | Load on<br>xtalin/xtalout<br>C <sub>1</sub> = C <sub>2</sub> (pF) <sup>(1)</sup> | Shunt<br>capacitance<br>between xtalout<br>and xtalin<br>C0 <sup>(2)</sup> (pF) |

|-------------------------------|--------------------------|----------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 4                             | NX8045GB                 | 300                                                      | 2.68                                                       | 591.0                                                     | 21                                                                               | 2.93                                                                            |

| 8                             |                          | 300                                                      | 2.46                                                       | 160.7                                                     | 17                                                                               | 3.01                                                                            |

| 10                            |                          | 150                                                      | 2.93                                                       | 86.6                                                      | 15                                                                               | 2.91                                                                            |

| 12                            | NX5032GA                 | 120                                                      | 3.11                                                       | 56.5                                                      | 15                                                                               | 2.93                                                                            |

| 16                            |                          | 120                                                      | 3.90                                                       | 25.3                                                      | 10                                                                               | 3.00                                                                            |

Table 36.Crystal description

1. The values specified for C1 and C2 are the same as used in simulations. It should be ensured that the testing includes all the parasitics (from the board, probe, crystal, etc.) as the AC / transient behavior depends upon them.

2. The value of C0 specified here includes 2 pF additional capacitance for parasitics (to be seen with bond-pads, package, etc.).

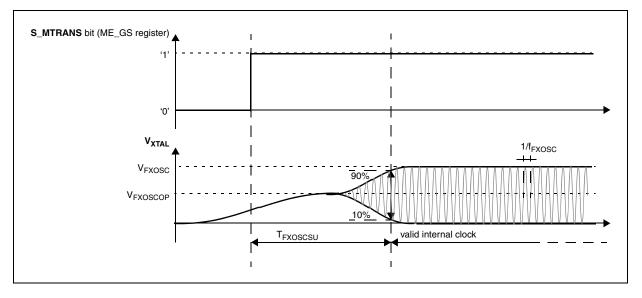

Figure 10. Fast external crystal oscillator (4 to 16 MHz) timing diagram

| Table 37. | Fast external cr | vstal oscillator (4 | 4 to 16 MHz | electrical characteristics |

|-----------|------------------|---------------------|-------------|----------------------------|

|           |                  |                     |             |                            |

| Symbol             | Symbol |   |                                               |            |     | Conditions <sup>(1)</sup> |      | Unit |

|--------------------|--------|---|-----------------------------------------------|------------|-----|---------------------------|------|------|

| Symbol             |        | C | Farameter                                     | Conditions | Min | Тур                       | Мах  | Onit |

| f <sub>FXOSC</sub> | SR     |   | Fast external crystal<br>oscillator frequency | _          | 4.0 |                           | 16.0 | MHz  |

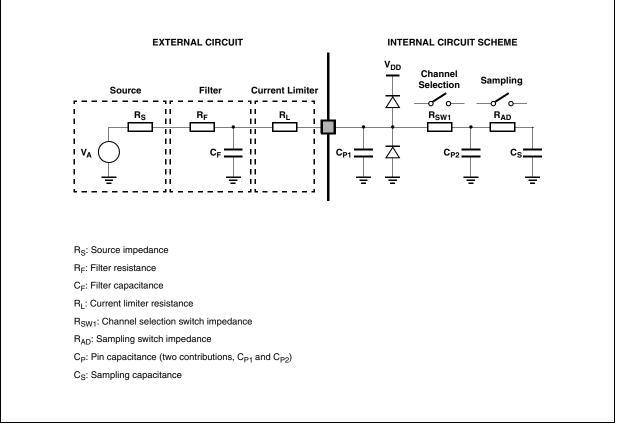

Figure 12. Input equivalent circuit (precise channels)

| Symbol                     | Symbol |   | Parameter                                               |                                                                                                                                     | Conditions                                                               | Typical value <sup>(2)</sup> | Unit |

|----------------------------|--------|---|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------|------|

|                            |        |   |                                                         | Ballast static                                                                                                                      | consumption (only clocked)                                               | 1                            | μA   |

| I <sub>DD_BV(SPI)</sub> CC |        | т | SPI (DSPI) supply<br>current on V <sub>DD_BV</sub>      | Ballast dynamic consumption (continuous<br>communication):<br>– Baudrate: 2 Mbit/s<br>– Transmission every 8 µs<br>– Frame: 16 bits |                                                                          | 16 × f <sub>periph</sub>     | μΑ   |

|                            |        |   |                                                         |                                                                                                                                     | Ballast static consumption (no conversion)                               | $41 \times f_{periph}$       | μA   |

| I <sub>DD_BV(ADC)</sub>    | СС     | Т | ADC supply current on<br>V <sub>DD_BV</sub>             | V <sub>DD</sub> = 5.5 V                                                                                                             | Ballast dynamic<br>consumption (continuous<br>conversion) <sup>(3)</sup> | $5 	imes f_{periph}$         | μA   |

|                            |        | т |                                                         |                                                                                                                                     | Analog static consumption<br>(no conversion)                             | $2 	imes f_{periph}$         | μA   |

| IDD_HV_ADC(ADC)            | CC     |   | ADC supply current on<br>V <sub>DD_HV_ADC</sub>         | V <sub>DD</sub> = 5.5 V                                                                                                             | Analog dynamic<br>consumption (continuous<br>conversion)                 | $75 	imes f_{periph} + 32$   | μA   |

| I <sub>DD_HV</sub> (FLASH) | сс     | Т | CFlash + DFlash supply<br>current on V <sub>DD_HV</sub> | V <sub>DD</sub> = 5.5 V —                                                                                                           |                                                                          | 8.21                         | mA   |

| I <sub>DD_HV(PLL)</sub>    | сс     | т | PLL supply current on<br>V <sub>DD_HV</sub>             | V <sub>DD</sub> = 5.5 V                                                                                                             | _                                                                        | $30 	imes f_{periph}$        | μΑ   |

| Table 43. | On-chip peripherals curren | t consumption <sup>(1)</sup> | (continued) |

|-----------|----------------------------|------------------------------|-------------|

|-----------|----------------------------|------------------------------|-------------|

1. Operating conditions:  $T_A = 25 \text{ °C}$ ,  $f_{periph} = 8 \text{ MHz}$  to 48 MHz

2.  $f_{periph}$  is an absolute value.

3. During the conversion, the total current consumption is given from the sum of the static and dynamic consumption, i.e.,  $(41 + 5) \times f_{periph}$ .

## 4.18.2 DSPI characteristics

| Table 44. | DSPI characteristics <sup>(1)</sup> |  |

|-----------|-------------------------------------|--|

|-----------|-------------------------------------|--|

| No. | Symbol                |                | С | Parameter                         |                           | DSPI0/DSPI1 |     |                  | Unit |

|-----|-----------------------|----------------|---|-----------------------------------|---------------------------|-------------|-----|------------------|------|

| NO. |                       |                | C |                                   |                           | Min         | Тур | Max              | Unit |

|     |                       | SR D<br>D<br>D | D | SCK cycle time                    | Master mode<br>(MTFE = 0) | 125         | _   | _                | - ns |

| 1   | 1 t <sub>SCK</sub> SF |                | D |                                   | Slave mode<br>(MTFE = 0)  | 125         | _   | _                |      |

| 1   |                       |                | D |                                   | Master mode<br>(MTFE = 1) | 83          | _   | _                |      |

|     |                       |                | D |                                   | Slave mode<br>(MTFE = 1)  | 83          | _   | _                |      |

| _   | f <sub>DSPI</sub>     | SR             | D | DSPI digital controller frequency |                           | —           | _   | f <sub>CPU</sub> | MHz  |

| Cumbal    |        | mm     |        | inches <sup>(1)</sup> |        |        |  |

|-----------|--------|--------|--------|-----------------------|--------|--------|--|

| Symbol    | Min    | Тур    | Мах    | Min                   | Тур    | Max    |  |

| А         | _      | —      | 1.600  | —                     | —      | 0.0630 |  |

| A1        | 0.050  | —      | 0.150  | 0.0020                |        | 0.0059 |  |

| A2        | 1.350  | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b         | 0.170  | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С         | 0.090  | —      | 0.200  | 0.0035                | —      | 0.0079 |  |

| D         | 15.800 | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1        | 13.800 | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3        | _      | 12.000 | _      | _                     | 0.4724 | —      |  |

| Е         | 15.800 | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1        | 13.800 | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3        | _      | 12.000 | _      | _                     | 0.4724 | —      |  |

| е         | _      | 0.500  | —      | _                     | 0.0197 | —      |  |

| L         | 0.450  | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1        | _      | 1.000  | —      | —                     | 0.0394 | —      |  |

| k         | 0.0 °  | 3.5 °  | 7.0 °  | 0.0 °                 | 3.5 °  | 7.0 °  |  |

| Tolerance | mm     |        |        | inches                |        |        |  |

| CCC       |        | 0.080  |        |                       | 0.0031 |        |  |

#### Table 46. LQFP100 mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

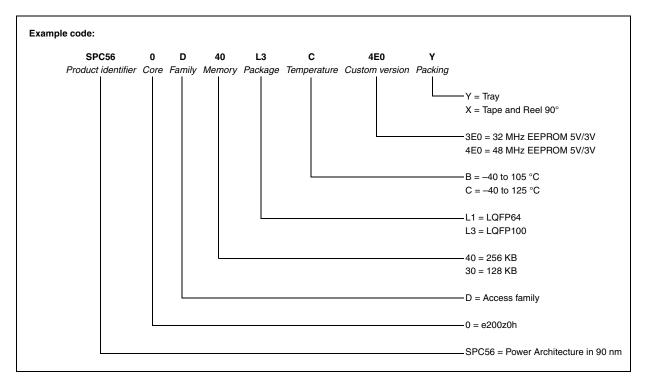

Figure 28. Commercial product code structure

# Appendix A Abbreviations

Table 50 lists abbreviations used in this document.

| Table 50. Ab | breviations                                                          |  |  |  |  |

|--------------|----------------------------------------------------------------------|--|--|--|--|

| Abbreviation | Meaning                                                              |  |  |  |  |

| APU          | Auxilliary processing unit                                           |  |  |  |  |

| CMOS         | Complementary metal-oxide-semiconductor                              |  |  |  |  |

| CPHA         | Clock phase                                                          |  |  |  |  |

| CPOL         | Clock polarity                                                       |  |  |  |  |

| CS           | Peripheral chip select                                               |  |  |  |  |

| DAOC         | Double action output compare                                         |  |  |  |  |

| ECC          | Error code correction                                                |  |  |  |  |

| EVTO         | Event out                                                            |  |  |  |  |

| GPIO         | General purpose input/output                                         |  |  |  |  |

| IPM          | Input period measurement                                             |  |  |  |  |

| IPWM         | Input pulse width measurement                                        |  |  |  |  |

| MB           | Message buffer                                                       |  |  |  |  |

| MC           | Modulus counter                                                      |  |  |  |  |

| МСВ          | Modulus counter buffered (up / down)                                 |  |  |  |  |

| МСКО         | Message clock out                                                    |  |  |  |  |

| MDO          | Message data out                                                     |  |  |  |  |

| MSEO         | Message start/end out                                                |  |  |  |  |

| MTFE         | Modified timing format enable                                        |  |  |  |  |

| NVUSRO       | Non-volatile user options register                                   |  |  |  |  |

| OPWFMB       | Output pulse width and frequency modulation buffered                 |  |  |  |  |

| OPWMB        | Output pulse width modulation buffered                               |  |  |  |  |

| OPWMCB       | Center aligned output pulse width modulation buffered with dead time |  |  |  |  |

| OPWMT        | Output pulse width modulation trigger                                |  |  |  |  |

| PWM          | Pulse width modulation                                               |  |  |  |  |

| SAIC         | Single action input capture                                          |  |  |  |  |

| SAOC         | Single action output compare                                         |  |  |  |  |

| SCK          | Serial communications clock                                          |  |  |  |  |

| SOUT         | Serial data out                                                      |  |  |  |  |

| TBD          | To be defined                                                        |  |  |  |  |

| TCK          | Test clock input                                                     |  |  |  |  |

| TDI          | Test data input                                                      |  |  |  |  |

Table 50. Abbreviations

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 04-Feb-2013 | 6        | <ul> <li>Removed all instances of table footnote "All values need to be confirmed during device validation"</li> <li>Section 4.1, Introduction, removed Caution note.</li> <li>Table 11 (Recommended operating conditions (3.3 V)), added minimum value of T<sub>VDD</sub> and footnote about it.</li> <li>Table 12 (Recommended operating conditions (5.0 V)), added minimum value of T<sub>VDD</sub> and footnote about it.</li> <li>Updated Section 4.17.2, Input impedance and ADC accuracy In Table 24, changed V<sub>LVDHV3L</sub>, V<sub>LVDHV3BL</sub> from 2.7 V to 2.6 V.</li> <li>Revised the Table 28 (Flash module life)</li> <li>Updated Table 43, DSPI characteristics, to add specifications 7 and 8, t<sub>PCSC</sub> and t<sub>PASC</sub>.</li> <li>Inserted Figure 24, DSPI PCS strobe (PCSS) timing.</li> </ul> |  |  |

| 17-Sep-2013 | 7        | Updated Disclaimer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Table 51. | Document revision history (continu | (beu |

|-----------|------------------------------------|------|

|-----------|------------------------------------|------|