Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 45                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16К х 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560d40l1b4e0x |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

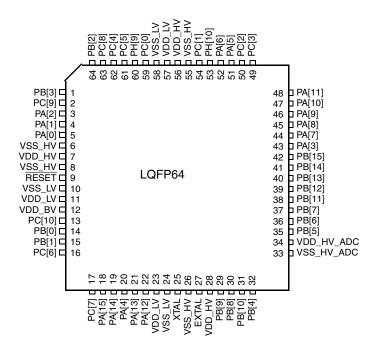

*Figure 3* shows the Pictus 512K in the LQFP64 package.

Figure 3. LQFP64 pin configuration (top view)

## 3.2 Pad configuration during reset phases

All pads have a fixed configuration under reset.

During the power-up phase, all pads are forced to tristate.

After power-up phase, all pads are forced to tristate with the following exceptions:

- PA[9] (FAB) is pull-down. Without external strong pull-up the device starts fetching from flash.

- PA[8] (ABS[0]) is pull-up.

- RESET pad is driven low. This is pull-up only after PHASE2 reset completion.

- JTAG pads (TCK, TMS and TDI) are pull-up while TDO remains tristate.

- Precise ADC pads (PB[7:4] and PD[11:0]) are left tristate (no output buffer available).

- Main oscillator pads (EXTAL, XTAL) are tristate.

# 3.3 Voltage supply pins

Voltage supply pins are used to provide power to the device. Two dedicated pins are used for 1.2 V regulator stabilization.

### Table 4. Voltage supply pin descriptions

| Port nin | Function                                                                                                                              | Pin number       |                           |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|--|--|

| Port pin | Function                                                                                                                              | LQFP64           | LQFP100                   |  |  |

| VDD_HV   | Digital supply voltage                                                                                                                | 7, 28, 34, 56    | 15, 37, 52, 70, 84        |  |  |

| VSS_HV   | Digital ground                                                                                                                        | 6, 8, 26, 33, 55 | 14, 16, 35, 51, 69,<br>83 |  |  |

| VDD_LV   | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{SS\_LV}$ pin.^{(1)}               | 11, 23, 57       | 19, 32, 85                |  |  |

| VSS_LV   | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{\text{DD}\_\text{LV}}$ pin.^{(1)} | 10, 24, 58       | 18, 33, 86                |  |  |

| VDD_BV   | Internal regulator supply voltage                                                                                                     | 12               | 20                        |  |  |

1. A decoupling capacitor must be placed between each of the three VDD\_LV/VSS\_LV supply pairs to ensure stable voltage (see the recommended operating conditions in the device datasheet for details).

# 3.4 Pad types

In the device the following types of pads are available for system pins and functional port pins:

$S = Slow^{(a)}$

M = Medium<sup>(a) (b)</sup>

$F = Fast^{(a)}$  (b)

I = Input only with analog feature<sup>(a)</sup>

J = Input/Output ('S' pad) with analog feature

X = Oscillator

# 3.5 System pins

The system pins are listed in Table 5.

### Table 5. System pin descriptions

| Port pin |       | Function                                                                   | I/O       | Pad type | RESET                                       | Pin number |         |

|----------|-------|----------------------------------------------------------------------------|-----------|----------|---------------------------------------------|------------|---------|

|          |       | Function                                                                   | direction | rau type | configuration                               | LQFP64     | LQFP100 |

|          | RESEL | Bidirectional reset with Schmitt-Trigger characteristics and noise filter. | I/O       | Μ        | Input, weak<br>pull-up only<br>after PHASE2 | 9          | 17      |

b. All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium (see the PCR[SRC] description in the device reference manual).

a. See the I/O pad electrical characteristics in the device datasheet for details.

| Table 6. | Functional port pin descriptions (continued) |  |

|----------|----------------------------------------------|--|

|----------|----------------------------------------------|--|

|          |        |                                      |                        |             | I/O              |             | T<br>ation             | Pin number |         |

|----------|--------|--------------------------------------|------------------------|-------------|------------------|-------------|------------------------|------------|---------|

| Port pin | PCR    | Alternate<br>function <sup>(1)</sup> | Function               | Peripheral  | direction<br>(2) | Pad<br>type | RESET<br>configuration | LQFP64     | LQFP100 |

|          |        | AF0                                  | GPIO[3]                | SIUL        | I/O              |             |                        |            |         |

|          |        | AF1                                  | E0UC[3]                | eMIOS_0     | I/O              |             |                        |            |         |

| PA[3]    | PCR[3] | AF2                                  | —                      | —           | —<br>            | S           | Tristate               | 43         | 68      |

|          |        | AF3                                  | CS4_0                  | DSPI_0      | I/O              |             |                        |            |         |

|          |        | _                                    | EIRQ[0]                | SIUL<br>ADC |                  |             |                        |            |         |

|          |        |                                      | ADC1_S[0]              |             |                  |             |                        |            |         |

|          |        | AF0                                  | GPIO[4]                | SIUL        | I/O              |             |                        |            |         |

|          |        | AF1                                  | E0UC[4]                | eMIOS_0     | I/O              | -           |                        |            |         |

| PA[4]    | PCR[4] | AF2                                  | —                      | —           | —<br>            | S           | Tristate               | 20         | 29      |

|          |        | AF3                                  | CS0_1                  | DSPI_1      | I/O              |             |                        |            |         |

|          |        | —                                    | WKPU[9] <sup>(3)</sup> | WKPU        |                  |             |                        |            |         |

|          |        | AF0                                  | GPIO[5]                | SIUL        | I/O              |             |                        |            |         |

| PA[5]    | PCR[5] | AF1                                  | E0UC[5]                | eMIOS_0     | I/O              | м           | M Tristate             | 51         | 79      |

| [-]      | [.]    | AF2                                  | —                      | —           | —                |             |                        |            |         |

|          |        | AF3                                  | —                      | —           | _                |             |                        |            |         |

|          |        | AF0                                  | GPIO[6]                | SIUL        | I/O              |             |                        |            |         |

|          |        | AF1                                  | E0UC[6]                | eMIOS_0     | I/O              |             |                        |            |         |

| PA[6]    | PCR[6] | AF2                                  | —                      | —           | —                | S           | Tristate               | 52         | 80      |

|          |        | AF3                                  | CS1_1                  | DSPI_1      | I/O              |             |                        |            |         |

|          |        |                                      | EIRQ[1]                | SIUL        | -                |             |                        |            |         |

|          |        | AF0                                  | GPIO[7]                | SIUL        | I/O              |             |                        |            |         |

|          |        | AF1                                  | E0UC[7]                | eMIOS_0     | I/O              |             |                        |            |         |

| PA[7]    | PCR[7] | AF2                                  | —                      | —           | —                | s           | Tristate               | 44         | 71      |

| FA[7]    | FON[7] | AF3                                  | —                      | —           | —                | 3           | mstate                 | 44         | / 1     |

|          |        | —                                    | EIRQ[2]                | SIUL        | I                |             |                        |            |         |

|          |        | —                                    | ADC1_S[1]              | ADC         | -                |             |                        |            |         |

|          |        | AF0                                  | GPIO[8]                | SIUL        | I/O              |             |                        |            |         |

|          |        | AF1                                  | E0UC[8]                | eMIOS_0     | I/O              |             |                        |            |         |

| PA[8]    | PCR[8] | AF2                                  | E0UC[14]               | eMIOS_0     | —                | s           | Input, weak            | 45         | 72      |

| FA[0]    | FUN[0] | AF3                                  | —                      | —           | —                | 3           | pull-up                | 40         | 12      |

|          |        | —                                    | EIRQ[3]                | SIUL        | I                |             |                        |            |         |

|          |        | N/A <sup>(5)</sup>                   | ABS[0]                 | BAM         | I                |             |                        |            |         |

|          |        | AF0                                  | GPIO[9]                | SIUL        | I/O              |             |                        |            |         |

|          |        | AF1                                  | E0UC[9]                | eMIOS_0     | I/O              |             |                        |            |         |

| PA[9]    | PCR[9] | AF2                                  | —                      | _           | —                | S           | Pull-down              | 46         | 73      |

|          |        | AF3                                  | CS2_1                  | DSPI_1      | I/O              |             |                        |            |         |

|          |        | N/A <sup>(5)</sup>                   | FAB                    | BAM         | I                |             |                        |            |         |

| Table 6. | Functional port pin descriptions (continued) |

|----------|----------------------------------------------|

|----------|----------------------------------------------|

|          |          | Alternate I/O                        |                                   | Devi              | T<br>ation       | Pin number  |                        |        |         |

|----------|----------|--------------------------------------|-----------------------------------|-------------------|------------------|-------------|------------------------|--------|---------|

| Port pin | PCR      | Alternate<br>function <sup>(1)</sup> | Function                          | Peripheral        | direction<br>(2) | Pad<br>type | RESET<br>configuration | LQFP64 | LQFP100 |

|          |          | AF0                                  | GPIO[17]                          | SIUL              | I/O              |             |                        |        |         |

|          |          | AF1                                  | —                                 |                   | —                |             |                        |        |         |

| PB[1]    | PCR[17]  | AF2                                  |                                   |                   |                  | s           | Tristate               | 15     | 24      |

|          |          | AF3                                  | LIN0RX<br>WKPU[4] <sup>(3)</sup>  | LINFlex_0<br>WKPU |                  |             |                        |        |         |

|          |          | _                                    | CANORX                            | FlexCAN_0         | I                |             |                        |        |         |

|          |          | AF0                                  | GPIO[18]                          | SIUL              | I/O              |             |                        |        |         |

| וסוסס    |          | AF1                                  | LINOTX                            | LINFlex_0         | 0                | 5.4         | Triatata               | 64     | 100     |

| PB[2]    | PCR[18]  | AF2                                  |                                   | —                 | —                | М           | Tristate               | 64     | 100     |

|          |          | AF3                                  | _                                 |                   |                  |             |                        |        |         |

|          |          | AF0                                  | GPIO[19]                          | SIUL              | I/O              |             |                        |        |         |

|          |          | AF1                                  |                                   | —                 | —                |             |                        |        |         |

| PB[3]    | PCR[19]  | AF2                                  | —                                 |                   | —                | s           | Tristate               | 1      | 1       |

|          |          | AF3                                  |                                   |                   |                  |             |                        |        |         |

|          |          | _                                    | WKPU[11] <sup>(3)</sup><br>LIN0RX | WKPU<br>LINFlex_0 |                  |             |                        |        |         |

|          |          |                                      |                                   |                   | I                |             |                        |        |         |

|          |          | AF0<br>AF1                           | GPIO[20]                          | SIUL              | I                |             |                        |        |         |

| PB[4]    | PCR[20]  | AF1<br>AF2                           | _                                 |                   |                  | I           | Tristate               | 32     | 50      |

|          | i on(20) | AF3                                  | _                                 | _                 |                  |             | motate                 | 02     | 50      |

|          |          | _                                    | ADC1_P[0]                         | ADC               | I                |             |                        |        |         |

|          |          | AF0                                  | GPIO[21]                          | SIUL              | I                |             |                        |        |         |

|          |          | AF1                                  | —                                 | —                 | —                |             |                        |        |         |

| PB[5]    | PCR[21]  | AF2                                  | —                                 | —                 | —                | - I         | Tristate               | 35     | 53      |

|          |          | AF3                                  | —                                 | —                 | —                |             |                        |        |         |

|          |          | —                                    | ADC1_P[1]                         | ADC               | I                |             |                        |        |         |

|          |          | AF0                                  | GPIO[22]                          | SIUL              | I                |             |                        |        |         |

|          |          | AF1                                  |                                   | —                 | —                |             |                        |        |         |

| PB[6]    | PCR[22]  | AF2                                  | —                                 |                   | —                | I           | Tristate               | 36     | 54      |

|          |          | AF3                                  |                                   |                   |                  |             |                        |        |         |

| -        |          | -                                    | ADC1_P[2]                         | ADC               | <br>             |             |                        |        |         |

|          |          | AF0                                  | GPIO[23]                          | SIUL              | I                |             |                        |        |         |

| PB[7]    | PCR[23]  | AF1<br>AF2                           | _                                 | _                 | _                | ,           | Tristate               | 37     | 55      |

|          | ԲՆՈ[ՀᲐ]  | AF2<br>AF3                           | _                                 |                   | _                | I           | mstate                 | 57     | 55      |

|          |          | —                                    | ADC1_P[3]                         | ADC               | I                |             |                        |        |         |

|          |         | Altowards I/O                        |                                      |             | T<br>Ition       | Pin number  |                        |        |         |

|----------|---------|--------------------------------------|--------------------------------------|-------------|------------------|-------------|------------------------|--------|---------|

| Port pin | PCR     | Alternate<br>function <sup>(1)</sup> | Function                             | Peripheral  | direction<br>(2) | Pad<br>type | RESET<br>configuration | LQFP64 | LQFP100 |

|          |         | AF0                                  | GPIO[24]                             | SIUL        | I                |             |                        |        |         |

|          |         | AF1                                  | —                                    |             | —                |             |                        |        |         |

| PB[8]    | PCR[24] | AF2                                  |                                      | —           | —                | I           | Tristate               | 30     | 39      |

|          |         | AF3                                  |                                      | -           |                  |             |                        |        |         |

|          |         | _                                    | ADC1_S[4]<br>WKPU[25] <sup>(3)</sup> | ADC<br>WKPU |                  |             |                        |        |         |

|          |         |                                      |                                      |             | I                |             |                        |        |         |

|          |         | AF0                                  | GPIO[25]                             | SIUL        | I                |             |                        |        |         |

|          |         | AF1                                  |                                      | —           | —                |             |                        |        |         |

| PB[9]    | PCR[25] | AF2                                  |                                      | —           | —                | I           | Tristate               | 29     | 38      |

|          |         | AF3                                  |                                      | -           |                  |             |                        |        |         |

|          |         | _                                    | ADC1_S[5]<br>WKPU[26] <sup>(3)</sup> | ADC<br>WKPU |                  |             |                        |        |         |

|          |         |                                      |                                      |             |                  |             |                        |        |         |

|          |         | AF0                                  | GPIO[26]                             | SIUL        | I/O              |             |                        |        |         |

|          |         | AF1                                  |                                      | _           | _                |             |                        |        |         |

| PB[10]   | PCR[26] | AF2                                  | _                                    |             |                  | J           | Tristate               | 31     | 40      |

|          |         | AF3                                  |                                      | ADC         |                  |             |                        |        |         |

|          |         | _                                    | ADC1_S[6]<br>WKPU[8] <sup>(3)</sup>  | WKPU        |                  |             |                        |        |         |

|          |         |                                      |                                      |             |                  |             |                        |        |         |

|          |         | AF0                                  | GPIO[27]                             | SIUL        | I/O              |             |                        |        |         |

| 00(141   |         | AF1                                  | E0UC[3]                              | eMIOS_0     | I/O              |             | Triatata               | 00     | 50      |

| PB[11]   | PCR[27] | AF2<br>AF3                           | <br>CS0_0                            | DSPI_0      | —<br>I/O         | J           | Tristate               | 38     | 59      |

|          |         | AF3<br>—                             | ADC1_S[12]                           | ADC         | 1/0              |             |                        |        |         |

|          |         |                                      |                                      |             |                  |             |                        |        |         |

|          |         | AF0                                  | GPIO[28]                             | SIUL        | I/O              |             |                        |        |         |

|          |         | AF1<br>AF2                           | E0UC[4]                              | eMIOS_0     | I/O              |             | Tristate               | 39     | 61      |

| PB[12]   | PCR[28] | AF2<br>AF3                           | <br>CS1_0                            | DSPI_0      | 0                | J           | Instate                | 39     | 61      |

|          |         | —<br>—                               | ADC1_X[0]                            | ADC         | I                |             |                        |        |         |

|          |         |                                      |                                      |             |                  |             |                        |        |         |

|          |         | AF0                                  | GPIO[29]                             | SIUL        | I/O              |             |                        |        |         |

| DD[10]   | DCD[20] | AF1                                  | E0UC[5]                              | eMIOS_0     | I/O              |             | Triototo               | 40     | 63      |

| PB[13]   | PCR[29] | AF2<br>AF3                           | <br>CS2_0                            | DSPI_0      | 0                | J           | Tristate               | 40     | 03      |

|          |         | AF3<br>—                             | ADC1_X[1]                            | ADC         | I                |             |                        |        |         |

|          |         |                                      |                                      |             |                  |             |                        |        |         |

|          |         | AF0                                  | GPIO[30]                             | SIUL        | I/O              |             |                        |        |         |

|          |         | AF1<br>AF2                           | E0UC[6]                              | eMIOS_0     | I/O              |             | Triat                  | 41     | 05      |

| PB[14]   | PCR[30] | AF2<br>AF3                           | <br>CS3_0                            | DSPI_0      | 0                | J           | Tristate               | 41     | 65      |

|          |         | нго<br>—                             | ADC1_X[2]                            | ADC         |                  |             |                        |        |         |

|          |         |                                      |                                      | ADC         |                  |             |                        |        |         |

| Table 6. | Functional | port p | in descri | ptions ( | (continued) | ) |

|----------|------------|--------|-----------|----------|-------------|---|

|          |            |        |           |          |             |   |

|          |         |                                      |                | I/O        |                  | T<br>ation  | Pin number             |        |         |

|----------|---------|--------------------------------------|----------------|------------|------------------|-------------|------------------------|--------|---------|

| Port pin | PCR     | Alternate<br>function <sup>(1)</sup> | Function       | Peripheral | direction<br>(2) | Pad<br>type | RESET<br>configuration | LQFP64 | LQFP100 |

|          |         | AF0                                  | GPIO[54]       | SIUL       | I                |             |                        |        |         |

| DDIel    |         | AF1                                  | —              | —          | —                |             | Triatata               |        | 47      |

| PD[6]    | PCR[54] | AF2<br>AF3                           | _              | _          |                  | I           | Tristate               |        | 47      |

|          |         | —                                    | ADC1_P[10]     | ADC        | I                |             |                        |        |         |

|          |         | AF0                                  | GPIO[55]       | SIUL       | l                |             |                        |        |         |

|          |         | AF1                                  | —              | —          | —                |             |                        |        |         |

| PD[7]    | PCR[55] | AF2                                  | —              | —          | —                | Ι           | Tristate               | —      | 48      |

|          |         | AF3                                  | —              | —          | —                |             |                        |        |         |

|          |         | —                                    | ADC1_P[11]     | ADC        | Ι                |             |                        |        |         |

|          |         | AF0                                  | GPIO[56]       | SIUL       | I                |             |                        |        |         |

|          |         | AF1                                  | —              | —          | —                |             |                        |        |         |

| PD[8]    | PCR[56] | AF2                                  | —              | —          | —                | Ι           | Tristate               | —      | 49      |

|          |         | AF3                                  | —              | —          | —                |             |                        |        |         |

|          |         | —                                    | ADC1_P[12]     | ADC        | I                |             |                        |        |         |

|          |         | AF0                                  | GPIO[57]       | SIUL       | I                |             |                        |        |         |

|          |         | AF1                                  | —              | —          | —                |             |                        |        |         |

| PD[9]    | PCR[57] | AF2                                  | —              | —          | —                | Ι           | Tristate               | —      | 56      |

|          |         | AF3                                  | —              | _          |                  |             |                        |        |         |

|          |         | —                                    | ADC1_P[13]     | ADC        | I                |             |                        |        |         |

|          |         | AF0                                  | GPIO[58]       | SIUL       | I                |             |                        |        |         |

|          |         | AF1                                  | —              | —          | —                |             |                        |        |         |

| PD[10]   | PCR[58] | AF2                                  | —              | —          | —                | I           | Tristate               | —      | 57      |

|          |         | AF3                                  |                | ADC        |                  |             |                        |        |         |

|          |         | —                                    | ADC1_P[14]     |            |                  |             |                        |        |         |

|          |         | AF0                                  | GPIO[59]       | SIUL       | I                |             |                        |        |         |

|          |         | AF1                                  | _              | _          | _                |             | Triatata               |        | 50      |

| PD[11]   | PCR[59] | AF2<br>AF3                           |                | _          |                  | I           | Tristate               |        | 58      |

|          |         | AF3<br>—                             | <br>ADC1_P[15] | ADC        | -                |             |                        |        |         |

|          |         | AF0                                  | GPIO[60]       | SIUL       | I/O              |             |                        |        |         |

|          |         | AF1                                  | CS5_0          | DSPI_0     | 0                |             |                        |        |         |

| PD[12]   | PCR[60] | AF2                                  | <br>E0UC[24]   | eMIOS_0    | I/O              | J           | Tristate               | _      | 60      |

|          |         | AF3                                  |                | _          | —                |             |                        |        |         |

|          |         | —                                    | ADC1_S[8]      | ADC        | I                |             |                        |        |         |

|          |         | AF0                                  | GPIO[61]       | SIUL       | I/O              |             |                        |        |         |

|          |         | AF1                                  | CS0_1          | DSPI_1     | I/O              | J           |                        |        | 62      |

| PD[13]   | PCR[61] | AF2                                  | E0UC[25]       | eMIOS_0    | I/O              |             | Tristate               | —      |         |

|          |         | AF3                                  | —              | —          | —                |             |                        |        |         |

|          |         | —                                    | ADC1_S[9]      | ADC        | l                |             |                        |        |         |

Table 6.

Functional port pin descriptions (continued)

| Table 6. | Func    | lional port                          | pin descrip            | tions (cont | inuea)           |             |                        |            |         |

|----------|---------|--------------------------------------|------------------------|-------------|------------------|-------------|------------------------|------------|---------|

|          |         |                                      |                        | I/O         |                  | Dead        | atio                   | Pin number |         |

| Port pin | PCR     | Alternate<br>function <sup>(1)</sup> | Function               | Peripheral  | direction<br>(2) | Pad<br>type | RESET<br>configuration | LQFP64     | LQFP100 |

|          |         | AF0                                  | GPIO[62]               | SIUL        | I/O              |             |                        |            |         |

|          |         | AF1                                  | CS1_1                  | DSPI_1      | 0                |             |                        |            |         |

| PD[14]   | PCR[62] | AF2                                  | E0UC[26]               | eMIOS_0     | I/O              | J           | Tristate               | —          | 64      |

|          |         | AF3                                  | —                      | -           | _                |             |                        |            |         |

|          |         | —                                    | ADC1_S[10]             | ADC         | I                |             |                        |            |         |

|          |         | AF0                                  | GPIO[63]               | SIUL        | I/O              |             |                        |            |         |

|          |         | AF1                                  | CS2_1                  | DSPI_1      | 0                |             |                        |            |         |

| PD[15]   | PCR[63] | AF2                                  | E0UC[27]               | eMIOS_0     | I/O              | J           | Tristate               | —          | 66      |

|          |         | AF3                                  | _                      | —           | —                |             |                        |            |         |

|          |         | —                                    | ADC1_S[11]             | ADC         | I                |             |                        |            |         |

|          |         |                                      |                        | Port        | E                |             |                        |            |         |

|          |         | AF0                                  | GPIO[64]               | SIUL        | I/O              |             |                        |            |         |

|          |         | AF1                                  | E0UC[16]               | eMIOS_0     | I/O              |             |                        |            |         |

| PE[0]    | PCR[64] | AF2                                  | —                      | —           | —                | S           | Tristate               | —          | 6       |

|          |         | AF3                                  | —                      | —           | —                |             |                        |            |         |

|          |         | —                                    | WKPU[6] <sup>(3)</sup> | WKPU        | I                |             |                        |            |         |

|          |         | AF0                                  | GPIO[65]               | SIUL        | I/O              |             |                        |            | 8       |

|          | DODIGEI | AF1                                  | E0UC[17]               | eMIOS_0     | I/O              | М           | Tristate               |            |         |

| PE[1]    | PCR[65] | AF2                                  | —                      | —           | —                |             |                        | _          |         |

|          |         | AF3                                  | —                      | —           | —                |             |                        |            |         |

|          |         | AF0                                  | GPIO[66]               | SIUL        | I/O              |             |                        |            |         |

|          |         | AF1                                  | E0UC[18]               | eMIOS_0     | I/O              |             |                        |            |         |

|          | DODION  | AF2                                  | _                      | —           | —                |             | Triatata               | Tristate — | 89      |

| PE[2]    | PCR[66] | AF3                                  |                        | —           | —                | М           | Iristate               |            |         |

|          |         | —                                    | EIRQ[21]               | SIUL        | I                |             |                        |            |         |

|          |         | —                                    | SIN_1                  | DSPI_1      | l I              |             |                        |            |         |

|          |         | AF0                                  | GPIO[67]               | SIUL        | I/O              |             |                        |            |         |

|          |         | AF1                                  | E0UC[19]               | eMIOS_0     | I/O              | NA          | Triatata               |            | 00      |

| PE[3]    | PCR[67] | AF2                                  | SOUT_1                 | DSPI_1      | 0                | М           | Tristate               | _          | 90      |

|          |         | AF3                                  | —                      | —           | —                |             |                        |            |         |

|          |         | AF0                                  | GPIO[68]               | SIUL        | I/O              |             |                        |            |         |

|          |         | AF1                                  | E0UC[20]               | eMIOS_0     | I/O              |             |                        |            |         |

| PE[4] F  | PCR[68] | AF2                                  | SCK_1                  | DSPI_1      | I/O              | М           | Tristate               | _          | 93      |

|          |         | AF3                                  | _                      | —           | _                |             |                        |            |         |

|          |         | —                                    | EIRQ[9]                | SIUL        | I                |             |                        |            |         |

|          |         | AF0                                  | GPIO[69]               | SIUL        | I/O              |             |                        |            |         |

| סרורי    |         | AF1                                  | E0UC[21]               | eMIOS_0     | I/O              |             | Triate                 |            | 0.1     |

| PE[5]    | PCR[69] | AF2                                  | CS0_1                  | DSPI_1      | I/O              | М           | Tristate               | _          | 94      |

|          |         | AF3                                  | MA[2]                  | ADC         | 0                |             |                        |            |         |

| Table 6. | Functional port pin descriptions (continued) |

|----------|----------------------------------------------|

|----------|----------------------------------------------|

# 4.5 Recommended operating conditions

| Cumb a                            |    | с | Deventer                                                                                         | Conditions                  | Va                    | lue                                       | 11   |

|-----------------------------------|----|---|--------------------------------------------------------------------------------------------------|-----------------------------|-----------------------|-------------------------------------------|------|

| Symbo                             | 1  | C | Parameter                                                                                        | Conditions                  | Min                   | Max                                       | Unit |

| $V_{SS}$                          | SR | _ | Digital ground on VSS_HV pins                                                                    | —                           | 0                     | 0                                         | V    |

| V <sub>DD</sub> <sup>(1)</sup>    | SR | _ | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                                 | —                           | 3.0                   | 3.6                                       | v    |

| V <sub>SS_LV</sub> <sup>(2)</sup> | SR | _ | Voltage on VSS_LV (low voltage digital supply)<br>pins with respect to ground (V <sub>SS</sub> ) | —                           | V <sub>SS</sub> - 0.1 | V <sub>SS</sub> + 0.1                     | v    |

| V <sub>DD_BV</sub> <sup>(3)</sup> | SR |   | Voltage on VDD_BV pin (regulator supply) with                                                    | —                           | 3.0                   | 3.6                                       | v    |

| VDD_BV`                           | Ъп |   | respect to ground (V <sub>SS</sub> )                                                             | Relative to V <sub>DD</sub> | $V_{DD} - 0.1$        | V <sub>DD</sub> + 0.1                     | v    |

| V <sub>SS_ADC</sub>               | SR |   | Voltage on VSS_HV_ADC (ADC reference) pin<br>with respect to ground (V <sub>SS</sub> )           | —                           | V <sub>SS</sub> -0.1  | V <sub>SS</sub> + 0.1                     | v    |

| V <sub>DD_ADC</sub>               | SR |   | Voltage on VDD_HV_ADC pin (ADC reference)                                                        | —                           | 3.0 <sup>(5)</sup>    | 3.6                                       | v    |

| (4)                               | эп |   | with respect to ground (V <sub>SS</sub> )                                                        | Relative to V <sub>DD</sub> | $V_{DD}-0.1$          | V <sub>DD</sub> + 0.1                     | V    |

| M                                 | SR |   | Voltage on any GPIO pin with respect to ground                                                   | —                           | $V_{SS} - 0.1$        | —                                         | v    |

| V <sub>IN</sub>                   | эп |   | (V <sub>SS</sub> )                                                                               | Relative to V <sub>DD</sub> | —                     | V <sub>DD</sub> + 0.1                     | v    |

| I <sub>INJPAD</sub>               | SR | _ | Injected input current on any pin during overload condition                                      | _                           | -5                    | 5                                         | mA   |

| I <sub>INJSUM</sub>               | SR |   | Absolute sum of all injected input currents during overload condition                            | _                           | -50                   | 50                                        | mA   |

| TV <sub>DD</sub>                  | SR |   | V <sub>DD</sub> slope to ensure correct power up <sup>(6)</sup>                                  | _                           | 3.0 <sup>(7)</sup>    | 250 x 10 <sup>3</sup><br>(0.25<br>[V/μs]) | V/s  |

### Table 12. Recommended operating conditions (3.3 V)

1. 100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair.

- 2. 330 nF capacitance needs to be provided between each  $V_{DD_{L}V}/V_{SS_{L}V}$  supply pair.

- 470 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics).

- 4. 100 nF capacitance needs to be provided between  $V_{DD\_ADC}/V_{SS\_ADC}$  pair.

- Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

- 6. Guaranteed by device validation

- 7. Minimum value of TV<sub>DD</sub> must be guaranteed until V<sub>DD</sub> reaches 2.6 V (maximum value of V<sub>PORH</sub>)

### Table 13. Recommended operating conditions (5.0 V)

|   | Symbol                         |    | с | Parameter                                     | Conditions                  | Va  | Unit |   |  |

|---|--------------------------------|----|---|-----------------------------------------------|-----------------------------|-----|------|---|--|

|   |                                |    | C | Farameter                                     | Min Max                     |     |      |   |  |

| l | $V_{SS}$                       | SR |   | Digital ground on VSS_HV pins                 | —                           | 0   | 0    | V |  |

| Ī | V <sub>DD</sub> <sup>(1)</sup> | SR |   | Voltage on VDD_HV pins with respect to ground | _                           | 4.5 | 5.5  | V |  |

|   | V DD` '                        | on |   | (V <sub>SS</sub> )                            | Voltage drop <sup>(2)</sup> | 3.0 | 5.5  | ľ |  |

# 4.6 Thermal characteristics

### 4.6.1 Package thermal characteristics

| Table 14. | LQFP thermal | characteristics <sup>(1)</sup> |

|-----------|--------------|--------------------------------|

| 1able 14. |              | characteristics ?              |

| Sym               | bol                   | С                                           | Parameter                                       | Conditions <sup>(2)</sup>                           |                                                      | Value                   | Unit   |                               |                       |        |      |      |   |  |                                            |                         |         |

|-------------------|-----------------------|---------------------------------------------|-------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|-------------------------|--------|-------------------------------|-----------------------|--------|------|------|---|--|--------------------------------------------|-------------------------|---------|

|                   |                       |                                             |                                                 | Cingle lover beard to                               | LQFP64                                               | 72.1                    |        |                               |                       |        |      |      |   |  |                                            |                         |         |

| Б                 | сс                    | П                                           | Thermal resistance, junction-to-ambient natural | Single-layer board —1s                              | LQFP100                                              | 65.2                    | °C/W   |                               |                       |        |      |      |   |  |                                            |                         |         |

| $R_{\theta J A}$  | 00                    |                                             | convection <sup>(3)</sup>                       | Four-layer board — 2s2p                             | LQFP64                                               | 57.3                    | 0/10   |                               |                       |        |      |      |   |  |                                            |                         |         |

|                   |                       |                                             |                                                 | Four-layer board — 252p                             | LQFP100                                              | 51.8                    |        |                               |                       |        |      |      |   |  |                                            |                         |         |

| Б                 | ~~                    | _                                           | Р                                               | Р                                                   | Thermal resistance, junction-to-board <sup>(4)</sup> | Four-layer board — 2s2p | LQFP64 | 44.1                          | °C/W                  |        |      |      |   |  |                                            |                         |         |

| $R_{\theta JB}$   |                       | memai resistance, junction-to-board         | Four-layer board — 252p                         | LQFP100                                             | 41.3                                                 | 0/10                    |        |                               |                       |        |      |      |   |  |                                            |                         |         |

|                   | R <sub>θJC</sub> CC D | D                                           | П                                               |                                                     | Cingle lover board to                                | LQFP64                  | 26.5   | °C/W                          |                       |        |      |      |   |  |                                            |                         |         |

| Б                 |                       |                                             |                                                 | Thermal resistance, junction-to-case <sup>(5)</sup> | Single-layer board — 1s                              | LQFP100                 | 23.9   |                               |                       |        |      |      |   |  |                                            |                         |         |

| п <sub>ө</sub> јс |                       | U                                           |                                                 |                                                     | LQFP64                                               | 26.2                    | 0,00   |                               |                       |        |      |      |   |  |                                            |                         |         |

|                   |                       |                                             |                                                 | Four-layer board — 2s2p                             | LQFP100                                              | 23.7                    |        |                               |                       |        |      |      |   |  |                                            |                         |         |

|                   |                       |                                             |                                                 |                                                     | Cingle lover board to                                | LQFP64                  | 41     |                               |                       |        |      |      |   |  |                                            |                         |         |

| )T(               | ~~                    |                                             |                                                 |                                                     |                                                      |                         |        | _                             | _                     |        |      |      | _ |  | Junction-to-board thermal characterization | Single-layer board — 1s | LQFP100 |

| $\Psi_{JB}$       | CC                    | U                                           | parameter, natural convection                   |                                                     | LQFP64                                               | 43                      | - °C/W |                               |                       |        |      |      |   |  |                                            |                         |         |

|                   |                       |                                             |                                                 | Four-layer board — 2s2p                             | LQFP100                                              | 43.4                    |        |                               |                       |        |      |      |   |  |                                            |                         |         |

|                   |                       |                                             |                                                 | Cingle lover board to                               | LQFP64                                               | 11.5                    | °C AM  |                               |                       |        |      |      |   |  |                                            |                         |         |

| )1(               | ~~                    | D Junction-to-case thermal characterization | Junction-to-case thermal characterization       | Single-layer board — 1s                             | LQFP100                                              | 10.4                    |        |                               |                       |        |      |      |   |  |                                            |                         |         |

| AlC               | Ψ <sub>JC</sub> CC    |                                             | ט ;                                             | D                                                   | טוי                                                  | D                       | D      | parameter, natural convection | Four lover board 0000 | LQFP64 | 11.1 | °C/W |   |  |                                            |                         |         |

|                   |                       |                                             | Four-layer board — 2s2p                         | LQFP100                                             | 10.2                                                 |                         |        |                               |                       |        |      |      |   |  |                                            |                         |         |

1. Thermal characteristics are targets based on simulation that are subject to change per device characterization.

2.  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C

Junction-to-ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-7. Thermal test board meets

JEDEC specification for this package. When Greek letters are not available, the symbols are typed as R<sub>thJA</sub>.

Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package. When Greek letters are not available, the symbols are typed as R<sub>thJB</sub>.

Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer. When Greek letters are not available, the symbols are typed as R<sub>thJC</sub>.

### 4.6.2 Power considerations

The average chip-junction temperature,  $T_J$ , in degrees Celsius, may be calculated using *Equation 1*:

57

### 4.7.3 I/O output DC characteristics

The following tables provide DC characteristics for bidirectional pads:

- *Table 16* provides weak pull figures. Both pull-up and pull-down resistances are supported.

- *Table 17* provides output driver characteristics for I/O pads when in SLOW configuration.

- *Table 18* provides output driver characteristics for I/O pads when in MEDIUM configuration.

|                     |     | • | Deveneter                                | Conditions <sup>(1)</sup>                                         |                     |     | Value |     |      |

|---------------------|-----|---|------------------------------------------|-------------------------------------------------------------------|---------------------|-----|-------|-----|------|

| Symb                | 100 | С | Parameter                                | Conditions                                                        | ,                   | Min | Тур   | Max | Unit |

|                     |     | Ρ |                                          |                                                                   | PAD3V5V = 0         | 10  | —     | 150 |      |

| ll <sub>WPU</sub> l | сс  | С | absolute value                           | $V_{IN} = V_{IL}, V_{DD} = 5.0 V \pm 10\%$                        | $PAD3V5V = 1^{(2)}$ | 10  | —     | 250 | μA   |

|                     |     | Ρ |                                          | $V_{IN} = V_{IL}, V_{DD} = 3.3 \text{ V} \pm 10\%$                | PAD3V5V = 1         | 10  | —     | 150 |      |

|                     |     | Ρ |                                          | V <sub>IN</sub> = V <sub>IH</sub> , V <sub>DD</sub> = 5.0 V ± 10% | PAD3V5V = 0         | 10  | —     | 150 |      |

| ll <sub>wpd</sub> l | сс  | С | Weak pull-down current<br>absolute value | $V_{\rm IN} - V_{\rm IH}, V_{\rm DD} = 5.0 V \pm 10.8$            | $PAD3V5V = 1^{(2)}$ | 10  | _     | 250 | μA   |

|                     |     | Ρ |                                          | $V_{IN} = V_{IH}, V_{DD} = 3.3 \text{ V} \pm 10\%$                | PAD3V5V = 1         | 10  | —     | 150 |      |

Table 16.

I/O pull-up/pull-down DC electrical characteristics

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET are configured in input or in high impedance state.

| Sum             | Symbol | 6 | Parameter                               |            | Conditions <sup>(1)</sup>                                                                            |                       | Value |                    |   |

|-----------------|--------|---|-----------------------------------------|------------|------------------------------------------------------------------------------------------------------|-----------------------|-------|--------------------|---|

| Sym             |        |   |                                         | Conditions | Min                                                                                                  | Тур                   | Max   | Unit               |   |

|                 |        | Ρ |                                         |            | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | 0.8V <sub>DD</sub>    | _     | _                  |   |

| V <sub>OH</sub> | сс     | С | Output high level<br>SLOW configuration | Push Pull  | I <sub>OH</sub> = −2 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(2)</sup>                | 0.8V <sub>DD</sub>    | _     | _                  | v |

|                 | с      | С |                                         |            | $I_{OH} = -1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$<br>(recommended) | V <sub>DD</sub> - 0.8 | _     | _                  |   |

|                 |        | Ρ |                                         |            | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended)  | _                     | _     | 0.1V <sub>DD</sub> |   |

| V <sub>OL</sub> | сс     | С | Output low level<br>SLOW configuration  | Push Pull  | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^{(2)}$             | _                     |       | 0.1V <sub>DD</sub> | v |

|                 |        | С |                                         |            | $I_{OL} = 1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$<br>(recommended)  | _                     |       | 0.5                |   |

| Table 17. | SLOW configuration output buffer electrical characteristics |

|-----------|-------------------------------------------------------------|

|-----------|-------------------------------------------------------------|

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

|        |                        | LQFP10  | 0/LQFP64 |          |

|--------|------------------------|---------|----------|----------|

| Pad    | Weigl                  | nt 5 V  | Weigh    | it 3.3 V |

|        | SRC <sup>(2)</sup> = 0 | SRC = 1 | SRC = 0  | SRC = 1  |

| PD[7]  | 1%                     | 1%      | 1%       | 1%       |

| PD[8]  | 1%                     | 1%      | 1%       | 1%       |

| PB[4]  | 1%                     | 1%      | 1%       | 1%       |

| PB[5]  | 1%                     | 1%      | 1%       | 1%       |

| PB[6]  | 1%                     | 1%      | 1%       | 1%       |

| PB[7]  | 1%                     | 1%      | 1%       | 1%       |

| PD[9]  | 1%                     | 1%      | 1%       | 1%       |

| PD[10] | 1%                     | 1%      | 1%       | 1%       |

| PD[11] | 1%                     | 1%      | 1%       | 1%       |

| PB[11] | 9%                     | 9%      | 11%      | 11%      |

| PD[12] | 8%                     | 8%      | 10%      | 10%      |

| PB[12] | 8%                     | 8%      | 10%      | 10%      |

| PD[13] | 8%                     | 8%      | 9%       | 9%       |

| PB[13] | 8%                     | 8%      | 9%       | 9%       |

| PD[14] | 7%                     | 7%      | 9%       | 9%       |

| PB[14] | 7%                     | 7%      | 8%       | 8%       |

| PD[15] | 7%                     | 7%      | 8%       | 8%       |

| PB[15] | 6%                     | 6%      | 7%       | 7%       |

| PA[3]  | 6%                     | 6%      | 7%       | 7%       |

| PA[7]  | 4%                     | 4%      | 5%       | 5%       |

| PA[8]  | 4%                     | 4%      | 5%       | 5%       |

| PA[9]  | 4%                     | 4%      | 5%       | 5%       |

| PA[10] | 5%                     | 5%      | 6%       | 6%       |

| PA[11] | 5%                     | 5%      | 6%       | 6%       |

| PE[12] | 5%                     | 5%      | 6%       | 6%       |

| PC[3]  | 5%                     | 5%      | 6%       | 6%       |

| PC[2]  | 5%                     | 7%      | 6%       | 6%       |

| PA[5]  | 5%                     | 6%      | 5%       | 6%       |

| PA[6]  | 4%                     | 4%      | 5%       | 5%       |

| PC[1]  | 5%                     | 17%     | 4%       | 12%      |

| PC[0]  | 6%                     | 9%      | 7%       | 8%       |

| PE[2]  | 7%                     | 10%     | 8%       | 9%       |

|        | 1                      |         |          | 1        |

Table 22.

I/O weight<sup>(1)</sup> (continued)

| Symbol                |          | ~  | Devemeter                                                                       | Conditions <sup>(1)</sup>                                                           |                                    | Value                                                 |                    | Unit |     |    |

|-----------------------|----------|----|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------|--------------------|------|-----|----|

| Symbol                |          | С  | Parameter                                                                       | Conditions                                                                          | Min                                | Тур                                                   | Max                | Unit |     |    |

| C <sub>REGn</sub>     | SR       |    | Internal voltage regulator external capacitance                                 | —                                                                                   | 200                                | _                                                     | 500                | nF   |     |    |

| R <sub>REG</sub>      | SR       |    | Stability capacitor equivalent serial resistance                                | Range:<br>10 kHz to 20 MHz                                                          | _                                  | _                                                     | 0.2                | Ω    |     |    |

| 6                     | 00       |    | Descuriting annotice (2) hallast                                                | V <sub>DD_BV</sub> /V <sub>SS_LV</sub> pair:<br>V <sub>DD_BV</sub> = 4.5 V to 5.5 V | 100 <sup>(3)</sup>                 | 470 <sup>(4)</sup>                                    |                    |      |     |    |

| C <sub>DEC1</sub> SR  |          | _  | Decoupling capacitance <sup>(2)</sup> ballast                                   | V <sub>DD_BV</sub> /V <sub>SS_LV</sub> pair:<br>V <sub>DD_BV</sub> = 3 V to 3.6 V   | 400                                | 470(*)                                                |                    | nF   |     |    |

| C <sub>DEC2</sub>     | SR       |    | Decoupling capacitance regulator supply                                         | V <sub>DD</sub> /V <sub>SS</sub> pair                                               | 10                                 | 100                                                   | _                  | nF   |     |    |

| M                     | <u> </u> | Т  | Main regulator output voltage                                                   | Before exiting from reset                                                           | —                                  | 1.32                                                  |                    | v    |     |    |

| V <sub>MREG</sub>     | СС       | Ρ  | Main regulator output voltage                                                   | After trimming                                                                      | 1.16                               | 1.28                                                  |                    | v    |     |    |

| I <sub>MREG</sub>     | SR       |    | Main regulator current provided to V <sub>DD_LV</sub> domain                    | —                                                                                   | _                                  | _                                                     | 150                | mA   |     |    |

| 1                     | сс       | D  | Main regulator module current                                                   | I <sub>MREG</sub> = 200 mA                                                          | _                                  | —                                                     | 2                  | mA   |     |    |

| IMREGINT              | 00       |    | consumption                                                                     | I <sub>MREG</sub> = 0 mA                                                            | _                                  | —                                                     | 1                  |      |     |    |

| V <sub>LPREG</sub>    | СС       | Ρ  | Low-power regulator output voltage                                              | After trimming                                                                      | 1.16                               | 1.28                                                  |                    | V    |     |    |

| I <sub>LPREG</sub>    | SR       |    | Low power regulator current provided to $V_{DD_{LV}}$ domain                    | _                                                                                   | _                                  | _                                                     | 15                 | mA   |     |    |

| 1                     | CC       | сс | <u> </u>                                                                        | D                                                                                   | Low-power regulator module current | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C | _                  | —    | 600 | μA |

| I <sub>LPREGINT</sub> | 00       |    | consumption                                                                     | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C                                | — 5 —                              |                                                       | μΑ                 |      |     |    |

| V <sub>ULPREG</sub>   | сс       |    | Ultra low power regulator output<br>voltage                                     | After trimming                                                                      | 1.16                               | 1.28                                                  |                    | v    |     |    |

| I <sub>ULPREG</sub>   | SR       |    | Ultra low power regulator current provided to V <sub>DD_LV</sub> domain         | _                                                                                   | _                                  | _                                                     | 5                  | mA   |     |    |

| <b>I.</b>             | сс       | D  | Ultra low power regulator module                                                | I <sub>ULPREG</sub> = 5 mA;<br>T <sub>A</sub> = 55 °C                               | _                                  | _                                                     | 100                | μA   |     |    |

| ULPREGINT             | 00       |    | current consumption                                                             | I <sub>ULPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C                               |                                    | 2                                                     |                    | μΛ   |     |    |

| I <sub>DD_BV</sub>    | сс       | D  | In-rush average current on V <sub>DD_BV</sub><br>during power-up <sup>(5)</sup> | —                                                                                   | _                                  | _                                                     | 300 <sup>(6)</sup> | mA   |     |    |

| Table 24. | Voltage regulator electrical characteristics |

|-----------|----------------------------------------------|

|-----------|----------------------------------------------|

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. This capacitance value is driven by the constraints of the external voltage regulator supplying the V<sub>DD\_BV</sub> voltage. A typical value is in the range of 470 nF.

3. This value is acceptable to guarantee operation from 4.5 V to 5.5 V.

4. External regulator and capacitance circuitry must be capable of providing  $I_{DD_BV}$  while maintaining supply  $V_{DD_BV}$  in operating range.

In-rush average current is seen only for short time during power-up and on standby exit (maximum 20 µs, depending on external capacitances to be loaded).