# E·XFL

### NXP USA Inc. - P89V51RC2FN,112 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-DIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89v51rc2fn-112 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

8-bit microcontrollers with 80C51 core

### 5.2 Pin description

| Symbol       | Pin                 |    |    | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|--------------|---------------------|----|----|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|              | DIP40 TQFP44 PLCC44 |    |    | _                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| P0.0 to P0.7 |                     |    |    | I/O                             | <b>Port 0:</b> Port 0 is an 8-bit open drain bidirectional I/O port.<br>Port 0 pins that have '1's written to them float, and in this<br>state can be used as high-impedance inputs. Port 0 is also<br>the multiplexed low-order address and data bus during<br>accesses to external code and data memory. In this<br>application, it uses strong internal pull-ups when<br>transitioning to '1's. Port 0 also receives the code bytes<br>during the external host mode programming, and outputs<br>the code bytes during the external host mode verification.<br>External pull-ups are required during program verification<br>or as a general purpose I/O port. |  |  |  |

| P0.0/AD0     | 39                  | 37 | 43 | I/O                             | <b>P0.0</b> — Port 0 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | AD0 — Address/data bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.1/AD1     | 38                  | 36 | 42 | I/O                             | <b>P0.1</b> — Port 0 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | AD1 — Address/data bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.2/AD2 37  | 37                  | 35 | 41 | I/O                             | <b>P0.2</b> — Port 0 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | AD2 — Address/data bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.3/AD3     | 36                  | 34 | 40 | I/O                             | <b>P0.3</b> — Port 0 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | AD3 — Address/data bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.4/AD4     | 35                  | 33 | 39 | I/O                             | <b>P0.4</b> — Port 0 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | AD4 — Address/data bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.5/AD5     | 34                  | 32 | 38 | I/O                             | <b>P0.5</b> — Port 0 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | AD5 — Address/data bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.6/AD6     | 33                  | 31 | 37 | I/O                             | <b>P0.6</b> — Port 0 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | AD6 — Address/data bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.7/AD7     | 32                  | 30 | 36 | I/O                             | <b>P0.7</b> — Port 0 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | AD7 — Address/data bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P1.0 to P1.7 |                     |    |    | I/O with<br>internal<br>pull-up | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 pins are pulled high by the internal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, Port 1 pins that are externally pulled LOW will source current ( $I_{IL}$ ) because of the internal pull-ups. P1.5, P1.6, P1.7 have high current drive of 16 mA. Port 1 also receives the low-order address bytes during the external host mode programming and verification.                                                                                                                                                         |  |  |  |

| P1.0/T2      | 1                   | 40 | 2  | I/O                             | <b>P1.0</b> — Port 1 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I/O                             | <b>T2</b> — External count input to Timer/counter 2 or Clock-out from Timer/counter 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| P1.1/T2EX    | 2                   | 41 | 3  | I/O                             | <b>P1.1</b> — Port 1 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|              |                     |    |    | I                               | <b>T2EX</b> : Timer/counter 2 capture/reload trigger and direction control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

8-bit microcontrollers with 80C51 core

| Symbol          | Pin   |                  |                  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|-------|------------------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | DIP40 | TQFP44           | PLCC44           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

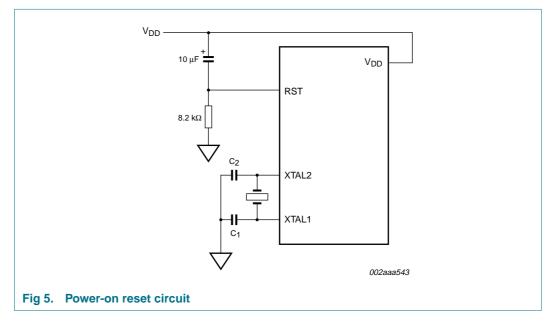

| RST             | 9     | 4                | 10               | I    | <b>Reset</b> : While the oscillator is running, a HIGH logic state<br>on this pin for two machine cycles will reset the device. If<br>the PSEN pin is driven by a HIGH-to-LOW input transition<br>while the RST input pin is held HIGH, the device will enter<br>the external host mode, otherwise the device will enter the<br>normal operation mode.                                                                                                                                                                               |

| ĒĀ              | 31    | 29               | 35               | I    | <b>External Access Enable</b> : $\overline{EA}$ must be connected to V <sub>SS</sub> in order to enable the device to fetch code from the external program memory. $\overline{EA}$ must be strapped to V <sub>DD</sub> for internal program execution. The $\overline{EA}$ pin can tolerate a high voltage of 12 V.                                                                                                                                                                                                                  |

| ALE/PROG        | 30    | 27               | 33               | I/O  | Address Latch Enable: ALE is the output signal for<br>latching the low byte of the address during an access to<br>external memory. This pin is also the programming pulse<br>input (PROG) for flash programming. Normally the ALE <sup>[1]</sup><br>is emitted at a constant rate of <sup>1</sup> / <sub>6</sub> the crystal frequency <sup>[2]</sup><br>and can be used for external timing and clocking. One ALE<br>pulse is skipped during each access to external data<br>memory. However, if AO is set to '1', ALE is disabled. |

| n.c.            | -     | 6, 17, 28,<br>39 | 1, 12, 23,<br>34 | I/O  | not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTAL1           | 19    | 15               | 21               | I    | <b>Crystal 1</b> : Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| XTAL2           | 18    | 14               | 20               | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub> | 40    | 38               | 44               | I    | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> | 20    | 16               | 22               | I    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 3. P89V51RB2/RC2/RD2 pin description ...continued

ALE loading issue: When ALE pin experiences higher loading (>30 pF) during the reset, the microcontroller may accidentally enter into modes other than normal working mode. The solution is to add a pull-up resistor of 3 kΩ to 50 kΩ to V<sub>DD</sub>, e.g., for ALE pin.

[2] For 6-clock mode, ALE is emitted at  $\frac{1}{3}$  of crystal frequency.

8-bit microcontrollers with 80C51 core

## Table 4.Special function registers\* indicates SFRs that are bit addressable

| , I | Name   | Description                   | SFR         | Bit functions and addresses |            |        |        |       |       |        |           |  |

|-----|--------|-------------------------------|-------------|-----------------------------|------------|--------|--------|-------|-------|--------|-----------|--|

|     |        |                               | address     | MSB                         |            |        |        |       |       |        | LSB       |  |

| 1   |        |                               | Bit address | E7                          | <b>E</b> 6 | E5     | E4     | E3    | E2    | E1     | E0        |  |

|     | ACC*   | Accumulator                   | E0H         |                             |            |        |        |       |       |        |           |  |

|     | AUXR   | Auxiliary function register   | 8EH         | -                           | -          | -      | -      | -     | -     | EXTRAM | AO        |  |

|     | AUXR1  | Auxiliary function register 1 | A2H         | -                           | -          | -      |        | GF2   | 0     | -      | DPS       |  |

|     |        |                               | Bit address | <b>F7</b>                   | <b>F6</b>  | F5     | F4     | F3    | F2    | F1     | <b>F0</b> |  |

| I   | B*     | B register                    | F0H         |                             |            |        |        |       |       |        |           |  |

| (   | CCAP0H | Module 0 Capture HIGH         | FAH         |                             |            |        |        |       |       |        |           |  |

|     | CCAP1H | Module 1 Capture HIGH         | FBH         |                             |            |        |        |       |       |        |           |  |

|     | CCAP2H | Module 2 Capture HIGH         | FCH         |                             |            |        |        |       |       |        |           |  |

|     | ССАРЗН | Module 3 Capture HIGH         | FDH         |                             |            |        |        |       |       |        |           |  |

| (   | CCAP4H | Module 4 Capture HIGH         | FEH         |                             |            |        |        |       |       |        |           |  |

| (   | CCAP0L | Module 0 Capture LOW          | EAH         |                             |            |        |        |       |       |        |           |  |

|     | CCAP1L | Module 1 Capture LOW          | EBH         |                             |            |        |        |       |       |        |           |  |

|     | CCAP2L | Module 2 Capture LOW          | ECH         |                             |            |        |        |       |       |        |           |  |

|     | CCAP3L | Module 3 Capture LOW          | EDH         |                             |            |        |        |       |       |        |           |  |

|     | CCAP4L | Module 4 Capture LOW          | EEH         |                             |            |        |        |       |       |        |           |  |

|     | CCAPM0 | Module 0 Mode                 | DAH         | -                           | ECOM_0     | CAPP_0 | CAPN_0 | MAT_0 | TOG_0 | PWM_0  | ECCF_     |  |

|     | CCAPM1 | Module 1 Mode                 | DBH         | -                           | ECOM_1     | CAPP_1 | CAPN_1 | MAT_1 | TOG_1 | PWM_1  | ECCF_     |  |

| (   | CCAPM2 | Module 2 Mode                 | DCH         | -                           | ECOM_2     | CAPP_2 | CAPN_2 | MAT_2 | TOG_2 | PWM_2  | ECCF_2    |  |

| (   | ССАРМЗ | Module 3 Mode                 | DDH         | -                           | ECOM_3     | CAPP_3 | CAPN_3 | MAT_3 | TOG_3 | PWM_3  | ECCF_     |  |

| (   | CCAPM4 | Module 4 Mode                 | DEH         | -                           | ECOM_4     | CAPP_4 | CAPN_4 | MAT_4 | TOG_4 | PWM_4  | ECCF_4    |  |

|     |        |                               | Bit address | DF                          | DE         | DD     | DC     | DB    | DA    | D9     | <b>D8</b> |  |

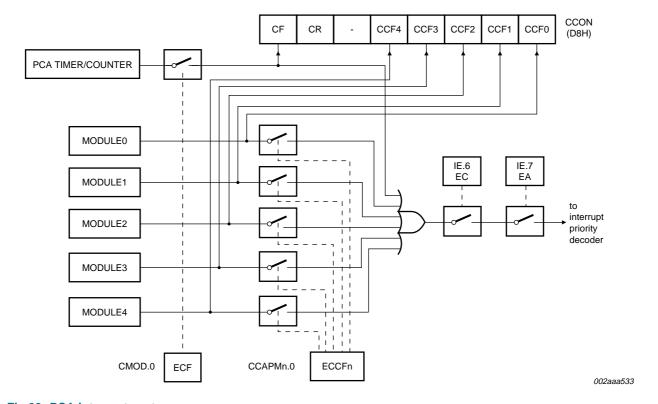

| (   | CCON*  | PCA Counter Control           | D8H         | CF                          | CR         | -      | CCF4   | CCF3  | CCF2  | CCF1   | CCF0      |  |

|     | СН     | PCA Counter HIGH              | F9H         |                             |            |        |        |       |       |        |           |  |

|     | CL     | PCA Counter LOW               | E9H         |                             |            |        |        |       |       |        |           |  |

|     | CMOD   | PCA Counter Mode              | D9H         | CIDL                        | WDTE       | -      | -      | -     | CPS1  | CPS0   | ECF       |  |

|     | DPTR   | Data Pointer (2 B)            |             |                             |            |        |        |       |       |        |           |  |

|     | DPH    | Data Pointer HIGH             | 83H         |                             |            |        |        |       |       |        |           |  |

11 of 80

#### 8-bit microcontrollers with 80C51 core

to work during initial power up, before the voltage reaches the brownout detection level. The POF flag in the PCON register is set to indicate an initial power up condition. The POF flag will remain active until cleared by software.

Following a power-on or external reset the P89V51RB2/RC2/RD2 will force the SWR and BSEL bits (FCF[1:0]) = 00. This causes the boot block to be mapped into the lower 8 kB of code memory and the device will execute the ISP code in the boot block and attempt to autobaud to the host. If the autobaud is successful the device will remain in ISP mode. If, after approximately 400 ms, the autobaud is unsuccessful the boot block code will check to see if the SoftICE flag is set (from a previous programming operation). If the SoftICE flag is set the device will enter SoftICE mode. If the SoftICE flag is cleared, the boot code will execute a software reset causing the device to execute the user code from block 0 starting at address 0000H. Note that an external reset applied to the RST pin has the same effect as a power-on reset.

#### 6.2.3 Software reset

A software reset is executed by changing the SWR bit (FCF.1) from '0' to '1'. A software reset will reset the program counter to address 0000H and force both the SWR and BSEL bits (FCF[1:0]) = 10. This will result in the lower 8 kB of the user code memory being mapped into the user code memory space. Thus the user's code will be executed starting at address 0000H. A software reset will not change WDTC.2 or RAM data. Other SFRs will be set to their reset values.

#### 6.2.4 Brownout detect reset

The device includes a brownout detection circuit to protect the system from severe supply voltage fluctuations. The P89V51RB2/RC2/RD2's brownout detection threshold is 2.35 V. When  $V_{DD}$  drops below this voltage threshold, the brownout detect triggers the circuit to generate a brownout interrupt but the CPU still runs until the supplied voltage returns to the brownout detection voltage  $V_{BOD}$ . The default operation for a brownout detection is to cause a processor reset.

8-bit microcontrollers with 80C51 core

A chip-erase operation can be performed using a commercially available parallel programer. This operation will erase the contents of this boot block and it will be necessary for the user to reprogram this boot block (block 1) with the NXP-provided ISP/IAP code in order to use the ISP or IAP capabilities of this device. Go to <a href="http://www.nxp.com/support">http://www.nxp.com/support</a> for questions or to obtain the hex file for this device.

#### 6.3.3 ISP

ISP is performed without removing the microcontroller from the system. The ISP facility consists of a series of internal hardware resources coupled with internal firmware to facilitate remote programming of the P89V51RB2/RC2/RD2 through the serial port. This firmware is provided by NXP and embedded within each P89V51RB2/RC2/RD2 device. The NXP ISP facility has made in-circuit programming in an embedded application possible with a minimum of additional expense in components and circuit board area. The ISP function uses five pins ( $V_{DD}$ ,  $V_{SS}$ , TXD, RXD, and RST). Only a small connector needs to be available to interface your application to an external circuit in order to use this feature.

#### 6.3.4 Using ISP

The ISP feature allows for a wide range of baud rates to be used in your application, independent of the oscillator frequency. It is also adaptable to a wide range of oscillator frequencies. This is accomplished by measuring the bit-time of a single bit in a received character. This information is then used to program the baud rate in terms of timer counts based on the oscillator frequency. The ISP feature requires that an initial character (an uppercase U) be sent to the P89V51RB2/RC2/RD2 to establish the baud rate. The ISP firmware provides auto-echo of received characters. Once baud rate initialization has been performed, the ISP firmware will only accept Intel Hex-type records. Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below:

#### :NNAAAARRDD..DDCC<crlf>

In the Intel Hex record, the 'NN' represents the number of data bytes in the record. The P89V51RB2/RC2/RD2 will accept up to 32 data bytes. The 'AAAA' string represents the address of the first byte in the record. If there are zero bytes in the record, this field is often set to 0000. The 'RR' string indicates the record type. A record type of '00' is a data record. A record type of '01' indicates the end-of-file mark. In this application, additional record types will be added to indicate either commands or data for the ISP facility.

The maximum number of data bytes in a record is limited to 32 (decimal). ISP commands are summarized in <u>Table 12</u>. As a record is received by the P89V51RB2/RC2/RD2, the information in the record is stored internally and a checksum calculation is performed. The operation indicated by the record type is not performed until the entire record has been received. Should an error occur in the checksum, the P89V51RB2/RC2/RD2 will send an 'X' out the serial port indicating a checksum error. If the checksum calculation is found to match the checksum in the record will be indicated by transmitting a '.' character out the serial port.

8-bit microcontrollers with 80C51 core

|             | Phex record formatscontinued                               |  |  |  |  |  |  |

|-------------|------------------------------------------------------------|--|--|--|--|--|--|

| Record type | Command/data function                                      |  |  |  |  |  |  |

| 03          | Miscellaneous Write Functions                              |  |  |  |  |  |  |

|             | :nnxxxx03ffssddcc                                          |  |  |  |  |  |  |

|             | Where:                                                     |  |  |  |  |  |  |

|             | nn = number of bytes in the record                         |  |  |  |  |  |  |

|             | xxxx = required field but value is a 'don't care'          |  |  |  |  |  |  |

|             | ff = subfunction code                                      |  |  |  |  |  |  |

|             | ss = selection code                                        |  |  |  |  |  |  |

|             | dd = data (if needed)                                      |  |  |  |  |  |  |

|             | cc = checksum                                              |  |  |  |  |  |  |

|             | Subfunction code = 01 (Erase block 0)                      |  |  |  |  |  |  |

|             | ff = 01                                                    |  |  |  |  |  |  |

|             | Subfunction code = 05 (Program security bit, Double Clock) |  |  |  |  |  |  |

|             | ff = 05                                                    |  |  |  |  |  |  |

|             | ss = 01 program security bit                               |  |  |  |  |  |  |

|             | ss = 05 program double clock bit                           |  |  |  |  |  |  |

|             | Subfunction code = 08 (Erase sector, 128 B)                |  |  |  |  |  |  |

|             | ff = 08                                                    |  |  |  |  |  |  |

|             | ss = high byte of sector address (A15:8)                   |  |  |  |  |  |  |

|             | dd = low byte of sector address (A7, A6:0 = 0)             |  |  |  |  |  |  |

|             | Example:                                                   |  |  |  |  |  |  |

|             | :030000308E000F2 (erase sector at E000H)                   |  |  |  |  |  |  |

| 04          | Display Device Data or Blank Check                         |  |  |  |  |  |  |

|             | :05xxxx04sssseeeeffcc                                      |  |  |  |  |  |  |

|             | Where                                                      |  |  |  |  |  |  |

|             | 05 = number of bytes in the record                         |  |  |  |  |  |  |

|             | xxxx = required field but value is a 'don't care'          |  |  |  |  |  |  |

|             | 04 = function code for display or blank check              |  |  |  |  |  |  |

|             | ssss = starting address, MSB first                         |  |  |  |  |  |  |

|             | eeee = ending address, MSB first                           |  |  |  |  |  |  |

|             | ff = subfunction                                           |  |  |  |  |  |  |

|             | 00 = display data                                          |  |  |  |  |  |  |

|             | 01 = blank check                                           |  |  |  |  |  |  |

|             | cc = checksum                                              |  |  |  |  |  |  |

|             | Subfunction codes:                                         |  |  |  |  |  |  |

|             |                                                            |  |  |  |  |  |  |

|             | Example:                                                   |  |  |  |  |  |  |

8-bit microcontrollers with 80C51 core

#### 6.4.3 Mode 2

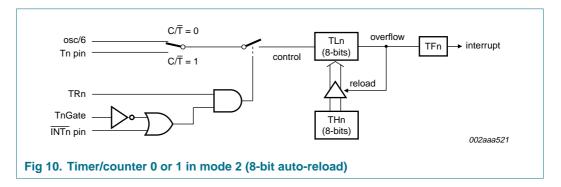

Mode 2 configures the Timer register as an 8-bit Counter (TLn) with automatic reload, as shown in <u>Figure 10</u>. Overflow from TLn not only sets TFn, but also reloads TLn with the contents of THn, which must be preset by software. The reload leaves THn unchanged. Mode 2 operation is the same for Timer 0 and Timer 1.

#### 6.4.4 Mode 3

When timer 1 is in mode 3 it is stopped (holds its count). The effect is the same as setting TR1 = 0.

Timer 0 in mode 3 establishes TL0 and TH0 as two separate 8-bit counters. The logic for mode 3 and Timer 0 is shown in Figure 11. TL0 uses the Timer 0 control bits:  $T0C/\overline{T}$ , T0GATE, TR0, INT0, and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the 'Timer 1' interrupt.

Mode 3 is provided for applications that require an extra 8-bit timer. With Timer 0 in mode 3, the P89V51RB2/RC2/RD2 can look like it has an additional Timer.

**Note:** When Timer 0 is in mode 3, Timer 1 can be turned on and off by switching it into and out of its own mode 3. It can still be used by the serial port as a baud rate generator, or in any application not requiring an interrupt.

#### 8-bit microcontrollers with 80C51 core

| Table 21. | T2CON - Time | er/counter 2 control register (address C8H) bit descriptioncontinued                                                                                                                                                                                                                                                                   |

|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit       | Symbol       | Description                                                                                                                                                                                                                                                                                                                            |

| 4         | TCLK         | Transmit clock flag. When set, causes the UART to use Timer 2 overflow pulses for its transmit clock in modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used for the transmit clock.                                                                                                                                            |

| 3         | EXEN2        | Timer 2 external enable flag. When set, allows a capture or reload to occur as a result of a negative transition on T2EX if Timer 2 is not being used to clock the serial port. EXEN2 = 0 causes Timer 2 to ignore events at T2EX.                                                                                                     |

| 2         | TR2          | Start/stop control for Timer 2. A logic '1' enables the timer to run.                                                                                                                                                                                                                                                                  |

| 1         | C/T2         | Timer or counter select. (Timer 2)<br>$0 = \text{internal timer } (f_{osc} / 6)$<br>$1 = \text{external event counter } (falling edge triggered; external clock's maximum rate = f_{osc} / 12$                                                                                                                                         |

| 0         | CP/RL2       | Capture/Reload flag. When set, captures will occur on negative transitions at T2EX if EXEN2 = 1. When cleared, auto-reloads will occur either with Timer 2 overflows or negative transitions at T2EX when EXEN2 = 1. When either RCLK = 1 or TCLK = 1, this bit is ignored and the timer is forced to auto-reload on Timer 2 overflow. |

## Table 22. T2MOD - Timer 2 mode control register (address C9H) bit allocation Not bit addressable; Reset value: XX00 0000B

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|--------|---|---|---|---|---|---|------|------|

| Symbol | - | - | - | - | - | - | T2OE | DCEN |

#### Table 23. T2MOD - Timer 2 mode control register (address C9H) bit description

| Bit    | Symbol | Description                                                                                  |

|--------|--------|----------------------------------------------------------------------------------------------|

| 7 to 2 | -      | Reserved for future use. Should be set to '0' by user programs.                              |

| 1      | T2OE   | Timer 2 Output Enable bit. Used in programmable clock-out mode only.                         |

| 0      | DCEN   | Down Count Enable bit. When set, this allows Timer 2 to be configured as an up/down counter. |

### 6.5.1 Capture mode

In the Capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2 = 0 Timer 2 is a 16-bit timer or counter (as selected by  $C/\overline{T}2$  in T2CON) which upon overflowing sets bit TF2, the Timer 2 overflow bit.

The capture mode is illustrated in Figure 12.

#### 6.6.2 Mode 1

10 bits are transmitted (through TXD) or received (through RXD): a start bit (logical 0), 8 data bits (LSB first), and a stop bit (logical 1). When data is received, the stop bit is stored in RB8 in Special Function Register SCON. The baud rate is variable and is determined by the Timer  $\frac{1}{2}$  overflow rate.

#### 6.6.3 Mode 2

11 bits are transmitted (through TXD) or received (through RXD): start bit (logical 0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (logical 1). When data is transmitted, the 9th data bit (TB8 in SCON) can be assigned the value of 0 or (e.g. the parity bit (P, in the PSW) could be moved into TB8). When data is received, the 9th data bit goes into RB8 in Special Function Register SCON, while the stop bit is ignored. The baud rate is programmable to either  $\frac{1}{16}$  or  $\frac{1}{32}$  of the CPU clock frequency, as determined by the SMOD1 bit in PCON.

#### 6.6.4 Mode 3

11 bits are transmitted (through TXD) or received (through RXD): a start bit (logical 0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (logical 1). In fact, mode 3 is the same as mode 2 in all respects except baud rate. The baud rate in mode 3 is variable and is determined by the Timer  $\frac{1}{2}$  overflow rate.

### Table 25. SCON - Serial port control register (address 98H) bit allocation Bit addressable; Reset value: 00H

| Bit    | 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|--------|--------|-----|-----|-----|-----|-----|----|----|

| Symbol | SM0/FE | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

#### Table 26. SCON - Serial port control register (address 98H) bit description

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SM0/FE | The usage of this bit is determined by SMOD0 in the PCON register. If $SMOD0 = 0$ , this bit is SM0, which with SM1, defines the serial port mode. If $SMOD0 = 1$ , this bit is FE (Framing Error). FE is set by the receiver when an invalid stop bit is detected. Once set, this bit cannot be cleared by valid frames but can only be cleared by software. (Note: It is recommended to set up UART mode bits SM0 and SM1 before setting SMOD0 to '1'.) |

| 6   | SM1    | With SM0, defines the serial port mode (see Table 27 below).                                                                                                                                                                                                                                                                                                                                                                                              |

| 5   | SM2    | Enables the multiprocessor communication feature in modes 2 and 3.<br>In mode 2 or 3, if SM2 is set to '1', then RI will not be activated if the<br>received 9th data bit (RB8) is '0'. In mode 1, if SM2 = 1 then RI will not<br>be activated if a valid stop bit was not received. In mode 0, SM2<br>should be '0'.                                                                                                                                     |

| 4   | REN    | Enables serial reception. Set by software to enable reception. Clear by software to disable reception.                                                                                                                                                                                                                                                                                                                                                    |

| 3   | TB8    | The 9th data bit that will be transmitted in modes 2 and 3. Set or clear by software as desired.                                                                                                                                                                                                                                                                                                                                                          |

### **NXP Semiconductors**

### P89V51RB2/RC2/RD2

8-bit microcontrollers with 80C51 core

#### Fig 22. PCA interrupt system

## Table 35. CMOD - PCA counter mode register (address D9H) bit allocation Not bit addressable; Reset value: 00H

| Bit    | 7    | 6    | 5 | 4 | 3 | 2    | 1    | 0   |

|--------|------|------|---|---|---|------|------|-----|

| Symbol | CIDL | WDTE | - | - | - | CPS1 | CPS0 | ECF |

#### Table 36. CMOD - PCA counter mode register (address D9H) bit description

| Bit    | Symbol        | Description                                                                                                                                         |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | CIDL          | Counter Idle Control: CIDL = 0 programs the PCA Counter to continue functioning during Idle mode. CIDL = 1 programs it to be gated off during idle. |

| 6      | WDTE          | Watchdog Timer Enable: WDTE = 0 disables watchdog timer function on module 4. WDTE = 1 enables it.                                                  |

| 5 to 3 | -             | Reserved for future use. Should be set to '0' by user programs.                                                                                     |

| 2 to 1 | CPS1,<br>CPS0 | PCA Count Pulse Select (see Table 37 below).                                                                                                        |

| 0      | ECF           | PCA Enable Counter Overflow Interrupt: ECF = 1 enables CF bit in CCON to generate an interrupt. ECF = 0 disables that function.                     |

### 8-bit microcontrollers with 80C51 core

Table 41.

CCAPMn - PCA modules compare/capture register (address CCAPM0 0DAH, CCAPM1 0DBH, CCAPM2 0DCH, CCAPM3 0DDH, CCAPM4 0DEH) bit description

| Bit | Symbol | Description                                                                                                                  |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------|

| 2   | TOGn   | Toggle. When TOGn = 1, a match of the PCA counter with this module's compare/capture register causes the CEXn pin to toggle. |

| 1   | PWMn   | Pulse Width Modulation mode. PWMn = 1 enables the CEXn pin to be used as a pulse width modulated output.                     |

| 0   | ECCFn  | Enable CCF Interrupt. Enables compare/capture flag CCFn in the CCON register to generate an interrupt.                       |

#### Table 42. PCA module modes (CCAPMn register)

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn | Module function                                      |

|-------|-------|-------|------|------|------|-------|------------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | no operation                                         |

| x     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigger on CEXn    |

| x     | 0     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a negative-edge trigger on<br>CEXn |

| х     | 1     | 1     | 0    | 0    | 0    | х     | 16-bit capture by any transition on CEXn             |

| 1     | 0     | 0     | 1    | 0    | 0    | х     | 16-bit software timer                                |

| 1     | 0     | 0     | 1    | 1    | 0    | х     | 16-bit high-speed output                             |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                            |

| 1     | 0     | 0     | 1    | х    | 0    | х     | Watchdog timer                                       |

|       |       |       |      |      |      |       |                                                      |

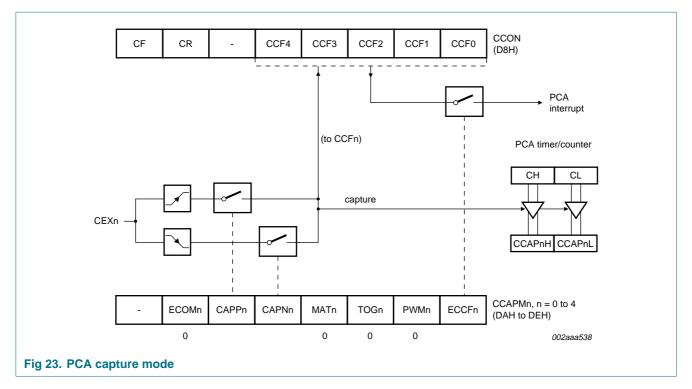

### 6.9.1 PCA capture mode

To use one of the PCA modules in the capture mode (Figure 23) either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH).

### **NXP Semiconductors**

### P89V51RB2/RC2/RD2

8-bit microcontrollers with 80C51 core

If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated.

#### 6.9.2 16-bit software timer mode

The PCA modules can be used as software timers (Figure 24) by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

8-bit microcontrollers with 80C51 core

value in the module's CCAPnL SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPnL is reloaded with the value in CCAPnH. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

#### 6.9.5 PCA watchdog timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a Watchdog. However, this module can still be used for other modes if the Watchdog is not needed. Figure 26 shows a diagram of how the Watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

User's software then must periodically change (CCAP4H,CCAP4L) to keep a match from occurring with the PCA timer (CH,CL). This code is given in the WATCHDOG routine shown above.

In order to hold off the reset, the user has three options:

- 1. Periodically change the compare value so it will never match the PCA timer.

- 2. Periodically change the PCA timer value so it will never match the compare values.

- 3. Disable the Watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for **all** modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This routine should not be part of an interrupt service routine, because if the program counter goes astray and gets stuck in an infinite loop, interrupts will still be serviced and the Watchdog will keep getting reset. Thus, the purpose of the Watchdog would be defeated. Instead, call this subroutine from the main program within 2<sup>16</sup> count of the PCA timer.

### **NXP Semiconductors**

## P89V51RB2/RC2/RD2

8-bit microcontrollers with 80C51 core

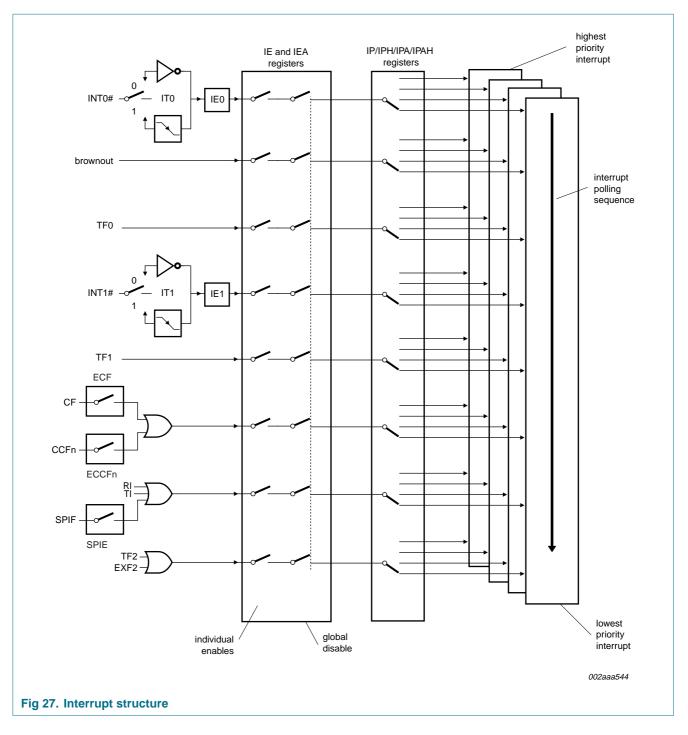

## Table 44. IEN0 - Interrupt enable register 0 (address A8H) bit allocation Bit addressable; Reset value: 00H

| Bit    | 7  | 6  | 5   | 4  | 3   | 2   | 1   | 0   |

|--------|----|----|-----|----|-----|-----|-----|-----|

| Symbol | EA | EC | ET2 | ES | ET1 | EX1 | ET0 | EX0 |

#### 8-bit microcontrollers with 80C51 core

#### Table 51. IP0H - Interrupt priority 0 high register (address B7H) bit description

| Bit | Symbol | Description                                                     |

|-----|--------|-----------------------------------------------------------------|

| 7   | -      | Reserved for future use. Should be set to '0' by user programs. |

| 6   | PPCH   | PCA interrupt priority HIGH bit.                                |

| 5   | PT2H   | Timer 2 interrupt priority HIGH bit.                            |

| 4   | PSH    | Serial Port interrupt priority HIGH bit.                        |

| 3   | PT1H   | Timer 1 interrupt priority HIGH bit.                            |

| 2   | PX1H   | External interrupt 1 priority HIGH bit.                         |

| 1   | PT0H   | Timer 0 interrupt priority HIGH bit.                            |

| 0   | PX0H   | External interrupt 0 priority HIGH bit.                         |

Table 52.

IP1 - Interrupt priority 1 register (address F8H) bit allocation

Bit addressable; Reset value: 00H

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

|--------|---|---|---|-----|---|---|---|---|

| Symbol | - | - | - | PBO | - | - | - | - |

#### Table 53. IP1 - Interrupt priority 1 register (address F8H) bit description

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 4      | PBO    | Brownout interrupt priority bit.                                |

| 3 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

Table 54.

IP1H - Interrupt priority 1 high register (address F7H) bit allocation

Not bit addressable; Reset value: 00H

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |

|--------|---|---|---|------|---|---|---|---|

| Symbol | - | - | - | PBOH | - | - | - | - |

#### Table 55. IP1H - Interrupt priority 1 high register (address F7H) bit description

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 4      | PBOH   | Brownout interrupt priority bit.                                |

| 3 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

### 6.12 Power-saving modes

The device provides two power saving modes of operation for applications where power consumption is critical. The two modes are Idle and Power-down, see <u>Table 56</u>.

#### 6.12.1 Idle mode

Idle mode is entered setting the IDL bit in the PCON register. In Idle mode, the program counter (PC) is stopped. The system clock continues to run and all interrupts and peripherals remain active. The on-chip RAM and the special function registers hold their data during this mode.

### 7. Limiting values

#### Table 61. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to  $V_{SS}$  unless otherwise noted.

| Symbol                 | Parameter                             | Conditions                                                         | Min  | Max                   | Unit |

|------------------------|---------------------------------------|--------------------------------------------------------------------|------|-----------------------|------|

| T <sub>amb(bias)</sub> | bias ambient temperature              |                                                                    | -55  | +125                  | °C   |

| T <sub>stg</sub>       | storage temperature                   |                                                                    | -65  | +150                  | °C   |

| VI                     | input voltage                         | on $\overline{EA}$ pin to $V_{SS}$                                 | -0.5 | +14                   | V    |

| V <sub>n</sub>         | voltage on any other pin              | except $V_{SS}$ ; with respect to $V_{DD}$                         | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| I <sub>OL(I/O)</sub>   | LOW-level output current per          | pins P1.5, P1.6, P1.7                                              | -    | 20                    | mA   |

|                        | input/output pin                      | all other pins                                                     | -    | 15                    | mA   |

| P <sub>tot(pack)</sub> | total power dissipation (per package) | based on package heat<br>transfer, not device power<br>consumption | -    | 1.5                   | W    |

### 8. Static characteristics

#### Table 62.Static characteristics

$T_a = 0 \ ^\circ C \ to \ +70 \ ^\circ C \ or \ -40 \ ^\circ C \ to \ +85 \ ^\circ C; \ V_{DD} = 4.5 \ V \ to \ 5.5 \ V; \ V_{SS} = 0 \ V$

| Symbol                | Parameter                      | Conditions                                             |            | Min                      | Тур | Max                   | Unit   |

|-----------------------|--------------------------------|--------------------------------------------------------|------------|--------------------------|-----|-----------------------|--------|

| n <sub>endu(fl)</sub> | endurance of flash memory      | JEDEC Standard A117                                    | <u>[1]</u> | 10000                    | -   | -                     | cycles |

| t <sub>ret(fl)</sub>  | flash memory<br>retention time | JEDEC Standard A103                                    | <u>[1]</u> | 100                      | -   | -                     | years  |

| I <sub>latch</sub>    | I/O latch-up current           | JEDEC Standard 78                                      | <u>[1]</u> | 100 + I <sub>DD</sub>    | -   | -                     | mA     |

| $V_{\text{th(HL)}}$   | HIGH-LOW threshold voltage     | $4.5 \text{ V} < \text{V}_{\text{DD}} < 5.5 \text{ V}$ |            | -0.5                     | -   | $0.2V_{DD} - 0.1$     | V      |

| V <sub>th(LH)</sub>   | LOW-HIGH threshold voltage     | except XTAL1, RST                                      |            | 0.2V <sub>DD</sub> + 0.9 | -   | V <sub>DD</sub> + 0.5 | V      |

| V <sub>IH</sub>       | HIGH-level input voltage       | 4.5 V < V <sub>DD</sub> < 5.5 V; XTAL1, RST            |            | 0.7V <sub>DD</sub>       | -   | 6.0                   | V      |

| V <sub>OL</sub>       | LOW-level output voltage       | $V_{DD}$ = 4.5 V; ports 1, 2, 3, except<br>PSEN, ALE   | [2][3][4]  |                          |     |                       |        |

|                       |                                | I <sub>OL</sub> = 100 μA                               |            | -                        | -   | 0.3                   | V      |

|                       |                                | I <sub>OL</sub> = 1.6 mA                               |            | -                        | -   | 0.45                  | V      |

|                       |                                | I <sub>OL</sub> = 3.5 mA                               |            | -                        | -   | 1.0                   | V      |

|                       |                                | $V_{DD} = 4.5 V$ ; port 0, $\overline{PSEN}$ , ALE     |            |                          |     |                       |        |

|                       |                                | I <sub>OL</sub> = 200 μA                               |            | -                        | -   | 0.3                   | V      |

|                       |                                | I <sub>OL</sub> = 3.2 mA                               |            | -                        | -   | 0.45                  | V      |

|                       |                                |                                                        |            |                          |     |                       |        |

8-bit microcontrollers with 80C51 core

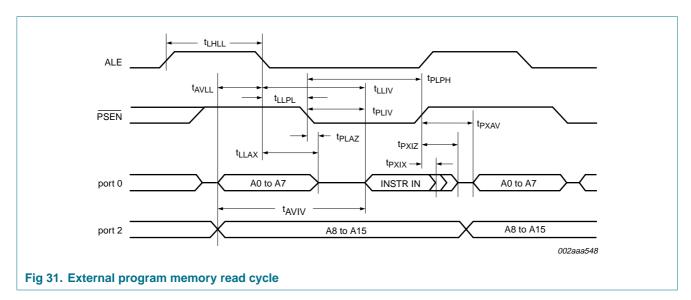

### 9.1 Explanation of symbols

Each timing symbol has 5 characters. The first character is always a 'T' (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

- A Address

- $\mathbf{C}$  Clock

- **D** Input data

- H Logic level HIGH

- I Instruction (program memory contents)

- L Logic level LOW or ALE

- P PSEN

- Q Output data

- **R** RD signal

- T Time

- V Valid

- $W \overline{WR}$  signal

- X No longer a valid logic level

- Z High impedance (Float)

Example:

t<sub>AVLL</sub> = Address valid to ALE LOW time

$t_{LLPL} = ALE LOW to \overline{PSEN} LOW time$

8-bit microcontrollers with 80C51 core

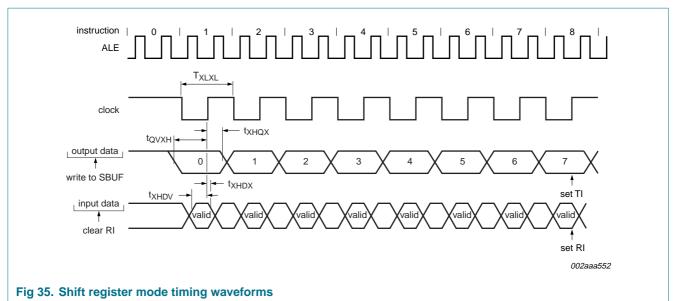

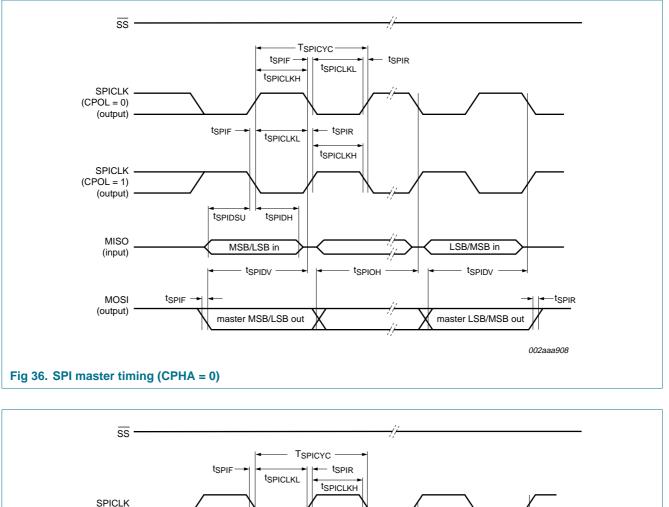

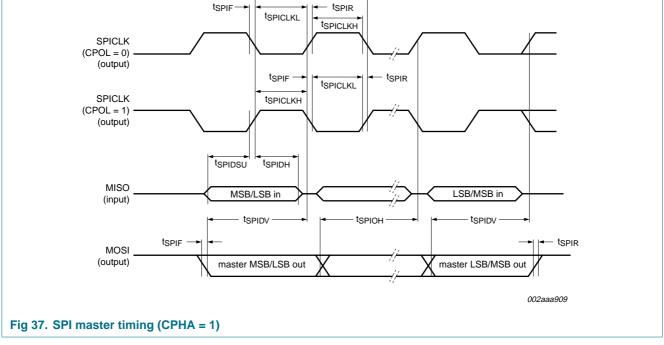

| Symbol               | Parameter                                          | Conditions                                                   | Varial                | ble clock                | f <sub>osc</sub> = 1 | 8 MHz | Unit |

|----------------------|----------------------------------------------------|--------------------------------------------------------------|-----------------------|--------------------------|----------------------|-------|------|

|                      |                                                    |                                                              | Min                   | Max                      | Min                  | Max   |      |

| f <sub>SPI</sub>     | SPI operating frequency                            |                                                              | 0                     | T <sub>cy(clk)</sub> / 4 | 0                    | 10    | MHz  |

| T <sub>SPICYC</sub>  | SPI cycle time                                     | see Figure 36, 37, 38, 39                                    | 4T <sub>cy(clk)</sub> | -                        | 222                  | -     | ns   |

| t <sub>SPILEAD</sub> | SPI enable lead time                               | see Figure 38, <u>39</u>                                     | 250                   | -                        | 250                  | -     | ns   |

| t <sub>SPILAG</sub>  | SPI enable lag time                                | see Figure 38, <u>39</u>                                     | 250                   | -                        | 250                  | -     | ns   |

| t <sub>SPICLKH</sub> | SPICLK HIGH time                                   | see Figure 36, <u>37</u> , <u>38</u> , <u>39</u>             | 2T <sub>cy(clk)</sub> | -                        | 111                  | -     | ns   |

| t <sub>SPICLKL</sub> | SPICLK LOW time                                    | see Figure 36, <u>37, 38, 39</u>                             | 2T <sub>cy(clk)</sub> | -                        | 111                  | -     | ns   |

| t <sub>SPIDSU</sub>  | SPI data set-up time                               | master or slave; see<br><u>Figure 36, 37</u> , <u>38, 39</u> | 100                   | -                        | 100                  | -     | ns   |

| t <sub>SPIDH</sub>   | SPI data hold time                                 | master or slave; see<br><u>Figure 36, 37, 38, 39</u>         | 100                   | -                        | 100                  | -     | ns   |

| t <sub>SPIA</sub>    | SPI access time                                    | see Figure 38, <u>39</u>                                     | 0                     | 80                       | 0                    | 80    | ns   |

| t <sub>SPIDIS</sub>  | SPI disable time                                   | see <u>Figure 38,</u> <u>39</u>                              | 0                     | 160                      | -                    | 160   | ns   |

| t <sub>SPIDV</sub>   | SPI enable to output data valid time               | see <u>Figure 36</u> , <u>37</u> , <u>38</u> , <u>39</u>     | -                     | 111                      | -                    | 111   | ns   |

| t <sub>SPIOH</sub>   | SPI output data hold time                          | see <u>Figure 36</u> , <u>37</u> , <u>38</u> , <u>39</u>     | 0                     | -                        | 0                    | -     | ns   |

| t <sub>SPIR</sub>    | SPI rise time                                      | see Figure 36, <u>37</u> , <u>38</u> , <u>39</u>             |                       |                          |                      |       |      |

|                      | SPI outputs (SPICLK, MOSI, MISO)                   |                                                              | -                     | 100                      | -                    | 100   | ns   |

|                      | SPI inputs (SPICLK,<br>MOSI, MISO, <del>SS</del> ) |                                                              | -                     | 2000                     | -                    | 2000  | ns   |

| t <sub>SPIF</sub>    | SPI fall time                                      | see Figure 36, <u>37, 38, 39</u>                             |                       |                          |                      |       |      |

|                      | SPI outputs (SPICLK, MOSI, MISO)                   |                                                              | -                     | 100                      | -                    | 100   | ns   |

|                      | SPI inputs (SPICLK,<br>MOSI, MISO, SS)             |                                                              | -                     | 2000                     | -                    | 2000  | ns   |

Table 66. SPI interface timing

### **NXP Semiconductors**

## P89V51RB2/RC2/RD2

8-bit microcontrollers with 80C51 core

8-bit microcontrollers with 80C51 core

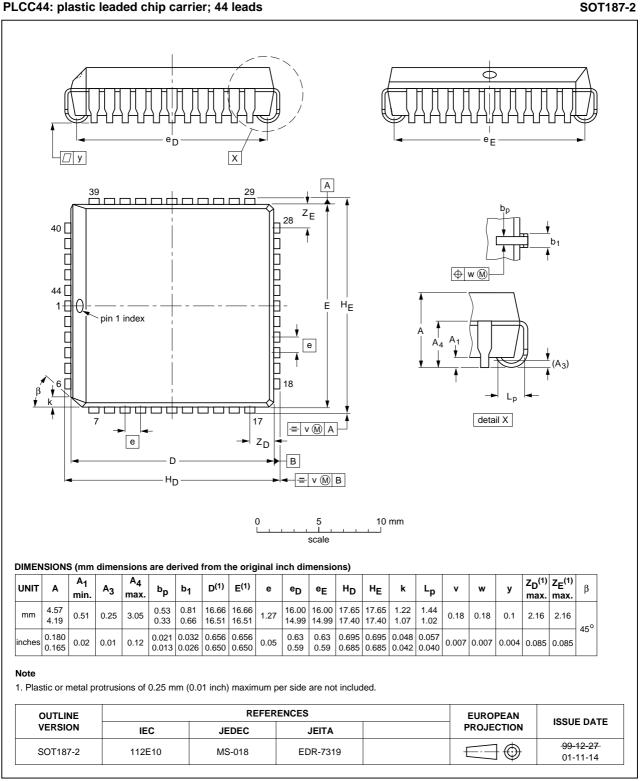

PLCC44: plastic leaded chip carrier; 44 leads

#### Fig 46. SOT187-2 (PLCC44) package outline