# E·XFL

### NXP USA Inc. - P89V51RD2FN,112 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-DIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89v51rd2fn-112 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

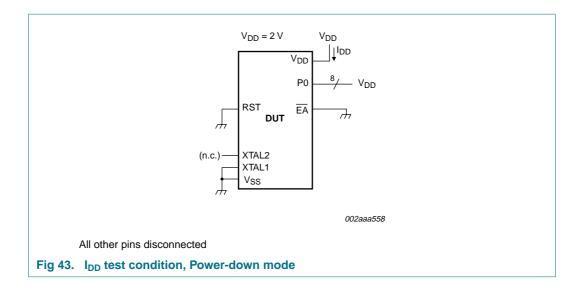

8-bit microcontrollers with 80C51 core

- Brownout detection

- Low power modes

- Power-down mode with external interrupt wake-up

- Idle mode

- DIP40, PLCC44 and TQFP44 packages

### 3. Ordering information

#### Table 1.Ordering information

| Type number  | Package |                                                                             |          |

|--------------|---------|-----------------------------------------------------------------------------|----------|

|              | Name    | Description                                                                 | Version  |

| P89V51RB2FA  | PLCC44  | plastic leaded chip carrier; 44 leads                                       | SOT187-2 |

| P89V51RB2FN  | DIP40   | plastic dual in-line package; 40 leads (600 mil)                            | SOT129-1 |

| P89V51RB2BBC | TQFP44  | plastic thin quad flat package; 44 leads; body $10 \times 10 \times 1.0$ mm | SOT376-1 |

| P89V51RC2FA  | PLCC44  | plastic leaded chip carrier; 44 leads                                       | SOT187-2 |

| P89V51RC2FBC | TQFP44  | plastic thin quad flat package; 44 leads; body $10 \times 10 \times 1.0$ mm | SOT376-1 |

| P89V51RC2FN  | DIP40   | plastic dual in-line package; 40 leads (600 mil)                            | SOT129-1 |

| P89V51RD2FA  | PLCC44  | plastic leaded chip carrier; 44 leads                                       | SOT187-2 |

| P89V51RD2FBC | TQFP44  | plastic thin quad flat package; 44 leads; body $10 \times 10 \times 1.0$ mm | SOT376-1 |

| P89V51RD2BN  | DIP40   | plastic dual in-line package; 40 leads (600 mil)                            | SOT129-1 |

| P89V51RD2FN  | DIP40   | plastic dual in-line package; 40 leads (600 mil)                            | SOT129-1 |

### 3.1 Ordering options

#### Table 2. Ordering options

| Type number  | Flash memory | Temperature range | Frequency       |

|--------------|--------------|-------------------|-----------------|

| P89V51RB2FA  | 16 kB        | –40 °C to +85 °C  | 0 MHz to 40 MHz |

| P89V51RB2FN  | 16 kB        | –40 °C to +85 °C  |                 |

| P89V51RB2BBC | 16 kB        | 0 °C to +70 °C    |                 |

| P89V51RC2FA  | 32 kB        | –40 °C to +85 °C  |                 |

| P89V51RC2FBC | 32 kB        | –40 °C to +85 °C  |                 |

| P89V51RC2FN  | 32 kB        | –40 °C to +85 °C  |                 |

| P89V51RD2FA  | 64 kB        | –40 °C to +85 °C  |                 |

| P89V51RD2FBC | 64 kB        | –40 °C to +85 °C  |                 |

| P89V51RD2BN  | 64 kB        | 0 °C to +70 °C    |                 |

| P89V51RD2FN  | 64 kB        | –40 °C to +85 °C  |                 |

8-bit microcontrollers with 80C51 core

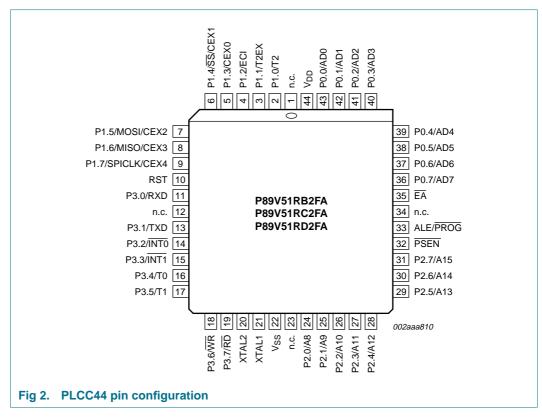

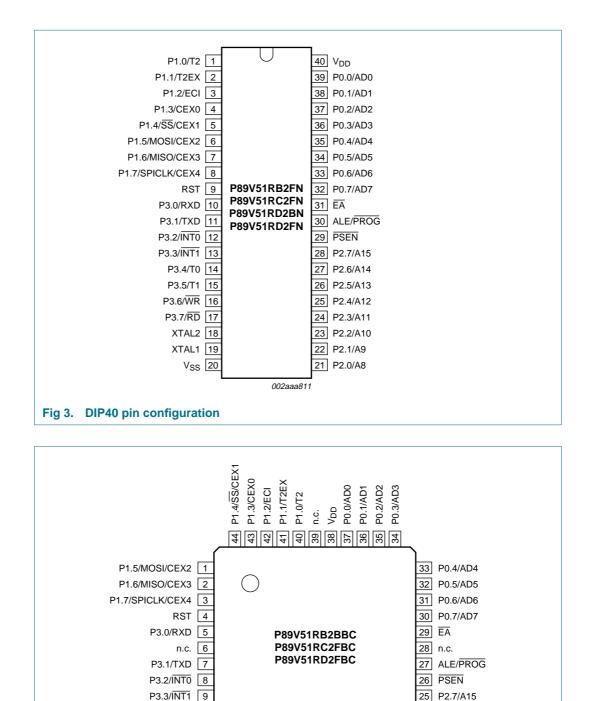

### 5. Pinning information

### 5.1 Pinning

8-bit microcontrollers with 80C51 core

P89V51RB2 RC2 RD2 5

12

P3.7/RD

P3.6/WR

15 16

4

XTAL2 XTAL1 VSS n.c. P2.0/A8

19

P2.1/A9

22 21 20

P2.2/A10

P2.3/A11

P2.4/A12

17

P3.4/T0 10

P3.5/T1 11

Fig 4. TQFP44 pin configuration

24 P2.6/A14

23 P2.5/A13

*002aaa*812

### **NXP Semiconductors**

# P89V51RB2/RC2/RD2

### 8-bit microcontrollers with 80C51 core

|              |               | pill   | description |                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|---------------|--------|-------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol       | Pin<br>DIR 40 | TOFRA  |             | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | DIP40         | TQFP44 | PLCC44      | 1/0                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P1.2/ECI     | 3             | 42     | 4           | I/O                             | <b>P1.2</b> — Port 1 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             |                                 | <b>ECI</b> — External clock input. This signal is the external clock input for the PCA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P1.3/CEX0    | 4             | 43     | 5           | I/O                             | <b>P1.3</b> — Port 1 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             | I/O                             | <b>CEX0</b> — Capture/compare external I/O for PCA Module 0.<br>Each capture/compare module connects to a Port 1 pin for<br>external I/O. When not used by the PCA, this pin can<br>handle standard I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P1.4/SS/CEX1 | 5             | 44     | 6           | I/O                             | <b>P1.4</b> — Port 1 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             | Ι                               | <b>SS</b> — Slave port select input for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              |               |        |             | I/O                             | <b>CEX1</b> — Capture/compare external I/O for PCA Module 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P1.5/MOSI/   | / 6 1         |        | 7           | I/O                             | <b>P1.5</b> — Port 1 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CEX2         |               |        |             | I/O                             | MOSI — Master Output Slave Input for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |               |        |             | I/O                             | <b>CEX2</b> — Capture/compare external I/O for PCA Module 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P1.6/MISO/   | 7             | 2      | 8           | I/O                             | <b>P1.6</b> — Port 1 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CEX3         |               |        |             | I/O                             | MISO — Master Input Slave Output for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |               |        |             | I/O                             | <b>CEX3</b> — Capture/compare external I/O for PCA Module 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P1.7/SPICLK/ | 8             | 3      | 9           | I/O                             | <b>P1.7</b> — Port 1 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CEX4         |               |        |             | I/O                             | SPICLK — Serial clock input/output for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             | I/O                             | <b>CEX4</b> — Capture/compare external I/O for PCA Module 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P2.0 to P2.7 |               |        |             | I/O with<br>internal<br>pull-up | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins are pulled HIGH by the internal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, Port 2 pins that are externally pulled LOW will source current ( $I_{IL}$ ) because of the internal pull-ups. Port 2 sends the high-order address byte during fetches from external program memory and during accesses to external Data Memory that use 16-bit address (MOVX@DPTR). In this application, it uses strong internal pull-ups when transitioning to '1's. Port 2 also receives some control signals and a partial of high-order address bits during the external host mode programming and verification. |

| P2.0/A8      | 21            | 18     | 24          | I/O                             | <b>P2.0</b> — Port 2 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             | 0                               | A8 — Address bit 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P2.1/A9      | 22            | 19     | 25          | I/O                             | <b>P2.1</b> — Port 2 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             | 0                               | A9 — Address bit 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P2.2/A10     | 23            | 20     | 26          | I/O                             | <b>P2.2</b> — Port 2 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             | 0                               | A10 — Address bit 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P2.3/A11     | 24            | 21     | 27          | I/O                             | <b>P2.3</b> — Port 2 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             | 0                               | A11 — Address bit 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P2.4/A12     | 25            | 22     | 28          | I/O                             | <b>P2.4</b> — Port 2 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |               |        |             | 0                               | A12 — Address bit 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              |               |        |             |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### Table 3 P89V51RB2/RC2/RD2 pin description ... continued

P89V51RB2\_RC2\_RD2\_5

Product data sheet

8-bit microcontrollers with 80C51 core

| Symbol          | Pin   |                  |                  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|-------|------------------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | DIP40 | TQFP44           | PLCC44           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RST             | 9     | 4                | 10               | I    | <b>Reset</b> : While the oscillator is running, a HIGH logic state<br>on this pin for two machine cycles will reset the device. If<br>the PSEN pin is driven by a HIGH-to-LOW input transition<br>while the RST input pin is held HIGH, the device will enter<br>the external host mode, otherwise the device will enter the<br>normal operation mode.                                                                                                                                                                               |

| ĒĀ              | 31    | 29               | 35               | I    | <b>External Access Enable</b> : $\overline{EA}$ must be connected to V <sub>SS</sub> in order to enable the device to fetch code from the external program memory. $\overline{EA}$ must be strapped to V <sub>DD</sub> for internal program execution. The $\overline{EA}$ pin can tolerate a high voltage of 12 V.                                                                                                                                                                                                                  |

| ALE/PROG        | 30    | 27               | 33               | I/O  | Address Latch Enable: ALE is the output signal for<br>latching the low byte of the address during an access to<br>external memory. This pin is also the programming pulse<br>input (PROG) for flash programming. Normally the ALE <sup>[1]</sup><br>is emitted at a constant rate of <sup>1</sup> / <sub>6</sub> the crystal frequency <sup>[2]</sup><br>and can be used for external timing and clocking. One ALE<br>pulse is skipped during each access to external data<br>memory. However, if AO is set to '1', ALE is disabled. |

| n.c.            | -     | 6, 17, 28,<br>39 | 1, 12, 23,<br>34 | I/O  | not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTAL1           | 19    | 15               | 21               | I    | <b>Crystal 1</b> : Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| XTAL2           | 18    | 14               | 20               | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub> | 40    | 38               | 44               | I    | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> | 20    | 16               | 22               | I    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 3. P89V51RB2/RC2/RD2 pin description ...continued

ALE loading issue: When ALE pin experiences higher loading (>30 pF) during the reset, the microcontroller may accidentally enter into modes other than normal working mode. The solution is to add a pull-up resistor of 3 kΩ to 50 kΩ to V<sub>DD</sub>, e.g., for ALE pin.

[2] For 6-clock mode, ALE is emitted at  $\frac{1}{3}$  of crystal frequency.

8-bit microcontrollers with 80C51 core

### 6. Functional description

### 6.1 Special function registers

Remark: SFR accesses are restricted in the following ways:

- User must not attempt to access any SFR locations not defined.

- Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

- SFR bits labeled '-', '0' or '1' can **only** be written and read as follows:

- '-' Unless otherwise specified, must be written with '0', but can return any value when read (even if it was written with '0'). It is a reserved bit and may be used in future derivatives.

- '0' must be written with '0', and will return a '0' when read.

- '1' **must** be written with '1', and will return a '1' when read.

8-bit microcontrollers with 80C51 core

| Bit      | 7          | 6            | 5            | 4                          | 3                         | 2           | 1                                                   | 0      |

|----------|------------|--------------|--------------|----------------------------|---------------------------|-------------|-----------------------------------------------------|--------|

| Symbol   | -          | -            | -            | -                          | -                         | -           | EXTRAM                                              | AO     |

| Table 8. | AUXR - Aux | diliary re   | gister (add  | dress 8EH                  | ) bit descri              | iption      |                                                     |        |

| Bit      | Symbol     | Des          | cription     |                            |                           |             |                                                     |        |

| 7 to 2   | -          | Res          | erved for fu | iture use. S               | Should be s               | et to '0' b | y user program                                      | s.     |

| 1        | EXTRAM     | core         | attempts t   | o access ir                | nternal XRA               | AM with a   | Ri/@DPTR. W<br>ddress specifie<br>s instruction exe | d in   |

|          |            | on-c<br>acce | hip availab  | le XRAM, (<br>en '1', ever | off-chip XR/<br>/ MOVX @I | AM is goi   | ng to be selecte<br>R instruction ta                | ed and |

### Table 7. AUXR - Auxiliary register (address 8EH) bit allocation

When instructions access addresses in the upper 128 B (above 7FH), the MCU determines whether to access the SFRs or RAM by the type of instruction given. If it is indirect, then RAM is accessed. If it is direct, then an SFR is accessed. See the examples below.

Indirect Access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper address range. Data in '#data' is written to RAM location 90H rather than port 1.

Direct Access:

MOV90H, #data; write data to P1

Data in '#data' is written to port 1. Instructions that write directly to the address write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be cleared and MOVX instructions must be used. The extra 768 B of memory is physically located on the chip and logically occupies the first 768 B of external memory (addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly addressed using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. Accessing the expanded RAM does not affect ports P0, P3.6 ( $\overline{WR}$ ), P3.7 ( $\overline{RD}$ ), or P2. With EXTRAM = 0, the expanded RAM can be accessed as in the following example.

Expanded RAM Access (Indirect Addressing only):

MOVX@DPTR, A DPTR contains 0A0H

8-bit microcontrollers with 80C51 core

DPTR points to 0A0H and data in 'A' is written to address 0A0H of the expanded RAM rather than external memory. Access to external memory higher than 2FFH using the MOVX instruction will access external memory (0300H to FFFFH) and will perform in the same way as the standard 8051, with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals.

When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 8051. Using MOVX @Ri provides an 8-bit address with multiplexed data on Port 0. Other output port pins can be used to output higher order address bits. This provides external paging capabilities. Using MOVX @DPTR generates a 16-bit address. This allows external addressing up the 64 kB. Port 2 provides the high-order eight address bits (DPH), and Port 0 multiplexes the low order eight address bits (DPL) with data. Both MOVX @Ri and MOVX @DPTR generates the necessary read and write signals (P3.6 - WR and P3.7 - RD) for external memory use. Table 9 shows external data memory RD, WR operation with EXTRAM bit.

The stack pointer (SP) can be located anywhere within the 256 B of internal RAM (lower 128 B and upper 128 B). The stack pointer may not be located in any part of the expanded RAM.

| AUXR       | MOVX @DPTR, A<br>@DPTR | or MOVX A,                          | MOVX @Ri, A or MOVX A, @Ri |

|------------|------------------------|-------------------------------------|----------------------------|

|            | ADDR < 0300H           | $\textbf{ADDR} \geq \textbf{0300H}$ | ADDR = any                 |

| EXTRAM = 0 | RD/WR not asserted     | RD/WR asserted                      | RD/WR not asserted         |

| EXTRAM = 1 | RD/WR asserted         | RD/WR asserted                      | RD/WR asserted             |

#### Table 9. External data memory RD, WR with EXTRAM bit<sup>[1]</sup>

[1] Access limited to ERAM address within OSPI to 0FFH; cannot access 100H to 02FFH.

8-bit microcontrollers with 80C51 core

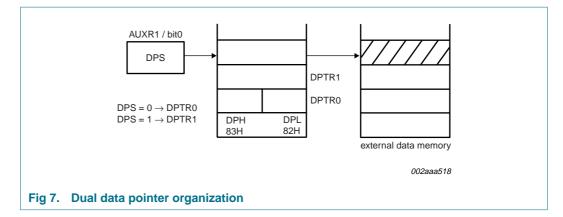

# Table 10. AUXR1 - Auxiliary register 1 (address A2H) bit allocation Not bit addressable; Reset value 00H

| Bit    | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   |

|--------|---|---|---|---|-----|---|---|-----|

| Symbol | - | - | - | - | GF2 | 0 | - | DPS |

#### Table 11. AUXR1 - Auxiliary register 1 (address A2H) bit description

| Bit    | Symbol | Description                                                                                                                                    |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 4 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 3      | GF2    | General purpose user-defined flag.                                                                                                             |

| 2      | 0      | This bit contains a hard-wired '0'. Allows toggling of the DPS bit by incrementing AUXR1, without interfering with other bits in the register. |

| 1      | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 0      | DPS    | Data pointer select. Chooses one of two Data Pointers for use by the program. See text for details.                                            |

### 6.3 Flash memory IAP

### 6.3.1 Flash organization

The P89V51RB2/RC2/RD2 program memory consists of a 16/32/64 kB block. ISP capability, in a second 8 kB block, is provided to allow the user code to be programmed in-circuit through the serial port. There are three methods of erasing or programming of the flash memory that may be used. First, the flash may be programmed or erased in the end-user application by calling low-level routines through a common entry point (IAP). Second, the on-chip ISP bootloader may be invoked. This ISP bootloader will, in turn, call low-level routines through the same common entry point that can be used by the end-user application. Third, the flash may be programmed or erased using the parallel method by using a commercially available EPROM programmer which supports this device.

### 6.3.2 Boot block (block 1)

When the microcontroller programs its own flash memory, all of the low level details are handled by code that is contained in block 1. A user program calls the common entry point in the block 1 with appropriate parameters to accomplish the desired operation. Boot block operations include erase user code, program user code, program security bits, etc.

8-bit microcontrollers with 80C51 core

| Record type | Command/data function                                                                                                                                                                                                                                                  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05          | Miscellaneous Read Functions<br>:02xxxx05ffsscc<br>Where:<br>02 = number of bytes in the record<br>xxxx = required field but value is a 'don't care'<br>05 = function code for misc read<br>ffss = subfunction and selection code<br>0000 = read manufacturer id       |

|             | 0001 = read device id 1<br>0002 = read boot code version<br>0700 = read security bit (00 SoftICE serial number match 0 SB 0 Double Clock<br>cc = checksum<br>Example:<br>:020000050000F9 (display manufacturer id)                                                     |

| 06          | Direct Load of Baud Rate<br>:02xxxx06HHLLcc<br>Where:<br>02 = number of bytes in the record<br>xxxx = required field but value is a 'don't care'<br>HH = high byte of timer<br>LL = low byte of timer<br>cc = checksum<br>Example:<br>:02000006FFFFcc (load T2 = FFFF) |

| 07          | Reset serial number, erase user code, clear SoftICE mode<br>:xxxxx07cc<br>Where:<br>xxxxx = required field but value is a 'don't care'<br>07 = reset serial number function<br>cc = checksum<br>Example:<br>:00000007F9                                                |

| 08          | Verify serial number<br>:nnxxx08sssscc<br>Where:<br>xxxxx = required field but value is a 'don't care'<br>08 = verify serial number function<br>ssss = serial number contents<br>cc = checksum<br>Example:<br>:03000008010203EF (verify s/n = 010203)                  |

8-bit microcontrollers with 80C51 core

| IAP function                                | IAP call parameters                       |  |  |  |  |

|---------------------------------------------|-------------------------------------------|--|--|--|--|

| Program Security Bit, Double                | Input parameters:                         |  |  |  |  |

| Clock                                       | R1 = 05H                                  |  |  |  |  |

|                                             | DPL = 01H = security bit                  |  |  |  |  |

|                                             | DPL = 05H = Double Clock                  |  |  |  |  |

|                                             | Return parameter(s):                      |  |  |  |  |

|                                             | ACC = 00 = pass                           |  |  |  |  |

|                                             | ACC = !00 = fail                          |  |  |  |  |

| Read Security Bit, Double Clock,<br>SoftICE | Input parameters:                         |  |  |  |  |

|                                             | ACC = 07H                                 |  |  |  |  |

|                                             | Return parameter(s):                      |  |  |  |  |

|                                             | ACC = 00 SoftICE S/N-match 0 SB 0 DBL_CLK |  |  |  |  |

| Erase sector                                | Input parameters:                         |  |  |  |  |

|                                             | R1 = 08H                                  |  |  |  |  |

|                                             | DPH = sector address high byte            |  |  |  |  |

|                                             | DPL = sector address low byte             |  |  |  |  |

|                                             | Return parameter(s):                      |  |  |  |  |

|                                             | ACC = 00 = pass                           |  |  |  |  |

|                                             | ACC = !00 = fail                          |  |  |  |  |

#### Table 13. IAP function calls ...continued

### 6.4 Timers/counters 0 and 1

The two 16-bit Timer/counter registers: Timer 0 and Timer 1 can be configured to operate either as timers or event counters (see Table 14 and Table 15).

In the 'Timer' function, the register is incremented every machine cycle. Thus, one can think of it as counting machine cycles. Since a machine cycle consists of six oscillator periods, the count rate is  $\frac{1}{6}$  of the oscillator frequency.

In the 'Counter' function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled once every machine cycle.

When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register in the machine cycle following the one in which the transition was detected. Since it takes two machine cycles (12 oscillator periods) for 1-to-0 transition to be recognized, the maximum count rate is 1/12 of the oscillator frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle. In addition to the 'Timer' or 'Counter' selection, Timer 0 and Timer 1 have four operating modes from which to select.

The 'Timer' or 'Counter' function is selected by control bits C/T in the Special Function Register TMOD. These two Timer/counters have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both Timers/counters. Mode 3 is different. The four operating modes are described in the following text.

8-bit microcontrollers with 80C51 core

not cause a reload from (RCAP2H, RCAP2L) to (TH2,TL2). Therefore when Timer 2 is in use as a baud rate generator, T2EX can be used as an additional external interrupt, if needed.

When Timer 2 is in the baud rate generator mode, one should not try to read or write TH2 and TL2. Under these conditions, a read or write of TH2 or TL2 may not be accurate. The RCAP2 registers may be read, but should not be written to, because a write might overlap a reload and cause write and/or reload errors. The timer should be turned off (clear TR2) before accessing the Timer 2 or RCAP2 registers. <u>Table 24</u> shows commonly used baud rates and how they can be obtained from Timer 2.

### 6.5.5 Summary of baud rate equations

Timer 2 is in baud rate generating mode. If Timer 2 is being clocked through pin T2 (P1.0) the baud rate is:

Baud rate = Timer 2 overflow rate / 16

If Timer 2 is being clocked internally, the baud rate is:

Baud rate =  $f_{osc}$  / (16 × (65536 – (RCAP2H, RCAP2L)))

Where  $f_{osc}$  = oscillator frequency

To obtain the reload value for RCAP2H and RCAP2L, the above equation can be rewritten as:

RCAP2H, RCAP2L =  $65536 - f_{osc} / (16 \times baud rate)$

| Table 24. | Timer 2 | generated | commonly | used ba | aud rates |

|-----------|---------|-----------|----------|---------|-----------|

|-----------|---------|-----------|----------|---------|-----------|

| Rate     | Osc freq | Timer 2 |        |  |  |

|----------|----------|---------|--------|--|--|

|          |          | RCAP2H  | RCAP2L |  |  |

| 750 kBd  | 12 MHz   | FF      | FF     |  |  |

| 19.2 kBd | 12 MHz   | FF      | D9     |  |  |

| 9.6 kBd  | 12 MHz   | FF      | B2     |  |  |

| 4.8 kBd  | 12 MHz   | FF      | 64     |  |  |

| 2.4 kBd  | 12 MHz   | FE      | C8     |  |  |

| 600 Bd   | 12 MHz   | FB      | 1E     |  |  |

| 220 Bd   | 12 MHz   | F2      | AF     |  |  |

| 600 Bd   | 6 MHz    | FD      | 8F     |  |  |

| 220 Bd   | 6 MHz    | F9      | 57     |  |  |

### 6.6 UARTs

The UART operates in all standard modes. Enhancements over the standard 80C51 UART include Framing Error detection, and automatic address recognition.

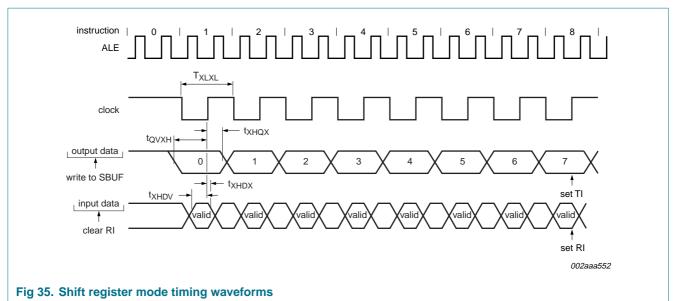

#### 6.6.1 Mode 0

Serial data enters and exits through RXD and TXD outputs the shift clock. Only 8 bits are transmitted or received, LSB first. The baud rate is fixed at  $\frac{1}{6}$  of the CPU clock frequency. UART configured to operate in this mode outputs serial clock on TXD line no matter whether it sends or receives data on RXD line.

The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated: (a) RI = 0, and (b) either SM2 = 0, or the received 9th data bit = 1.

If either of these conditions is not met, the received frame is irretrievably lost, and RI is not set. If both conditions are met, the received 9th data bit goes into RB8, and the first 8 data bits go into SBUF.

#### 6.6.8 Multiprocessor communications

UART modes 2 and 3 have a special provision for multiprocessor communications. In these modes, 9 data bits are received or transmitted. When data is received, the 9th bit is stored in RB8. The UART can be programmed so that when the stop bit is received, the serial port interrupt will be activated only if RB8 = 1. This feature is enabled by setting bit SM2 in SCON. One way to use this feature in multiprocessor systems is as follows:

When the master processor wants to transmit a block of data to one of several slaves, it first sends out an address byte which identifies the target slave. An address byte differs from a data byte in a way that the 9th bit is '1' in an address byte and '0' in the data byte. With SM2 = 1, no slave will be interrupted by a data byte, i.e. the received 9th bit is '0'. However, an address byte having the 9th bit set to '1' will interrupt all slaves, so that each slave can examine the received byte and see if it is being addressed or not. The addressed slave will clear its SM2 bit and prepare to receive the data (still 9 bits long) that follow. The slaves that weren't being addressed leave their SM2 bits set and go on about their business, ignoring the subsequent data bytes.

SM2 has no effect in mode 0, and in mode 1 can be used to check the validity of the stop bit, although this is better done with the Framing Error flag. When UART receives data in mode 1 and SM2 = 1, the receive interrupt will not be activated unless a valid stop bit is received.

#### 6.6.9 Automatic address recognition

Automatic Address Recognition is a feature which allows the UART to recognize certain addresses in the serial bit stream by using hardware to make the comparisons. This feature saves a great deal of software overhead by eliminating the need for the software to examine every serial address which passes by the serial port. This feature is enabled for the UART by setting the SM2 bit in SCON. In the 9 bit UART modes, mode 2 and mode 3, the Receive Interrupt flag (RI) will be automatically set when the received byte contains either the 'Given' address or the 'Broadcast' address. The 9 bit mode requires that the 9th information bit is a '1' to indicate that the received information is an address and not data.

Using the Automatic Address Recognition feature allows a master to selectively communicate with one or more slaves by invoking the Given slave address or addresses. All of the slaves may be contacted by using the Broadcast address. Two Special Function Registers are used to define the slave's address, SADDR, and the address mask, SADEN. SADEN is used to define which bits in the SADDR are to be used and which bits are 'don't care'. The SADEN mask can be logically ANDed with the SADDR to create the 'Given' address which the master will use for addressing each of the slaves. Use of the Given address allows multiple slaves to be recognized while excluding others.

This device uses the methods presented in Figure 16 to determine if a 'Given' or 'Broadcast' address has been received or not.

#### 8-bit microcontrollers with 80C51 core

Table 29.

SPCR - SPI control register (address D5H) bit description ...continued

| Bit | Symbol | Description                                                                                                                                                              |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

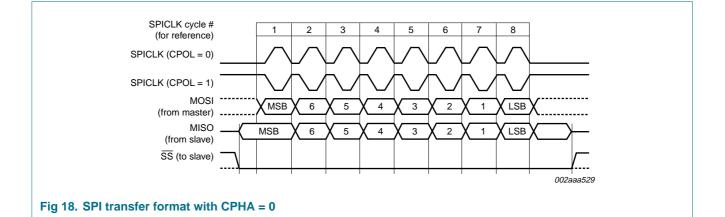

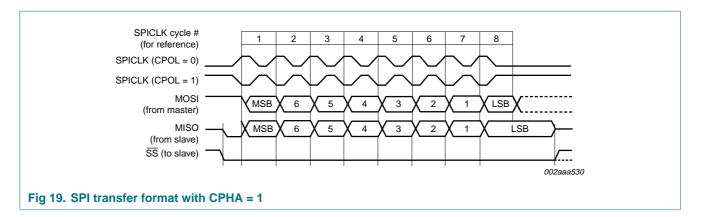

| 2   | СРНА   | Clock Phase control bit. $1 = $ shift triggered on the trailing edge of the clock; $0 = $ shift triggered on the leading edge of the clock.                              |

| 1   | SPR1   | SPI Clock Rate Select bit 1. Along with SPR0 controls the SPICLK rate of the device when a master. SPR1 and SPR0 have no effect on the slave. See <u>Table 30</u> below. |

| 0   | SPR0   | SPI Clock Rate Select bit 0. Along with SPR1 controls the SPICLK rate of the device when a master. SPR1 and SPR0 have no effect on the slave. See <u>Table 30</u> below. |

Table 30. SPCR - SPI control register (address D5H) clock rate selection

| SPR1 | SPR0 | SPICLK = f <sub>osc</sub> divided by |

|------|------|--------------------------------------|

| 0    | 0    | 4                                    |

| 0    | 1    | 16                                   |

| 1    | 0    | 64                                   |

| 1    | 1    | 128                                  |

### Table 31. SPSR - SPI status register (address AAH) bit allocation

Bit addressable; Reset source(s): any reset; Reset value: 0000 0000B

| Bit    | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|------|------|---|---|---|---|---|---|

| Symbol | SPIF | WCOL | - | - | - | - | - | - |

#### Table 32. SPSR - SPI status register (address AAH) bit description

| Bit    | Symbol | Description                                                                                                                                                            |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | SPIF   | SPI interrupt flag. Upon completion of data transfer, this bit is set to '1'. If SPIE = 1 and ES = 1, an interrupt is then generated. This bit is cleared by software. |

| 6      | WCOL   | Write Collision Flag. Set if the SPI data register is written to during data transfer. This bit is cleared by software.                                                |

| 5 to 0 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                                        |

8-bit microcontrollers with 80C51 core

### 6.8 Watchdog timer

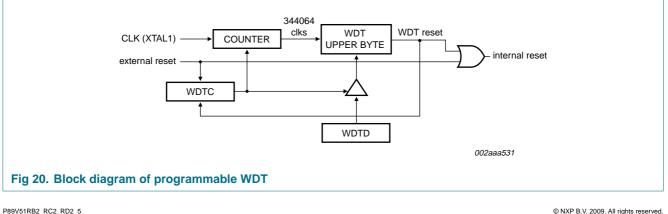

The device offers a programmable Watchdog Timer (WDT) for fail safe protection against software deadlock and automatic recovery.

To protect the system against software deadlock, the user software must refresh the WDT within a user-defined time period. If the software fails to do this periodical refresh, an internal hardware reset will be initiated if enabled (WDRE = 1). The software can be designed such that the WDT times out if the program does not work properly.

The WDT in the device uses the system clock (XTAL1) as its time base. So strictly speaking, it is a Watchdog counter rather than a WDT. The WDT register will increment every 344064 crystal clocks. The upper 8-bits of the time base register (WDTD) are used as the reload register of the WDT.

The WDTS flag bit is set by WDT overflow and is not changed by WDT reset. User software can clear WDTS by writing '1' to it.

Figure 20 provides a block diagram of the WDT. Two SFRs (WDTC and WDTD) control WDT operation. During Idle mode, WDT operation is temporarily suspended, and resumes upon an interrupt exit from idle.

The time-out period of the WDT is calculated as follows:

$Period = (255 - WDTD) \times 344064 \times 1 / f_{CLK(XTAL1)}$

where WDTD is the value loaded into the WDTD register and  $\ensuremath{f_{\text{osc}}}$  is the oscillator frequency.

### **NXP Semiconductors**

### P89V51RB2/RC2/RD2

8-bit microcontrollers with 80C51 core

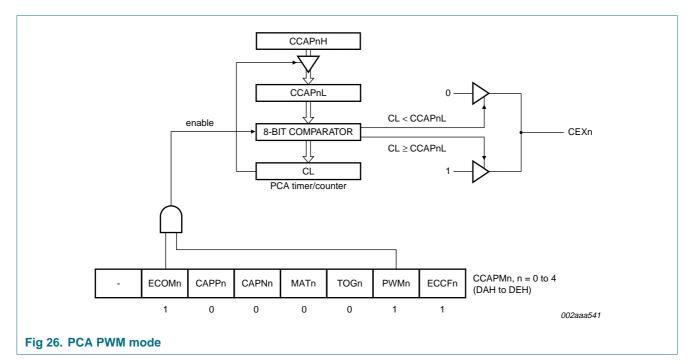

#### 6.9.4 PWM mode

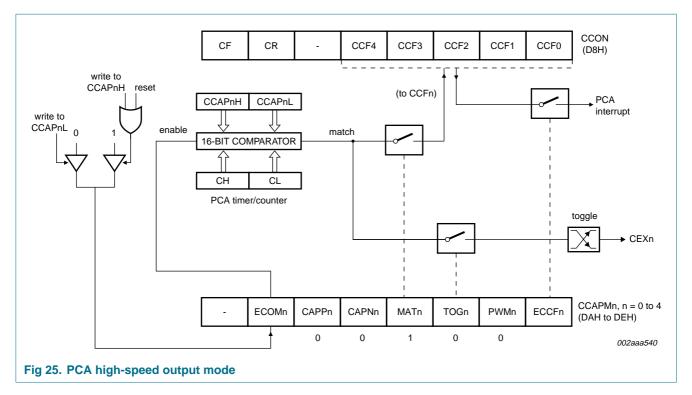

All of the PCA modules can be used as PWM outputs (Figure 26). Output frequency depends on the source for the PCA timer.

All of the modules will have the same frequency of output because they all share one and only PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPnL. When the value of the PCA CL SFR is less than the

### 8-bit microcontrollers with 80C51 core

#### Table 45. IEN0 - Interrupt enable register 0 (address A8H) bit description

| Bit | Symbol | Description                                                                                     |

|-----|--------|-------------------------------------------------------------------------------------------------|

| 7   | EA     | Interrupt Enable Bit: EA = 1 interrupt(s) can be serviced, EA = 0 interrupt servicing disabled. |

| 6   | EC     | PCA Interrupt Enable bit.                                                                       |

| 5   | ET2    | Timer 2 Interrupt Enable.                                                                       |

| 4   | ES     | Serial Port Interrupt Enable.                                                                   |

| 3   | ET1    | Timer 1 Overflow Interrupt Enable.                                                              |

| 2   | EX1    | External Interrupt 1 Enable.                                                                    |

| 1   | ET0    | Timer 0 Overflow Interrupt Enable.                                                              |

| 0   | EX0    | External Interrupt 0 Enable.                                                                    |

### Table 46. IEN1 - Interrupt enable register 1 (address E8H) bit allocation Bit addressable; Reset value: 00H

| Bit    | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 |

|--------|---|---|---|---|-----|---|---|---|

| Symbol | - | - | - | - | EBO | - | - | - |

#### Table 47. IEN1 - Interrupt enable register 1 (address E8H) bit description

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 4 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 3      | EBO    | Brownout Interrupt Enable. 1 = enable, 0 = disable.             |

| 2 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

### Table 48. IP0 - Interrupt priority 0 low register (address B8H) bit allocation Bit addressable; Reset value: 00H

|        | , |     |     |    |     |     |     |     |

|--------|---|-----|-----|----|-----|-----|-----|-----|

| Bit    | 7 | 6   | 5   | 4  | 3   | 2   | 1   | 0   |

| Symbol | - | PPC | PT2 | PS | PT1 | PX1 | PT0 | PX0 |

#### Table 49. IP0 - Interrupt priority 0 low register (address B8H) bit description

| Bit | Symbol | Description                                                     |

|-----|--------|-----------------------------------------------------------------|

| 7   | -      | Reserved for future use. Should be set to '0' by user programs. |

| 6   | PPC    | PCA interrupt priority LOW bit.                                 |

| 5   | PT2    | Timer 2 interrupt priority LOW bit.                             |

| 4   | PS     | Serial Port interrupt priority LOW bit.                         |

| 3   | PT1    | Timer 1 interrupt priority LOW bit.                             |

| 2   | PX1    | External interrupt 1 priority LOW bit.                          |

| 1   | PT0    | Timer 0 interrupt priority LOW bit.                             |

| 0   | PX0    | External interrupt 0 priority LOW bit.                          |

### Table 50. IP0H - Interrupt priority 0 high register (address B7H) bit allocation Not bit addressable; Reset value: 00H

| Bit    | 7 | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|--------|---|------|------|-----|------|------|------|------|

| Symbol | - | PPCH | PT2H | PSH | PT1H | PX1H | PT0H | PX0H |

8-bit microcontrollers with 80C51 core

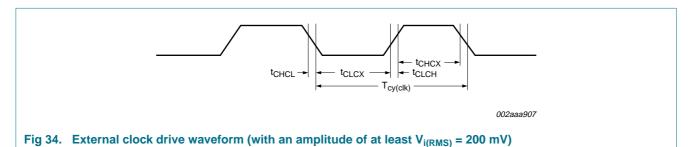

| Symbol               | Parameter            | Oscillat | Oscillator |                          |                   |     |  |

|----------------------|----------------------|----------|------------|--------------------------|-------------------|-----|--|

|                      |                      | 40 MHz   | 40 MHz     |                          | Variable          |     |  |

|                      |                      | Min      | Max        | Min                      | Max               |     |  |

| f <sub>osc</sub>     | oscillator frequency | -        | -          | 0                        | 40                | MHz |  |

| T <sub>cy(clk)</sub> | clock cycle time     | 25       | -          | -                        | -                 | ns  |  |

| t <sub>CHCX</sub>    | clock HIGH time      | 8.75     | -          | 0.35T <sub>cy(clk)</sub> | $0.65T_{cy(clk)}$ | ns  |  |

| t <sub>CLCX</sub>    | clock LOW time       | 8.75     | -          | 0.35T <sub>cy(clk)</sub> | $0.65T_{cy(clk)}$ | ns  |  |

| t <sub>CLCH</sub>    | clock rise time      | -        | 10         | -                        | -                 | ns  |  |

| t <sub>CHCL</sub>    | clock fall time      | -        | 10         | -                        | -                 | ns  |  |

| Symbol            | Parameter                                     | Oscillator |     |                              |                     | Unit |

|-------------------|-----------------------------------------------|------------|-----|------------------------------|---------------------|------|

|                   |                                               | 40 MHz     |     | Variable                     |                     |      |

|                   |                                               | Min        | Max | Min                          | Max                 | -    |

| T <sub>XLXL</sub> | serial port clock cycle time                  | 0.3        | -   | 12T <sub>cy(clk)</sub>       | -                   | μs   |

| t <sub>QVXH</sub> | output data set-up to clock rising edge time  | 117        | -   | 10T <sub>cy(clk)</sub> – 133 | -                   | ns   |

| t <sub>XHQX</sub> | output data hold after clock rising edge time | 0          | -   | $2 T_{cy(clk)} - 50$         | -                   | ns   |

| t <sub>XHDX</sub> | input data hold after clock rising edge time  | 0          | -   | 0                            | -                   | ns   |

| t <sub>XHDV</sub> | input data valid to clock rising edge time    | -          | 117 | -                            | $10T_{cy(clk)}-133$ | ns   |

#### Table 65. Serial port timing

8-bit microcontrollers with 80C51 core

| Symbol               | Parameter                                          | Conditions                                                   | Variable clock        |                          | f <sub>osc</sub> = 18 MHz |      | Unit |

|----------------------|----------------------------------------------------|--------------------------------------------------------------|-----------------------|--------------------------|---------------------------|------|------|

|                      |                                                    |                                                              | Min                   | Max                      | Min                       | Max  |      |

| f <sub>SPI</sub>     | SPI operating frequency                            |                                                              | 0                     | T <sub>cy(clk)</sub> / 4 | 0                         | 10   | MHz  |

| T <sub>SPICYC</sub>  | SPI cycle time                                     | see Figure 36, 37, 38, 39                                    | 4T <sub>cy(clk)</sub> | -                        | 222                       | -    | ns   |

| t <sub>SPILEAD</sub> | SPI enable lead time                               | see Figure 38, <u>39</u>                                     | 250                   | -                        | 250                       | -    | ns   |

| t <sub>SPILAG</sub>  | SPI enable lag time                                | see Figure 38, <u>39</u>                                     | 250                   | -                        | 250                       | -    | ns   |

| t <sub>SPICLKH</sub> | SPICLK HIGH time                                   | see Figure 36, <u>37</u> , <u>38</u> , <u>39</u>             | 2T <sub>cy(clk)</sub> | -                        | 111                       | -    | ns   |

| t <sub>SPICLKL</sub> | SPICLK LOW time                                    | see Figure 36, <u>37, 38, 39</u>                             | 2T <sub>cy(clk)</sub> | -                        | 111                       | -    | ns   |

| t <sub>SPIDSU</sub>  | SPI data set-up time                               | master or slave; see<br><u>Figure 36, 37</u> , <u>38, 39</u> | 100                   | -                        | 100                       | -    | ns   |

| t <sub>SPIDH</sub>   | SPI data hold time                                 | master or slave; see<br><u>Figure 36, 37, 38, 39</u>         | 100                   | -                        | 100                       | -    | ns   |

| t <sub>SPIA</sub>    | SPI access time                                    | see Figure 38, <u>39</u>                                     | 0                     | 80                       | 0                         | 80   | ns   |

| t <sub>SPIDIS</sub>  | SPI disable time                                   | see <u>Figure 38,</u> <u>39</u>                              | 0                     | 160                      | -                         | 160  | ns   |

| t <sub>SPIDV</sub>   | SPI enable to output data valid time               | see <u>Figure 36</u> , <u>37</u> , <u>38</u> , <u>39</u>     | -                     | 111                      | -                         | 111  | ns   |

| t <sub>SPIOH</sub>   | SPI output data hold time                          | see <u>Figure 36</u> , <u>37</u> , <u>38</u> , <u>39</u>     | 0                     | -                        | 0                         | -    | ns   |

| t <sub>SPIR</sub>    | SPI rise time                                      | see Figure 36, <u>37</u> , <u>38</u> , <u>39</u>             |                       |                          |                           |      |      |

|                      | SPI outputs (SPICLK, MOSI, MISO)                   |                                                              | -                     | 100                      | -                         | 100  | ns   |

|                      | SPI inputs (SPICLK,<br>MOSI, MISO, <del>SS</del> ) |                                                              | -                     | 2000                     | -                         | 2000 | ns   |

| t <sub>SPIF</sub>    | SPI fall time                                      | see Figure 36, <u>37, 38, 39</u>                             |                       |                          |                           |      |      |

|                      | SPI outputs (SPICLK, MOSI, MISO)                   |                                                              | -                     | 100                      | -                         | 100  | ns   |

|                      | SPI inputs (SPICLK,<br>MOSI, MISO, SS)             |                                                              | -                     | 2000                     | -                         | 2000 | ns   |

Table 66. SPI interface timing

P89V51RB2\_RC2\_RD2\_5

8-bit microcontrollers with 80C51 core