Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TC)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-QFN (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ata6612p-plqw |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5. Electrical Characteristics (Continued)

$5V < V_s < 27V$ ,  $40^{\circ}C < J_{case} < 125^{\circ}C$ ,  $40^{\circ}C < T_i < 150^{\circ}C$ , unless otherwise specified. All values refer to GND pins

| No.  | Parameters                                    | Test Conditions                                                              | Pin        | Symbol                  | Min.              | Тур. | Max.                     | Unit   | Type* |

|------|-----------------------------------------------|------------------------------------------------------------------------------|------------|-------------------------|-------------------|------|--------------------------|--------|-------|

| 12   | NRES Open Drain Outp                          | ut Pin                                                                       |            |                         |                   |      |                          |        |       |

| 12.1 | Low-level output volta                        | V <sub>s</sub> 5.5V<br>94 <sub>NRES</sub> = 1mA<br>1 <sub>NRES</sub> = 250µA | NRES       | V <sub>NRESL</sub>      |                   |      | 0.2<br>0.14              | V<br>V | A     |

| 12.2 | Low-level output low                          | $\begin{array}{l} 10k  to \ V_{CC} \\ V_{CC} \ = \ OV \end{array}$           | NRES       | V <sub>NRESLL</sub>     |                   |      | 0.2                      | V      | A     |

| 12.3 | Undervoltage reset tin                        | V <sub>S</sub> 5.5V<br>C <sub>NRES</sub> = 20pF                              | NRES       | t <sub>reset</sub>      | 2                 | 4    | 6                        | ms     | A     |

| 12.4 | Reset debounce time for falling edge          | b∀ <sub>s</sub> 5.5V<br>C <sub>NRES</sub> = 20pF                             | NRES       | t <sub>res_f</sub>      | 1.5               |      | 10                       | aų     | A     |

| 13   | Watchdog Oscillator                           |                                                                              |            |                         | I                 |      |                          |        |       |

| 13.1 | Voltage at WD_OSC in Normal Mode              | $I_{WD_OSC} = 200\mu A$<br>$V_{VS} = 4V$                                     | WD_<br>OSC | V <sub>WD_OSC</sub>     | 1.13              | 1.23 | 1.33                     | V      | A     |

| 13.2 | Possible values of resistor                   |                                                                              | WD_<br>OSC | R <sub>OSC</sub>        | 34                |      | 120                      | k      | A     |

| 13.3 | Oscillator period                             | $R_{SC} = 34k$                                                               |            | t <sub>osc</sub>        | 10.65             | 13.3 | 15.97                    | aų     | ŀ     |

| 13.4 | Oscillator period                             | e <sup>R</sup> <sub>SC</sub> = 51k                                           |            | t <sub>osc</sub>        | 15.68             | 19.6 | 23.52                    | ац     |       |

| 13.5 | Oscillator period                             | $B_{SC} = 91k$                                                               |            | t <sub>osc</sub>        | 26.83             | 33.5 | 40.24                    | ац     |       |

| 13.6 | Oscillator period                             | B <sub>C</sub> = 120k                                                        |            | t <sub>osc</sub>        | 34.2              | 42.8 | 51.4                     | aų     |       |

| 14   | Watchdog Timing Relat                         | ive to $d_{SC}$                                                              |            |                         |                   |      |                          |        |       |

| 14.1 | Watchdog lead time aft<br>Reset               | er                                                                           |            | t <sub>a</sub>          |                   | 7895 |                          | cycles | ŀ     |

| 14.2 | Watchdog closed window                        |                                                                              |            | t <sub>1</sub>          |                   | 1053 |                          | cycles | A     |

| 14.3 | Watchdog open windo                           | w                                                                            |            | <sub>2</sub> t          |                   | 1105 |                          | cycles | A     |

| 14.4 | Watchdog reset time<br>NRES                   |                                                                              | NRES       | t <sub>nres</sub>       | 3.2               | 4    | 4.8                      | ms     | ŀ     |

| 15   | KL_15 Pin                                     | L                                                                            | 1          | 11                      |                   |      | L1                       |        |       |

| 15.1 | High-level input voltage $R_v = 47 \text{ k}$ | Positive edge initializes a wake-up                                          | KL_15      | V <sub>KL_15H</sub>     | 4                 |      | V <sub>S</sub> +<br>0.3V | V      | A     |

| 15.2 | Low-level input voltage $R_v = 47 \text{ k}$  |                                                                              | KL_15      | V <sub>KL_15L</sub>     | 1                 |      | +2                       | V      | А     |

| 15.3 | KL_15 pull-down curre                         | V <sub>S</sub> < 27V<br>V <sub>KL_15</sub> = 27V                             | KL_15      | I <sub>KL_15</sub>      |                   | 50   | 65                       | μA     | A     |

| 15.4 | Internal debounce time                        |                                                                              | itor K     | L_15 <sub>KL_</sub> Tgb | 80                | 160  | 250                      | aų     | 1     |

| 15.5 | KL_15 wake-up time                            | $_{\rm V}$ R= 47k , C = 100nF                                                | KL_15      | Typ15                   | 0.4               | 2    | 4.5                      | ms     | (     |

| 16   | WAKE Pin                                      |                                                                              |            |                         |                   |      |                          |        |       |

| 16.1 | High-level input voltage                      | 2                                                                            | WAK        | Е "Жакен                | V <sub>S</sub> 1V |      | V <sub>S</sub> +<br>0.3V | V      | A     |

| 16.2 | Low-level input voltage                       | Initializes a wake-up si                                                     | gnal W     | ake <sub>wak</sub> y    | 1                 |      | V <sub>S</sub><br>3.3V   | V      | A     |

| 16.3 | WAKE pull-up current                          | V <sub>S</sub> < 27V<br>V <sub>WAKE</sub> = OV                               | WAKE       | I <sub>WAKE</sub>       | 30                | 10   |                          | μA     | A     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

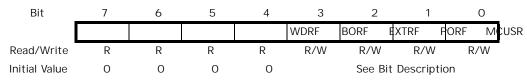

### 6.8.7 MCU Status Register MCUSR

The MCU Status Register provides information which reset source caused an MCU reset.

Bit 7..4: Res: Reserved Bits

These bits are unused bits in the Atm&TA6612/ATA6613, and will always read as zero.

Bit 3 WDRF: Watchdog System Reset Flag

This bit is set if a Watchdog System Reseture: The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

Bit 2 BORF: Brown-out Reset Flag

This bit is set if a Brown-out Reset occursbilthis reset by a Powen-Reset, or by writing a logic zero to the flag.

Bit 1 EXTRF: External Reset Flag

This bit is set if an External Reset occurs. The bit is reset by a Power-on Reset, or by ing a logic zero to the flag.

Bit O PORF: Power-on Reset Flag

This bit is set if a Power-onside occurs. The bit is reset donlywriting a logic zero to the flag.

To make use of the Reset Flags to identify a reset condition, the user should read a then Reset the MCUSR as early as possible in the program. If the register is clear before another reset occurs, the source of the reset can be found by examining the R Flags.

### 6.8.8 Internal Voltage Reference

Atmel ATA6612/ATA6613 features an internal bandgap reference. This reference is used the Brown-out Detection, and it can be used as an input to the Analog Comparator or the ADC

### 6.8.8.1 Voltage Reference Enable Signals and Start-up Time

The voltage reference has a start-up time that may influence the way it should be used. start-up time is given *liable 6-23* on page 74o save power, the reference is not always turned on. The reference is on during the following situations:

- 1. When the BOD is enabled (by programming the BODLEVEL [2..0] Fuses).

- 2. When the bandgap reference is connected to the Analog Comparator (by setting the ACBG bit in ACSR).

- 3. When the ADC is enabled.

Thus, when the BOD is not enabled, after setting the ACBG bit or enabling the ADC, the us must always allow the reference to start up before the output from the Analog Compara ADC is used. To reduce power consumption in Power-down mode, the user can avoid t three conditions above to ensure that the energie is turned off before entering Power-down mode.

When the BOOTRST Fuse is unprogrammed, the Boot section size set to 2Kbytes and the IVSEL bit in the MCUCR Register is set beformey interrupts are enland, the most typical and general program setup for the Reset and Interrupt Vector Addresses hATTAGE12 is:

| Address L      | _abels Code                                      |              | Comments                            |

|----------------|--------------------------------------------------|--------------|-------------------------------------|

| 0x000          | RESET: Idi                                       | r16,high(RAN | /END); Main program start           |

| 0x001          | out                                              | SPH,r16      | ; Set Stack Pointer to top of RAM   |

| 0x002          | ldi                                              | r16,Iow(RAN  | /IEND)                              |

| 0x003<br>0x004 | out<br>sei                                       | SPL,r16      | ; Enable interrupts                 |

| 0x005          | <inst< th=""><th>r&gt; xxx</th><th></th></inst<> | r> xxx       |                                     |

| ;              |                                                  |              |                                     |

| .org 0xC0      | 1                                                |              |                                     |

| OxCO1          | rjmp                                             | EXT_INTO     | ; IRQO Handler                      |

| 0xC02          | rjmp                                             | EXT_INT1     | ; IRQ1 Handler                      |

|                |                                                  |              | ;                                   |

| OxC19          | rjmp                                             | SPM_RDY      | ; Store Program Memory Ready Handle |

OxC19 rjmp SPM\_RDY ; Store Program Memory Ready Handler When the BOOTRST Fuse is programmed and the Boot section size set to 2Kbytes, the mo typical and general program setup for the Reset and Interrupt Vector Addresses in At ATA6612 is:

| Address Labe | s Code          |             | Comments                             |

|--------------|-----------------|-------------|--------------------------------------|

| 0x001        | rjmp            | EXT_INTO    | : IRQO Handler                       |

|              | 5 1             |             | ,                                    |

| 0x002        | rjmp            | EXT_INT1    | ; IRQ1 Handler                       |

|              |                 |             | •                                    |

| 0x019        | rjmp            | SPM_RDY     | ; Store Program Memory Ready Handler |

| ;            |                 |             |                                      |

| .org 0xC00   |                 |             |                                      |

| OxCOO RES    | ET: ldi r       | 16,high(RAI | MEND); Main program start            |

| OxCO1        | out             | SPH,r16     | ; Set Stack Pointer to top of RAM    |

| OxCO2        | ldi             | r16,low(RA  | MEND)                                |

| 0xCO3        | out             | SPL,r16     |                                      |

| 0xCO4        | sei             |             | ; Enable interrupts                  |

| 0xC05        | <instr></instr> | > xxx       |                                      |

When the BOOTRST Fuse is programmed, the Boot section size set to 2Kbytes and the IVSEL bit in the MCUCR Register is set beformey interrupts are enladed, the most typical and general program setup for the Reset and Interrupt Vector Addresses hATTAGE12 is:

| Address Labels Code                                   | 9                 | Comments                             |

|-------------------------------------------------------|-------------------|--------------------------------------|

| ;                                                     |                   |                                      |

| .org 0xC00                                            |                   |                                      |

| 0xC00 rjr                                             | mp RESET          | ; Reset handler                      |

| OxCO1 rjr                                             | mp EXT_INTO       | ; IRQO Handler                       |

| OxCO2 rjr                                             | mp EXT_INT1       | ; IRQ1 Handler                       |

|                                                       | ;                 |                                      |

| OxC19 rjr                                             | mp SPM_RDY        | ; Store Program Memory Ready Handler |

| •                                                     |                   |                                      |

| OxC1A RESET: Idi                                      | r16,high(RAMEND); | Main program start                   |

| OxC1B ou                                              | it SPH,r16        | ; Set Stack Pointer to top of RAM    |

| OxC1C Idi                                             | r16,Iow(RAMEND)   |                                      |

| OxC1D ou                                              | it SPL,r16        |                                      |

| OxC1E se                                              | i                 | ; Enable interrupts                  |

| OxC1F <ir< td=""><td>nstr&gt; xxx</td><td></td></ir<> | nstr> xxx         |                                      |

6.9.2 Interrupt Vectors in ATA6613

Table 6-28. Reset and Interrupt Vectors in ATA6613

| Vector No. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                 |  |

|------------|-----------------------------------|--------------|----------------------------------------------------------------------|--|

| 1          | 0x000 <mark>0</mark> )            | RESET        | External Pin, Power-on Reset, Brown-out Reset and Watchdog System Re |  |

| 2          | 0x0002                            | INTO         | External Interrupt Request O                                         |  |

| 3          | 0x0004                            | INT1         | External Interrupt Request 1                                         |  |

| 4          | 0x0006                            | PCINTO       | Pin Change Interrupt Request O                                       |  |

| 5          | 0x0008                            | PCINT1       | Pin Change Interrupt Request 1                                       |  |

| 6          | OxOOOA                            | PCINT2       | Pin Change Interrupt Request 2                                       |  |

| 7          | 0x000C                            | WDT          | Watchdog Time-out Interrupt                                          |  |

| 8          | OxOOOE                            | TIMER2 COMPA | Timer/Counter2 Compare Match A                                       |  |

| 9          | 0x0010                            | TIMER2 COMPB | Timer/Counter2 Compare Match B                                       |  |

| 10         | 0x0012                            | TIMER2 OVF   | Timer/Counter2 Overflow                                              |  |

| 11         | 0x0014                            | TIMER1 CAPT  | Timer/Counter1 Capture Event                                         |  |

| 12         | 0x0016                            | TIMER1 COMPA | Time/Counter1 Compare Match A                                        |  |

| 13         | 0x0018                            | TIMER1 COMPB | Timer/Coutner1 Compare Match B                                       |  |

| 14         | OxOO1A                            | TIMER1 OVF   | Timer/Counter1 Overflow                                              |  |

| 15         | 0x001C                            | TIMERO COMPA | Timer/CounterO Compare Match A                                       |  |

| 16         | OxOO1E                            | TIMERO COMPB | Timer/CounterO Compare Match B                                       |  |

| 17         | 0x0020                            | TIMERO OVF   | Timer/Counter0 Overflow                                              |  |

| 18         | 0x0022                            | SPI, STC     | SPI Serial Transfer Complete                                         |  |

| 19         | 0x0024                            | USART, RX    | USART Rx Complete                                                    |  |

| 20         | 0x0026                            | USART, UDRE  | USART, Data Register Empty                                           |  |

When the BOOTRST Fuse is unprogrammed, theoBt section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set beformey interrupts are enladd, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATA6613 is:

| Address Labels Code                                     |                  | Comments                             |

|---------------------------------------------------------|------------------|--------------------------------------|

| OxOOOO RESET: Idi                                       | r16,high(RAMEND) | ); Main program start                |

| 0x0001 out                                              | SPH,r16          | ; Set Stack Pointer to top of RAM    |

| 0x0002 Idi                                              | r16,low(RAMEND   | )                                    |

| 0x0003 out                                              | SPL,r16          |                                      |

| 0x0004 sei                                              |                  | ; Enable interrupts                  |

| 0x0005 <ins< td=""><td>str&gt; xxx</td><td></td></ins<> | str> xxx         |                                      |

| ;                                                       |                  |                                      |

| .org 0xC02                                              |                  |                                      |

| 0x1C02 jmp                                              | EXT_INTO         | ; IRQO Handler                       |

| Ox1CO4 jmp                                              | EXT_INT1         | ; IRQ1 Handler                       |

|                                                         | . ;              |                                      |

| Ox1C32 jmp                                              | SPM_RDY          | ; Store Program Memory Ready Handler |

When the BOOTRST Fuse is programmed and the Boot section size set to 2K bytes, the motypical and general program setup for the Reset and Interrupt Vector Addresses in ATA66 is:

| Address La<br>.org 0x0002 |                                                  | Con            | nments                               |

|---------------------------|--------------------------------------------------|----------------|--------------------------------------|

| 8                         |                                                  |                |                                      |

| 0x0002                    | jmp                                              | EXT_INTO       | ; IRQO Handler                       |

| 0x0004                    | jmp                                              | EXT_INT1       | ; IRQ1 Handler                       |

|                           |                                                  | ;              |                                      |

| 0x0032                    | jmp                                              | SPM_RDY        | ; Store Program Memory Ready Handler |

| ;                         |                                                  |                |                                      |

| .org 0x1C00               | C                                                |                |                                      |

| Ox1COO F                  | RESET: Idi                                       | r16,high(RAMEN | D); Main program start               |

| Ox1CO1                    | out                                              | SPH,r16        | ; Set Stack Pointer to top of RAM    |

| 0x1C02                    | ldi                                              | r16,Iow(RAMEN  | ID)                                  |

| Ox1CO3                    | out                                              | SPL,r16        |                                      |

| Ox1CO4                    | sei                                              |                | ; Enable interrupts                  |

| 0x1C05                    | <inst< td=""><td>r&gt; xxx</td><td></td></inst<> | r> xxx         |                                      |

The following code example shows how to set port B pins O and 1 high, 2 and 3 low, define the port pins from 4 to 7 as input with pull-ups assigned to port pins 6 and 7. The ing pin values are read back again, but asympusly discussed, a nop instruction is included to be able to read back the value recently assigned to some of the pins.

| Assembly Code Examplé <sup>1)</sup>                                                              |

|--------------------------------------------------------------------------------------------------|

|                                                                                                  |

| ; Define pull-ups and set outputs high                                                           |

| ; Define directions for port pins                                                                |

| ldi r16,(1< <pb7) (1<<pb6) (1<<pb1) (1<<pb0)< td=""></pb7) (1<<pb6) (1<<pb1) (1<<pb0)<>          |

| ldi r17,(1< <ddb3) (1<<ddb2) (1<<ddb1) (1<<ddb0)< td=""></ddb3) (1<<ddb2) (1<<ddb1) (1<<ddb0)<>  |

| out PORTB,r16                                                                                    |

| out DDRB,r17                                                                                     |

| ; Insert nop for synchronization                                                                 |

| nop                                                                                              |

| ; Read port pins                                                                                 |

| in r16,PINB                                                                                      |

|                                                                                                  |

| C Code Example                                                                                   |

| unsigned char i;                                                                                 |

|                                                                                                  |

| /* Define pull-ups and set outputs high */                                                       |

| /* Define directions for port pins */                                                            |

| PORTB = (1< <pb7) (1<<pb6) (1<<pb1) (1<<pb0);< td=""></pb7) (1<<pb6) (1<<pb1) (1<<pb0);<>        |

| DDRB = (1< <ddb3) (1<<ddb2) (1<<ddb1) (1<<ddb0);< td=""></ddb3) (1<<ddb2) (1<<ddb1) (1<<ddb0);<> |

| /* Insert nop for synchronization */                                                             |

| no_operation();                                                                                  |

| /* Read port pins */                                                                             |

| i = PINB;                                                                                        |

|                                                                                                  |

Note: 1. For the assembly program, two temporary registers are used to minimize the time from pull-ups are set on pins 0, 1, 6, and 7, until the direction bits are correctly set, defining I and 3 as low and redefining bits 0 and 1 as strong high drivers.

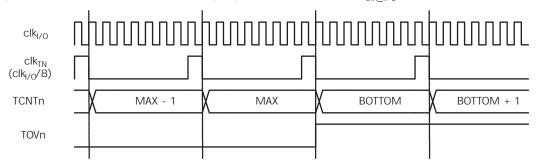

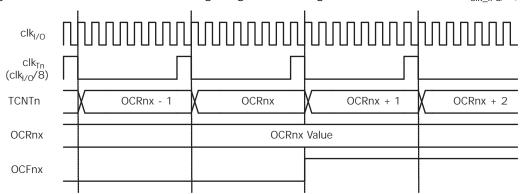

Figure 6-61 shows the same timing data, but with the prescaler enabled.

Figure 6-61. Timer/Counter Timing Digram, with  $Prescaler_{clk}(f_{1/d}/8)$

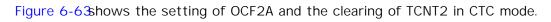

Figure 6-62 shows the setting of OCF2A in all modes except CTC mode.

Figure 6-62. Timer/Counter Timing Diagram, Setting of OCF2A, with Prescaler/(18)

Figure 6-63. Timer/Counter Timing Diagram, Clear Timer on Compare Match mode, with Prescaler ( $f_{ik_{\perp}i/0}$ /8)

## 6.22 debugWIRE On-chip Debug System

#### 6.22.1 Features

- Complete Program Flow Control

- Emulates All On-chip Functions, Both Digital and Analog, except RESET Pin

- Real-time Operation

- Symbolic Debugging Support (Both at C and Assembler Source Level, or for Other HLLs)

- Unlimited Number of Program Break Points (Using Software Break Points)

- Non-intrusive Operation

- Electrical Characteristics Identical to Real Device

- Automatic Configuration System

- High-Speed Operation

- Programming of Non-volatile Memories

#### 6.22.2 Overview

The debugWIRE On-chip debug system uses a One-wire, bi-directional interface to control the program flow, execute AVR<sup>®</sup> instructions in the CPU and to program the different non-volatile memories.

#### 6.22.3 Physical Interface

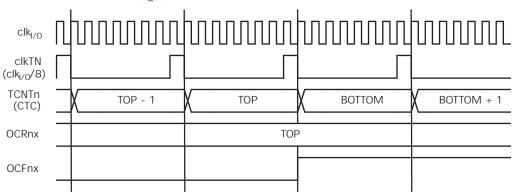

When the debugWIRE Enable (DWEN) Fuse is programmed and Lock bits are unprogrammed, the debugWIRE system within the target device is activated. The RESET port pin is configured as a wire-AND (open-drain) bi-directional I/O pin with pull-up enabled and becomes the communication gateway between target and emulator.

#### Figure 6-113. The debugWIRE Setup

Figure 6-113 shows the schematic of a target MCU, with debugWIRE enabled, and the emulator connector. The system clock is not affected by debugWIRE and will always be the clock source selected by the CKSEL Fuses.

# 282 Atmel ATA6612/ATA6613

If the user has a fixed voltage source connected to the AREF pin, the user may not use other reference voltage options in the application they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch betweennot V 1.1V as reference selection. The first ADC common result after switching reference voltage source may be inaccurate, and the user is advised to discard this result.

#### 6.21.5 ADC Noise Canceler

The ADC features a noise canceler theatables conversion during sleep mode to reduce noise induced from the CPU core and otherple Opherals. The noise canceler can be used with ADC Noise Reduction and Idle mode. To make of this feature, the following procedure should be used:

- a. Make sure that the ADC is enabled anothost busy converting. Single Conversion mode must be selected and the ADC conversion complete interrupt must be enabled.

- b. Enter ADC Noise Reduction mode (orledmode). The ADC will start a conversion once the CPU has been halted.

- c. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and exectite ADC Conversion Complete interrupt routine. If another interrupt wakes up the CPU before the ADC conversion is complete, that interrupt will be executed, an ADC Conversion Complete interrupt request will be generated when the ADD version completes. The CPU will remain in active mode until a new sleep command is executed.

Note that the ADC will not be automatically ed off when entering other sleep modes than Idle mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN befor entering such sleep modes to add excessive power consumption.

### 6.21.5.1 Analog Input Circuitry

The analog input circuit for single ended channels is illustrated fingure 6-107 on page 273 An analog source applied to ADCn is subjected to the pin capacitance and input leakage that pin, regardless of whether that channel is selected as input for the ADC. When the c nel is selected, the source must drive **She** capacitor through the series resistance (combined resistance in the input path).

The ADC is optimized for analog signals with an output impedance of approximately r10 k less. If such a source is used, the sampling e will be negligible. If a source with higher impedance is used, the sampling time wide pend on how long time the source needs to charge the S/H capacitor, with can vary widely. The user is recommended to only use impedant sources with slowly varying signates with similarity the required charge transfer to the S/H capacitor.

Signal components higher than the Nyquist frequency/(2) should not be present for either kind of channels, to avoid distortion from unpabdectignal convolution. The user is advised to remove high frequency components withwaplass filter before applying the signals as inputs to the ADC.

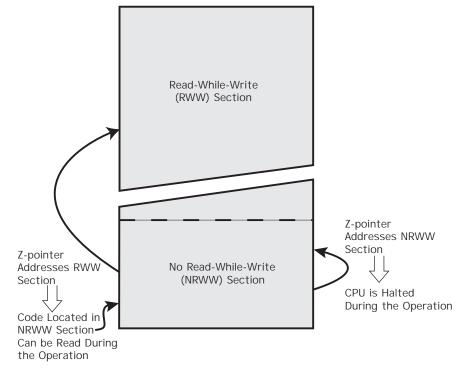

Figure 6-114.Read-While-Write versus No Read-While-Write