Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 72MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 51                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 10K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 8x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

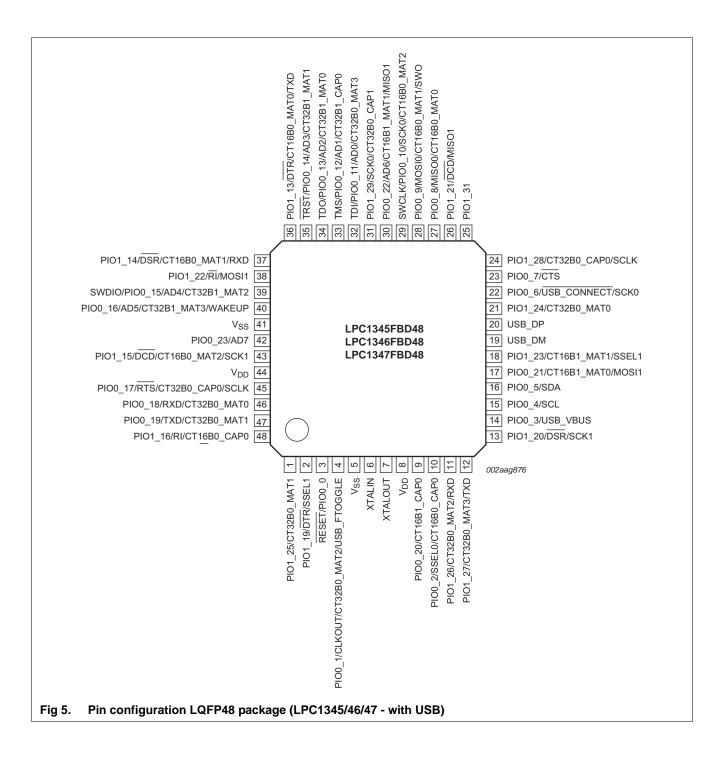

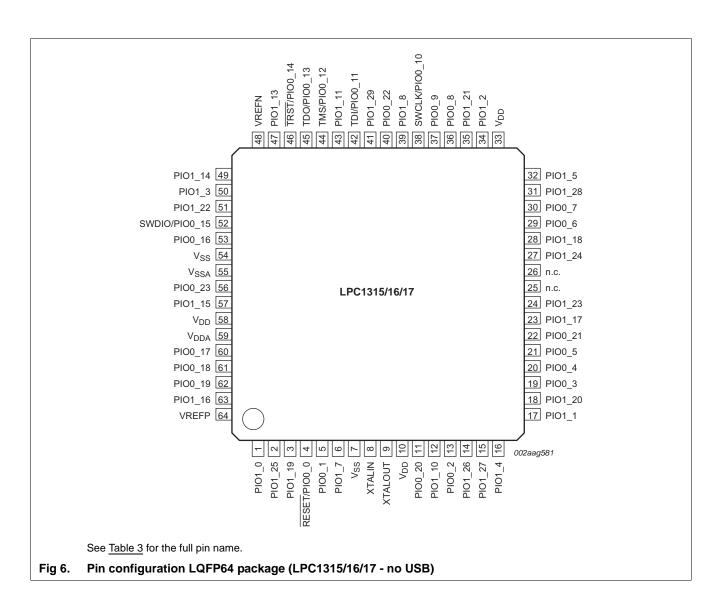

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1317fbd64-551 |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 32-bit ARM Cortex-M3 microcontroller

- Debug options:

- Standard JTAG test interface for BSDL.

- Serial Wire Debug.

- Support for ETM ARM Cortex-M3 debug time stamping.

- Digital peripherals:

- ◆ Up to 51 General Purpose I/O (GPIO) pins with configurable pull-up/pull-down resistors, repeater mode, input inverter, and pseudo open-drain mode. Eight pins support programmable glitch filter.

- Up to 8 GPIO pins can be selected as edge and level sensitive interrupt sources.

- Two GPIO grouped interrupt modules enable an interrupt based on a programmable pattern of input states of a group of GPIO pins.

- High-current source output driver (20 mA) on one pin (P0\_7).

- ◆ High-current sink driver (20 mA) on true open-drain pins (P0\_4 and P0\_5).

- Four general purpose counter/timers with a total of up to 8 capture inputs and 13 match outputs.

- Programmable Windowed WatchDog Timer (WWDT) with a internal low-power WatchDog Oscillator (WDO).

- Repetitive Interrupt Timer (RI Timer).

- Analog peripherals:

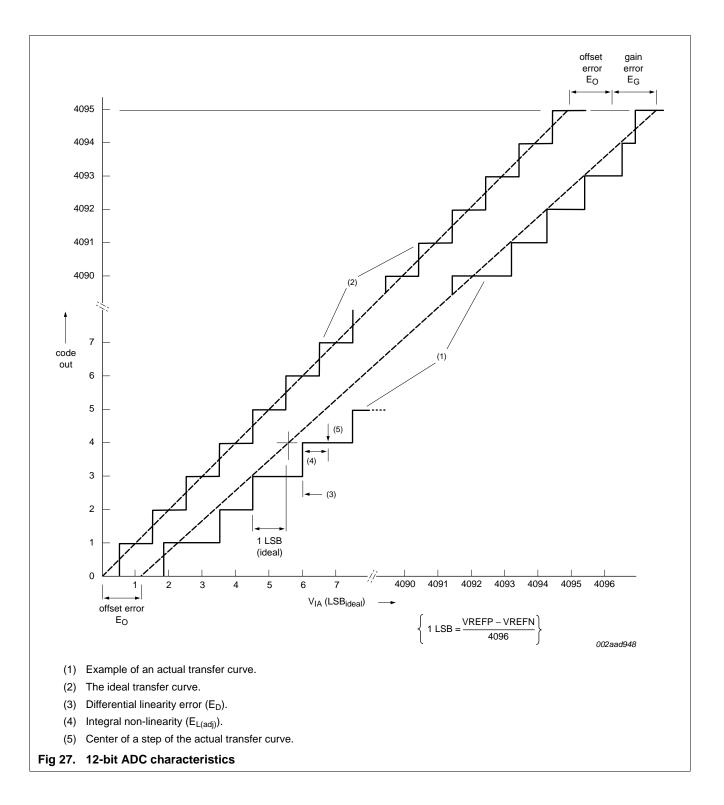

- ◆ 12-bit ADC with eight input channels and sampling rates of up to 500 kSamples/s.

- Serial interfaces:

- USB 2.0 full-speed device controller (LPC1345/46/47) with on-chip ROM-based USB driver library.

- USART with fractional baud rate generation, internal FIFO, a full modem control handshake interface, and support for RS-485/9-bit mode and synchronous mode. USART supports an asynchronous smart card interface (ISO 7816-3).

- Two SSP controllers with FIFO and multi-protocol capabilities.

- ◆ I<sup>2</sup>C-bus interface supporting the full I<sup>2</sup>C-bus specification and Fast-mode Plus with a data rate of up to 1 Mbit/s with multiple address recognition and monitor mode.

- Clock generation:

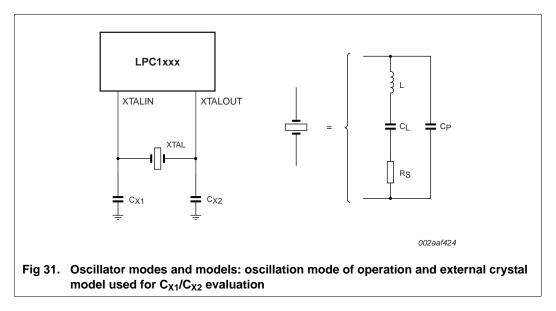

- Crystal Oscillator with an operating range of 1 MHz to 25 MHz (system oscillator) with failure detector.

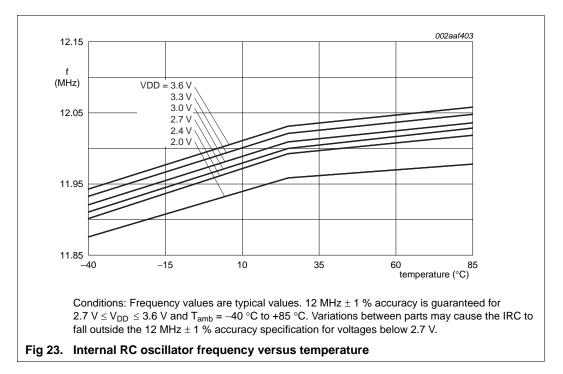

- 12 MHz high-frequency Internal RC oscillator (IRC) trimmed to 1 % accuracy over the entire voltage and temperature range. The IRC can optionally be used as a system clock.

- Internal low-power, low-frequency WatchDog Oscillator (WDO) with programmable frequency output.

- PLL allows CPU operation up to the maximum CPU rate with the system oscillator or the IRC as clock sources.

- ♦ A second, dedicated PLL is provided for USB (LPC1345/46/47).

- Clock output function with divider that can reflect the crystal oscillator, the main clock, the IRC, or the watchdog oscillator.

- Power control:

- ◆ Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

- Power profiles residing in boot ROM allow optimized performance and minimized power consumption for any given application through one simple function call.

#### 32-bit ARM Cortex-M3 microcontroller

### **NXP Semiconductors**

# LPC1315/16/17/45/46/47

32-bit ARM Cortex-M3 microcontroller

### 32-bit ARM Cortex-M3 microcontroller

# 6.2 Pin description

| Symbol                        |        |        |         |            | <u>e[1]</u>                |      | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------|--------|--------|---------|------------|----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | LQFP64 | LQFP48 | HVQFN33 |            | Reset state <sup>[1]</sup> | Type |                                                                                                                                                                                                                                                                                                                                                                                         |

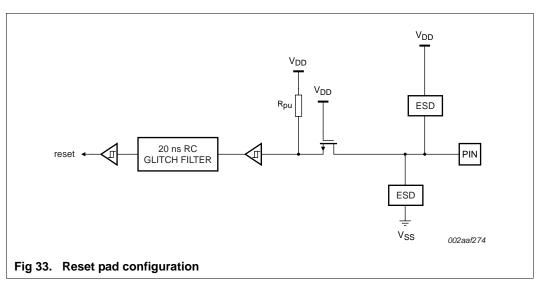

| RESET/PIO0_0                  | 4      | 3      | 2       | [2]        | I; PU                      | I    | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. This pin also serves as the debug select input. LOW level selects the JTAG boundary scan. HIGH level selects the ARM SWD debug mode. |

|                               |        |        |         |            | -                          | I/O  | <b>PIO0_0</b> — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                               |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 5      | 4      | 3       | <u>[3]</u> | I; PU                      | I/O  | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                                                                                                                                                          |

|                               |        |        |         |            | -                          | 0    | CLKOUT — Clockout pin.                                                                                                                                                                                                                                                                                                                                                                  |

|                               |        |        |         |            | -                          | 0    | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                                        |

| PIO0_2/SSEL0/                 | 13     | 10     | 8       | [3]        | I; PU                      | I/O  | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| CT16B0_CAP0                   |        |        |         |            |                            | I/O  | SSEL0 — Slave select for SSP0.                                                                                                                                                                                                                                                                                                                                                          |

|                               |        |        |         |            |                            | I    | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                       |

| PIO0_3                        | 19     | 14     | 9       | [3]        | I; PU                      | I/O  | PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| PIO0_4/SCL                    | 20     | 15     | 10      | [4]        | IA                         | I/O  | <b>PIO0_4</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                                                                                                                                                                  |

|                               |        |        |         |            | -                          | I/O  | <b>SCL</b> — I <sup>2</sup> C-bus clock input/output (open-drain).<br>High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                                                                                                                                                          |

| PIO0_5/SDA                    | 21     | 16     | 11      | [4]        | IA                         | I/O  | <b>PIO0_5</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                                                                                                                                                                  |

|                               |        |        |         |            | -                          | I/O  | <b>SDA</b> — I <sup>2</sup> C-bus data input/output (open-drain).<br>High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                                                                                                                                                           |

| PIO0_6/R/                     | 29     | 22     | 15      | [3]        | I; PU                      | I/O  | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| SCK0                          |        |        |         |            | -                          | -    | R — Reserved.                                                                                                                                                                                                                                                                                                                                                                           |

|                               |        |        |         |            | -                          | I/O  | SCK0 — Serial clock for SSP0.                                                                                                                                                                                                                                                                                                                                                           |

| PIO0_7/CTS                    | 30     | 23     | 16      | [5]        | I; PU                      | I/O  | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                                                                                                                                                                  |

|                               |        |        |         |            | -                          | I    | <b>CTS</b> — Clear To Send input for USART.                                                                                                                                                                                                                                                                                                                                             |

| PIO0_8/MISO0/                 | 36     | 27     | 17      | [3]        | I; PU                      | I/O  | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| CT16B0_MAT0                   |        |        |         |            | -                          | I/O  | MISO0 — Master In Slave Out for SSP0.                                                                                                                                                                                                                                                                                                                                                   |

|                               |        |        |         |            | -                          | 0    | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                        |

| PIO0_9/MOSI0/                 | 37     | 28     | 18      | [3]        | I; PU                      | I/O  | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| CT16B0_MAT1/                  |        |        |         |            | -                          | I/O  | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                                                                                                                                                                                                                                   |

| SWO                           |        |        |         |            | -                          | 0    | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                        |

|                               |        |        |         |            | -                          | 0    | SWO — Serial wire trace output.                                                                                                                                                                                                                                                                                                                                                         |

#### LPC1315\_16\_17\_45\_46\_47

All information provided in this document is subject to legal disclaimers.

### 32-bit ARM Cortex-M3 microcontroller

| PIO0_1/CLKOUT/<br>CT32B0_MAT2/<br>USB_FTOGGLE       5       4       3       II       IV       PIO0_0 - General purpose digital input/output pin.<br>LOW level selects the ARM SWD debug mode.<br>selects the ARM SWD debug mode.         PIO0_1/CLKOUT/<br>CT32B0_MAT2/<br>USB_FTOGGLE       5       4       3       III       IV       PIO0_1 - General purpose digital input/output pin.<br>LOW level selects the ARM SWD debug mode.         PIO0_1/CLKOUT/<br>CT32B0_MAT2/<br>USB_FTOGGLE       5       4       3       III       IV       PIO0_1 - General purpose digital input/output pin.<br>LOW level on this pin during reset starts the ISP<br>command handler or the USB device enumeration.         PIO0_2/SSEL0/<br>CT16B0_CAPO       13       10       8       III       IV       PIO0_2 - General purpose digital input/output pin.<br>LOW level on this pin during reset starts the ISP<br>command handler - USB 1 ms Start-of-Frame signal.         PIO0_2/SSEL0/<br>CT16B0_CAPO       13       10       8       III       IV       PIO0_2 - General purpose digital input/output pin.<br>IVO       SSEL0 - Slave select for SSP0.         PIO0_3/USB_VBUS       19       14       9       III       IV       PIO0_2 - General purpose digital input/output pin.<br>IVO       SSEL0 - Clature input 0 for 16-bit timer 0.         PIO0_4/SCL       20       15       10       II       II       IV       PIO0_4 - General purpose digital input/output pin.<br>(open-drain).       IVO       PIO0_4 - General purpose digital in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Symbol          | LQFP64 | LQFP48 | HVQFN33 |            | Reset state <sup>[1]</sup> | Type | Description                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|--------|---------|------------|----------------------------|------|--------------------------------------------------------------------------------------------------------------------|

| PIO0_1/CLKOUT/<br>CT32B0_MAT2/<br>USB_FTOGGLE         5         4         3         3         1         PIO0_1 — General purpose digital input/output pin. A<br>LOW level on this pin during reset starts the ISP<br>command handler or the USB device enumeration.           USB_FTOGGLE         0         CLKOUT — Clockout pin.         0         CT32B0_MAT2 — Match output 2 for 32-bit timer 0.           PIO0_2/SSEL0/<br>CT16B0_CAPO         13         10         8         2         1         PU //O         PIO0_2 — General purpose digital input/output pin.           PIO0_3/USB_VBUS         19         14         9         2         1         PIO0_1         PIO0_3 — General purpose digital input/output pin.           PIO0_3/USB_VBUS         19         14         9         2         1         PIO0_3         General purpose digital input/output pin.           PIO0_4/SCL         10         14         9         12         1         PIO0_4 — General purpose digital input/output pin.           PIO0_4/SCL         20         15         10         4         10         PIO0_5 — General purpose digital input/output pin (open-drain).           PIO0_5/SDA         21         16         11         4         10         PIO0_5 — General purpose digital input/output pin (open-drain).           PIO0_6/USB_CONNECT/         29         22         15         10 </td <td>RESET/PIO0_0</td> <td>4</td> <td>3</td> <td>2</td> <td>[2]</td> <td>I; PU</td> <td>I</td> <td>address 0. This pin also serves as the debug select input.<br/>LOW level selects the JTAG boundary scan. HIGH level</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RESET/PIO0_0    | 4      | 3      | 2       | [2]        | I; PU                      | I    | address 0. This pin also serves as the debug select input.<br>LOW level selects the JTAG boundary scan. HIGH level |

| $ \begin{array}{c} \mbox{CT32B0_MAT2/} \mbox{USB_FTOGGLE} \\ \mbox{USB_CAPO} \\ \mbox{USD_CAPO} \\ \mbox{USB_CAPO} \\ \mbox{USD_CAPO} \\ \mbox{USB_CAPO} \\ \mbox{USD_CAPO} \\ \mbox{USD_CAPO} \\ \mbox{USD_CAPO} \\ \mbox{USB_CAPO} \\ \mbox{USD_CAPO} \\ \mbox{USD_CAPO} \\ \mbox{USB_CAPO} \\ \mbox{USD_CAPO} \\ \m$                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |        |        |         |            | -                          | I/O  | PIO0_0 — General purpose digital input/output pin.                                                                 |

| PIO0_2/SSEL0/<br>CT16B0_CAP0         13         10         8         Image: Product of the product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CT32B0_MAT2/    |        | 4      | 3       | <u>[3]</u> | I; PU                      | I/O  | LOW level on this pin during reset starts the ISP                                                                  |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |        |        |         |            | -                          | 0    | CLKOUT — Clockout pin.                                                                                             |

| PIO0_2/SSEL0/<br>CT16B0_CAP0         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         8         13         10         14         9         13         11         14         9         13         10         14         9         13         10         14         14         14         14         14         14         14         14         14         14         14         14         14         10         10 <td></td> <td></td> <td></td> <td></td> <td></td> <td>-</td> <td>0</td> <td>CT32B0_MAT2 — Match output 2 for 32-bit timer 0.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        |        |         |            | -                          | 0    | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                   |

| CT16B0_CAP0       //O       SSEL0 — Slave select for SSP0.         I       CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.         PIO0_3/USB_VBUS       19       14       9       12       I; PU       //O       PIO0_3 — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler. A HIGH level during reset starts the USB device enumeration.         PIO0_4/SCL       20       15       10       [4]       IA       //O       PIO0_4 — General purpose digital input/output pin (open-drain).         PIO0_5/SDA       21       16       11       [4]       IA       //O       SCL — I <sup>2</sup> C-bus clock input/output (open-drain).         PIO0_5/SDA       21       16       11       [4]       IA       //O       SDA — I <sup>2</sup> C-bus data input/output (open-drain).         PIO0_6/USB_CONNECT/       29       22       15       [3]       I; PU       //O       PIO0_6 — General purpose digital input/output pin (open-drain).         SCK0       29       22       15       [3]       I; PU       //O       PIO0_6 — General purpose digital input/output pin.         SCK0       29       22       15       [3]       I; PU       //O       PIO0_6 — General purpose digital input/output pin.         SCK0       29       22       15       [1] <td< td=""><td></td><td></td><td></td><td></td><td></td><td>-</td><td>0</td><td>USB_FTOGGLE — USB 1 ms Start-of-Frame signal.</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |        |        |         |            | -                          | 0    | USB_FTOGGLE — USB 1 ms Start-of-Frame signal.                                                                      |

| PIO0_3/USB_VBUS       19       14       9       3       I; PU       I/O       PIO0_3 - General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler. A HIGH level during reset starts the USB device enumeration.         PIO0_4/SCL       20       15       10       4       I       I/O       PIO0_4 - General purpose digital input/output pin (open-drain).         PIO0_4/SCL       20       15       10       4       I       I/O       PIO0_4 - General purpose digital input/output pin (open-drain).         PIO0_5/SDA       21       16       11       14       I/O       PIO0_5 - General purpose digital input/output pin (open-drain).         PIO0_5/SDA       21       16       11       14       I/O       PIO0_5 - General purpose digital input/output pin (open-drain).         PIO0_6/USB_CONNECT/       29       22       15       13       I; PU       I/O       PIO0_6 - General purpose digital input/output pin.         SCK0       21       16       11       14       I       I/O       PIO0_6 - General purpose digital input/output pin.         SCK0       29       22       15       15       I; PU       I/O       PIO0_6 - General purpose digital input/output pin.         SCK0       29       22       15       I; PU       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | 13     | 10     | 8       | [3]        | I; PU                      | I/O  | PIO0_2 — General purpose digital input/output pin.                                                                 |

| $\begin{array}{c} PIO0\_3/USB\_VBUS \\ PIO0\_3/USB\_VBUS \\ PIO0\_3/USB\_VBUS \\ PIO0\_4/SCL \\ PIO0\_6/SCL \\ PIO0\_6$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CT16B0_CAP0     |        |        |         |            |                            | I/O  | SSEL0 — Slave select for SSP0.                                                                                     |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |        |        |         |            |                            | I    | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PIO0_3/USB_VBUS | 19     | 14     | 9       | <u>[3]</u> | I; PU                      | I/O  | LOW level on this pin during reset starts the ISP command handler. A HIGH level during reset starts the            |

| $\frac{1}{100} = \frac{1}{100} + \frac{1}{1000} + \frac{1}{10000} + \frac{1}{10000} + \frac{1}{100000} + \frac{1}{10000000000000000000000000000000000$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |        |        |         |            | -                          | I    | USB_VBUS — Monitors the presence of USB bus power.                                                                 |

| PIO0_5/SDA       21       16       11       [4]       IA       I/O       PIO0_5 — General purpose digital input/output pin (open-drain).         PIO0_5/SDA       21       16       11       [4]       IA       I/O       PIO0_5 — General purpose digital input/output pin (open-drain).         PIO0_6/USB_CONNECT/       29       22       15       [3]       I; PU       I/O       PIO0_6 — General purpose digital input/output pin.         SCK0       29       22       15       [3]       I; PU       I/O       PIO0_6 — General purpose digital input/output pin.         SCK0       29       22       15       [3]       I; PU       I/O       PIO0_6 — General purpose digital input/output pin.         SCK0       29       22       15       [3]       I; PU       I/O       PIO0_6 — General purpose digital input/output pin.         SCK0       29       23       16       [1]       PU       I/O       SCK0 — Serial clock for SSP0.         PIO0_7/CTS       30       23       16       [1]       I; PU       I/O       PIO0_7 — General purpose digital input/output pin (high-current output driver).         I       I       I; PU       I/O       PIO0_8 — General purpose digital input/output pin.         I       I; PU       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PIO0_4/SCL      | 20     | 15     | 10      | [4]        | IA                         | I/O  |                                                                                                                    |

| $\frac{(\text{open-drain}).}{\text{High-current sink only if I}^2 C \text{ Fast-mode Plus is selected the I/O configuration register.}} = \frac{(\text{open-drain}).}{\text{High-current sink only if I}^2 C \text{ Fast-mode Plus is selected the I/O configuration register.}} = \frac{(\text{Open-drain}).}{(\text{Open-drain}).} = \frac{(\text{Open-drain}).}{(\text{Open-drain})} = \frac{(\text{Open-drain}).}{(\text{Open-drain})} = \frac{(\text{Open-drain}).}{(\text{Open-drain})} = \frac{(\text{Open-drain}).}{(\text{High-current sink only if I}^2 C \text{ Fast-mode Plus is selected the I/O configuration register.}} = \frac{(\text{Open-drain}).}{(\text{Open-drain})} = \frac{(\text{Open-drain}).}{(\text{Open-drain})} = \frac{(\text{Open-drain}).}{(\text{High-current sink only if I}^2 C \text{ Fast-mode Plus is selected the I/O configuration register.}} = \frac{(\text{Open-drain}).}{(\text{Open-drain})} = \frac{(\text{Open-drain}).}{(\text{Open-drain})} = \frac{(\text{Open-drain}).}{(\text{High-current sink only if I}^2 C \text{ Fast-mode Plus is selected the I/O configuration register.}} = \frac{(\text{Open-drain}).}{(\text{Open-drain})} = \frac{(\text{Open-drain})}{(\text{Open-drain})} = (\text{Ope$ |                 |        |        |         |            | -                          | I/O  | High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in                                           |

| PIO0_6/USB_CONNECT/       29       22       15       I; PU       I/O       PIO0_6 — General purpose digital input/output pin.         SCK0       29       22       15       I; PU       I/O       PIO0_6 — General purpose digital input/output pin.         SCK0       -       -       O       USB_CONNECT — Signal used to switch an external 1.5 kΩ resistor under software control. Used with the SoftConnect USB feature.         -       I/O       SCK0 — Serial clock for SSP0.         PIO0_7/CTS       30       23       16       I; PU       I/O       PIO0_7 — General purpose digital input/output pin (high-current output driver).         -       I       CTS — Clear To Send input for USART.         PIO0_8/MISO0/       36       27       17       I; PU       I/O       PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PIO0_5/SDA      | 21     | 16     | 11      | [4]        | IA                         | I/O  |                                                                                                                    |

| SCK0       -       O       USB_CONNECT — Signal used to switch an external 1.5 kΩ resistor under software control. Used with the SoftConnect USB feature.         -       I/O       SCK0 — Serial clock for SSP0.         PIO0_7/CTS       30       23       16       I; PU       I/O       PIO0_7 — General purpose digital input/output pin (high-current output driver).         -       I       CTS — Clear To Send input for USART.         PIO0_8/MISO0/       36       27       17       I; PU       I/O       PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |        |        |         |            | -                          | I/O  | High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in                                           |

| -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | 29     | 22     | 15      | [3]        | I; PU                      | I/O  | PIO0_6 — General purpose digital input/output pin.                                                                 |

| PIO0_7/CTS       30       23       16       5       I; PU       I/O       PIO0_7 — General purpose digital input/output pin (high-current output driver).         -       I       CTS — Clear To Send input for USART.         PIO0_8/MISO0/       36       27       17       3       I; PU       I/O       PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SCK0            |        |        |         |            | -                          | 0    |                                                                                                                    |

| (high-current output driver).         -       I         CTS       Clear To Send input for USART.         PIO0_8/MISO0/       36       27       17         I; PU I/O       PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |        |        |         |            | -                          | I/O  | SCK0 — Serial clock for SSP0.                                                                                      |

| PIO0_8/MISO0/ 36 27 17 3 I; PU I/O PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PIO0_7/CTS      | 30     | 23     | 16      | [5]        | I; PU                      | I/O  |                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |        |        |         |            | -                          | I    | CTS — Clear To Send input for USART.                                                                               |

| CT16B0_MAT0 - I/O <b>MISO0</b> — Master In Slave Out for SSP0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PIO0_8/MISO0/   | 36     | 27     | 17      | [3]        | I; PU                      | I/O  | PIO0_8 — General purpose digital input/output pin.                                                                 |