Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 72MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART, USB              |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 40                                                                       |

| Program Memory Size        | 48KB (48K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 10K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 8x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1346fbd48-151 |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **NXP Semiconductors**

## LPC1315/16/17/45/46/47

#### 32-bit ARM Cortex-M3 microcontroller

### 32-bit ARM Cortex-M3 microcontroller

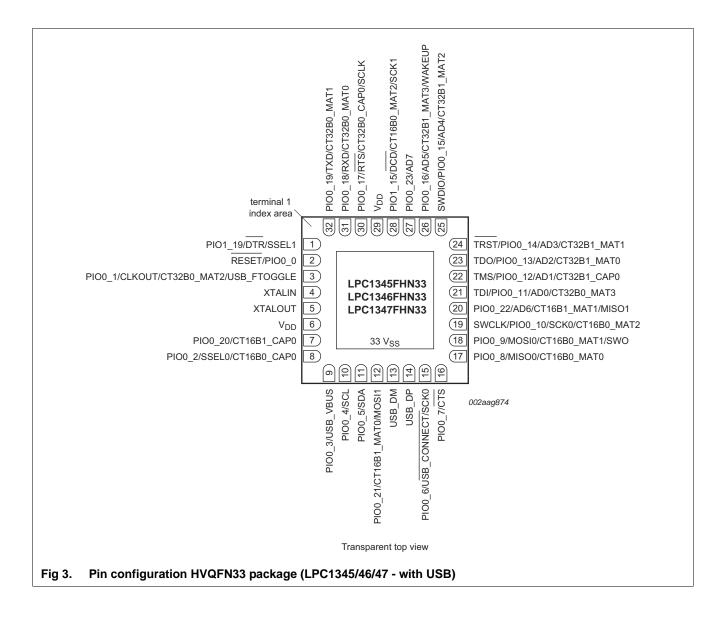

### 6.2 Pin description

| Symbol                        |        |        |         |            | <u>e[1]</u>                |      | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------|--------|--------|---------|------------|----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | LQFP64 | LQFP48 | HVQFN33 |            | Reset state <sup>[1]</sup> | Type |                                                                                                                                                                                                                                                                                                                                                                                         |

| RESET/PIO0_0                  | 4      | 3      | 2       | [2]        | I; PU                      | I    | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. This pin also serves as the debug select input. LOW level selects the JTAG boundary scan. HIGH level selects the ARM SWD debug mode. |

|                               |        |        |         |            | -                          | I/O  | <b>PIO0_0</b> — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                               |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 5      | 4      | 3       | <u>[3]</u> | I; PU                      | I/O  | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                                                                                                                                                          |

|                               |        |        |         |            | -                          | 0    | CLKOUT — Clockout pin.                                                                                                                                                                                                                                                                                                                                                                  |

|                               |        |        |         |            | -                          | 0    | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                                        |

| PIO0_2/SSEL0/                 | 13     | 10     | 8       | [3]        | I; PU                      | I/O  | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| CT16B0_CAP0                   |        |        |         |            |                            | I/O  | SSEL0 — Slave select for SSP0.                                                                                                                                                                                                                                                                                                                                                          |

|                               |        |        |         |            |                            | I    | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                       |

| PIO0_3                        | 19     | 14     | 9       | [3]        | I; PU                      | I/O  | PIO0_3 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

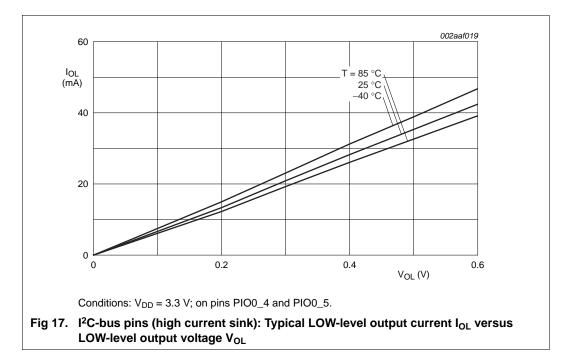

| PIO0_4/SCL                    | 20     | 15     | 10      | [4]        | IA                         | I/O  | <b>PIO0_4</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                                                                                                                                                                  |

|                               |        |        |         |            | -                          | I/O  | <b>SCL</b> — I <sup>2</sup> C-bus clock input/output (open-drain).<br>High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                                                                                                                                                          |

| PIO0_5/SDA                    | 21     | 16     | 11      | [4]        | IA                         | I/O  | <b>PIO0_5</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                                                                                                                                                                  |

|                               |        |        |         |            | -                          | I/O  | <b>SDA</b> — I <sup>2</sup> C-bus data input/output (open-drain).<br>High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                                                                                                                                                           |

| PIO0_6/R/                     | 29     | 22     | 15      | [3]        | I; PU                      | I/O  | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| SCK0                          |        |        |         |            | -                          | -    | R — Reserved.                                                                                                                                                                                                                                                                                                                                                                           |

|                               |        |        |         |            | -                          | I/O  | SCK0 — Serial clock for SSP0.                                                                                                                                                                                                                                                                                                                                                           |

| PIO0_7/CTS                    | 30     | 23     | 16      | [5]        | I; PU                      | I/O  | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                                                                                                                                                                  |

|                               |        |        |         |            | -                          | I    | <b>CTS</b> — Clear To Send input for USART.                                                                                                                                                                                                                                                                                                                                             |

| PIO0_8/MISO0/                 | 36     | 27     | 17      | [3]        | I; PU                      | I/O  | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| CT16B0_MAT0                   |        |        |         |            | -                          | I/O  | MISO0 — Master In Slave Out for SSP0.                                                                                                                                                                                                                                                                                                                                                   |

|                               |        |        |         |            | -                          | 0    | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                        |

| PIO0_9/MOSI0/                 | 37     | 28     | 18      | [3]        | I; PU                      | I/O  | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                      |

| CT16B0_MAT1/                  |        |        |         |            | -                          | I/O  | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                                                                                                                                                                                                                                   |

| SWO                           |        |        |         |            | -                          | 0    | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                                                                                                                                                        |

|                               |        |        |         |            | -                          | 0    | SWO — Serial wire trace output.                                                                                                                                                                                                                                                                                                                                                         |

#### LPC1315\_16\_17\_45\_46\_47

All information provided in this document is subject to legal disclaimers.

#### 32-bit ARM Cortex-M3 microcontroller

| Table 4.         | Fill description (LFV | 51343/   | 40/47 - W |                            | "    |                                                                                                                                                                                                                                                       |

|------------------|-----------------------|----------|-----------|----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | LQFP64                | LQFP48   | HVQFN33   | Reset state <sup>[1]</sup> | Type | Description                                                                                                                                                                                                                                           |

| VREFP            | 64                    | -        | -         | -                          | -    | ADC positive reference voltage: This should be nominally the same voltage as $V_{DDA}$ but should be isolated to minimize noise and error. Level on this pin is used as a reference for ADC. This pin should be tied to 3.3 V if the ADC is not used. |

| V <sub>SSA</sub> | 55                    | -        | -         | -                          | -    | analog ground: 0 V reference. This should nominally be the same voltage as $V_{SS}$ , but should be isolated to minimize noise and error.                                                                                                             |

| V <sub>DD</sub>  | 10<br>33<br>58        | 44       | 6;<br>29  | -                          | -    | Supply voltage to the internal regulator and the external rail. On LQFP48 and HVQFN33 packages, this pin is also connected to the 3.3 V ADC supply and reference voltage.                                                                             |

| $V_{SS}$         | 7;<br>54              | 5;<br>41 | 33        | -                          | -    | Ground.                                                                                                                                                                                                                                               |

#### Table 4. Pin description (LPC1345/46/47 - with USB)

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled; IA = inactive, no pull-up/down enabled; F = floating; floating pins, if not used, should be tied to ground or power to minimize power consumption.

[2] See Figure 33 for the reset pad configuration. RESET functionality is not available in Deep power-down mode. Use the WAKEUP pin to reset the chip and wake up from Deep power-down mode. An external pull-up resistor is required on this pin for the Deep power-down mode.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 32).

- [4] I<sup>2</sup>C-bus pins compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode, I<sup>2</sup>C Fast-mode, and I<sup>2</sup>C Fast-mode Plus.

- [5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see <u>Figure 32</u>); includes high-current output driver.

- [6] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see <u>Figure 32</u>); includes programmable digital input glitch filter.

- [7] WAKEUP pin. 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see <u>Figure 32</u>); includes digital input glitch filter.

- [8] Pad provides USB functions. It is designed in accordance with the USB specification, revision 2.0 (Full-speed and Low-speed mode only). This pad is not 5 V tolerant.

- [9] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.15

32-bit ARM Cortex-M3 microcontroller

• Software interrupt generation.

### 7.6.2 Interrupt sources

Each peripheral device has one interrupt line connected to the NVIC but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

### 7.7 IOCON block

The IOCON block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on-chip peripherals.

Peripherals should be connected to the appropriate pins prior to being activated and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined.

### 7.7.1 Features

- Programmable pull-up, pull-down, or repeater mode.

- All GPIO pins (except PIO0\_4 and PIO0\_5) are pulled up to 3.3 V ( $V_{DD}$  = 3.3 V) if their pull-up resistor is enabled.

- Programmable pseudo open-drain mode.

- Programmable 10-ns glitch filter on pins PIO0\_22, PIO0\_23, and PIO0\_11 to PIO0\_16. The glitch filter is turned off by default.

- Programmable hysteresis.

- Programmable input inverter.

### 7.8 General Purpose Input/Output GPIO

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Multiple outputs can be set or cleared in one write operation.

LPC1315/16/17/45/46/47 use accelerated GPIO functions:

- GPIO registers are a dedicated AHB peripheral so that the fastest possible I/O timing can be achieved.

- Entire port value can be written in one instruction.

Any GPIO pin providing a digital function can be programmed to generate an interrupt on a level, a rising or falling edge, or both.

The GPIO block consists of three parts:

- 1. The GPIO ports.

- 2. The GPIO pin interrupt block to control eight GPIO pins selected as pin interrupts.

- 3. Two GPIO group interrupt blocks to control two combined interrupts from all GPIO pins.

### 32-bit ARM Cortex-M3 microcontroller

receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

### 7.12.1 Features

- The I<sup>2</sup>C-interface is an I<sup>2</sup>C-bus compliant interface with open-drain pins. The I<sup>2</sup>C-bus interface supports Fast-mode Plus with bit rates up to 1 Mbit/s.

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- The I<sup>2</sup>C-bus controller supports multiple address recognition and a bus monitor mode.

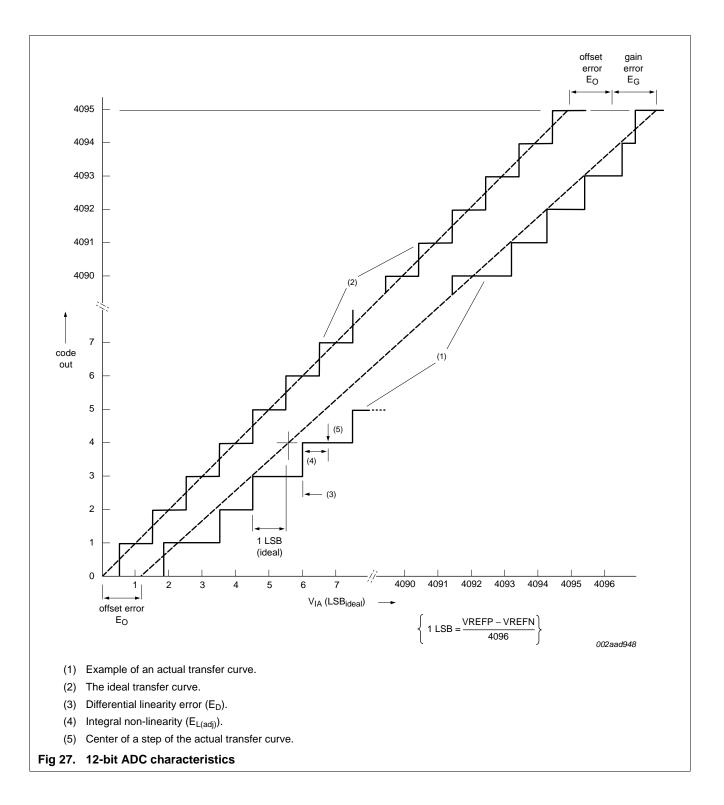

### 7.13 12-bit ADC

The LPC1315/16/17/45/46/47 contains one ADC. It is a single 12-bit successive approximation ADC with eight channels.

### 7.13.1 Features

- 12-bit successive approximation ADC.

- Input multiplexing among 8 pins and three internal sources.

- Low-power mode.

- 10-bit double-conversion rate mode (conversion rate of up to 1 Msample/s).

- Measurement range VREFN to VREFP (typically 3 V; not to exceed VDDA voltage level).

- 12-bit conversion rate of up to 500 kHz.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or timer match signal.

- On the LQFP64 package, power and reference pins (V<sub>DDA</sub>, V<sub>SSA</sub>, VREFP, VREFN) are brought out on separate pins for superior noise immunity.

### 7.14 General purpose external event counter/timers

The LPC1315/16/17/45/46/47 includes two 32-bit counter/timers and two 16-bit counter/timers. The counter/timer is designed to count cycles of the system derived clock. It can optionally generate interrupts or perform other actions at specified timer values, based on four match registers. Each counter/timer also includes one capture input to trap the timer value when an input signal transitions, optionally generating an interrupt.

### 32-bit ARM Cortex-M3 microcontroller

### 7.14.1 Features

- A 32-bit/16-bit timer/counter with a programmable 32-bit/16-bit prescaler.

- Counter or timer operation.

- One capture channel per timer, that can take a snapshot of the timer value when an input signal transitions. A capture event may also generate an interrupt.

- Four match registers per timer that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- The timer and prescaler may be configured to be cleared on a designated capture event. This feature permits easy pulse-width measurement by clearing the timer on the leading edge of an input pulse and capturing the timer value on the trailing edge.

### 7.15 Repetitive Interrupt (RI) timer

The repetitive interrupt timer provides a free-running 48-bit counter which is compared to a selectable value, generating an interrupt when a match occurs. Any bits of the timer/compare can be masked such that they do not contribute to the match detection. The repetitive interrupt timer can be used to create an interrupt that repeats at predetermined intervals.

### 7.15.1 Features

- 48-bit counter running from the main clock. Counter can be free-running or can be reset when an RIT interrupt is generated.

- 48-bit compare value.

- 48-bit compare mask. An interrupt is generated when the counter value equals the compare value, after masking. This allows for combinations not possible with a simple compare.

- Support for ETM timestamp generator.

### 7.16 System tick timer

The ARM Cortex-M3 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a fixed time interval (typically 10 ms).

### 7.17 Windowed WatchDog Timer (WWDT)

The purpose of the watchdog is to reset the controller if software fails to periodically service it within a programmable time window.

### 32-bit ARM Cortex-M3 microcontroller

controlled as needed by changing clock sources, reconfiguring PLL values, and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, a register is provided for shutting down the clocks to individual on-chip peripherals, allowing fine tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Selected peripherals have their own clock divider which provides even better power control.

### 7.18.5.1 Power profiles

The power consumption in Active and Sleep modes can be optimized for the application through simple calls to the power profile. The power configuration routine configures the LPC1315/16/17/45/46/47 for one of the following power modes:

- Default mode corresponding to power configuration after reset.

- · CPU performance mode corresponding to optimized processing capability.

- Efficiency mode corresponding to optimized balance of current consumption and CPU performance.

- Low-current mode corresponding to lowest power consumption.

In addition, the power profile includes routines to select the optimal PLL settings for a given system clock and PLL input clock.

**Remark:** When using the USB, configure the LPC1345/46/47 in Default mode.

#### 7.18.5.2 Sleep mode

When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence but re-enabling the clock to the ARM core.

In Sleep mode, execution of instructions is suspended until either a reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and may generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

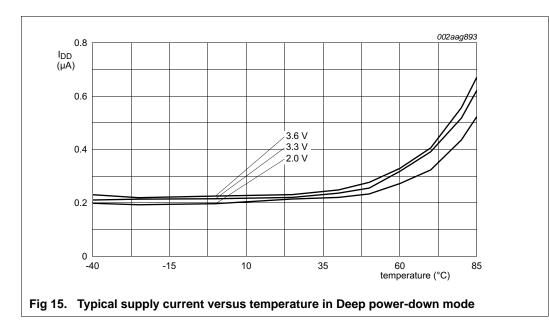

### 7.18.5.3 Deep-sleep mode

In Deep-sleep mode, the LPC1315/16/17/45/46/47 is in Sleep-mode and all peripheral clocks and all clock sources are off with the exception of the IRC. The IRC output is disabled unless the IRC is selected as input to the watchdog timer. In addition all analog blocks are shut down and the flash is in stand-by mode. In Deep-sleep mode, the user has the option to keep the watchdog oscillator and the BOD circuit running for self-timed wake-up and BOD protection.

The LPC1315/16/17/45/46/47 can wake up from Deep-sleep mode via reset, selected GPIO pins, a watchdog timer interrupt, or an interrupt generating USB port activity.

Deep-sleep mode saves power and allows for short wake-up times.

LPC1315\_16\_17\_45\_46\_47

32-bit ARM Cortex-M3 microcontroller

| Symbol           | Parameter                                  | Conditions                                                                                                                                                      |                  | Min          | Typ <u>[1]</u> | Max                | Unit |

|------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|----------------|--------------------|------|

| I <sub>ОН</sub>  | HIGH-level output<br>current               | $2.5 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V};$<br>$\text{V}_{\text{OH}} = \text{V}_{\text{DD}} - 0.4 \text{ V}$                                    |                  | -4           | -              | -                  | mA   |

|                  |                                            | $\begin{array}{l} 2.0 \text{ V} \leq \text{V}_{\text{DD}} < 2.5 \text{ V}; \\ \text{V}_{\text{OH}} = \text{V}_{\text{DD}} - 0.4 \text{ V} \end{array}$          |                  | -3           | -              | -                  | mA   |

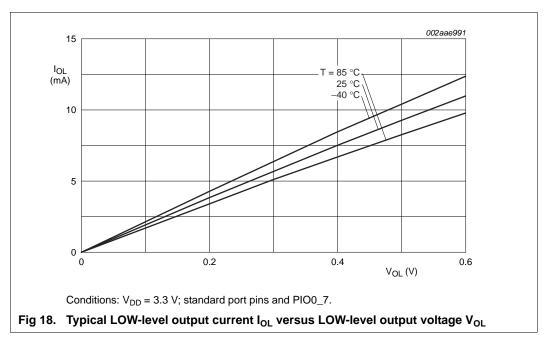

| l <sub>OL</sub>  | LOW-level output                           | $2.5~\text{V} \leq \text{V}_{DD} \leq 3.6~\text{V};~\text{V}_{OL}$ = 0.4 V                                                                                      |                  | 4            | -              | -                  | mA   |

|                  | current                                    | $2.0~\text{V} \leq \text{V}_{DD}~<2.5$ V; $\text{V}_{OL}$ = 0.4 V                                                                                               |                  | 3            | -              | -                  | mA   |

| I <sub>OHS</sub> | HIGH-level short-circuit<br>output current | V <sub>OH</sub> = 0 V                                                                                                                                           | [15]             | -            | -              | -45                | mA   |

| I <sub>OLS</sub> | LOW-level short-circuit output current     | $V_{OL} = V_{DD}$                                                                                                                                               | [15]             | -            | -              | 50                 | mA   |

| I <sub>pd</sub>  | pull-down current                          | V <sub>I</sub> = 5 V                                                                                                                                            |                  | 10           | 50             | 150                | μA   |

| I <sub>pu</sub>  | pull-up current                            | V <sub>I</sub> = 0 V;                                                                                                                                           |                  | -15          | -50            | -85                | μΑ   |

|                  |                                            | $2.0~V < V_{DD} \leq 3.6~V$                                                                                                                                     |                  |              |                |                    |      |

|                  |                                            | $V_{DD} = 2.0 V$                                                                                                                                                |                  | -10          | -50            | -85                | μA   |

|                  |                                            | $V_{DD} < V_I < 5 V$                                                                                                                                            |                  | 0            | 0              | 0                  | μΑ   |

| High-dri         | ve output pin (PIO0_7)                     |                                                                                                                                                                 |                  |              |                |                    |      |

| I <sub>IL</sub>  | LOW-level input current                    | V <sub>I</sub> = 0 V; on-chip pull-up resistor disabled                                                                                                         |                  | -            | 0.5            | 10                 | nA   |

| I <sub>IH</sub>  | HIGH-level input<br>current                | $V_I = V_{DD}$ ; on-chip pull-down resistor disabled                                                                                                            |                  | -            | 0.5            | 10                 | nA   |

| l <sub>oz</sub>  | OFF-state output<br>current                | $V_O = 0 V$ ; $V_O = V_{DD}$ ; on-chip pull-up/down resistors disabled                                                                                          |                  | -            | 0.5            | 10                 | nA   |

| VI               | input voltage                              | pin configured to provide a digital function                                                                                                                    | [12][13]<br>[14] | 0            | -              | 5.0                | V    |

| Vo               | output voltage                             | output active                                                                                                                                                   |                  | 0            | -              | V <sub>DD</sub>    | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                   |                                                                                                                                                                 |                  | $0.7V_{DD}$  | -              | -                  | V    |

| VIL              | LOW-level input voltage                    |                                                                                                                                                                 |                  | -            | -              | 0.3V <sub>DD</sub> | V    |

| V <sub>hys</sub> | hysteresis voltage                         |                                                                                                                                                                 |                  | 0.4          | -              | -                  | V    |

| V <sub>OH</sub>  | HIGH-level output                          | $2.5~\text{V} \leq \text{V}_{DD} \leq 3.6~\text{V};~\text{I}_{OH}$ = -20 mA                                                                                     |                  | $V_{DD}-0.4$ | -              | -                  | V    |

|                  | voltage                                    | $2.0~\text{V} \leq \text{V}_{\text{DD}}$ < 2.5 V; $\text{I}_{\text{OH}}$ = -12 mA                                                                               |                  | $V_{DD}-0.4$ | -              | -                  | V    |

| V <sub>OL</sub>  | LOW-level output                           | $2.5~\text{V} \leq \text{V}_{\text{DD}} \leq 3.6~\text{V};~\text{I}_{\text{OL}}$ = 4 mA                                                                         |                  | -            | -              | 0.4                | V    |

|                  | voltage                                    | $2.0 \text{ V} \leq \text{V}_{\text{DD}}$ < $2.5 \text{ V}$ ; $\text{I}_{\text{OL}}$ = $3 \text{ mA}$                                                           |                  | -            | -              | 0.4                | V    |

| I <sub>OH</sub>  | HIGH-level output<br>current               | $\begin{array}{l} 2.5 \; \text{V} \leq \text{V}_{\text{DD}} \leq 3.6 \; \text{V}; \\ \text{V}_{\text{OH}} = \text{V}_{\text{DD}} - 0.4 \; \text{V} \end{array}$ |                  | 20           | -              | -                  | mA   |

|                  |                                            | $\begin{array}{l} 2.0 \; \text{V} \leq \text{V}_{\text{DD}} < 2.5 \; \text{V}; \\ \text{V}_{\text{OH}} = \text{V}_{\text{DD}} - 0.4 \; \text{V}; \end{array}$   |                  | 12           | -              | -                  | mA   |

| l <sub>OL</sub>  | LOW-level output                           | $2.5~\text{V} \leq \text{V}_{DD} \leq 3.6~\text{V};~\text{V}_{OL}$ = 0.4 V                                                                                      |                  | 4            | -              | -                  | mA   |

|                  | current                                    | $2.0~\text{V} \leq \text{V}_{\text{DD}}$ < 2.5 V; $\text{V}_{\text{OL}}$ = 0.4 V                                                                                |                  | 3            | -              | -                  | mA   |

| I <sub>OLS</sub> | LOW-level short-circuit output current     | $V_{OL} = V_{DD}$                                                                                                                                               | [15]             | -            | -              | 50                 | mA   |

| I <sub>pd</sub>  | pull-down current                          | V <sub>1</sub> = 5 V                                                                                                                                            |                  | 10           | 50             | 150                | μA   |

#### Table 6. Static characteristics ... continued

LPC1315\_16\_17\_45\_46\_47 Product data sheet

#### 32-bit ARM Cortex-M3 microcontroller

- System oscillator enabled; PLL and IRC disabled. [3]

- IRC enabled; system oscillator disabled; system PLL disabled. [4]

- I<sub>DD</sub> measurements were performed with all pins configured as GPIO outputs driven LOW and pull-up resistors disabled. [5]

- [6] BOD disabled.

- [7] All peripherals disabled in the AHBCLKCTRL register. Peripheral clocks to USART, SSP0/1 disabled in the syscon block.

- [8] USB\_DP and USB\_DM pulled LOW externally.

- [9] Low-current mode PWR\_LOW\_CURRENT selected when running the set\_power routine in the power profiles.

- [10] IRC disabled; system oscillator enabled; system PLL enabled.

- [11] WAKEUP pin pulled HIGH externally. An external pull-up resistor is required on the RESET pin for the Deep power-down mode.

- [12] Including voltage on outputs in 3-state mode.

- [13] V<sub>DD</sub> supply voltage must be present.

- [14] 3-state outputs go into 3-state mode in Deep power-down mode.

- [15] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

- [16] To V<sub>SS</sub>.

- [17] Includes external resistors of 33  $\Omega \pm 1$  % on USB\_DP and USB\_DM.

### 9.1 BOD static characteristics

#### BOD static characteristics<sup>[1]</sup> Table 7.

$T_{amb} = 25 \ ^{\circ}C.$

| Symbol          | Parameter         | Conditions        | Min | Тур  | Max | Unit |

|-----------------|-------------------|-------------------|-----|------|-----|------|

| V <sub>th</sub> | threshold voltage | interrupt level 1 |     |      |     |      |

|                 |                   | assertion         | -   | 2.22 | -   | V    |

|                 |                   | de-assertion      | -   | 2.35 | -   | V    |

|                 |                   | interrupt level 2 |     |      |     |      |

|                 |                   | assertion         | -   | 2.52 | -   | V    |

|                 |                   | de-assertion      | -   | 2.66 | -   | V    |

|                 |                   | interrupt level 3 |     |      |     |      |

|                 |                   | assertion         | -   | 2.80 | -   | V    |

|                 |                   | de-assertion      | -   | 2.90 | -   | V    |

|                 |                   | reset level 0     |     |      |     |      |

|                 |                   | assertion         | -   | 1.46 | -   | V    |

|                 |                   | de-assertion      | -   | 1.63 | -   | V    |

|                 |                   | reset level 1     |     |      |     |      |

|                 |                   | assertion         | -   | 2.06 | -   | V    |

|                 |                   | de-assertion      | -   | 2.15 | -   | V    |

|                 |                   | reset level 2     |     |      |     |      |

|                 |                   | assertion         | -   | 2.35 | -   | V    |

|                 |                   | de-assertion      | -   | 2.43 | -   | V    |

|                 |                   | reset level 3     |     |      |     |      |

|                 |                   | assertion         | -   | 2.63 | -   | V    |

|                 |                   | de-assertion      | -   | 2.71 | -   | V    |

[1] Interrupt levels are selected by writing the level value to the BOD control register BODCTRL, see LPC1315/16/17/45/46/47 user manual.

### 32-bit ARM Cortex-M3 microcontroller

#### Table 8. Power consumption for individual analog and digital blocks

The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled in the SYSAHBCLKCTRL or PDRUNCFG (for analog blocks) registers. All other blocks are disabled in both registers and no code is executed. Measured on a typical sample at T<sub>amb</sub> = 25 °C. Unless noted otherwise, the system oscillator and PLL are running in both measurements.

|                                        |       | supply cur<br>or different<br>cies |                 |                     | Notes                                                                                                                                              |

|----------------------------------------|-------|------------------------------------|-----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | n/a   | 12 MHz                             | 48 MHz          | 72 MHz              |                                                                                                                                                    |

| IRC                                    | 0.23  | -                                  | -               | -                   | System oscillator running; PLL off; independent of main clock frequency.                                                                           |

| System oscillator<br>at 12 MHz         | 0.23  | -                                  | -               | -                   | IRC running; PLL off; independent of main clock frequency.                                                                                         |

| Watchdog<br>oscillator at<br>500 kHz/2 | 0.002 | -                                  | -               | -                   | System oscillator running; PLL off; independent of main clock frequency.                                                                           |

| BOD                                    | 0.045 | -                                  | -               | -                   | Independent of main clock frequency.                                                                                                               |

| Main PLL or USB<br>PLL                 | -     | 0.26                               | 0.34            | 0.48                |                                                                                                                                                    |

| ADC                                    | -     | 0.07                               | 0.25            | 0.37                |                                                                                                                                                    |

| CLKOUT                                 | -     | 0.14                               | 0.56            | 0.82                | Main clock divided by 4 in the CLKOUTDIV register.                                                                                                 |

| CT16B0                                 | -     | 0.01                               | 0.05            | 0.08                |                                                                                                                                                    |

| CT16B1                                 | -     | 0.01                               | 0.04            | 0.06                |                                                                                                                                                    |

| CT32B0                                 | -     | 0.01                               | 0.05            | 0.07                |                                                                                                                                                    |

| CT32B1                                 | -     | 0.01                               | 0.04            | 0.06                |                                                                                                                                                    |

| GPIO                                   | -     | 0.21                               | 0.80            | 1.17                | GPIO pins configured as outputs and set to LOW. Direction<br>and pin state are maintained if the GPIO is disabled in the<br>SYSAHBCLKCFG register. |

| IOCON                                  | -     | 0.00                               | 0.02            | 0.02                |                                                                                                                                                    |

| 12C                                    | -     | 0.03                               | 0.12            | 0.17                |                                                                                                                                                    |

| LPC1315_16_17_45_46_47                 |       |                                    | All information | provided in this do | cument is subject to legal disclaimers. © NXP B.V. 2012. All rights reserve                                                                        |

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

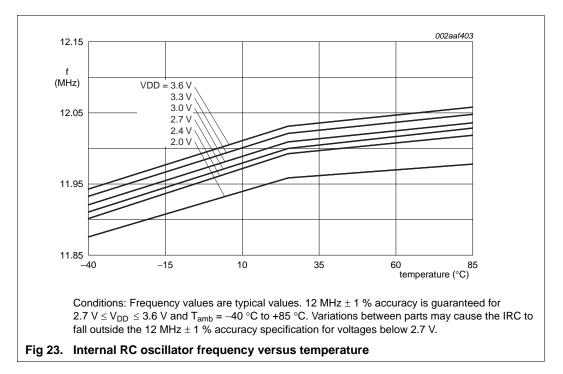

### 10.3 Internal oscillators

#### Table 12. Dynamic characteristics: IRC

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 2.7 \text{ V} \le V_{DD} \le 3.6 \text{ V}_{11}.$

| Symbol               | Parameter                           | Conditions | Min   | Typ <u>[2]</u> | Max   | Unit |

|----------------------|-------------------------------------|------------|-------|----------------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator<br>frequency | -          | 11.88 | 12             | 12.12 | MHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

Table 13. Dynamic characteristics: Watchdog oscillator

| Symbol                | Parameter                        | Conditions                                                  |        | Min | Typ <u>[1]</u> | Max | Unit |

|-----------------------|----------------------------------|-------------------------------------------------------------|--------|-----|----------------|-----|------|

| f <sub>osc(int)</sub> | internal oscillator<br>frequency | DIVSEL = 0x1F, FREQSEL = 0x1<br>in the WDTOSCCTRL register; | [2][3] | -   | 9.4            | -   | kHz  |

|                       |                                  | DIVSEL = 0x00, FREQSEL = 0xF<br>in the WDTOSCCTRL register  | [2][3] | -   | 2300           | -   | kHz  |

[1] Typical ratings are not guaranteed. The values listed are at nominal supply voltages.

[2] The typical frequency spread over processing and temperature ( $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$ ) is ±40 %.

[3] See the LPC1315/16/17/45/46/47 user manual.

### 32-bit ARM Cortex-M3 microcontroller

### 10.6 SSP interface

#### Table 16. Dynamic characteristics: SSP pins in SPI mode

| Symbol                | Parameter              | Conditions                     |            | Min                         | Max                          | Unit |

|-----------------------|------------------------|--------------------------------|------------|-----------------------------|------------------------------|------|

| SSP maste             | er                     |                                |            |                             |                              |      |

| T <sub>cy(clk)</sub>  | clock cycle time       | full-duplex mode               | [1]        | 40                          | -                            | ns   |

|                       |                        | when only transmitting         | <u>[1]</u> | 27.8                        | -                            | ns   |

| t <sub>DS</sub>       | data set-up time       | in SPI mode;                   | [2]        | 15                          | -                            | ns   |

|                       |                        | $2.4~V \leq V_{DD} \leq 3.6~V$ |            |                             |                              |      |

|                       |                        | $2.0~V \leq V_{DD} < 2.4~V$    | [2]        | 20                          | -                            | ns   |

| t <sub>DH</sub>       | data hold time         | in SPI mode                    | [2]        | 0                           | -                            | ns   |

| t <sub>v(Q)</sub>     | data output valid time | in SPI mode                    | [2]        | -                           | 10                           | ns   |

| t <sub>h(Q)</sub>     | data output hold time  | in SPI mode                    | [2]        | 0                           | -                            | ns   |

| SSP slave             |                        |                                |            |                             |                              |      |

| T <sub>cy(PCLK)</sub> | PCLK cycle time        |                                |            | 13.9                        | -                            | ns   |

| t <sub>DS</sub>       | data set-up time       | in SPI mode                    | [3][4]     | 0                           | -                            | ns   |

| t <sub>DH</sub>       | data hold time         | in SPI mode                    | [3][4]     | $3 \times T_{cy(PCLK)}$ + 4 | -                            | ns   |

| t <sub>v(Q)</sub>     | data output valid time | in SPI mode                    | [3][4]     | -                           | $3 \times T_{cy(PCLK)}$ + 11 | ns   |

| t <sub>h(Q)</sub>     | data output hold time  | in SPI mode                    | [3][4]     | -                           | $2 \times T_{cy(PCLK)} + 5$  | ns   |

[1] T<sub>cy(clk)</sub> = (SSPCLKDIV × (1 + SCR) × CPSDVSR) / f<sub>main</sub>. The clock cycle time derived from the SPI bit rate T<sub>cy(clk)</sub> is a function of the main clock frequency f<sub>main</sub>, the SSP peripheral clock divider (SSPCLKDIV), the SSP SCR parameter (specified in the SSP0CR0 register), and the SSP CPSDVSR parameter (specified in the SSP clock prescale register).

[2]  $T_{amb} = -40 \ ^{\circ}C$  to 85  $^{\circ}C$ .

$[3] \quad T_{cy(clk)} = 12 \times T_{cy(PCLK)}.$

$\label{eq:Tamb} \begin{array}{ll} \mbox{[4]} & \mbox{T}_{amb} = 25 \ ^{\circ}\mbox{C}; \ \mbox{V}_{DD} = 3.3 \ \mbox{V}. \end{array}$

### **NXP Semiconductors**

## LPC1315/16/17/45/46/47

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

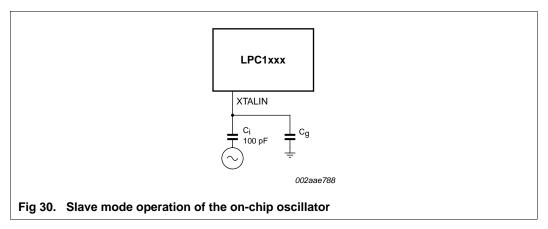

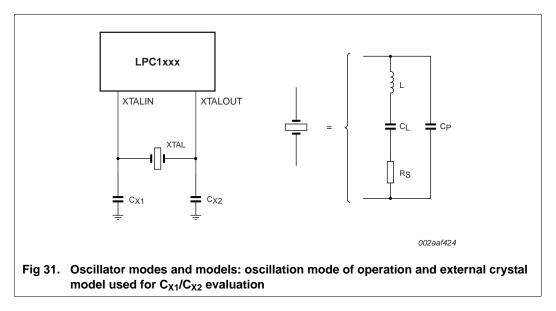

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF (<u>Figure 30</u>), with an amplitude between 200 mV(RMS) and 1000 mV(RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

External components and models used in oscillation mode are shown in Figure 31 and in Table 18 and Table 19. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of fundamental mode oscillation (the fundamental frequency is represented by L,  $C_L$  and  $R_S$ ). Capacitance  $C_P$  in Figure 31 represents the parallel package capacitance and should not be larger than 7 pF. Parameters  $F_{OSC}$ ,  $C_L$ ,  $R_S$  and  $C_P$  are supplied by the crystal manufacturer.

Table 18. Recommended values for  $C_{X1}/C_{X2}$  in oscillation mode (crystal and external components parameters) low frequency mode

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load capacitors C <sub>X1</sub> , C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|

| 1 MHz - 5 MHz                                      | 10 pF                                      | < <b>300</b> Ω                                      | 18 pF, 18 pF                                               |

|                                                    | 20 pF                                      | < 300 Ω                                             | 39 pF, 39 pF                                               |

|                                                    | 30 pF                                      | < 300 Ω                                             | 57 pF, 57 pF                                               |

| All information prov                               | egal disclaimers.                          | © NXP B.V. 2012. All rights reserved.               |                                                            |

32-bit ARM Cortex-M3 microcontroller

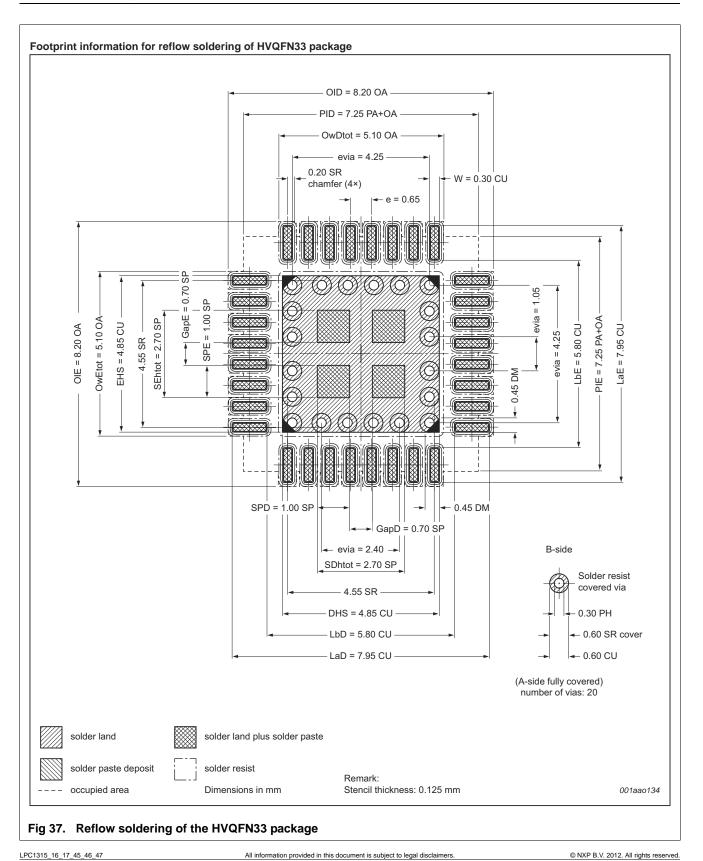

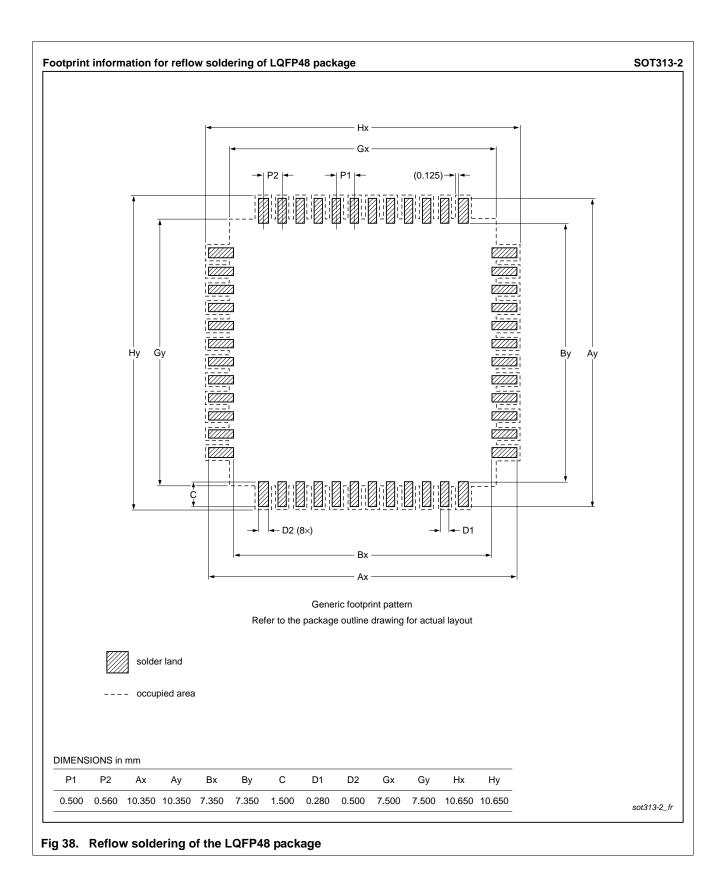

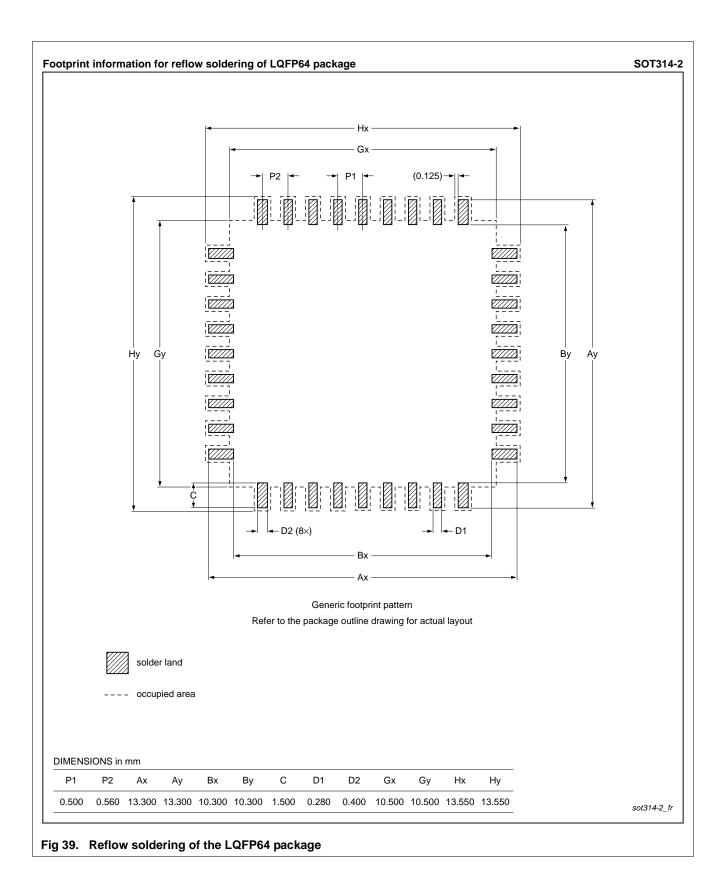

### 14. Soldering

LPC1315\_16\_17\_45\_46\_47 Product data sheet

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

### 15. Abbreviations

| Table 20. | Abbreviations                                           |

|-----------|---------------------------------------------------------|

| Acronym   | Description                                             |

| A/D       | Analog-to-Digital                                       |

| ADC       | Analog-to-Digital Converter                             |

| AHB       | Advanced High-performance Bus                           |

| APB       | Advanced Peripheral Bus                                 |

| BOD       | BrownOut Detection                                      |

| CDC       | Communication Device Class                              |

| ETM       | Embedded Trace Macrocell                                |

| GPIO      | General Purpose Input/Output                            |

| HID       | Human Interface Device                                  |

| JTAG      | Joint Test Action Group                                 |

| MSC       | Mass Storage Class                                      |

| PLL       | Phase-Locked Loop                                       |

| RC        | Resistor-Capacitor                                      |

| SPI       | Serial Peripheral Interface                             |

| SSI       | Serial Synchronous Interface                            |

| SSP       | Synchronous Serial Port                                 |

| TAP       | Test Access Port                                        |

| USART     | Universal Synchronous Asynchronous Receiver/Transmitter |

#### 32-bit ARM Cortex-M3 microcontroller

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b)

### 18. Contact information

whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

### 17.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners. I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com