Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Obsolete                                               |

|--------------------------------------------------------|

| Z16C00                                                 |

| 1 Core, 16-Bit                                         |

| 10MHz                                                  |

| -                                                      |

| -                                                      |

| No                                                     |

| -                                                      |

| -                                                      |

| -                                                      |

| -                                                      |

| 5.0V                                                   |

| 0°C ~ 70°C (TA)                                        |

| -                                                      |

| 40-DIP (0.620", 15.75mm)                               |

| 40-PDIP                                                |

| https://www.e-xfl.com/product-detail/zilog/z16c0110psg |

|                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z16C01/C02

**CPU CENTRAL PROCESSING UNIT**

#### **FEATURES**

|        | Memory    | Memory     | Speed |

|--------|-----------|------------|-------|

| Part   | Address   | Extension  | (MHz) |

| Z16C01 | 8 Mbytes  | 48 Mbytes  | 10    |

| Z16C02 | 64 Kbytes | 384 Kbytes | 10    |

- 40/48-Pin PDIP and 44-Pin PLCC Packages

- $\blacksquare$  +4.5 ≤  $V_{cc}$  ≤ +5.5-Volt Operating Range

- Low-Power CMOS

- 0°C to +70°C Temperature Range

- Extendable Register Files

- Nine Basic Instruction Types

- Eight User-Selectable Addressing Modes

- Seven Data Types

- Supports Three Interrupt Types and Four Traps

- RISC-Like Load/Store Architecture

#### **GENERAL DESCRIPTION**

The Z16C01/C02 CPU are members of the 16-bit processor and controller family. Designed using a RISC-like Load/Store architecture, the CPU can operate in either system or normal modes, permitting privileged operations and improving operating system organization and implementation.

To boost the main CPU's performance capability, the processor core includes hardwired control and is a 16-bit real-time processor functioning at register access speeds. Register flexibility is created by grouping or overlapping multiple registers, and by allowing extended register file capabilities as the system expands. Easy extended register file control is accomplished through a single instruction stream communication.

The CPU supports three types of interrupts (non-maskable, vectored, and non-vectored) and four traps (system call, extended process architecture instruction, privileged instructions, and segmentation trap). The vectored and non-vectored interrupts are maskable.

The processor's resources include seven data types that range from bits to 32-bit long words, and byte and word strings, plus eight user-selectable addressing modes. The nine basic instruction types can be combined with various data types and addressing modes to form a powerful set of 414 instructions.

The extended processing architecture features provide a modular approach to expanding both the hardware and software capabilities of the Z16C01/C02.

#### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B/W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

CPS95SCC0103 (3/95)

### **GENERAL DESCRIPTION** (Continued)

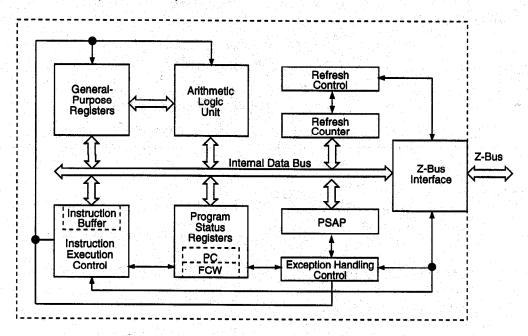

Z16C00 CPU Functional Block Diagram

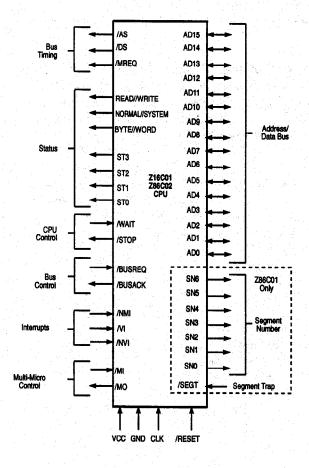

Z16C01/C02 Signal Descriptions

#### PIN DESCRIPTION

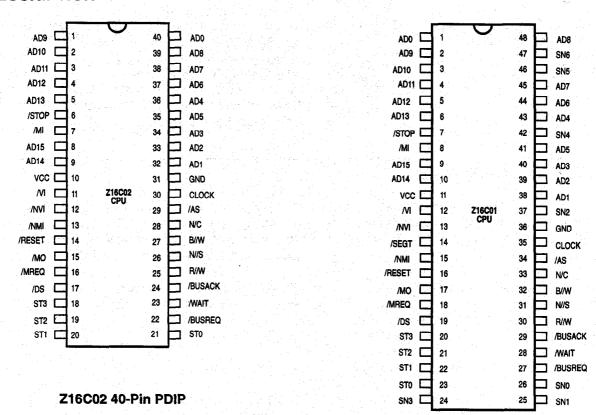

Z16C01 48-Pin PDIP

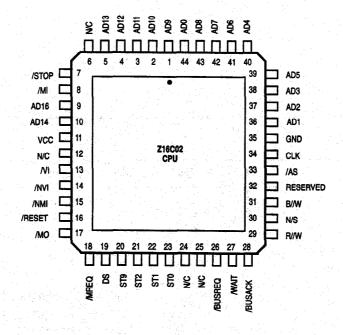

Z16C02 44-Pin PLCC

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltages on V <sub>cc</sub> with respect to V <sub>s</sub> | 0.3V to +7.0V          |

|------------------------------------------------------------|------------------------|

| Voltages on all inputs with respect                        |                        |

| V <sub>SS</sub>                                            | 0.3V to $V_{cc}$ +0.3V |

| Storage Temperature                                        |                        |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operating of the device at any condition above these indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### STANDARD TEST CONDITIONS

The DC characteristics below apply for the following test conditions, unless otherwise noted. All voltages are referenced to GND (0V). Positive current flows into the referenced pin.

Available operating temperature ranges are:

- S = 0°C to +70°C, + 4.5 $V \le V_{CC} \le$  + 5.5V (Z16C01, Z16C02)

- E = -40°C to +100°C, + 4.5V ≤  $V_{cc}$  ≤ + 5.5V (Z16C01, Z16C02)

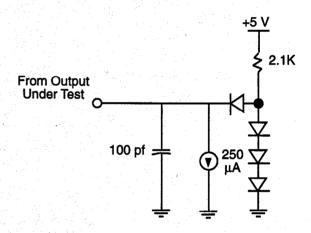

All AC parameters assume a total load capacitance (including parasitic capacitances) or 100 pf max, except for parameter 6 (50 pf max). Timing reference between two output signals assume a load difference of 50 pf max.

The Ordering Information section lists package temperature ranges and product numbers.

**Test Load Diagram**

#### DC CHARACTERISTICS

| Sym                 | Parameter                            | MIN                  | MAX                  | Units | Condition                          |  |

|---------------------|--------------------------------------|----------------------|----------------------|-------|------------------------------------|--|

| V <sub>CH</sub>     | Clock Input High Voltage             | V <sub>cc</sub> -0.4 | V <sub>cc</sub> +0.3 | ٧     | Driven by External Clock Generator |  |

| V <sub>CL</sub>     | Clock input Low Voltage              | ~-0.3                | ິັ0.45               | ٧     | Driven by External Clock Generator |  |

| V <sub>IH</sub>     | Input High Voltage                   | 2.0                  | V <sub>cc</sub> +0.3 | ٧     |                                    |  |

| V,,, RESET          | Input High Voltage on /RESET Pin     | 2.4                  | V <sub>cc</sub> +0.3 | ν     |                                    |  |

| V <sub>IH</sub> NMI | Input High Voltage on NMI Pin        | 2.4                  | V <sub>cc</sub> +0.3 | ٧     |                                    |  |

| <b>/</b> ,          | Input Low Voltage                    | -0.3                 | ິ 0.8                | ٧     |                                    |  |

| , oH                | Output High Voltage                  | 2.4                  |                      | V     | $I_{0H} = -250uA$                  |  |

| OL OL               | Output Low Voltage                   |                      | 0.4                  | V     | $I_{01} = +2.0$ mA                 |  |

| UL                  | Input Leakage                        |                      | ±10                  | μA    | 0.4V ≤ VIN ≤ +2.4V                 |  |

| SEGT                | Input Leakage on /SEGT Pin           | -100                 | 100                  | μΑ    |                                    |  |

| OL .                | Output Leakage                       |                      | ±10                  | μA    | 0.4V ≤ VIN ≤ +2.4V                 |  |

| CC                  | V <sub>cc</sub> Power Supply Current |                      | 35                   | mΑ    | 10MHz                              |  |

### **FOOTNOTES TO AC CHARACTERISTICS**

| No.                              | Symbol                                                  | Z16C01/2<br>10 MHz<br>Equation                                                      |  |

|----------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| 11<br>13<br>16<br>17<br>19       | TdA(DR)<br>TdDS(A)<br>TdDW(DS)<br>TdA(MR)<br>TwMRh      | 2TcC+TwCh-60ns<br>TwCl+5ns<br>TcC+TwCh-30ns<br>TwCh-20ns<br>TcC-20ns                |  |

| 20<br>21<br>22<br>25<br>27       | TdMR(A)<br>TdDW(DSW)<br>TdMR(DR)<br>TdA(AS)<br>TdAS(DR) | TwCl-20ns TwCh-25ns 2TcC-60ns TwCh-20ns 2TcC-60ns                                   |  |

| 28<br>29<br>30<br>32<br>33       | TdDS(AS)<br>TwAS<br>TdAS(A)<br>TdAS(DSR)<br>TdDSR(DR)   | TwCI-20ns TwCh-5ns TwCI-10ns TwCI-5ns TcC+TwCh-60ns                                 |  |

| 35<br>36<br>38<br>40<br>41       | TdDS(DW) TdA(DSR) TwDSR TwDSW TdDSI(DR)                 | TwCI-15ns TcC-35ns TcC+TwCh-30ns TcC-25ns 2TcC-80ns                                 |  |

| 43<br>44<br>46<br>48<br>68<br>69 | TwDS TdAS(DSA) TdDSA(DR) TdS(AS) TwA TdDS(s)            | 2TcC-40ns<br>4TcC+TwCl-30ns<br>2TcC+TwCh-75ns<br>TwCh-20ns<br>TcC-50ns<br>TwCl-10ns |  |

AC Timing Test Conditions:

$\begin{aligned} & V_{\text{OL}} = 0.8V \\ & V_{\text{OH}} = 2.0V \\ & V_{\text{IL}} = 0.8V \\ & V_{\text{IH}} = 2.4V \\ & V_{\text{ILC}} = 0.45V \\ & V_{\text{IHC}} = V_{\text{cc}} - 0.4V \end{aligned}$

### **AC CHARACTERISTICS**

|         |           |                                              | Z16C01<br>10 MH |                          |

|---------|-----------|----------------------------------------------|-----------------|--------------------------|

| No.     | Symbol    | Parameter                                    | Min             | Max                      |

| 1       | TcC       | Clock Cycle Time                             | 100             |                          |

| 2       | TwCh      | Clock Width (High)                           | 40              |                          |

| 3       | TwCl      | Clock Width (Low)                            | 40              |                          |

| 4       | TfC       | Clock Fall Time                              |                 | 10                       |

| 5       | TrC       | Clock Rise Time                              |                 |                          |

| 6       | TdC(SNv)  | Clock+ Segment Number Valid (50pf load)      |                 |                          |

| 7       | TdC(SNn)  | Clock +Segment Number Not Valid              | 0               |                          |

| 8       | TdC(Bz)   | Clock + Bus Float                            |                 | 50                       |

| 9       | TdC(A)    | Clock +Address Valid                         |                 | 50                       |

|         |           |                                              |                 |                          |

| 10      | TdC(Az)   | Clock + Address Float                        |                 | 50                       |

| 11      | TdA(DR)   | Address Valid to Read Data Required Valid    |                 | 180*                     |

| 12      | TsDR(C)   | Read Data to Clock Fall Setup Time           | 20              |                          |

| 13      | TdDS(A)   | /DS+Address Active                           | 45*             |                          |

| 14      | TdC(DW)   | Clock + Write Data Valid                     |                 | . <b>60</b>              |

| 15      | ThDR(DS)  | Read Data to /DS Rise Hold Time              | 0               |                          |

| 16      | TdDW(DS)  | Write Data Valid to /DS Rise Delay           | 110*            |                          |

| 17      | TdA(MR)   | Address Valid to /MREQ Fall Delay            | 20*             |                          |

| 18      | TdC(MR)   | Clock Fall to /MREQ Fall Delay               |                 | 50                       |

| 19      | TwMRh     | /MREQ Width (High)                           | 80*             |                          |

| 20      | TdMR(A)   | /MPEO E Address Not Active                   | 20*             |                          |

| 21      |           | /MREQ [ Address Not Active                   | 20*             |                          |

| 22      | TdDW(DSW) | Write Data Valid to /DS Fall (Write) Delay   | 15*             | 440#                     |

|         | TdMR(DR)  | /MREQ [Read Data Required Valid              |                 | <b>140</b> * 20, 12 (12) |

| 23      | TdC(MR)   | Clock Fall /MREQ Rise Delay                  |                 | 2 <b>50</b>              |

| 24      | TdC(ASf)  | Clock + /AS Fall Delay                       | 004             | <b>35</b>                |

| 25      | TdA(AS)   | Address Valid to /AS Rise Delay              | 20*             |                          |

| 26      | TdC(ASr)  | Clock [ /AS Rise Delay                       |                 | <b>25</b>                |

| 27      | TdAS(DR)  | /AS + Read Data Required Valid               |                 | . <b>140*</b>            |

| 28      | TdDS(AS)  | /DS + /AS Fall Delay                         | 20*             |                          |

| 29      | TwAS      | /AS Width (Low)                              | 35*             |                          |

| 30      | TdAS(A)   | /AS + Address Not Active Delay               | 30*             |                          |

| 31      | TdAz(DSR) | Address Float to /DS (Read) Fall Delay       | 0               |                          |

| 32      | TdAS(DSR) | /AS + /DS (Read) Fall Delay                  |                 | <b>35*</b>               |

| 33      | TdDSR(DR) | /DS (Read) Fall to Read Data Required Valid  |                 | 80*                      |

| 34      | TdC(DSr)  | Clock Fall to /DS Rise Delay                 |                 | 30                       |

| 35      | TdDS(DW)  | /DS + Write Data Not Valid                   | 25*             |                          |

| 36      | TdA(DSR)  | Address Valid to /DS (Read) Fall Delay       | 65*             |                          |

| 37      | TdC(DSR)  | Clock Rise /DS (Read) Fall Delay             |                 | 45                       |

| 38      | TwDSR     | /DS (Read) Width (Low)                       | 110*            |                          |

| 39      | TdC(DSW)  | Clock Fall to /DS (Write) Fall Delay         |                 | 45 ( 46 )                |

|         |           |                                              |                 |                          |

| 40      | TwDSW     | /DS (Write) Width (Low)                      | 75*             |                          |

| 41      | TdDSI(DR) | /DS (I/O) [ Read Data Required Valid         | 34.44 BV        | 120*                     |

| 42      | TdC(DSf)  | Clock [ /DS (I/O) Fall Delay                 | Se CAND 2       | 45                       |

| 43      | TwDS      | /DS (I/O) Width (Low)                        | 160*            |                          |

| 44      | TdAS(DSA) | /AS + /DS (Acknowledge) Fall Delay           | 410*            |                          |

| 45      | TdC(DSA)  | Clock + /DS (Acknowledge) Fall Delay         |                 | 1 <b>45</b>              |

| 46      | TdDSA(DR) | /DS (Acknowledge) [ Read Data Required Delay |                 | <b>165*</b>              |

| 47      | TdC(S)    | Clock Rise to Status Valid Delay             |                 | <b>50</b>                |

| <u></u> |           |                                              |                 |                          |

## AC CHARACTERISTICS (Continued)

| No.      | Symbol             | Parameter                                                        | Z16C01/2<br>10 MHz<br>Min Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48       | TdS(AS)            | Status Valid to /AS Rise Delay                                   | 20*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 49       | TsR(C)             | /RESET to Clock Rise Setup Time                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 50       | ThR(C)             | /RESET to Clock Rise Hold Time                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 51<br>52 | TwNMI<br>TsNMI(C)  | /NMI Width (Low)                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 53       | TsVI(C)            | /NMI to Clock Rise Setup Time /VI, /NVI to Clock Rise Setup Time | 7 (1) (1) (3) (3) (3) (4) (4) (4) (4) (4) (4) (4) (4) (4) (4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 54       | ThVI(C)            | /VI, /NVI to Clock Rise Hold Time                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 55       | TsSGT(C)           | /SEGT to Clock Rise Setup Time                                   | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 56       | ThSGT(C)           | /SEGT to Clock Rise Hold Time                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 57       | TsMI(C)            | /MI to Clock Rise Setup Time                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 58<br>59 | ThMI(C)<br>TdC(MO) | /MI to Clock Rise Hold Time                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 60       | TsSTP(C)           | Clock Rise to /MO Delay<br>/STOP to Clock Fall Setup Time        | 7. Sec. 1997.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 61       | ThSTP(C)           | /STOP to Clock Fall Hold Time                                    | [4], \$14, <b>35</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 62       | TsW(C)             | /WAIT to Clock Fall Setup Time                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 63       | ThW(C)             | /WAIT to Clock Fall Hold Time                                    | 다리 2,5학 대로 생활하다. 후기 회가 가는 모든 모든 모든                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 64       | TsBRQ(C)           | /BUSREQ to Clock Rise Setup Time                                 | 원생 (kj. 35, ) : [원생 (kj. 1 ki ) : [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [원 (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [đ (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 ki ) ] (kj. 1 ki ) [d (kj. 1 |

| 65       | ThBRQ(C)           | /BUSREQ to Clock Rise Hold Time                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 66<br>67 | TdC(BAKr)          | Clock Rise to /BUSACK Rise Delay                                 | 를 하다고 하는 <b>35</b> 로만 급하는 것이 되고 있다.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 68       | TdC(BAKf)<br>TwA   | Clock Rise to /BUSACK Fall Delay<br>Address Valid Width          | 35 En*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 69       | TdDS(S)            | /DS Rise to STATUS Not Valid                                     | 50*<br>30*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |                    | 7-0                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

<sup>\*</sup> Clock-cycle time-dependent characteristics. See Footnotes to AC Characteristics. \*\* Clock may be stopped. † Units in nanoseconds (ns).

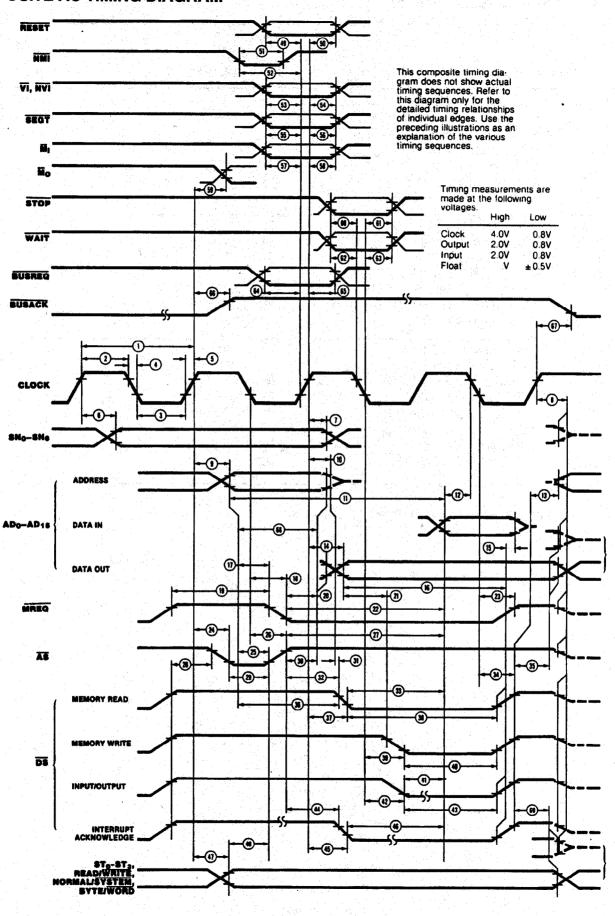

### **COMPOSITE AC TIMING DIAGRAM**

**Composite AC Timing**

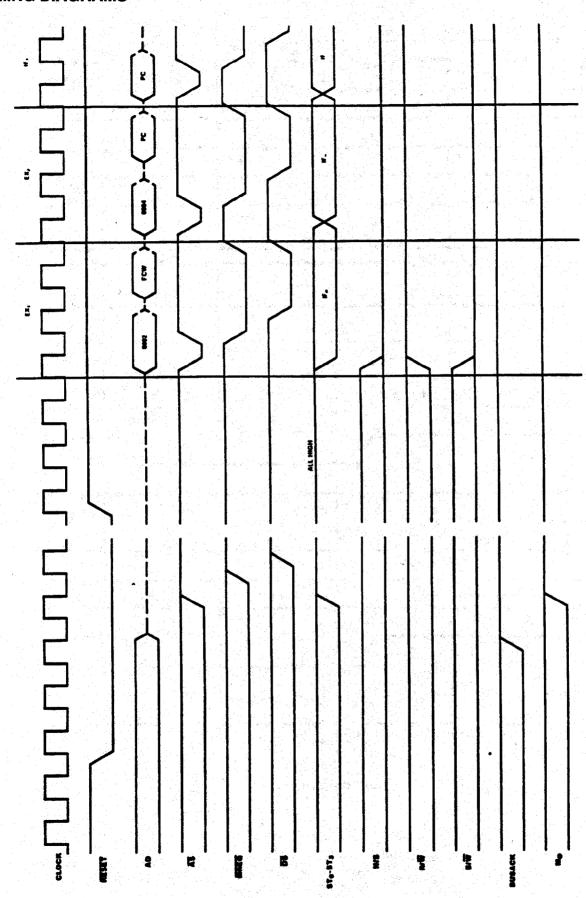

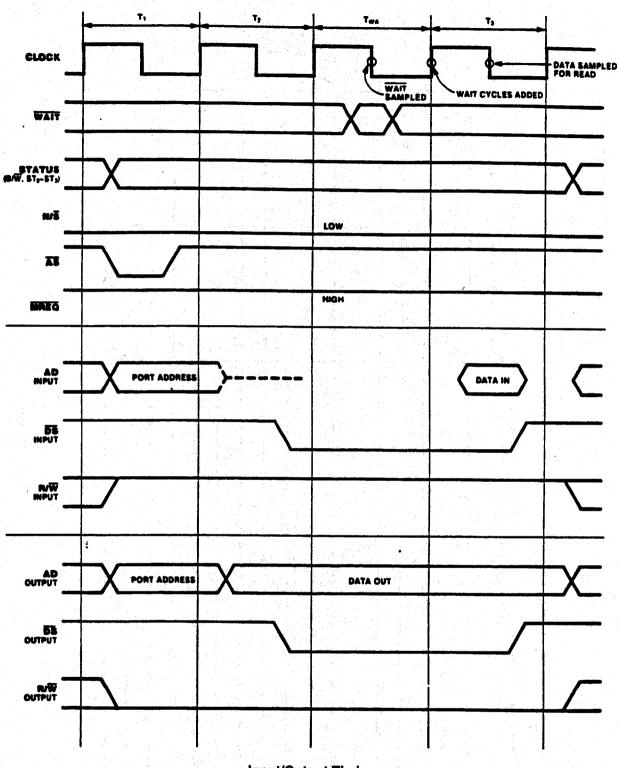

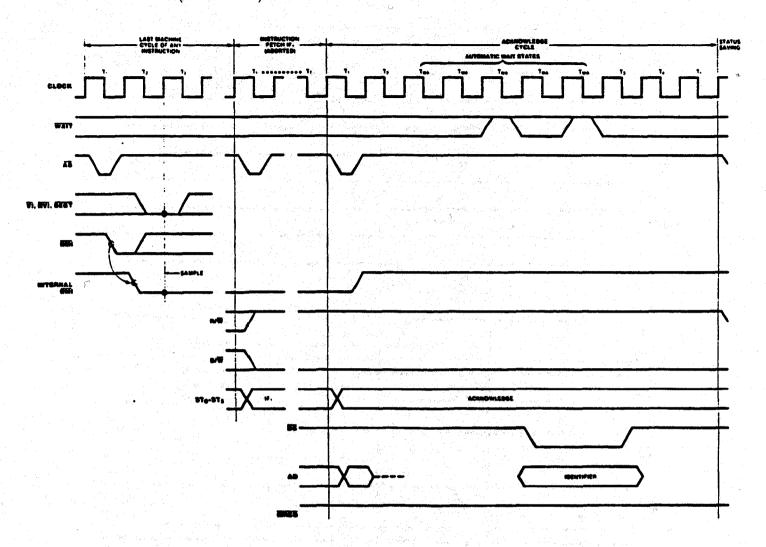

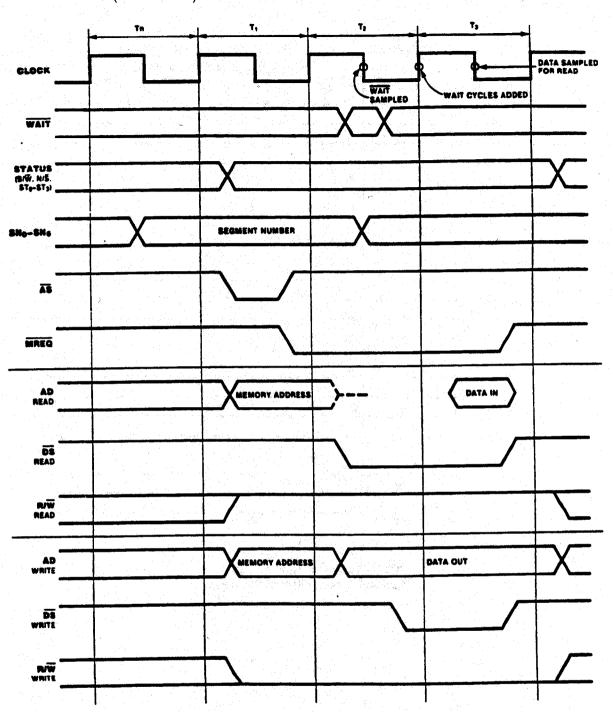

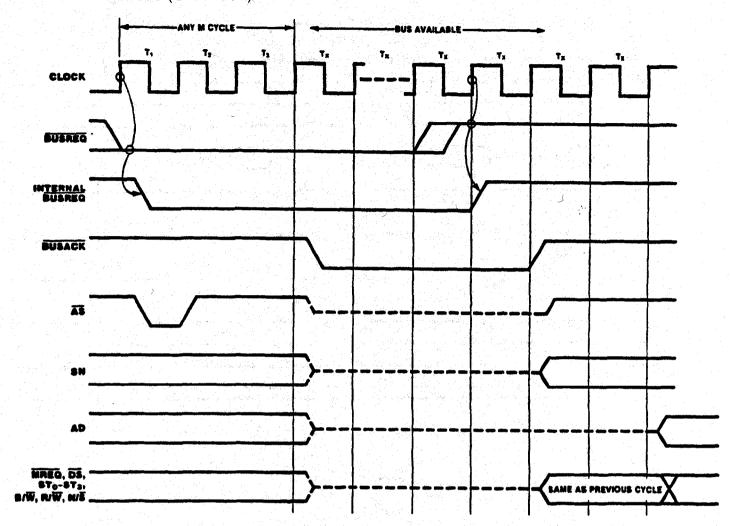

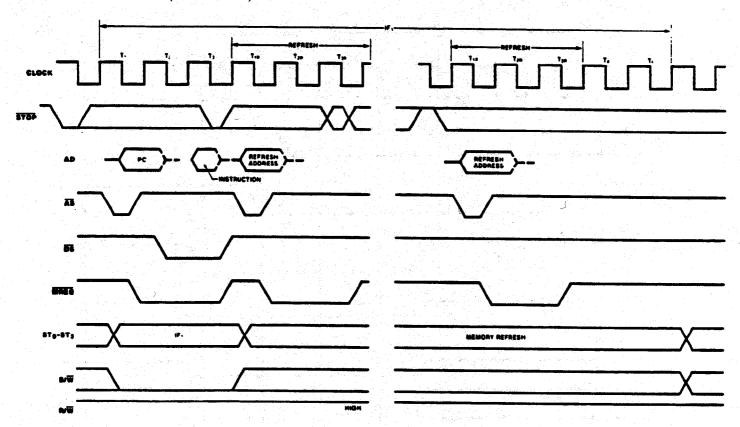

### **TIMING DIAGRAMS**

Reset Timing

Input/Output Timing

Interrupt and Segment Trap Request/Acknowledge Timing

**Memory Read and Write Timing**

**Bus Request/Acknowledge Timing**

**Stop Timing**

© 1995 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 Telex 910-338-7621 FAX 408 370-8056

Internet: http://www.zilog.com/zilog General Questions: info@zilog.com