Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                  |

| Core Size                  | 16/32-Bit                                                              |

| Speed                      | 44MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI                                                  |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 20                                                                     |

| Program Memory Size        | 62KB (31K x16)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 32                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                            |

| Data Converters            | A/D 12x12b; D/A 4x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

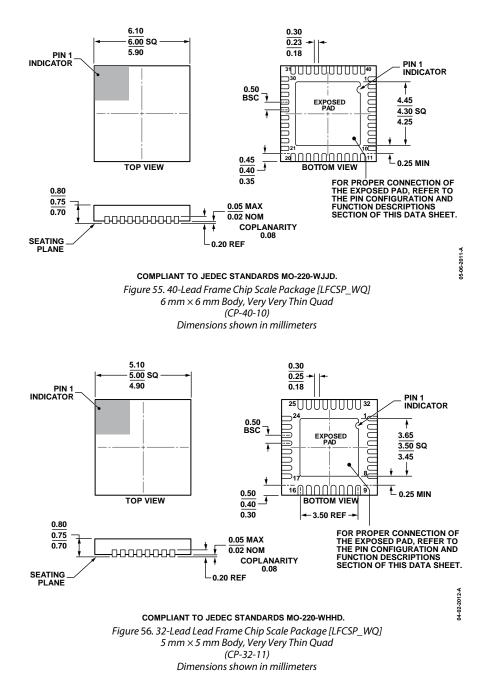

| Package / Case             | 40-WFQFN Exposed Pad, CSP                                              |

| Supplier Device Package    | 40-LFCSP-WQ (6x6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7023bcp6z62ir7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ADUC7023\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS

View a parametric search of comparable parts.

# EVALUATION KITS

ADuC7023 QuickStart Plus Development Systems

# **DOCUMENTATION**

### **Application Notes**

AN-806: Flash Programming via I2C—Protocol Type 5

### Data Sheet

ADuC7023: Precision Analog Microcontroller, 12-Bit Analog I/O, ARM7TDMI MCU with Enhanced IRQ Handler Data Sheet

### **User Guides**

UG-176: Evaluation Board User Guide for ADuC7023

# REFERENCE DESIGNS

• CN0153

# REFERENCE MATERIALS

#### Informational

• SFP Chipset and Reference Design Simplify 4.25 GBPS Transceivers

### **Technical Articles**

- · Integrated Route Taken to Pulse Oximetry

- · Low Power, Low Cost, Wireless ECG Holter Monitor

- Part 1: Simplifying Design of Industrial Process-Control Systems with PLC Evaluation Boards

- Part 2: Simplifying Design of Industrial Process-Control Systems with PLC Evaluation Boards

- Precision Analog Microcontroller Simplifies Optical Transceiver Design

# DESIGN RESOURCES

- ADuC7023 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

# DISCUSSIONS

View all ADuC7023 EngineerZone Discussions.

# SAMPLE AND BUY

Visit the product page to see pricing options.

# TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

# DOCUMENT FEEDBACK

Submit feedback for this data sheet.

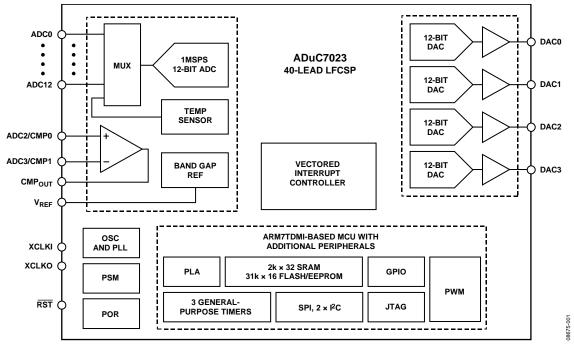

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

# **SPECIFICATIONS**

$AV_{DD} = IOV_{DD} = 2.7 V$  to 3.6 V,  $V_{REF} = 2.5 V$  internal reference,  $f_{CORE} = 41.78 MHz$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

| Table 1.                                         | _     |           |                          |        | 1                                                                  |

|--------------------------------------------------|-------|-----------|--------------------------|--------|--------------------------------------------------------------------|

| Parameter                                        | Min   | Тур       | Max                      | Unit   | Test Conditions/Comments                                           |

| ADC CHANNEL SPECIFICATIONS                       |       |           |                          |        | Eight acquisition clocks and f <sub>ADC</sub> /2                   |

| ADC Power-Up Time                                |       | 5         |                          | μs     |                                                                    |

| DC Accuracy <sup>1, 2</sup>                      |       |           |                          |        |                                                                    |

| Resolution                                       | 12    |           |                          | Bits   |                                                                    |

| Integral Nonlinearity                            |       | ±0.6      | ±1.5                     | LSB    | 2.5 V internal reference                                           |

|                                                  |       | ±1.0      |                          | LSB    | 1.0 V external reference                                           |

| Differential Nonlinearity <sup>3, 4</sup>        |       | ±0.5      | +1/-0.9                  | LSB    | 2.5 V internal reference                                           |

|                                                  |       | +0.7/-0.6 |                          | LSB    | 1.0 V external reference                                           |

| DC Code Distribution                             |       | 1         |                          | LSB    | ADC input is a dc voltage                                          |

| ENDPOINT ERRORS <sup>5</sup>                     |       |           |                          |        |                                                                    |

| Offset Error                                     |       | ±1        | ±2                       | LSB    |                                                                    |

| Offset Error Match                               |       | ±1        |                          | LSB    |                                                                    |

| Gain Error                                       |       | ±2        |                          | LSB    |                                                                    |

| Gain Error Match                                 |       | ±1        |                          | LSB    |                                                                    |

| DYNAMIC PERFORMANCE                              |       |           |                          |        | $f_{IN} = 10 \text{ kHz}$ sine wave, $f_{SAMPLE} = 1 \text{ MSPS}$ |

| Signal-to-Noise Ratio (SNR)                      |       | 69        |                          | dB     | Includes distortion and noise components                           |

| Total Harmonic Distortion (THD)                  |       | -78       |                          | dB     |                                                                    |

| Peak Harmonic or Spurious Noise                  |       | -75       |                          | dB     |                                                                    |

| Channel-to-Channel Crosstalk                     |       | -80       |                          | dB     | Measured on adjacent channels                                      |

| ANALOG INPUT                                     |       |           |                          |        |                                                                    |

| Input Voltage Ranges                             |       |           |                          |        |                                                                    |

| Differential Mode                                |       |           | $V_{CM} \pm V_{REF}/2^6$ | V      |                                                                    |

| Single-Ended Mode                                |       |           | $0$ to $V_{\text{REF}}$  | V      |                                                                    |

| Leakage Current                                  |       | ±1        | ±6                       | μA     |                                                                    |

| Input Capacitance                                |       | 20        |                          | рF     | During ADC acquisition                                             |

| ON-CHIP VOLTAGE REFERENCE                        |       |           |                          |        | 0.47 μF from V <sub>REF</sub> to AGND                              |

| Output Voltage                                   |       | 2.5       |                          | V      |                                                                    |

| Accuracy                                         |       |           | ±4                       | mV     | $T_A = 25^{\circ}C$                                                |

| Reference Temperature Coefficient                |       | ±15       |                          | ppm/°C |                                                                    |

| Power Supply Rejection Ratio                     |       | 75        |                          | dB     |                                                                    |

| Output Impedance                                 |       | 51        |                          | Ω      | $T_A = 25^{\circ}C$                                                |

| Internal V <sub>REF</sub> Power-On Time          |       | 1         |                          | ms     |                                                                    |

| EXTERNAL REFERENCE INPUT                         |       |           |                          |        |                                                                    |

| Input Voltage Range                              | 0.625 |           | AV <sub>DD</sub>         | V      |                                                                    |

| DAC CHANNEL SPECIFICATIONS                       |       |           |                          |        |                                                                    |

| DC Accuracy <sup>7</sup>                         |       |           |                          |        | $R_L = 5 k\Omega, C_L = 100 pF$                                    |

| Resolution                                       |       | 12        |                          | Bits   |                                                                    |

| Relative Accuracy                                |       | ±2        |                          | LSB    |                                                                    |

| Differential Nonlinearity                        |       |           | ±1                       | LSB    | Guaranteed monotonic                                               |

| Offset Error                                     |       |           | ±15                      | mV     | 2.5 V internal reference                                           |

| Gain Error <sup>8</sup>                          |       |           | ±1                       | %      |                                                                    |

| Gain Error Mismatch                              |       | 0.1       |                          | %      | % of full scale on DAC0                                            |

| DC Accuracy <sup>9</sup>                         |       |           |                          |        | $R_L = 1 k\Omega, C_L = 100 pF$                                    |

| Resolution                                       |       | 12        |                          | Bits   |                                                                    |

| Relative Accuracy                                |       | ±2.5      |                          | LSB    |                                                                    |

| Differential Nonlinearity                        |       | ±1        |                          | LSB    | Guaranteed monotonic                                               |

| Offset Error                                     |       | ±15       |                          | mV     | 2.5 V internal reference                                           |

| Gain Error <sup>10</sup>                         |       | ±1        |                          | %      |                                                                    |

| Gain Error Mismatch                              |       | 0.1       |                          | %      | % of full scale on DAC0                                            |

| ANALOG OUTPUTS                                   |       |           |                          |        |                                                                    |

|                                                  |       | 0 to 2.5  |                          | v      | V <sub>REF</sub> range: AGND to AV <sub>DD</sub>                   |

| Output Voltage Range 1                           |       | 0102      |                          |        |                                                                    |

| Output Voltage Range 1<br>Output Voltage Range 2 |       | 0 to 2.5  |                          | v      |                                                                    |

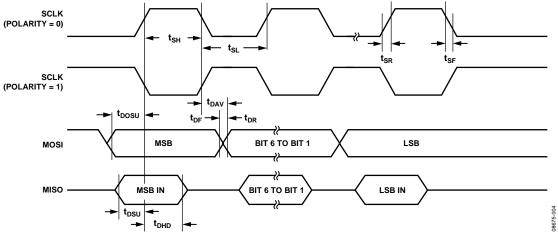

| Table 5. SPI Master Mode Timing (Phase Mode = 0) |  |

|--------------------------------------------------|--|

|--------------------------------------------------|--|

| Parameter         | Description                                         | Min                        | Тур                            | Max  | Unit |

|-------------------|-----------------------------------------------------|----------------------------|--------------------------------|------|------|

| t <sub>sL</sub>   | SCLK low pulse width <sup>1</sup>                   |                            | $(SPIDIV + 1) \times t_{UCLK}$ |      | ns   |

| t <sub>sH</sub>   | SCLK high pulse width <sup>1</sup>                  |                            | $(SPIDIV + 1) \times t_{UCLK}$ |      | ns   |

| t <sub>DAV</sub>  | Data output valid after SCLK edge                   |                            |                                | 25   | ns   |

| t <sub>DOSU</sub> | Data output setup before SCLK edge                  |                            |                                | 75   | ns   |

| tdsu              | Data input setup time before SCLK edge <sup>1</sup> | $1 \times t_{\text{UCLK}}$ |                                |      | ns   |

| t <sub>DHD</sub>  | Data input hold time after SCLK edge <sup>1</sup>   | $2 	imes t_{\text{UCLK}}$  |                                |      | ns   |

| t <sub>DF</sub>   | Data output fall time                               |                            | 5                              | 12.5 | ns   |

| t <sub>DR</sub>   | Data output rise time                               |                            | 5                              | 12.5 | ns   |

| t <sub>sr</sub>   | SCLK rise time                                      |                            | 5                              | 12.5 | ns   |

| tsF               | SCLK fall time                                      |                            | 5                              | 12.5 | ns   |

$^{1}$  t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider.

Figure 4. SPI Master Mode Timing (Phase Mode = 0)

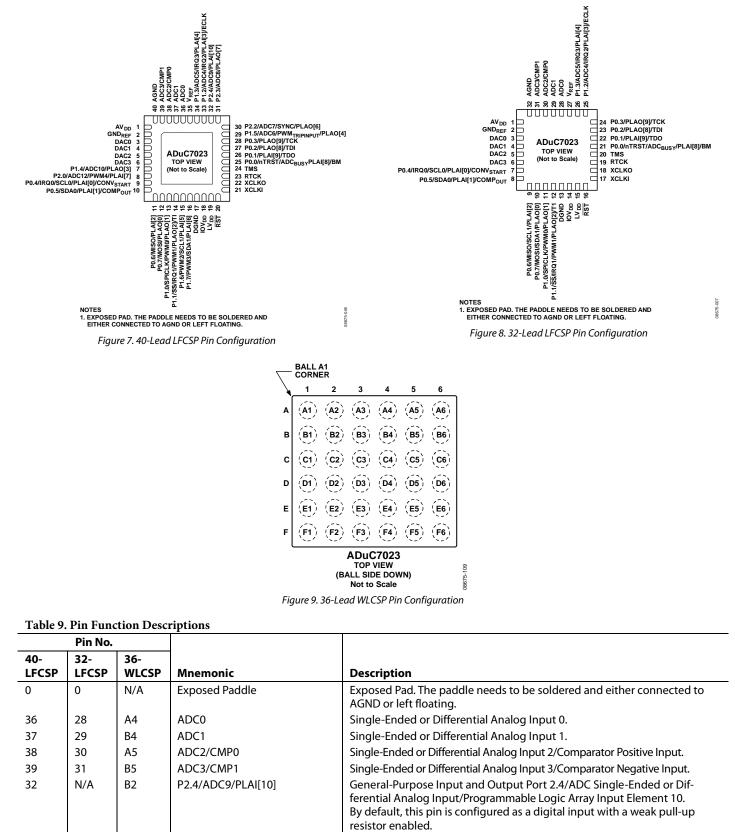

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

# ADuC7023

|       | Pin No. |       |                              |                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|---------|-------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40-   | 32-     | 36-   |                              |                                                                                                                                                                                                                                                                                                                                                                                        |

| LFCSP | LFCSP   | WLCSP | Mnemonic                     | Description                                                                                                                                                                                                                                                                                                                                                                            |

| 34    | 26      | A3    | P1.3/ADC5/IRQ3/PLAI[4]       | General-Purpose Input and Output Port 1.3/ADC Single-Ended or<br>Differential Analog Input 5/External Interrupt Request 3/ Programmable<br>Logic Array Input Element 4.<br>By default, this pin is configured as a digital input with a weak pull-up<br>resistor enabled. When used as ADC input, the pull-up resistor should be<br>disabled manually.                                 |

| 33    | 25      | A2    | P1.2/ADC4/IRQ2/PLAI[3]/ECLK/ | General-Purpose Input and Output Port 1.2/ADC Single-Ended or<br>Differential Analog Input 4/External Interrupt Request 2/ Programmable<br>Logic Array Input Element 3/Input-Output for External Clock.<br>By default, this pin is configured as a digital input with a weak pull-up<br>resistor enabled. When used as ADC input, the pull-up resistor should be<br>disabled manually. |

| 14    | 12      | F4    | P1.1/SS/IRQ1/PWM1/PLAO[2]/T1 | General-Purpose Input and Output Port 1.1/SPI Interface Slave Select<br>(Active Low)/External Interrupt Request 1/PWM Output 1/ Programmable<br>Logic Array Output Element 2/Timer 1 Input Clock. By default, this pin is<br>configured as a digital input with a weak pull-up resistor enabled.                                                                                       |

| 13    | 11      | E4    | P1.0/SCLK/PWM0/PLAO[1]       | General-Purpose Input and Output Port 1.0/SPI Interface Clock Signal/<br>PWM Output 0/Programmable Logic Array Output Element 1. By default,<br>this pin is configured as a digital input with a weak pull-up resistor enabled.                                                                                                                                                        |

| 35    | 27      | B3    | V <sub>REF</sub>             | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 $\mu\text{F}$ capacitor when using the internal reference.                                                                                                                                                                                                                                                               |

| 40    | 32      | A6    | AGND                         | Analog Ground. Ground reference point for the analog circuitry.                                                                                                                                                                                                                                                                                                                        |

| 1     | 1       | B6    | AV <sub>DD</sub>             | 3.3 V Analog Power.                                                                                                                                                                                                                                                                                                                                                                    |

More information relative to the model of the programmer and the ARM7TDMI core architecture can be found in ARM7TDMI technical and ARM architecture manuals available directly from ARM Ltd.

# **INTERRUPT LATENCY**

The worst-case latency for a fast interrupt request (FIQ) consists of the following: the longest time the request can take to pass through the synchronizer, the time for the longest instruction to complete (the longest instruction is an LDM) that loads all the registers including the PC, and the time for the data abort and FIQ entry.

At the end of this time, the ARM7TDMI executes the instruction at 0x1C (FIQ interrupt vector address). The maximum total time is 50 processor cycles, which is just under 1.2  $\mu$ s in a system using a continuous 41.78 MHz processor clock.

The maximum interrupt request (IRQ) latency calculation is similar but must allow for the fact that FIQ has higher priority and could delay entry into the IRQ handling routine for an arbitrary length of time. This time can be reduced to 42 cycles if the LDM command is not used. Some compilers have an option to compile without using this command. Another option is to run the part in thumb mode where the time is reduced to 22 cycles.

The minimum latency for FIQ or IRQ interrupts is a total of five cycles, which consist of the shortest time the request can take through the synchronizer, plus the time to enter the exception mode.

The ARM7TDMI always runs in ARM (32-bit) mode when in privileged modes, for example, when executing interrupt service routines.

# **NONVOLATILE FLASH/EE MEMORY**

The ADuC7023 incorporates Flash/EE memory technology on chip to provide the user with nonvolatile, in-circuit reprogrammable memory space.

Like EEPROM, flash memory can be programmed in-system at a byte level, although it must first be erased. The erase is performed in page blocks. As a result, flash memory is often and more correctly referred to as Flash/EE memory.

The Flash/EE memory represents a step closer to the ideal memory device that includes nonvolatility, in-circuit programmability, high density, and low cost. Incorporated in the ADuC7023, Flash/EE memory technology allows the user to update program code space in-circuit, without needing to replace one-time programmable (OTP) devices at remote operating nodes.

Each part contains a 64 kB array of Flash/EE memory. The lower 62 kB are available to the user, and the upper 2 kB contain permanently embedded firmware, allowing in-circuit serial download. These 2 kB of embedded firmware also contain a power-on configuration routine that downloads factorycalibrated coefficients to the various calibrated peripherals (such as ADC, temperature sensor, and band gap references). This 2 kB embedded firmware is hidden from user code.

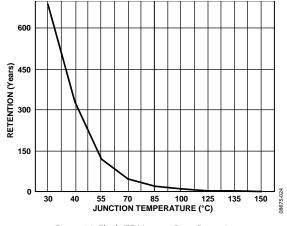

### Flash/EE Memory Reliability

The Flash/EE memory arrays on the parts are fully qualified for two key Flash/EE memory characteristics: Flash/EE memory cycling endurance and Flash/EE memory data retention.

Endurance quantifies the ability of the Flash/EE memory to be cycled through many program, read, and erase cycles. A single endurance cycle is composed of four independent, sequential events, defined as:

- 1. Initial page erase sequence.

- 2. Read/verify sequence (single Flash/EE).

- 3. Byte program sequence memory.

- 4. Second read/verify sequence (endurance cycle).

In reliability qualification, every half word (16-bit wide) location of the three pages (top, middle, and bottom) in the Flash/EE memory is cycled 10,000 times from 0x0000 to 0xFFFF. As indicated in Table 1, the Flash/EE memory endurance qualification is carried out in accordance with JEDEC Retention Lifetime Specification A117 over the industrial temperature range of  $-40^{\circ}$  to  $+125^{\circ}$ C. The results allow the specification of a minimum endurance figure over a supply temperature of 10,000 cycles.

Retention quantifies the ability of the Flash/EE memory to retain its programmed data over time. Again, the parts are qualified in accordance with the formal JEDEC Retention Lifetime Specification (A117) at a specific junction temperature ( $T_1 = 85^{\circ}$ C). As part of this qualification procedure, the Flash/EE memory is cycled to its specified endurance limit before data retention is characterized. This means that the Flash/EE memory is guaranteed to retain its data for its fully specified retention lifetime every time the Flash/EE memory is reprogrammed. In addition, note that retention lifetime, based on activation energy of 0.6 eV, derates with  $T_J$  as shown in Figure 30.

Figure 30. Flash/EE Memory Data Retention

# PROGRAMMING

The 62 kB of Flash/EE memory can be programmed in circuit, using the serial download mode or the provided JTAG mode.

### Downloading (In-Circuit Programming) via I<sup>2</sup>C

The ADuC7023 facilitates code download via the the I<sup>2</sup>C port. The parts enter download mode after a reset or power cycle if the BM pin is pulled low through an external 1 k $\Omega$  resistor and Flash Addess 0x80014 = 0xFFFFFFF. Once in download mode, the user can download code to the full 62 kB of Flash/EE memory while the device is in-circuit in its target application hardware. An executable PC I<sup>2</sup>C download is provided as part of the development system for serial downloading via the I<sup>2</sup>C. A USB to I<sup>2</sup>C download dongle can be purchased from Analog Devices, Inc. This board connects to the USB port of a PC and to the I<sup>2</sup>C port of the ADuC7023. The part number is USB-I2C/LIN-CONV-Z.

The AN-806 Application Note describes the protocol for serial downloading via the I<sup>2</sup>C in more detail.

### JTAG Access

The JTAG protocol uses the on-chip JTAG interface to facilitate code download and debug.

The JTAG interface is active as long as the part is not in download mode; that is, the P0.0/BM pin = 0 and Address 0x80014 = 0xFFFFFFF at reset.

When debugging, user code must not write to the bits in GP0CON/GP0DAT corresponding to P0.0/P0.1/P0.2 and P0.3 pins. If user code changes the state of any of these pins, JTAG debug pods are not able to connect to the ADuC7023. In case this happens, the user should have a function in code that can be called externally to mass erase the part. Alternatively, the user should ensure that Flash Address 0x80014 is erased to allow erasing of the part through the I<sup>2</sup>C interface.

# ADuC7023

# FEEMOD Register

| Name:          | FEEMOD                                                                                                     |

|----------------|------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF804                                                                                                  |

| Default value: | 0x0000                                                                                                     |

| Access:        | Read/write                                                                                                 |

| Function:      | FEEMOD sets the operating mode of the flash control interface. Table 32 shows FEEMOD MMR bit designations. |

### Table 32. FEEMOD MMR Bit Designations

| Bit     | Description                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------|

| 15 to 9 | Reserved.                                                                                                      |

| 8       | Reserved. Always set this bit to 0.                                                                            |

| 7 to 5  | Reserved. Always set this bit to 0 except when writing keys. See the Sequence to Write the Key section.        |

| 4       | Flash/EE interrupt enable.                                                                                     |

|         | This bit is set by the user to enable the Flash/EE interrupt. The interrupt occurs when a command is complete. |

|         | This bit is cleared by the user to disable the Flash/EE interrupt.                                             |

| 3       | Erase/write command protection.                                                                                |

|         | This bit is set by the user to enable the erase and write commands.                                            |

|         | This bit is cleared to protect the Flash/EE against erase/write command.                                       |

| 2 to 0  | Reserved. Always set this bit to 0.                                                                            |

# **FEECON** Register

| Name:          | FEECON                                                                       |

|----------------|------------------------------------------------------------------------------|

| Address:       | 0xFFFF808                                                                    |

| Default value: | 0x07                                                                         |

| Access:        | Read/write                                                                   |

| Function:      | FEECON is an 8-bit command register. The commands are described in Table 33. |

### Table 33. Command Codes in FEECON

| Code              | Command       | Description                                                                                                                                                                                                                                           |

|-------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00 <sup>1</sup> | Null          | Idle state.                                                                                                                                                                                                                                           |

| 0x01 <sup>1</sup> | Single read   | Load FEEDAT with the 16-bit data. Indexed by FEEADR.                                                                                                                                                                                                  |

| 0x02 <sup>1</sup> | Single write  | Write FEEDAT at the address pointed by FEEADR. This operation takes 50 μs.                                                                                                                                                                            |

| 0x03 <sup>1</sup> | Erase/write   | Erase the page indexed by FEEADR, and write FEEDAT at the location pointed by FEEADR. This operation takes approximately 24 ms.                                                                                                                       |

| 0x04 <sup>1</sup> | Single verify | Compare the contents of the location pointed by FEEADR to the data in FEEDAT. The result of the comparison is returned in FEESTA Bit 1.                                                                                                               |

| 0x05 <sup>1</sup> | Single erase  | Erase the page indexed by FEEADR.                                                                                                                                                                                                                     |

| 0x06 <sup>1</sup> | Mass erase    | Erase 62 kB of user space. The 2 kB of kernel are protected. This operation takes 2.48 sec. To prevent accidental execution, a command sequence is required to execute this instruction. See the Command Sequence for Executing a Mass Erase section. |

| 0x07              | Reserved      | Reserved.                                                                                                                                                                                                                                             |

| 0x08              | Reserved      | Reserved.                                                                                                                                                                                                                                             |

| 0x09              | Reserved      | Reserved.                                                                                                                                                                                                                                             |

| 0x0A              | Reserved      | Reserved.                                                                                                                                                                                                                                             |

| 0x0B              | Signature     | Give a signature of the 64 kB of Flash/EE in the 24-bit FEESIGN MMR. This operation takes 32,778 clock cycles.                                                                                                                                        |

| 0x0C              | Protect       | This command can run one time only. The value of FEEPRO is saved and removed only with a mass erase (0x06) or the key (FEEADR/FEEDAT).                                                                                                                |

# Table 63. SPISTA MMR Bit Designations

| Bit      | Name           | Description                                                                                                                                               |

|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 12 |                | Reserved bits.                                                                                                                                            |

| 11       | SPIREX         | SPI Rx FIFO excess bytes present.                                                                                                                         |

|          |                | This bit is set when there are more bytes in the Rx FIFO than indicated in the SPIMDE bits in SPICON.                                                     |

|          |                | This bit is cleared when the number of bytes in the FIFO is equal or less than the number in SPIMDE.                                                      |

| 10 to 8  | SPIRXFSTA[2:0] | SPI Rx FIFO status bits.                                                                                                                                  |

|          |                | [000] = Rx FIFO is empty.                                                                                                                                 |

|          |                | [001] = 1 valid byte in the FIFO.                                                                                                                         |

|          |                | [010] = 2 valid byte in the FIFO.                                                                                                                         |

|          |                | [011] = 3 valid byte in the FIFO.                                                                                                                         |

|          |                | [100] = 4 valid byte in the FIFO.                                                                                                                         |

| 7        | SPIFOF         | SPI Rx FIFO overflow status bit.                                                                                                                          |

|          |                | This bit is set when the Rx FIFO is full when new data is loaded to the FIFO. This bit generates an interrupt except when SPIRFLH is set in SPICON.       |

|          |                | This bit is cleared when the SPISTA register is read.                                                                                                     |

| 6        | SPIRXIRQ       | SPI Rx IRQ status bit.                                                                                                                                    |

|          |                | This bit is set when a receive interrupt occurs. This bit is set when SPITMDE in SPICON is cleared and the required number of bytes have been received.   |

|          |                | This bit is cleared when the SPISTA register is read.                                                                                                     |

| 5        | SPITXIRQ       | SPI Tx IRQ status bit.                                                                                                                                    |

|          |                | This bit is set when a transmit interrupt occurs. This bit is set when SPITMDE in SPICON is set and the required number of bytes have been transmitted.   |

|          |                | This bit is cleared when the SPISTA register is read.                                                                                                     |

| 4        | SPITXUF        | SPI Tx FIFO underflow.                                                                                                                                    |

|          |                | This bit is set when a transmit is initiated without any valid data in the Tx FIFO. This bit generates an interrupt except when SPITFLH is set in SPICON. |

|          |                | This bit is cleared when the SPISTA register is read.                                                                                                     |

| 3 to 1   | SPITXFSTA[2:0] | SPI Tx FIFO status bits.                                                                                                                                  |

|          |                | [000] = Tx FIFO is empty.                                                                                                                                 |

|          |                | [001] = 1 valid byte in the FIFO.                                                                                                                         |

|          |                | [010] = 2 valid byte in the FIFO.                                                                                                                         |

|          |                | [011] = 3 valid byte in the FIFO.                                                                                                                         |

|          |                | [100] = 4 valid byte in the FIFO.                                                                                                                         |

| 0        | SPIISTA        | SPI interrupt status bit.                                                                                                                                 |

|          |                | This bit is set to 1 when an SPI based interrupt occurs.                                                                                                  |

|          |                | This bit is cleared after reading SPISTA.                                                                                                                 |

| SPIRX Registe  | ister SPITX Register                        |                | r                                            |

|----------------|---------------------------------------------|----------------|----------------------------------------------|

| Name:          | SPIRX                                       | Name:          | SPITX                                        |

| Address:       | 0xFFFF0A04                                  | Address:       | 0xFFFF0A08                                   |

| Default value: | 0x00                                        | Default value: | 0xXX                                         |

| Access:        | Read                                        | Access:        | Write                                        |

| Function:      | This 8-bit MMR is the SPI receive register. | Function:      | This 8-bit MMR is the SPI transmit register. |

| Bit      | Value | Description                                                                       |

|----------|-------|-----------------------------------------------------------------------------------|

| 31 to 11 |       | Reserved.                                                                         |

| 10 to 9  |       | Mux 0 control (see Table 81).                                                     |

| 8 to 7   |       | Mux 1 control (see Table 81).                                                     |

| 6        |       | Mux 2 control.                                                                    |

|          |       | This bit is set by the user to select the output of Mux 0.                        |

|          |       | This bit is cleared by the user to select the bit value from the PLADIN register. |

| 5        |       | Mux 3 control.                                                                    |

|          |       | This bit is set by the user to select the input pin of the particular element.    |

|          |       | This bit is cleared by the user to select the output of Mux 1.                    |

| 4 to 1   |       | Look-up table control.                                                            |

|          | 0000  | 0.                                                                                |

|          | 0001  | NOR.                                                                              |

|          | 0010  | B and not A.                                                                      |

|          | 0011  | Not A.                                                                            |

|          | 0100  | A and not B.                                                                      |

|          | 0101  | Not B.                                                                            |

|          | 0110  | EXOR.                                                                             |

|          | 0111  | NAND.                                                                             |

|          | 1000  | AND.                                                                              |

|          | 1001  | EXNOR.                                                                            |

|          | 1010  | В.                                                                                |

|          | 1011  | Not A or B.                                                                       |

|          | 1100  | Α.                                                                                |

|          | 1101  | A or not B.                                                                       |

|          | 1110  | OR.                                                                               |

|          | 1111  | 1.                                                                                |

| C        |       | Mux 4 control.                                                                    |

|          |       | This bit is set by the user to bypass the flip-<br>flop.                          |

|          |       | This bit is cleared by the user to select the flip-flop (cleared by default).     |

# Table 77. PLAELMx MMR Bit Descriptions

# PLACLK Register

| Name:          | PLACLK                                                                                                                                                         |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0B40                                                                                                                                                     |

| Default value: | 0x00                                                                                                                                                           |

| Access:        | Read/write                                                                                                                                                     |

| Function:      | PLACLK is the clock selection for the flip-<br>flops. The maximum frequency when using<br>the GPIO pins as the clock input for the PLA<br>blocks is 41.78 MHz. |

# Table 78. PLACLK MMR Bit Descriptions

| Bit     | Value | Description                  |

|---------|-------|------------------------------|

| 31 to 7 |       | Reserved.                    |

| 6 to 4  |       | Clock source selection.      |

|         | 000   | GPIO clock on P0.5.          |

|         | 001   | GPIO clock on P1.1.          |

|         | 010   | GPIO clock on P1.6.          |

|         | 011   | HCLK.                        |

|         | 100   | External 32.768 kHz crystal. |

|         | 101   | Timer1 overflow.             |

|         | 110   | UCLK.                        |

|         | 111   | Internal 32,768 oscillator.  |

| 3       |       | Reserved.                    |

| 2 to 0  |       | Clock source selection.      |

|         | 000   | GPIO clock on P0.5.          |

|         | 001   | GPIO clock on P1.1.          |

|         | 010   | GPIO clock on P1.6.          |

|         | 011   | HCLK.                        |

|         | 100   | External 32.768 kHz crystal. |

|         | 101   | Timer1 overflow.             |

|         | 110   | UCLK.                        |

|         | 111   | Internal 32,768 oscillator.  |

# ADuC7023

# PLAIRQ Register

| -              |                                                                    |

|----------------|--------------------------------------------------------------------|

| Name:          | PLAIRQ                                                             |

| Address:       | 0xFFFF0B44                                                         |

| Default value: | 0x0000000                                                          |

| Access:        | Read/write                                                         |

| Function:      | PLAIRQ enables IRQ0 and/or IRQ1 and selects the source of the IRQ. |

# Table 79. PLAIRQ MMR Bit Descriptions

| Bit      | Value | Description                                                         |

|----------|-------|---------------------------------------------------------------------|

| 31 to 13 |       | Reserved.                                                           |

| 12       |       | PLA IRQ1 enable bit.                                                |

| 11 to 8  | 0000  | PLA Element 0.                                                      |

|          | 0001  | PLA Element 1.                                                      |

|          | 0010  | PLA Element 2.                                                      |

|          | 0011  | PLA Element 3.                                                      |

|          | 0100  | PLA Element 4.                                                      |

|          | 0101  | PLA Element 5.                                                      |

|          | 0110  | PLA Element 6.                                                      |

|          | 0111  | PLA Element 7.                                                      |

|          | 1000  | PLA Element 8.                                                      |

|          | 1001  | PLA Element 9.                                                      |

|          | 1010  | PLA Element 10.                                                     |

|          | 1011  | PLA Element 11.                                                     |

|          | 1100  | PLA Element 12.                                                     |

|          | 1101  | PLA Element 13.                                                     |

|          | 1110  | PLA Element 14.                                                     |

|          | 1111  | PLA Element 15.                                                     |

| 7 to 5   |       | Reserved.                                                           |

| 4        |       | PLA IRQ0 enable bit.                                                |

|          |       | This bit is set by the user to enable IRQ0 output from PLA.         |

|          |       | This bit is cleared by the user to disable<br>IRQ0 output from PLA. |

| 3 to 0   |       | PLA IRQ0 source.                                                    |

|          | 0000  | PLA Element 0.                                                      |

|          | 0001  | PLA Element 1.                                                      |

|          | 0010  | PLA Element 2.                                                      |

|          | 0011  | PLA Element 3.                                                      |

|          | 0100  | PLA Element 4.                                                      |

|          | 0101  | PLA Element 5.                                                      |

|          | 0110  | PLA Element 6.                                                      |

|          | 0111  | PLA Element 7.                                                      |

|          | 1xxx  | Reserved.                                                           |

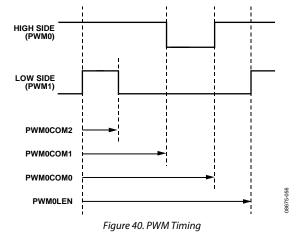

# PULSE-WIDTH MODULATOR pulse-width modulator general overview

The ADuC7023 integrates a 5-channel pulse-width modulator (PWM) interface. The PWM outputs can be configured to drive an H-bridge or can be used as standard PWM outputs. On power-up, the PWM outputs default to H-bridge mode. This ensures that the motor is turned off by default. In standard PWM mode, the outputs are arranged as three pairs of PWM pins. Users have control over the period of each pair of outputs and over the duty cycle of each individual output.

#### Table 84. PWM MMRs

| MMR Name | Description                                              |

|----------|----------------------------------------------------------|

| PWMCON1  | PWM Control Register 1.                                  |

| PWM0COM0 | Compare Register 0 for PWM Output 0 and<br>PWM Output 1. |

| PWM0COM1 | Compare Register 1 for PWM Output 0 and PWM Output 1.    |

| PWM0COM2 | Compare Register 2 for PWM Output 0 and PWM Output 1.    |

| PWMOLEN  | Frequency control for PWM Output 0 and PWM Output 1.     |

| PWM1COM0 | Compare Register 0 for PWM Output 2 and PWM Output 3.    |

| PWM1COM1 | Compare Register 1 for PWM Output 2 and PWM Output 3.    |

| PWM1COM2 | Compare Register 2 for PWM Output 2 and PWM Output 3.    |

| PWM1LEN  | Frequency control for PWM Output 2 and PWM Output 3.     |

| PWM2COM0 | Compare Register 0 for PWM Output 4                      |

| PWM2COM1 | Compare Register 1 for PWM Output 4                      |

| PWM2LEN  | Frequency control for PWM Output 4.                      |

| PWMCLRI  | PWM interrupt clear.                                     |

In all modes, the PWMxCOMx MMRs control the point at which the PWM outputs change state. An example of the first pair of PWM outputs (PWM0 and PWM1) is shown in Figure 40.

The PWM clock is selectable via PWMCON1 with one of the following values: UCLK divided by 2, 4, 8, 16, 32, 64, 128, or 256. The length of a PWM period is defined by PWMxLEN.

The PWM waveforms are set by the count value of the 16-bit timer and the compare registers contents, as shown with the PWM0 and PWM1 waveforms in Figure 40.

The low-side waveform, PWM1, goes high when the timer count reaches PWM0LEN, and it goes low when the timer count reaches the value held in PWM0COM2 or when the high-side waveform (PWM0) goes low.

The high-side waveform, PWM0, goes high when the timer count reaches the value held in PWM0COM0, and it goes low when the timer count reaches the value held in PWM0COM1.

#### **PWMCON1** Control Register

| Name:          | PWMCON1                                               |

|----------------|-------------------------------------------------------|

| Address:       | 0xFFFF0F80                                            |

| Default value: | 0x0012                                                |

| Access:        | Read and write                                        |

| Function:      | This is a 16-bit MMR that configures the PWM outputs. |

### Table 85. PWMCON1 MMR Bit Designations

| Bit    | Name       | Description                                                                                                                                                                    |

|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14     | SYNC       | Enables PWM synchronization.                                                                                                                                                   |

|        |            | Set to 1 by the user so that all PWM counters are reset on the next clock edge after the detection of a high-to-low transition on the P2.2/SYNC pin.                           |

|        |            | Cleared by the user to ignore transitions on the P2.2/SYNC pin.                                                                                                                |

| 13     | Reserved   | Set to 0 by the user.                                                                                                                                                          |

| 12     | PWM3INV    | Set to 1 by the user to invert PWM3.                                                                                                                                           |

|        |            | Cleared by the user to use PWM3 in normal mode.                                                                                                                                |

| 11     | PWM1INV    | Set to 1 by the user to invert PWM1.                                                                                                                                           |

|        |            | Cleared by the user to use PWM1 in normal mode.                                                                                                                                |

| 10     | PWMTRIP    | Set to 1 by the user to enable PWM trip interrupt. When the PWM trip input (Pin P1.5/PWM <sub>TRPINPUT</sub> ) is low, the PWMEN bit is cleared and an interrupt is generated. |

|        |            | Cleared by the user to disable the PWMTRIP interrupt.                                                                                                                          |

| 9      | ENA        | If HOFF = 0 and HMODE = 1. Note that, if not in H-bridge mode, this bit has no effect.                                                                                         |

|        |            | Set to 1 by the user to enable PWM outputs.                                                                                                                                    |

|        |            | Cleared by the user to disable PWM outputs.                                                                                                                                    |

|        |            | If HOFF = 1 and HMODE = 1, see Table 86.                                                                                                                                       |

| 8 to 6 | PWMCP[2:0] | PWM clock prescaler bits. Sets the UCLK divider.                                                                                                                               |

|        |            | [000] = UCLK/2.                                                                                                                                                                |

|        |            | [001] = UCLK/4.                                                                                                                                                                |

|        |            | [010] = UCLK/8.                                                                                                                                                                |

|        |            | [011] = UCLK/16.                                                                                                                                                               |

|        |            | [100] = UCLK/32.                                                                                                                                                               |

|        |            | [101] = UCLK/64.                                                                                                                                                               |

|        |            | [110] = UCLK/128.                                                                                                                                                              |

|        |            | [111] = UCLK/256.                                                                                                                                                              |

| 5      | POINV      | Set to 1 by the user to invert all PWM outputs.                                                                                                                                |

|        |            | Cleared by the user to use PWM outputs as normal.                                                                                                                              |

| 4      | HOFF       | High side off.                                                                                                                                                                 |

|        |            | Set to 1 by the user to force PWM0 and PWM2 outputs high. This also forces PWM1 and PWM3 low.                                                                                  |

|        |            | Cleared by the user to use the PWM outputs as normal.                                                                                                                          |

| 3      | LCOMP      | Load compare registers.                                                                                                                                                        |

|        |            | Set to 1 by the user to load the internal compare registers with the values in PWMxCOMx on the next transition of the PWM timer from 0x00 to 0x01.                             |

|        |            | Cleared by the user to use the values previously stored in the internal compare registers.                                                                                     |

| 2      | DIR        | Direction control.                                                                                                                                                             |

|        |            | Set to 1 by the user to enable PWM0 and PWM1 as the output signals while PWM2 and PWM3 are held low.                                                                           |

|        |            | Cleared by the user to enable PWM2 and PWM3 as the output signals while PWM0 and PWM1 are held low.                                                                            |

| 1      | HMODE      | Enables H-bridge mode. <sup>1</sup>                                                                                                                                            |

|        |            | Set to 1 by the user to enable H-bridge mode.                                                                                                                                  |

|        |            | Cleared by the user to operate the PWMs in standard mode.                                                                                                                      |

| 0      | PWMEN      | Set to 1 by the user to enable all PWM outputs.                                                                                                                                |

|        |            | Cleared by the user to disable all PWM outputs.                                                                                                                                |

$^{1}$  In H-bridge mode, HMODE = 1. See Table 86 to determine the PWM outputs.

# **Data Sheet**

| DWWAACOMAA                                                                                             | Commons Do alistan                                                                                                                                                                                              | PWM1COM0                                                                                              |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Name:                                                                                                  | Compare Register<br>PWM0COM0                                                                                                                                                                                    | Name:                                                                                                 |

|                                                                                                        | PWM0COM0                                                                                                                                                                                                        |                                                                                                       |

| Address:                                                                                               | 0xFFFF0F84                                                                                                                                                                                                      | Address:                                                                                              |

| Default value:                                                                                         | 0x0000                                                                                                                                                                                                          | Default value:                                                                                        |

| Access:                                                                                                | Read and write                                                                                                                                                                                                  | Access:                                                                                               |

| Function:                                                                                              | PWM0 output pin goes high when the PWM<br>timer reaches the count value stored in this<br>register.                                                                                                             | Function:                                                                                             |

| РШМОСОМ1                                                                                               | Compare Register                                                                                                                                                                                                | PWM1COM1                                                                                              |

| Name:                                                                                                  | PWM0COM1                                                                                                                                                                                                        | Name:                                                                                                 |

| Address:                                                                                               | 0xFFFF0F88                                                                                                                                                                                                      | Address:                                                                                              |

| Default value:                                                                                         | 0x0000                                                                                                                                                                                                          | Default value:                                                                                        |

| Access:                                                                                                | Read and write                                                                                                                                                                                                  | Access:                                                                                               |

| Function:                                                                                              | PWM0 output pin goes low when the PWM timer reaches the count value stored in this register.                                                                                                                    | Function:                                                                                             |

|                                                                                                        | 0                                                                                                                                                                                                               |                                                                                                       |

| PWM0COM2                                                                                               | Compare Register                                                                                                                                                                                                | PWM1COM2                                                                                              |

| <b>PWM0COM2 (</b><br>Name:                                                                             | -                                                                                                                                                                                                               | <b>PWM1COM2</b><br>Name:                                                                              |

|                                                                                                        | Compare Register                                                                                                                                                                                                |                                                                                                       |

| Name:                                                                                                  | Compare Register<br>PWM0COM2                                                                                                                                                                                    | Name:                                                                                                 |

| Name:<br>Address:                                                                                      | Compare Register<br>PWM0COM2<br>0xFFFF0F8C                                                                                                                                                                      | Name:<br>Address:                                                                                     |

| Name:<br>Address:<br>Default value:                                                                    | Compare Register<br>PWM0COM2<br>0xFFFF0F8C<br>0x0000                                                                                                                                                            | Name:<br>Address:<br>Default value:                                                                   |

| Name:<br>Address:<br>Default value:<br>Access:<br>Function:                                            | Compare Register<br>PWM0COM2<br>0xFFFF0F8C<br>0x0000<br>Read and write<br>PWM1 output pin goes low when the PWM<br>timer reaches the count value stored in this<br>register.                                    | Name:<br>Address:<br>Default value:<br>Access:                                                        |

| Name:<br>Address:<br>Default value:<br>Access:                                                         | Compare Register<br>PWM0COM2<br>0xFFFF0F8C<br>0x0000<br>Read and write<br>PWM1 output pin goes low when the PWM<br>timer reaches the count value stored in this<br>register.                                    | Name:<br>Address:<br>Default value:<br>Access:<br>Function:                                           |

| Name:<br>Address:<br>Default value:<br>Access:<br>Function:                                            | Compare Register<br>PWM0COM2<br>0xFFFF0F8C<br>0x0000<br>Read and write<br>PWM1 output pin goes low when the PWM<br>timer reaches the count value stored in this<br>register.                                    | Name:<br>Address:<br>Default value:<br>Access:<br>Function:<br><b>PWM1LEN Re</b>                      |

| Name:<br>Address:<br>Default value:<br>Access:<br>Function:<br><b>PWMOLEN Reg</b><br>Name:             | Compare Register<br>PWM0COM2<br>0xFFFF0F8C<br>0x0000<br>Read and write<br>PWM1 output pin goes low when the PWM<br>timer reaches the count value stored in this<br>register.<br>pWM0LEN                         | Name:<br>Address:<br>Default value:<br>Access:<br>Function:<br><b>PWM1LEN Re</b><br>Name:             |

| Name:<br>Address:<br>Default value:<br>Access:<br>Function:<br><b>PWMOLEN Reg</b><br>Name:<br>Address: | Compare Register<br>PWM0COM2<br>0xFFFF0F8C<br>0x0000<br>Read and write<br>PWM1 output pin goes low when the PWM<br>timer reaches the count value stored in this<br>register.<br>pister<br>PWM0LEN<br>0xFFFF0F90 | Name:<br>Address:<br>Default value:<br>Access:<br>Function:<br><b>PWM1LEN Re</b><br>Name:<br>Address: |

# PWM1COM0 Compare Register

| P WINI I COINIO | Lompule Register                                                                              |

|-----------------|-----------------------------------------------------------------------------------------------|

| Name:           | PWM1COM0                                                                                      |

| Address:        | 0xFFFF0F94                                                                                    |

| Default value:  | 0x0000                                                                                        |

| Access:         | Read and write                                                                                |

| Function:       | PWM2 output pin goes high when the PWM timer reaches the count value stored in this register. |

| PWM1COM1        | Compare Register                                                                              |

| Name:           | PWM1COM1                                                                                      |

| Address:        | 0xFFFF0F98                                                                                    |

| Default value:  | 0x0000                                                                                        |

| Access:         | Read and write                                                                                |

| Function:       | PWM2 output pin goes low when the PWM timer reaches the count value stored in this register.  |

| PWM1COM2        | Compare Register                                                                              |

| Name:           | PWM1COM2                                                                                      |

| Address:        | 0xFFFF0F9C                                                                                    |

| Default value:  | 0x0000                                                                                        |

| Access:         | Read and write                                                                                |

| Function:       | PWM3 output pin goes low when the PWM timer reaches the count value stored in this register.  |

| PWM1LEN Reg     | gister                                                                                        |

| Name:           | PWM1LEN                                                                                       |

| Address:        | 0xFFFF0FA0                                                                                    |

| Default value:  | 0x0000                                                                                        |

| Access:         | Read and write                                                                                |

| Function:       | PWM3 output pin goes high when the PWM                                                        |

timer reaches the value stored in this register.

# PROCESSOR REFERENCE PERIPHERALS **INTERRUPT SYSTEM**