Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | 792                                                             |

| Total RAM Bits                 | -                                                               |

| Number of I/O                  | 101                                                             |

| Number of Gates                | 30000                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                              |

| Package / Case                 | 128-TQFP                                                        |

| Supplier Device Package        | 128-VTQFP (14x14)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/aglp030v5-vq128i |

|                                |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 🌜 Microsemi.

IGLOO PLUS Low Power Flash FPGAs

## I/Os Per Package<sup>1</sup>

| IGLOO PLUS Devices | AGLP030 | AGLP060           | AGLP125 |  |

|--------------------|---------|-------------------|---------|--|

| Package            |         | Single-Ended I/Os |         |  |

| CS201              | 120     | 157               | _       |  |

| CS281              | -       | -                 | 212     |  |

| CS289              | 120     | 157               | 212     |  |

| VQ128              | 101     | -                 | _       |  |

| VQ176              | -       | 137               | _       |  |

Note: When the Flash\*Freeze pin is used to directly enable Flash\*Freeze mode and not used as a regular I/O, the number of singleended user I/Os available is reduced by one.

#### Table 2 • IGLOO PLUS FPGAs Package Size Dimensions

| Package                | CS201 | CS281   | CS289   | VQ128   | VQ176   |

|------------------------|-------|---------|---------|---------|---------|

| Length × Width (mm/mm) | 8 × 8 | 10 × 10 | 14 × 14 | 14 × 14 | 20 × 20 |

| Nominal Area (mm2)     | 64    | 100     | 196     | 196     | 400     |

| Pitch (mm)             | 0.5   | 0.5     | 0.8     | 0.4     | 0.4     |

| Height (mm)            | 0.89  | 1.05    | 1.20    | 1.0     | 1.0     |

## **IGLOO PLUS Device Status**

| IGLOO PLUS Device | Status     |

|-------------------|------------|

| AGLP030           | Production |

| AGLP060           | Production |

| AGLP125           | Production |

## **Temperature Grade Offerings**

| Package | AGLP030 | AGLP060 | AGLP125 |

|---------|---------|---------|---------|

| CS201   | C, I    | C, I    | -       |

| CS281   | -       | -       | C, I    |

| CS289   | C, I    | C, I    | C, I    |

| VQ128   | C, I    | -       | -       |

| VQ176   | -       | C, I    | _       |

Notes:

C = Commercial temperature range: 0°C to 85°C junction temperature.

I = Industrial temperature range: -40°C to 100°C junction temperature.

Contact your local Microsemi SoC Products Group representative for device availability:

http://www.microsemi.com/soc/company/contact/default.aspx.

Each I/O module contains several input, output, and output enable registers.

Hot-swap (also called hot-plug, or hot-insertion) is the operation of hot-insertion or hot-removal of a card in a powered-up system.

Cold-sparing (also called cold-swap) refers to the ability of a device to leave system data undisturbed when the system is powered up, while the component itself is powered down, or when power supplies are floating.

### Wide Range I/O Support

IGLOO PLUS devices support JEDEC-defined wide range I/O operation. IGLOO PLUS devices support both the JESD8-B specification, covering 3 V and 3.3 V supplies, for an effective operating range of 2.7 V to 3.6 V, and JESD8-12 with its 1.2 V nominal, supporting an effective operating range of 1.14 V to 1.575 V.

Wider I/O range means designers can eliminate power supplies or power conditioning components from the board or move to less costly components with greater tolerances. Wide range eases I/O bank management and provides enhanced protection from system voltage spikes, while providing the flexibility to easily run custom voltage applications.

### Specifying I/O States During Programming

You can modify the I/O states during programming in FlashPro. In FlashPro, this feature is supported for PDB files generated from Designer v8.5 or greater. See the *FlashPro User's Guide* for more information.

- Note: PDB files generated from Designer v8.1 to Designer v8.4 (including all service packs) have limited display of Pin Numbers only.

- 1. Load a PDB from the FlashPro GUI. You must have a PDB loaded to modify the I/O states during programming.

- 2. From the FlashPro GUI, click PDB Configuration. A FlashPoint Programming File Generator window appears.

- 3. Click the Specify I/O States During Programming button to display the Specify I/O States During Programming dialog box.

- 4. Sort the pins as desired by clicking any of the column headers to sort the entries by that header. Select the I/Os you wish to modify (Figure 1-4 on page 1-8).

- Set the I/O Output State. You can set Basic I/O settings if you want to use the default I/O settings for your pins, or use Custom I/O settings to customize the settings for each pin. Basic I/O state settings:

- 1 I/O is set to drive out logic High

- 0 I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming Z -Tri-State: I/O is tristated

| Product<br>Grade | Programming<br>Cycles | Program<br>Retention<br>(biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub><br>(°C) <sup>2</sup> | Maximum Operating<br>Junction<br>Temperature T <sub>J</sub> (°C) <sup>2</sup> |

|------------------|-----------------------|-------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Commercial       | 500                   | 20 years                                  | 110                                                                  | 100                                                                           |

| Industrial       | 500                   | 20 years                                  | 110                                                                  | 100                                                                           |

#### Table 2-3 • Flash Programming Limits – Retention, Storage, and Operating Temperature <sup>1</sup>

Notes:

1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

2. These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

| Table 2-4 • Overshoot and Undershoot Limits |

|---------------------------------------------|

|---------------------------------------------|

| vcci          | Average VCCI–GND Overshoot or<br>Undershoot Duration<br>as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                                 | 1.4 V                                         |

|               | 5%                                                                                                  | 1.49 V                                        |

| 3 V           | 10%                                                                                                 | 1.1 V                                         |

|               | 5%                                                                                                  | 1.19 V                                        |

| 3.3 V         | 10%                                                                                                 | 0.79 V                                        |

|               | 5%                                                                                                  | 0.88 V                                        |

| 3.6 V         | 10%                                                                                                 | 0.45 V                                        |

|               | 5%                                                                                                  | 0.54 V                                        |

Notes:

1. Based on reliability requirements at 85°C.

2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every IGLOO PLUS device. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-4.

There are five regions to consider during power-up.

IGLOO PLUS I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 2-1 and Figure 2-2 on page 2-5).

- 2. VCCI > VCC 0.75 V (typical)

- 3. Chip is in the operating mode.

#### VCCI Trip Point:

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.2 V Ramping down (V5 devices): 0.5 V < trip\_point\_down < 1.1 V Ramping up (V2 devices): 0.75 V < trip\_point\_up < 1.05 V Ramping down (V2 devices): 0.65 V < trip\_point\_down < 0.95 V

#### VCC Trip Point:

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.1 V Ramping down (V5 devices): 0.5 V < trip\_point\_down < 1.0 V **Microsemi**

IGLOO PLUS DC and Switching Characteristics

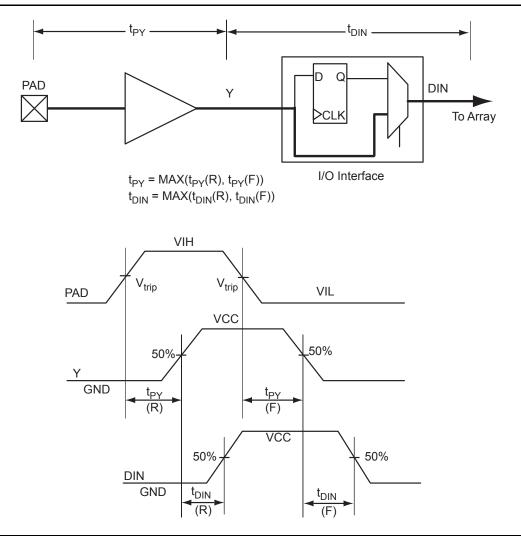

Figure 2-4 • Input Buffer Timing Model and Delays (example)

| Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances          |

|--------------------------------------------------------------|

| Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values |

|                         | ${\sf R}_{\sf (WEAK PULL-UP)}^1$ ( $\Omega$ ) |       | $R_{(WEAK PULL-DOWN)}^2$ ( $\Omega$ ) |       |

|-------------------------|-----------------------------------------------|-------|---------------------------------------|-------|

| VCCI                    | Min.                                          | Max.  | Min.                                  | Max.  |

| 3.3 V                   | 10 K                                          | 45 K  | 10 K                                  | 45 K  |

| 3.3 V (wide range I/Os) | 10 K                                          | 45 K  | 10 K                                  | 45 K  |

| 2.5 V                   | 11 K                                          | 55 K  | 12 K                                  | 74 K  |

| 1.8 V                   | 18 K                                          | 70 K  | 17 K                                  | 110 K |

| 1.5 V                   | 19 K                                          | 90 K  | 19 K                                  | 140 K |

| 1.2 V                   | 25 K                                          | 110 K | 25 K                                  | 150 K |

| 1.2 V (wide range I/Os) | 19 K                                          | 110 K | 19 K                                  | 150 K |

Notes:

R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>(WEAK PULL-UP-MIN)</sub>

R<sub>(WEAK PULLDOWN-MAX)</sub> = (VOLspec) / I<sub>(WEAK PULLDOWN-MIN)</sub>

#### Table 2-30 • I/O Short Currents IOSH/IOSL

|                            | Drive Strength | IOSL (mA)*         | IOSH (mA)*             |

|----------------------------|----------------|--------------------|------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA           | 27                 | 25                     |

|                            | 4 mA           | 27                 | 25                     |

|                            | 6 mA           | 54                 | 51                     |

|                            | 8 mA           | 54                 | 51                     |

|                            | 12 mA          | 109                | 103                    |

|                            | 16 mA          | 109                | 103                    |

| 3.3 V LVCMOS Wide Range    | 100 µA         | Same as equivalent | software default drive |

| 2.5 V LVCMOS               | 2 mA           | 18                 | 16                     |

|                            | 4 mA           | 18                 | 16                     |

| Γ                          | 6 mA           | 37                 | 32                     |

|                            | 8 mA           | 37                 | 32                     |

|                            | 12 mA          | 74                 | 65                     |

| 1.8 V LVCMOS               | 2 mA           | 11                 | 9                      |

|                            | 4 mA           | 22                 | 17                     |

|                            | 6 mA           | 44                 | 35                     |

|                            | 8 mA           | 44                 | 35                     |

| 1.5 V LVCMOS               | 2 mA           | 16                 | 13                     |

| F                          | 4 mA           | 33                 | 25                     |

| 1.2 V LVCMOS               | 2 mA           | 26                 | 20                     |

| 1.2 V LVCMOS Wide Range    | 100 µA         | 26                 | 20                     |

*Note:*  $^{*}T_{J} = 100^{\circ}C$

IGLOO PLUS DC and Switching Characteristics

The length of time an I/O can withstand IOSH/IOSL events depends on the junction temperature. The reliability data below is based on a 3.3 V, 12 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than six months to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

#### Table 2-31 • Duration of Short Circuit Event before Failure

| Temperature | Time before Failure |

|-------------|---------------------|

| -40°C       | > 20 years          |

| 0°C         | > 20 years          |

| 25°C        | > 20 years          |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 6 months            |

#### Table 2-32 • Schmitt Trigger Input Hysteresis Hysteresis Voltage Value (Typ.) for Schmitt Mode Input Buffers

| Input Buffer Configuration                | Hysteresis Value (typ.) |

|-------------------------------------------|-------------------------|

| 3.3 V LVTTL/LVCMOS (Schmitt trigger mode) | 240 mV                  |

| 2.5 V LVCMOS (Schmitt trigger mode)       | 140 mV                  |

| 1.8 V LVCMOS (Schmitt trigger mode)       | 80 mV                   |

| 1.5 V LVCMOS (Schmitt trigger mode)       | 60 mV                   |

| 1.2 V LVCMOS (Schmitt trigger mode)       | 40 mV                   |

#### Table 2-33 • I/O Input Rise Time, Fall Time, and Related I/O Reliability

| Input Buffer             |          |         | Input Rise/Fall Time<br>(min.) | Input Rise/Fall Time<br>(max.)                                                     | Reliability      |

|--------------------------|----------|---------|--------------------------------|------------------------------------------------------------------------------------|------------------|

| LVTTL/LVCMOS disabled)   | (Schmitt | trigger | No requirement                 | 10 ns *                                                                            | 20 years (100°C) |

| LVTTL/LVCMOS<br>enabled) | (Schmitt | trigger | No requirement                 | No requirement, but input<br>noise voltage cannot<br>exceed Schmitt<br>hysteresis. | 20 years (100°C) |

Note: \*The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

## static Microsemi.

IGLOO PLUS DC and Switching Characteristics

#### Timing Characteristics

#### Applies to 1.5 V DC Core Voltage

## Table 2-36 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>1</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

|                |             |                   | -               |                  |                 |                  |                   |                 |                 |                 |                 |       |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

| 2 mA           | STD         | 0.97              | 3.94            | 0.18             | 0.85            | 1.15             | 0.66              | 4.02            | 3.46            | 1.82            | 1.87            | ns    |

| 4 mA           | STD         | 0.97              | 3.94            | 0.18             | 0.85            | 1.15             | 0.66              | 4.02            | 3.46            | 1.82            | 1.87            | ns    |

| 6 mA           | STD         | 0.97              | 3.20            | 0.18             | 0.85            | 1.15             | 0.66              | 3.27            | 2.94            | 2.04            | 2.27            | ns    |

| 8 mA           | STD         | 0.97              | 3.20            | 0.18             | 0.85            | 1.15             | 0.66              | 3.27            | 2.94            | 2.04            | 2.27            | ns    |

| 12 mA          | STD         | 0.97              | 2.72            | 0.18             | 0.85            | 1.15             | 0.66              | 2.78            | 2.57            | 2.20            | 2.53            | ns    |

| 16 mA          | STD         | 0.97              | 2.72            | 0.18             | 0.85            | 1.15             | 0.66              | 2.78            | 2.57            | 2.20            | 2.53            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Table 2-37 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 2.36            | 0.18             | 0.85            | 1.15             | 0.66              | 2.41            | 1.90            | 1.82            | 1.98            | ns    |

| 4 mA           | STD         | 0.97              | 2.36            | 0.18             | 0.85            | 1.15             | 0.66              | 2.41            | 1.90            | 1.82            | 1.98            | ns    |

| 6 mA           | STD         | 0.97              | 1.96            | 0.18             | 0.85            | 1.15             | 0.66              | 2.01            | 1.56            | 2.04            | 2.38            | ns    |

| 8 mA           | STD         | 0.97              | 1.96            | 0.18             | 0.85            | 1.15             | 0.66              | 2.01            | 1.56            | 2.04            | 2.38            | ns    |

| 12 mA          | STD         | 0.97              | 1.76            | 0.18             | 0.85            | 1.15             | 0.66              | 1.80            | 1.39            | 2.20            | 2.64            | ns    |

| 16 mA          | STD         | 0.97              | 1.76            | 0.18             | 0.85            | 1.15             | 0.66              | 1.80            | 1.39            | 2.20            | 2.64            | ns    |

Notes:

1. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2. Software default selection highlighted in gray.

#### Applies to 1.2 V DC Core Voltage

## Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.2 V DC Core VoltageCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.98              | 4.56            | 0.19             | 0.99            | 1.37             | 0.67              | 4.63            | 3.98            | 2.26            | 2.57            | ns    |

| 4 mA           | STD         | 0.98              | 4.56            | 0.19             | 0.99            | 1.37             | 0.67              | 4.63            | 3.98            | 2.26            | 2.57            | ns    |

| 6 mA           | STD         | 0.98              | 3.80            | 0.19             | 0.99            | 1.37             | 0.67              | 3.96            | 3.45            | 2.49            | 2.98            | ns    |

| 8 mA           | STD         | 0.98              | 3.80            | 0.19             | 0.99            | 137              | 0.67              | 3.86            | 3.45            | 2.49            | 2.98            | ns    |

| 12 mA          | STD         | 0.98              | 3.31            | 0.19             | 0.99            | 1.37             | 0.67              | 3.36            | 3.07            | 2.65            | 3.25            | ns    |

| 16 mA          | STD         | 0.98              | 3.31            | 0.19             | 0.99            | 1.37             | 0.67              | 3.36            | 3.07            | 2.65            | 3.25            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## static Microsemi.

IGLOO PLUS DC and Switching Characteristics

#### Timing Characteristics

#### Applies to 1.5 V DC Core Voltage

#### Table 2-42 • 3.3 V LVCMOS Wide Range Low Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 µA            | 4 mA                                                                          | STD            | 0.97              | 5.85            | 0.18             | 1.18            | 1.64             | 0.66              | 5.86            | 5.05            | 2.57            | 2.57            | ns    |

| 100 µA            | 6 mA                                                                          | STD            | 0.97              | 4.70            | 0.18             | 1.18            | 1.64             | 0.66              | 4.72            | 4.27            | 2.92            | 3.19            | ns    |

| 100 µA            | 8 mA                                                                          | STD            | 0.97              | 4.70            | 0.18             | 1.18            | 1.64             | 0.66              | 4.72            | 4.27            | 2.92            | 3.19            | ns    |

| 100 µA            | 12 mA                                                                         | STD            | 0.97              | 3.96            | 0.18             | 1.18            | 1.64             | 0.66              | 3.98            | 3.70            | 3.16            | 3.59            | ns    |

| 100 µA            | 16 mA                                                                         | STD            | 0.97              | 3.96            | 0.18             | 1.18            | 1.64             | 0.66              | 3.98            | 3.70            | 3.16            | 3.59            | ns    |

Notes:

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-43 • 3.3 V LVCMOS Wide Range High Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 µA            | 4 mA                                                                          | STD            | 0.97              | 3.39            | 0.18             | 1.18            | 1.64             | 0.66              | 3.41            | 2.69            | 2.57            | 2.73            | ns    |

| 100 µA            | 6 mA                                                                          | STD            | 0.97              | 2.79            | 0.18             | 1.18            | 1.64             | 0.66              | 2.80            | 2.17            | 2.92            | 3.36            | ns    |

| 100 µA            | 8 mA                                                                          | STD            | 0.97              | 2.79            | 0.18             | 1.18            | 1.64             | 0.66              | 2.80            | 2.17            | 2.92            | 3.36            | ns    |

| 100 µA            | 12 mA                                                                         | STD            | 0.97              | 2.47            | 0.18             | 1.18            | 1.64             | 0.66              | 2.48            | 1.91            | 3.16            | 3.76            | ns    |

| 100 µA            | 16 mA                                                                         | STD            | 0.97              | 2.47            | 0.18             | 1.18            | 1.64             | 0.66              | 2.48            | 1.91            | 3.16            | 3.76            | ns    |

Notes:

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

3. Software default selection highlighted in gray.

## **Microsemi**.

IGLOO PLUS DC and Switching Characteristics

### 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for generalpurpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

| 1.8 V<br>LVCMOS   | VIL     |             |             |         | VOH     | IOL       | ЮН | IOSL | IOSH                  | IIL¹                  | IIH <sup>2</sup> |                 |

|-------------------|---------|-------------|-------------|---------|---------|-----------|----|------|-----------------------|-----------------------|------------------|-----------------|

| Drive<br>Strength | Min., V | Max., V     | Min., V     | Max., V | Max., V | Min., V   | mA | mA   | Max., mA <sup>3</sup> | Max., mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup> |

| 2 mA              | -0.3    | 0.35 * VCCI | 0.65 * VCCI | 3.6     | 0.45    | VCCI-0.45 | 2  | 2    | 9                     | 11                    | 10               | 10              |

| 4 mA              | -0.3    | 0.35 * VCCI | 0.65 * VCCI | 3.6     | 0.45    | VCCI-0.45 | 4  | 4    | 17                    | 22                    | 10               | 10              |

| 6 mA              | -0.3    | 0.35 * VCCI | 0.65 * VCCI | 3.6     | 0.45    | VCCI-0.45 | 6  | 6    | 35                    | 44                    | 10               | 10              |

| 8 mA              | -0.3    | 0.35 * VCCI | 0.65 * VCCI | 3.6     | 0.45    | VCCI-0.45 | 8  | 8    | 35                    | 44                    | 10               | 10              |

| Table 2-52 • Minimum and Maximum | DC Input and Output Levels |

|----------------------------------|----------------------------|

|----------------------------------|----------------------------|

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

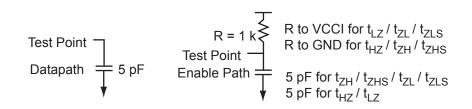

Test Point

Datapath

$$\downarrow$$

5 pF  $R = 1 k$

Enable Path  $\downarrow$   $R$  to VCCI for  $t_{LZ} / t_{ZL} / t_{ZLS}$

$R$  to GND for  $t_{HZ} / t_{ZH} / t_{ZHS}$

$5 pF$  for  $t_{ZH} / t_{ZHS} / t_{ZL} / t_{ZLS}$

$5 pF$  for  $t_{HZ} / t_{ZH} / t_{ZLS}$

#### Figure 2-9 • AC Loading

#### Table 2-53 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.8            | 0.9                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

IGLOO PLUS DC and Switching Characteristics

### 1.5 V LVCMOS (JESD8-11)

Low-Voltage CMOS for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for generalpurpose 1.5 V applications. It uses a 1.5 V input buffer and a push-pull output buffer.

| 1.5 V<br>LVCMOS   |           | VIL         | VIH        |           | VOL         | L VOH       |    | юн | IOSL                    | IOSH                    | IIL¹ | IIH <sup>2</sup> |

|-------------------|-----------|-------------|------------|-----------|-------------|-------------|----|----|-------------------------|-------------------------|------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V  | Max.<br>V | Max.<br>V   | Min.<br>V   | mA | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA⁴  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2  | 2  | 13                      | 16                      | 10   | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 4  | 4  | 25                      | 33                      | 10   | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

#### Figure 2-10 • AC Loading

Table 2-59 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.5            | 0.75                 | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

## **Microsemi**.

IGLOO PLUS DC and Switching Characteristics

#### 1.2 V DC Core Voltage

## Table 2-79 • Output Enable Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V

| Parameter             | Description                                                            | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 1.06 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.52 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 1.25 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 1.36 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.24 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.24 | ns    |

| tOEWCLR               | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.19 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.19 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.31 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

### *Timing Characteristics* 1.5 V DC Core Voltage

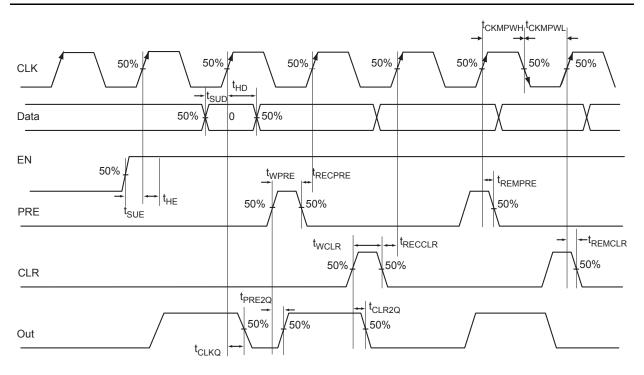

#### Table 2-82 • Register Delays

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.89 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.81 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.73 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.60 | ns    |

| t <sub>PRE2Q</sub>  | 2Q Asynchronous Preset-to-Q of the Core Register              |      | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        |      | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        |      | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.56 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.56 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## 🌜 Microsemi.

IGLOO PLUS DC and Switching Characteristics

## Embedded SRAM and FIFO Characteristics

#### RAM4K9 **RAM512X18** RADDR8 **RD17** ADDRA11 DOUTA8 RADDR7 RD16 DOUTA7 ADDRA10 -٠ . . ٠ DOUTAO ADDRA0 RADDR0 RD0 DINA8 DINA7 . RW1 RW0 DINA0 WIDTHA1 WIDTHA0 PIPE PIPEA WMODEA BLKA d REN WENA O RCLK CLKA ADDRB11 DOUTB8 WADDR8 ADDRB10 DOUTB7 WADDR7 ٠ ٠ ADDRB0 DOUTBO WADDR0 WD17 WD16 DINB8 DINB7 • WD0 . DINB0 WW1 ŴŴŎ WIDTHB1 WIDTHB0 PIPEB WMODEB BLKB -d WEN WENB d **DWCLK CLKB** RESET RESET

### SRAM

Figure 2-23 • RAM Models

Pin Descriptions and Packaging

#### VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

There is one VCOMPLF pin on IGLOO PLUS devices.

#### VJTAG JTAG Supply Voltage

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a device is in a JTAG chain of interconnected boards, the board containing the device can be powered down, provided both VJTAG and VCC to the part remain powered; otherwise, JTAG signals will not be able to transition the device, even in bypass mode.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

#### VPUMP Programming Supply Voltage

IGLOO PLUS devices support single-voltage ISP of the configuration flash and FlashROM. For programming, VPUMP should be 3.3 V nominal. During normal device operation, VPUMP can be left floating or can be tied (pulled up) to any voltage between 0 V and the VPUMP maximum. Programming power supply voltage (VPUMP) range is listed in the datasheet.

When the VPUMP pin is tied to ground, it will shut off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

### **User Pins**

#### I/O

GL

#### User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with the I/O standard selected.

During programming, I/Os become tristated and weakly pulled up to VCCI. With VCCI, VMV, and VCC supplies continuously powered up, when the device transitions from programming to operating mode, the I/Os are instantly configured to the desired user configuration.

Unused I/Os are configured as follows:

- Output buffer is disabled (with tristate value of high impedance)

- Input buffer is disabled (with tristate value of high impedance)

- Weak pull-up is programmed

#### Globals

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors.

See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" chapter of the *IGLOO PLUS FPGA Fabric User's Guide*. All inputs labeled GC/GF are direct inputs into the quadrant clocks. For example, if GAA0 is used for an input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs labeled GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. The inputs to the global network are multiplexed, and only one input can be used as a global input.

Refer to the I/O Structure chapter of the IGLOO PLUS FPGA Fabric User's Guide for an explanation of the naming of global pins.

IGLOO PLUS Low Power Flash FPGAs

| CS201      |                     | C          | S201                | CS201      |                     |  |

|------------|---------------------|------------|---------------------|------------|---------------------|--|

| Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function |  |

| H14        | IO45RSB1            | L15        | IO58RSB1            | P5         | IO87RSB2            |  |

| H15        | IO43RSB1            | M1         | IO93RSB3            | P6         | IO86RSB2            |  |

| J1         | GEA0/IO107RSB3      | M2         | IO92RSB3            | P7         | IO84RSB2            |  |

| J2         | IO105RSB3           | M3         | IO97RSB3            | P8         | IO80RSB2            |  |

| J3         | IO104RSB3           | M4         | GND                 | P9         | IO74RSB2            |  |

| J4         | IO102RSB3           | M5         | NC                  | P10        | IO73RSB2            |  |

| J6         | VCCIB3              | M6         | IO79RSB2            | P11        | IO76RSB2            |  |

| J7         | GND                 | M7         | IO77RSB2            | P12        | IO67RSB2            |  |

| J8         | VCC                 | M8         | IO72RSB2            | P13        | IO64RSB2            |  |

| J9         | GND                 | M9         | IO70RSB2            | P14        | VPUMP               |  |

| J10        | VCCIB1              | M10        | IO61RSB2            | P15        | TRST                |  |

| J12        | NC                  | M11        | IO59RSB2            | R1         | NC                  |  |

| J13        | NC                  | M12        | GND                 | R2         | NC                  |  |

| J14        | IO52RSB1            | M13        | NC                  | R3         | IO91RSB2            |  |

| J15        | IO50RSB1            | M14        | IO55RSB1            | R4         | FF/IO90RSB2         |  |

| K1         | IO103RSB3           | M15        | IO56RSB1            | R5         | IO89RSB2            |  |

| K2         | IO101RSB3           | N1         | NC                  | R6         | IO83RSB2            |  |

| K3         | IO99RSB3            | N2         | NC                  | R7         | IO82RSB2            |  |

| K4         | IO100RSB3           | N3         | GND                 | R8         | IO85RSB2            |  |

| K6         | GND                 | N4         | NC                  | R9         | IO78RSB2            |  |

| K7         | VCCIB2              | N5         | IO88RSB2            | R10        | IO69RSB2            |  |

| K8         | VCCIB2              | N6         | IO81RSB2            | R11        | IO62RSB2            |  |

| K9         | VCCIB2              | N7         | IO75RSB2            | R12        | IO60RSB2            |  |

| K10        | VCCIB1              | N8         | IO68RSB2            | R13        | TMS                 |  |

| K12        | NC                  | N9         | IO66RSB2            | R14        | TDI                 |  |

| K13        | IO57RSB1            | N10        | IO65RSB2            | R15        | ТСК                 |  |

| K14        | IO49RSB1            | N11        | IO71RSB2            |            |                     |  |

| K15        | IO53RSB1            | N12        | IO63RSB2            |            |                     |  |

| L1         | IO96RSB3            | N13        | GND                 |            |                     |  |

| L2         | IO98RSB3            | N14        | TDO                 |            |                     |  |

| L3         | IO95RSB3            | N15        | VJTAG               | 1          |                     |  |

| L4         | IO94RSB3            | P1         | NC                  | 1          |                     |  |

| L12        | NC                  | P2         | NC                  | 1          |                     |  |

| L13        | NC                  | P3         | NC                  | 1          |                     |  |

| L14        | IO51RSB1            | P4         | NC                  | 1          |                     |  |

Package Pin Assignments

| CS201      |                     | (          | CS201               | (          | CS201               |  |  |

|------------|---------------------|------------|---------------------|------------|---------------------|--|--|

| Pin Number | AGLP060<br>Function | Pin Number | AGLP060<br>Function | Pin Number | AGLP060<br>Function |  |  |

| A1         | IO150RSB3           | C6         | IO07RSB0            | F3         | IO145RSB3           |  |  |

| A2         | GAA0/IO00RSB0       | C7         | IO16RSB0            | F4         | IO147RSB3           |  |  |

| A3         | GAC0/IO04RSB0       | C8         | IO21RSB0            | F6         | GND                 |  |  |

| A4         | IO08RSB0            | C9         | IO28RSB0            | F7         | VCC                 |  |  |

| A5         | IO11RSB0            | C10        | GBB1/IO33RSB0       | F8         | VCCIB0              |  |  |

| A6         | IO15RSB0            | C11        | GBA1/IO35RSB0       | F9         | VCCIB0              |  |  |

| A7         | IO17RSB0            | C12        | GBB2/IO38RSB1       | F10        | VCCIB0              |  |  |

| A8         | IO18RSB0            | C13        | GND                 | F12        | IO47RSB1            |  |  |

| A9         | IO22RSB0            | C14        | IO48RSB1            | F13        | IO45RSB1            |  |  |

| A10        | IO26RSB0            | C15        | IO39RSB1            | F14        | GCC1/IO52RSB1       |  |  |

| A11        | IO29RSB0            | D1         | IO146RSB3           | F15        | GCA1/IO56RSB1       |  |  |

| A12        | GBC1/IO31RSB0       | D2         | IO144RSB3           | G1*        | VCOMPLF             |  |  |

| A13        | GBA2/IO36RSB1       | D3         | IO148RSB3           | G2         | GFB0/IO137RSB3      |  |  |

| A14        | IO41RSB1            | D4         | GND                 | G3         | GFC0/IO139RSB3      |  |  |

| A15        | NC                  | D5         | GAB0/IO02RSB0       | G4         | IO143RSB3           |  |  |

| B1         | IO151RSB3           | D6         | GAC1/IO05RSB0       | G6         | VCCIB3              |  |  |

| B2         | GAB2/IO154RSB3      | D7         | IO14RSB0            | G7         | GND                 |  |  |

| B3         | IO06RSB0            | D8         | IO19RSB0            | G8         | VCC                 |  |  |

| B4         | IO09RSB0            | D9         | GBC0/IO30RSB0       | G9         | GND                 |  |  |

| B5         | IO13RSB0            | D10        | GBB0/IO32RSB0       | G10        | GND                 |  |  |

| B6         | IO10RSB0            | D11        | GBA0/IO34RSB0       | G12        | IO50RSB1            |  |  |

| B7         | IO12RSB0            | D12        | GND                 | G13        | GCB1/IO54RSB1       |  |  |

| B8         | IO20RSB0            | D13        | GBC2/IO40RSB1       | G14        | GCC2/IO60RSB1       |  |  |

| B9         | IO23RSB0            | D14        | IO51RSB1            | G15        | GCA2/IO58RSB1       |  |  |

| B10        | IO25RSB0            | D15        | IO44RSB1            | H1*        | VCCPLF              |  |  |

| B11        | IO24RSB0            | E1         | IO142RSB3           | H2         | GFA1/IO136RSB3      |  |  |

| B12        | IO27RSB0            | E2         | IO149RSB3           | H3         | GFB1/IO138RSB3      |  |  |

| B13        | IO37RSB1            | E3         | IO153RSB3           | H4         | NC                  |  |  |

| B14        | IO46RSB1            | E4         | GAC2/IO152RSB3      | H6         | VCCIB3              |  |  |

| B15        | IO42RSB1            | E12        | IO43RSB1            | H7         | GND                 |  |  |

| C1         | IO155RSB3           | E13        | IO49RSB1            | H8         | VCC                 |  |  |

| C2         | GAA2/IO156RSB3      | E14        | GCC0/IO53RSB1       | H9         | GND                 |  |  |

| C3         | GND                 | E15        | GCB0/IO55RSB1       | H10        | VCCIB1              |  |  |

| C4         | GAA1/IO01RSB0       | F1         | IO141RSB3           | H12        | GCB2/IO59RSB1       |  |  |

| C5         | GAB1/IO03RSB0       | F2         | GFC1/IO140RSB3      | H13        | GCA0/IO57RSB1       |  |  |

Note: \*Pin numbers G1 and H1 must be connected to ground because a PLL is not supported for AGLP060-CS/G201.

### 🌜 Microsemi.

Package Pin Assignments

| CS281      |                  | CS281                       |                | CS281      |                  |  |

|------------|------------------|-----------------------------|----------------|------------|------------------|--|

| Pin Number | AGLP125 Function | Pin Number AGLP125 Function |                | Pin Number | AGLP125 Function |  |

| H8         | VCC              | K15                         | IO89RSB1       | N4         | IO182RSB3        |  |

| H9         | VCCIB0           | K16                         | GND            | N5         | IO161RSB2        |  |

| H10        | VCC              | K18                         | IO88RSB1       | N7         | GEA2/IO164RSB2   |  |

| H11        | VCCIB0           | K19                         | VCCIB1         | N8         | VCCIB2           |  |

| H12        | VCC              | L1                          | GFB2/IO187RSB3 | N9         | IO137RSB2        |  |

| H13        | VCCIB1           | L2                          | IO185RSB3      | N10        | IO135RSB2        |  |

| H15        | IO77RSB1         | L4                          | GFC2/IO186RSB3 | N11        | IO131RSB2        |  |

| H16        | GCB0/IO82RSB1    | L5                          | IO184RSB3      | N12        | VCCIB2           |  |

| H18        | GCA1/IO83RSB1    | L7                          | IO199RSB3      | N13        | VPUMP            |  |

| H19        | GCA2/IO85RSB1    | L8                          | VCCIB3         | N15        | IO117RSB2        |  |

| J1         | VCOMPLF          | L9                          | GND            | N16        | IO96RSB1         |  |

| J2         | GFA0/IO189RSB3   | L10                         | GND            | N18        | IO98RSB1         |  |

| J4         | VCCPLF           | L11                         | GND            | N19        | IO94RSB1         |  |

| J5         | GFC0/IO193RSB3   | L12                         | VCCIB1         | P1         | IO174RSB3        |  |

| J7         | GFA2/IO188RSB3   | L13                         | IO95RSB1       | P2         | GND              |  |

| J8         | VCCIB3           | L15                         | IO91RSB1       | P3         | IO176RSB3        |  |

| J9         | GND              | L16                         | NC             | P4         | IO177RSB3        |  |

| J10        | GND              | L18                         | IO90RSB1       | P5         | GEA0/IO165RSB3   |  |

| J11        | GND              | L19                         | NC             | P15        | IO111RSB2        |  |

| J12        | VCCIB1           | M1                          | IO180RSB3      | P16        | IO108RSB2        |  |

| J13        | GCC1/IO79RSB1    | M2                          | IO179RSB3      | P17        | GDC1/IO99RSB1    |  |

| J15        | GCA0/IO84RSB1    | M4                          | IO181RSB3      | P18        | GND              |  |

| J16        | GCB2/IO86RSB1    | M5                          | IO183RSB3      | P19        | IO97RSB1         |  |

| J18        | IO76RSB1         | M7                          | VCCIB3         | R1         | IO173RSB3        |  |

| J19        | IO78RSB1         | M8                          | VCC            | R2         | IO172RSB3        |  |

| K1         | VCCIB3           | M9                          | VCCIB2         | R4         | GEC1/IO170RSB3   |  |

| K2         | GFA1/IO190RSB3   | M10                         | VCC            | R5         | GEB1/IO168RSB3   |  |

| K4         | GND              | M11                         | VCCIB2         | R6         | IO154RSB2        |  |

| K5         | IO19RSB0         | M12                         | VCC            | R7         | IO149RSB2        |  |

| K7         | IO197RSB3        | M13                         | VCCIB1         | R8         | IO146RSB2        |  |

| K8         | VCC              | M15                         | IO122RSB2      | R9         | IO138RSB2        |  |

| K9         | GND              | M16                         | IO93RSB1       | R10        | IO134RSB2        |  |

| K10        | GND              | M18                         | IO92RSB1       | R11        | IO132RSB2        |  |

| K11        | GND              | M19                         | NC             | R12        | IO130RSB2        |  |

| K12        | VCC              | N1                          | IO178RSB3      | R13        | IO118RSB2        |  |

| K13        | GCC2/IO87RSB1    | N2                          | IO175RSB3      | R14        | IO112RSB2        |  |

IGLOO PLUS Low Power Flash FPGAs

| CS289      |                     | С          | S289                | C          | CS289               |  |  |

|------------|---------------------|------------|---------------------|------------|---------------------|--|--|

| Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function |  |  |

| A1         | IO03RSB0            | C4         | NC                  | E7         | IO06RSB0            |  |  |

| A2         | NC                  | C5         | VCCIB0              | E8         | IO11RSB0            |  |  |

| A3         | NC                  | C6         | IO09RSB0            | E9         | IO22RSB0            |  |  |

| A4         | GND                 | C7         | IO13RSB0            | E10        | IO26RSB0            |  |  |

| A5         | IO10RSB0            | C8         | IO15RSB0            | E11        | VCCIB0              |  |  |

| A6         | IO14RSB0            | C9         | IO21RSB0            | E12        | NC                  |  |  |

| A7         | IO16RSB0            | C10        | GND                 | E13        | IO33RSB0            |  |  |

| A8         | IO18RSB0            | C11        | IO29RSB0            | E14        | IO36RSB1            |  |  |

| A9         | GND                 | C12        | NC                  | E15        | IO38RSB1            |  |  |

| A10        | IO23RSB0            | C13        | NC                  | E16        | VCCIB1              |  |  |

| A11        | IO27RSB0            | C14        | NC                  | E17        | NC                  |  |  |

| A12        | NC                  | C15        | GND                 | F1         | IO111RSB3           |  |  |

| A13        | NC                  | C16        | IO34RSB0            | F2         | NC                  |  |  |

| A14        | GND                 | C17        | NC                  | F3         | IO116RSB3           |  |  |

| A15        | NC                  | D1         | NC                  | F4         | VCCIB3              |  |  |

| A16        | NC                  | D2         | IO119RSB3           | F5         | IO117RSB3           |  |  |

| A17        | IO30RSB0            | D3         | GND                 | F6         | NC                  |  |  |

| B1         | IO01RSB0            | D4         | IO02RSB0            | F7         | NC                  |  |  |

| B2         | GND                 | D5         | NC                  | F8         | IO08RSB0            |  |  |

| B3         | NC                  | D6         | NC                  | F9         | IO12RSB0            |  |  |

| B4         | NC                  | D7         | NC                  | F10        | NC                  |  |  |

| B5         | IO07RSB0            | D8         | GND                 | F11        | NC                  |  |  |

| B6         | NC                  | D9         | IO20RSB0            | F12        | NC                  |  |  |

| B7         | VCCIB0              | D10        | IO25RSB0            | F13        | NC                  |  |  |

| B8         | IO17RSB0            | D11        | NC                  | F14        | GND                 |  |  |

| B9         | IO19RSB0            | D12        | NC                  | F15        | NC                  |  |  |

| B10        | IO24RSB0            | D13        | GND                 | F16        | IO37RSB1            |  |  |

| B11        | IO28RSB0            | D14        | IO32RSB0            | F17        | IO41RSB1            |  |  |

| B12        | VCCIB0              | D15        | IO35RSB0            | G1         | IO110RSB3           |  |  |

| B13        | NC                  | D16        | NC                  | G2         | GND                 |  |  |

| B14        | NC                  | D17        | NC                  | G3         | IO113RSB3           |  |  |

| B15        | NC                  | E1         | VCCIB3              | G4         | NC                  |  |  |

| B16        | IO31RSB0            | E2         | IO114RSB3           | G5         | NC                  |  |  |

| B17        | GND                 | E3         | IO115RSB3           | G6         | NC                  |  |  |

| C1         | NC                  | E4         | IO118RSB3           | G7         | GND                 |  |  |

| C2         | IO00RSB0            | E5         | IO05RSB0            | G8         | GND                 |  |  |

| C3         | IO04RSB0            | E6         | NC                  | G9         | VCC                 |  |  |

| stati 👟 Microsemi.               |

|----------------------------------|

| IGLOO PLUS Low Power Flash FPGAs |

| CS289      |                  | CS289      |                  |  |

|------------|------------------|------------|------------------|--|

| Pin Number | AGLP125 Function | Pin Number | AGLP125 Function |  |

| P8         | GND              | T12        | IO124RSB2        |  |

| P9         | IO132RSB2        | T13        | IO122RSB2        |  |

| P10        | IO125RSB2        | T14        | GND              |  |

| P11        | IO126RSB2        | T15        | IO115RSB2        |  |

| P12        | IO112RSB2        | T16        | TDI              |  |

| P13        | VCCIB2           | T17        | TDO              |  |

| P14        | IO108RSB2        | U1         | FF/GEB2/IO163RS  |  |

| P15        | GDA2/IO105RSB2   |            | B2               |  |

| P16        | GDC2/IO107RSB2   | U2         | GND              |  |

| P17        | VJTAG            | U3         | IO151RSB2        |  |

| R1         | GND              | U4         | IO149RSB2        |  |

| R2         | GEA2/IO164RSB2   | U5         | IO146RSB2        |  |

| R3         | IO158RSB2        | U6         | IO142RSB2        |  |

| R4         | IO155RSB2        | U7         | GND              |  |

| R5         | IO150RSB2        | U8         | IO138RSB2        |  |

| R6         | VCCIB2           | U9         | IO136RSB2        |  |

| R7         | IO145RSB2        | U10        | IO133RSB2        |  |

| R8         | IO141RSB2        | U11        | IO129RSB2        |  |

| R9         | IO134RSB2        | U12        | GND              |  |

| R10        | IO130RSB2        | U13        | IO123RSB2        |  |

| R11        | GND              | U14        | IO120RSB2        |  |

| R12        | IO118RSB2        | U15        | IO117RSB2        |  |

| R13        | IO116RSB2        | U16        | ТСК              |  |

| R14        | IO114RSB2        | U17        | VPUMP            |  |

| R15        | IO110RSB2        |            |                  |  |

| R16        | TMS              |            |                  |  |

| R17        | TRST             |            |                  |  |

| T1         | GEA1/IO166RSB3   |            |                  |  |

| T2         | GEC2/IO162RSB2   |            |                  |  |

| Т3         | IO153RSB2        |            |                  |  |

| T4         | GND              |            |                  |  |

| T5         | IO147RSB2        |            |                  |  |

| T6         | IO143RSB2        |            |                  |  |

| T7         | IO140RSB2        |            |                  |  |

| Т8         | IO139RSB2        |            |                  |  |

| T9         | VCCIB2           |            |                  |  |

| T10        | IO131RSB2        |            |                  |  |

| 110        |                  |            |                  |  |