#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 50                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128c3-mh |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Six of the 32 registers can be used as three 16-bit address register pointers for data space addressing, enabling efficient address calculations. One of these address pointers can also be used as an address pointer for lookup tables in flash program memory.

## 7.8 Memory Timing

Read and write access to the I/O memory takes one CPU clock cycle. A write to SRAM takes one cycle, and a read from SRAM takes two cycles. EEPROM page load (write) takes one cycle, and three cycles are required for read. For burst read, new data are available every second cycle. Refer to the instruction summary for more details on instructions and instruction timing.

## 7.9 Device ID and Revision

Each device has a three-byte device ID. This ID identifies Atmel as the manufacturer of the device and the device type. A separate register contains the revision number of the device.

## 7.10 I/O Memory Protection

Some features in the device are regarded as critical for safety in some applications. Due to this, it is possible to lock the I/O register related to the clock system, the event system, and the advanced waveform extensions. As long as the lock is enabled, all related I/O registers are locked and they can not be written from the application software. The lock registers themselves are protected by the configuration change protection mechanism.

### 7.11 Flash and EEPROM Page Size

The flash program memory and EEPROM data memory are organized in pages. The pages are word accessible for the flash and byte accessible for the EEPROM.

Table 7-2 on page 16 shows the Flash Program Memory organization and Program Counter (PC) size. Flash write and erase operations are performed on one page at a time, while reading the Flash is done one byte at a time. For Flash access the Z-pointer (Z[m:n]) is used for addressing. The most significant bits in the address (FPAGE) give the page number and the least significant address bits (FWORD) give the word in the page.

| Devices      | PC size | Flash size | Page size | FWORD  | FPAGE   | Application |              | FPAGE Application |              | I | Boot |

|--------------|---------|------------|-----------|--------|---------|-------------|--------------|-------------------|--------------|---|------|

|              | bits    | bytes      | words     |        |         | Size        | No. of pages | Size              | No. of pages |   |      |

| ATxmega32C3  | 16      | 32K + 4K   | 128       | Z[7:1] | Z[16:8] | 32K         | 128          | 4K                | 16           |   |      |

| ATxmega64C3  | 16      | 64K + 4K   | 128       | Z[7:1] | Z[16:8] | 64K         | 256          | 4K                | 16           |   |      |

| ATxmega128C3 | 17      | 128K + 8K  | 256       | Z[8:1] | Z[17:9] | 128K        | 256          | 8K                | 16           |   |      |

| ATxmega192C3 | 17      | 192K + 8K  | 256       | Z[8:1] | Z[17:9] | 192K        | 384          | 8K                | 16           |   |      |

| ATxmega256C3 | 18      | 256K + 8K  | 256       | Z[8:1] | Z[18:9] | 256K        | 512          | 8K                | 16           |   |      |

#### Table 7-2. Number of Words and Pages in the Flash

Table 7-3 on page 17 shows EEPROM memory organization. EEEPROM write and erase operations can be performed one page or one byte at a time, while reading the EEPROM is done one byte at a time. For EEPROM access the NVM address register (ADDR[m:n]) is used for addressing. The most significant bits in the address (E2PAGE) give the page number and the least significant address bits (E2BYTE) give the byte in the page.

### 11.4.2 Brownout Detection

The on-chip brownout detection (BOD) circuit monitors the  $V_{CC}$  level during operation by comparing it to a fixed, programmable level that is selected by the BODLEVEL fuses. If disabled, BOD is forced on at the lowest level during chip erase and when the PDI is enabled.

### 11.4.3 External Reset

The external reset circuit is connected to the external  $\overrightarrow{\text{RESET}}$  pin. The external reset will trigger when the  $\overrightarrow{\text{RESET}}$  pin is driven below the  $\overrightarrow{\text{RESET}}$  pin threshold voltage,  $V_{\text{RST}}$ , for longer than the minimum pulse period,  $t_{\text{EXT}}$ . The reset will be held as long as the pin is kept low. The  $\overrightarrow{\text{RESET}}$  pin includes an internal pull-up resistor.

### 11.4.4 Watchdog Reset

The watchdog timer (WDT) is a system function for monitoring correct program operation. If the WDT is not reset from the software within a programmable timeout period, a watchdog reset will be given. The watchdog reset is active for one to two clock cycles of the 2MHz internal oscillator. For more details see "WDT – Watchdog Timer" on page 26.

### 11.4.5 Software Reset

The software reset makes it possible to issue a system reset from software by writing to the software reset bit in the reset control register. The reset will be issued within two CPU clock cycles after writing the bit. It is not possible to execute any instruction from when a software reset is requested until it is issued.

### 11.4.6 Program and Debug Interface Reset

The program and debug interface reset contains a separate reset source that is used to reset the device during external programming and debugging. This reset source is accessible only from external debuggers and programmers.

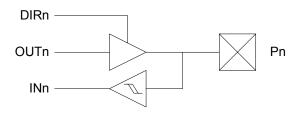

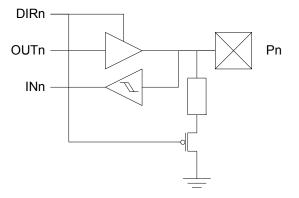

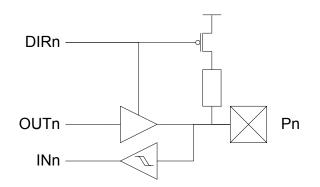

## 14.3 Output Driver

All port pins (Pn) have programmable output configuration.

### 14.3.1 Push-pull

### Figure 14-1. I/O Configuration - Totem-pole

### 14.3.2 Pull-down

Figure 14-2. I/O Configuration - Totem-pole with Pull-down (on input)

### 14.3.3 Pull-up

Figure 14-3. I/O Configuration - Totem-pole with Pull-up (on input)

## 18. Hi-Res – High Resolution Extension

## 18.1 Features

- Increases waveform generator resolution up to 8x (three bits)

- Supports frequency, single-slope PWM, and dual-slope PWM generation

- Supports the AWeX when this is used for the same timer/counter

## 18.2 Overview

The high-resolution (hi-res) extension can be used to increase the resolution of the waveform generation output from a timer/counter by four or eight. It can be used for a timer/counter doing frequency, single-slope PWM, or dual-slope PWM generation. It can also be used with the AWeX if this is used for the same timer/counter.

The hi-res extension uses the peripheral 4x clock ( $Clk_{PER4}$ ). The system clock prescalers must be configured so the peripheral 4x clock frequency is four times higher than the peripheral and CPU clock frequency when the hi-res extension is enabled.

There is one hi-res extensions that can be enabled for timer/counters pair on PORTC. The notation of this is HIRESC.

## 24. IRCOM – IR Communication Module

## 24.1 Features

- Pulse modulation/demodulation for infrared communication

- IrDA compatible for baud rates up to 115.2Kbps

- Selectable pulse modulation scheme

- 3/16 of the baud rate period

- Fixed pulse period, 8-bit programmable

- Pulse modulation disabled

- Built-in filtering

- Can be connected to and used by any USART

## 24.2 Overview

Atmel AVR XMEGA devices contain an infrared communication module (IRCOM) that is IrDA compatible for baud rates up to 115.2Kbps. It can be connected to any USART to enable infrared pulse encoding/decoding for that USART.

## 25. CRC – Cyclic Redundancy Check Generator

## 25.1 Features

- Cyclic redundancy check (CRC) generation and checking for

- Communication data

- Program or data in flash memory

- Data in SRAM and I/O memory space

- Integrated with flash memory and CPU

- Automatic CRC of the complete or a selectable range of the flash memory

- CPU can load data to the CRC generator through the I/O interface

- CRC polynomial software selectable to

- CRC-16 (CRC-CCITT)

- CRC-32 (IEEE 802.3)

- Zero remainder detection

## 25.2 Overview

A cyclic redundancy check (CRC) is an error detection technique test algorithm used to find accidental errors in data, and it is commonly used to determine the correctness of a data transmission, and data present in the data and program memories. A CRC takes a data stream or a block of data as input and generates a 16- or 32-bit output that can be appended to the data and used as a checksum. When the same data are later received or read, the device or application repeats the calculation. If the new CRC result does not match the one calculated earlier, the block contains a data error. The application will then detect this and may take a corrective action, such as requesting the data to be sent again or simply not using the incorrect data.

Typically, an n-bit CRC applied to a data block of arbitrary length will detect any single error burst not longer than n bits (any single alteration that spans no more than n bits of the data), and will detect the fraction 1-2<sup>-n</sup> of all longer error bursts. The CRC module in Atmel AVR XMEGA devices supports two commonly used CRC polynomials; CRC-16 (CRC-CCITT) and CRC-32 (IEEE 802.3).

### • CRC-16:

Polynomial:  $x^{16}+x^{12}+x^{5}+1$

Hex value: 0x1021

• CRC-32:

Polynomial:  $x^{32}+x^{26}+x^{23}+x^{22}+x^{16}+x^{12}+x^{11}+x^{10}+x^8+x^7+x^5+x^4+x^2+x+1$

Hex value: 0x04C11DB7

### 33.1.13.5 Internal Phase Locked Loop (PLL) Characteristics

### Table 33-23. Internal PLL Characteristics

| Symbol           | Parameter                       | Condition                                                 | Min. | Тур. | Max. | Units |

|------------------|---------------------------------|-----------------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>  | Input frequency                 | Output frequency must be within $\mathbf{f}_{\text{OUT}}$ | 0.4  |      | 64   |       |

| f <sub>оит</sub> | Output frequency <sup>(1)</sup> | V <sub>CC</sub> = 1.6 - 1.8V                              | 20   |      | 48   | MHz   |

|                  |                                 | V <sub>CC</sub> = 2.7 - 3.6V                              | 20   |      | 128  |       |

|                  | Start-up time                   |                                                           |      | 25   |      |       |

|                  | Re-lock time                    |                                                           |      | 25   |      | μs    |

Note: 1. The maximum output frequency vs. supply voltage is linear between 1.8V and 2.7V, and can never be higher than four times the maximum CPU frequency.

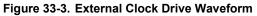

### 33.1.13.6 External Clock Characteristics

### Table 33-24. External Clock used as System Clock without Prescaling

| Symbol            | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units |

|-------------------|---------------------------------------------------|------------------------------|------|------|------|-------|

| 1 /ł              | Clock Frequency <sup>(1)</sup>                    | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 12   | MHz   |

| 1/t <sub>CK</sub> | Clock frequency V                                 | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 32   |       |

| +                 | Clock Period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 83.3 |      |      |       |

| t <sub>ск</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 31.5 |      |      |       |

| +                 | Clock High Time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      |       |

| t <sub>сн</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      |       |

| +                 | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      | ne    |

| t <sub>CL</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | ns    |

| +                 | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   | -     |

| t <sub>CR</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    | _     |

| +                 |                                                   | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |       |

| t <sub>CF</sub>   | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    |       |

| $\Delta t_{CK}$   | Change in period from one clock cycle to the next |                              |      |      | 10   | %     |

Note: 1. The maximum frequency vs. supply voltage is linear between 1.6V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

### Table 33-92. Current Consumption for Modules and Peripherals

| Symbol          | Parameter                 | Condition <sup>(1)</sup>                |                                  | Min. | Тур. | Max. | Units |  |  |  |

|-----------------|---------------------------|-----------------------------------------|----------------------------------|------|------|------|-------|--|--|--|

|                 | ULP oscillator            |                                         |                                  |      | 0.9  |      |       |  |  |  |

|                 | 32.768kHz int. oscillator |                                         |                                  |      | 25   |      |       |  |  |  |

|                 | 2MHz int. oscillator      |                                         |                                  |      | 78   |      |       |  |  |  |

|                 |                           | DFLL enabled with                       | 32.768kHz int. osc. as reference |      | 110  |      | -     |  |  |  |

|                 | 32MHz int. oscillator     |                                         |                                  |      | 250  |      |       |  |  |  |

|                 |                           | DFLL enabled with                       | 32.768kHz int. osc. as reference |      | 440  |      |       |  |  |  |

|                 | PLL                       | 20x multiplication f 32MHz int. osc. Dl |                                  |      | 310  |      | μA    |  |  |  |

|                 | Watchdog timer            |                                         |                                  |      | 1.0  |      |       |  |  |  |

|                 | BOD                       | Continuous mode                         |                                  | 132  |      |      |       |  |  |  |

|                 |                           | Sampled mode, ind                       |                                  | 1.4  |      |      |       |  |  |  |

| I <sub>CC</sub> | Internal 1.0V reference   |                                         |                                  | 185  |      |      |       |  |  |  |

|                 | Temperature sensor        |                                         |                                  |      | 182  |      |       |  |  |  |

|                 |                           | 16ksps                                  |                                  |      | 1.12 |      | mA    |  |  |  |

|                 |                           |                                         | CURRLIMIT = LOW                  |      | 1.01 |      |       |  |  |  |

|                 |                           | V <sub>REF</sub> = Ext. ref.            | CURRLIMIT = MEDIUM               |      | 0.9  |      |       |  |  |  |

|                 | ADC                       |                                         | CURRLIMIT = HIGH                 |      | 0.8  |      |       |  |  |  |

|                 |                           | 75ksps<br>V <sub>REF</sub> = Ext. ref.  | CURRLIMIT = LOW                  |      | 1.7  |      |       |  |  |  |

|                 |                           | 300ksps<br>V <sub>REF</sub> = Ext. ref. |                                  |      | 3.1  |      |       |  |  |  |

|                 | USART                     | Rx and Tx enabled                       | 1, 9600 BAUD                     |      | 9.5  |      | μA    |  |  |  |

|                 | Flash memory and EEPRO    | M programming                           |                                  |      | 10   |      | mA    |  |  |  |

Note: 1. All parameters measured as the difference in current consumption between module enabled and disabled. All data at V<sub>CC</sub> = 3.0V, Clk<sub>SYS</sub> = 1MHz external clock without prescaling, T = 25°C unless other conditions are given.

| Symbol             | Parameter                          | Condition | Min. | Тур. | Max. | Units |

|--------------------|------------------------------------|-----------|------|------|------|-------|

| C <sub>XTAL1</sub> | Parasitic capacitance<br>XTAL1 pin |           |      | 5.9  |      |       |

| C <sub>XTAL2</sub> | Parasitic capacitance<br>XTAL2 pin |           |      | 8.3  |      | pF    |

| C <sub>LOAD</sub>  | Parasitic capacitance load         |           |      | 3.5  |      |       |

Note: 1. Numbers for negative impedance are not tested in production but guaranteed from design and characterization.

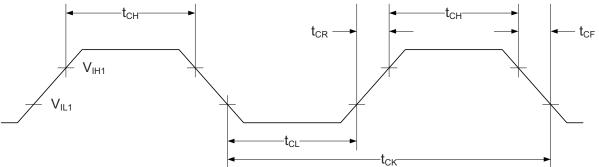

### 33.4.13.8 External 32.768kHz Crystal Oscillator and TOSC Characteristics

### Table 33-114. External 32.768 kHz Crystal Oscillator and TOSC Characteristics

| Symbol             | Parameter                          | Condition                                         | Min. | Тур. | Max. | Units |

|--------------------|------------------------------------|---------------------------------------------------|------|------|------|-------|

|                    | Recommended crystal                | Crystal load capacitance 6.5pF                    |      |      | 60   |       |

| ESR/R1             | equivalent series                  | Crystal load capacitance 9.0pF                    |      |      | 35   | kΩ    |

| resistance (E      | resistance (ESR)                   | Crystal load capacitance 12pF                     |      |      | 28   | -     |

| C <sub>TOSC1</sub> | Parasitic capacitance<br>TOSC1 pin |                                                   |      | 3.5  |      | pF    |

| C <sub>TOSC2</sub> | Parasitic capacitance<br>TOSC2 pin |                                                   |      | 3.5  |      | pr    |

|                    | Recommended safety factor          | Capacitance load matched to crystal specification | 3    |      |      |       |

Note:

See Figure 33-25 for definition.

### Figure 33-25.TOSC Input Capacitance

The parasitic capacitance between the TOSC pins is  $C_{L1} + C_{L2}$  in series as seen from the crystal when oscillating without external capacitors.

### Table 33-127. Gain Stage Characteristics

| Symbol              | Parameter                       | Condition               | Min. | Тур. | Max.                   | Units                        |

|---------------------|---------------------------------|-------------------------|------|------|------------------------|------------------------------|

| R <sub>in</sub>     | Input resistance                | Switched in normal mode |      | 4.0  |                        | kΩ                           |

| C <sub>sample</sub> | Input capacitance               | Switched in normal mode |      | 4.4  |                        | pF                           |

|                     | Signal range                    | Gain stage output       | 0    |      | AV <sub>CC</sub> - 0.6 | V                            |

|                     | Propagation delay               | ADC conversion rate     | 1/2  | 1    | 3                      | Clk <sub>ADC</sub><br>cycles |

|                     | Clock frequency                 | Same as ADC             | 100  |      | 1800                   | kHz                          |

|                     |                                 | 0.5x gain, normal mode  |      | -1   |                        |                              |

|                     |                                 | 1x gain, normal mode    |      | -1   |                        | %                            |

|                     | Gain error                      | 8x gain, normal mode    |      | -1   |                        | /0                           |

|                     |                                 | 64x gain, normal mode   |      | 5    |                        |                              |

|                     | Offset error,<br>input referred | 0.5x gain, normal mode  |      | 10   |                        |                              |

|                     |                                 | 1x gain, normal mode    |      | 5    |                        | m) (                         |

|                     |                                 | 8x gain, normal mode    |      | -20  |                        | mV                           |

|                     |                                 | 64x gain, normal mode   |      | -126 |                        |                              |

## 33.5.7 Analog Comparator Characteristics

### Table 33-128. Analog Comparator Characteristics

| Symbol             | Parameter                                 | Condition                       | Min. | Тур. | Max.             | Units |

|--------------------|-------------------------------------------|---------------------------------|------|------|------------------|-------|

| V <sub>off</sub>   | Input offset voltage                      |                                 |      | 10   |                  | mV    |

| I <sub>lk</sub>    | Input leakage current                     |                                 |      | <10  | 50               | nA    |

|                    | Input voltage range                       |                                 | -0.1 |      | AV <sub>CC</sub> | V     |

|                    | AC startup time                           |                                 |      | 50   |                  | μs    |

| V <sub>hys1</sub>  | Hysteresis, none                          | V <sub>CC</sub> = 1.6V - 3.6V   |      | 0    |                  |       |

| V <sub>hys2</sub>  | Hysteresis, small                         | V <sub>CC</sub> = 1.6V - 3.6V   |      | 15   |                  | mV    |

| V <sub>hys3</sub>  | Hysteresis, large                         | V <sub>CC</sub> = 1.6V - 3.6V   |      | 30   |                  | -     |

| +                  | Propagation delay                         | V <sub>CC</sub> = 3.0V, T= 85°C |      | 20   | 40               | 20    |

| t <sub>delay</sub> |                                           | V <sub>CC</sub> = 3.0V          |      | 17   |                  | ns    |

|                    | 64-level voltage scaler                   | Integral non-linearity (INL)    |      | 0.3  | 0.5              | lsb   |

|                    | Current source accuracy after calibration |                                 |      | 5    |                  | %     |

|                    | Current source calibration range          | Single mode                     | 4    |      | 6                | μA    |

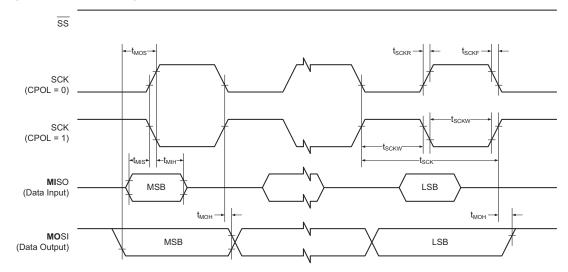

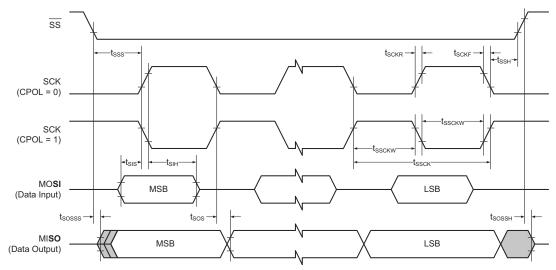

### 33.5.14 SPI Characteristics

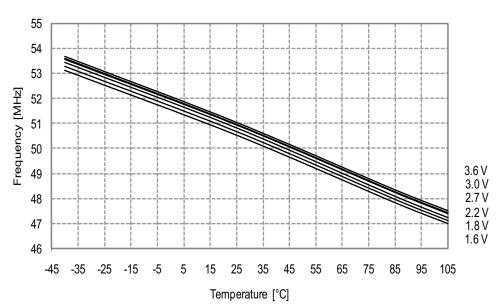

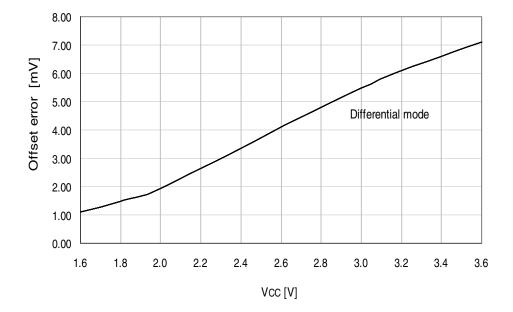

### 34.1.8.5 32MHz Internal Oscillator Calibrated to 48MHz

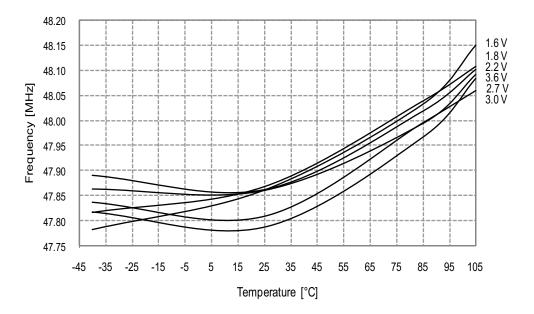

Figure 34-67. 48MHz Internal Oscillator Frequency vs. Temperature DFLL disabled

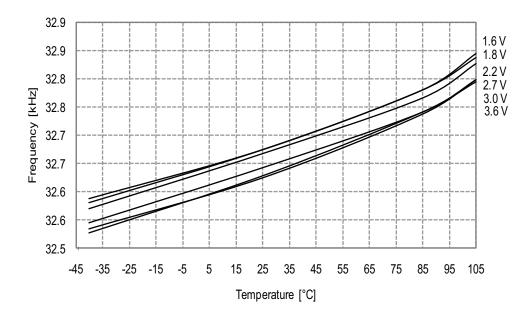

Figure 34-126. 32.768kHz Internal Oscillator Frequency vs. Temperature

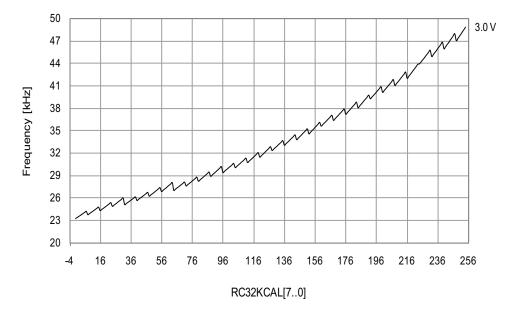

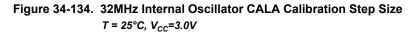

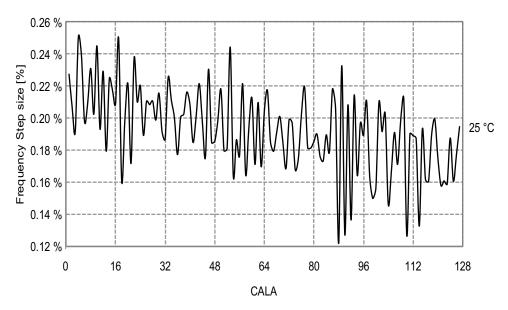

Figure 34-135. 32MHz Internal Oscillator CALA Calibration Step Size  $T = 85^{\circ}C$ ,  $V_{cc}=3.0V$

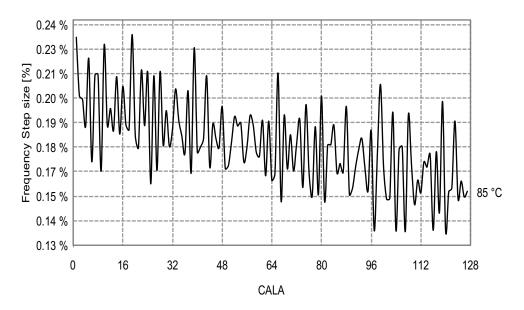

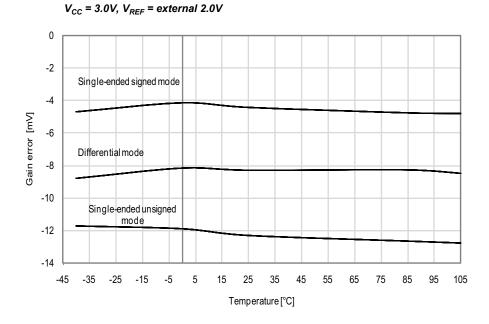

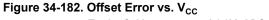

Figure 34-181. Gain Error vs. Temperature

$T = 25 \,$ °C,  $V_{REF} = external 1.0V$ , ADC sample rate = 300ksps

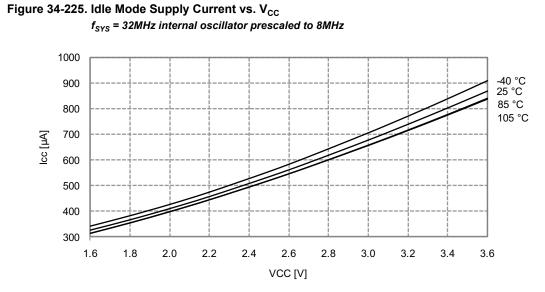

Figure 34-226. Idle Mode Current vs.  $V_{CC}$  $f_{SYS}$  = 32MHz internal oscillator

## 34.4.4 Analog Comparator Characteristics

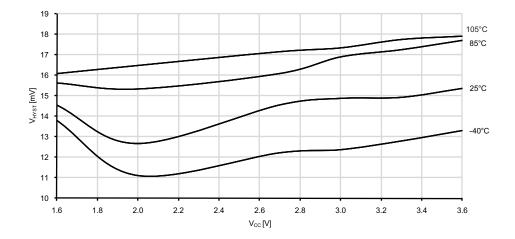

Figure 34-253. Analog Comparator Hysteresis vs. V<sub>CC</sub> Small hysteresis

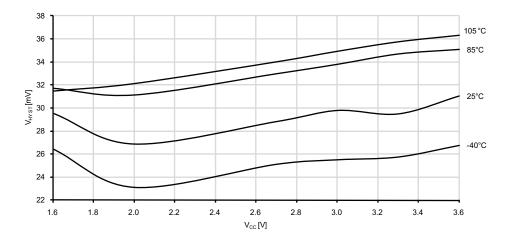

Figure 34-254. Analog Comparator Hysteresis vs. V<sub>CC</sub> Large hysteresis

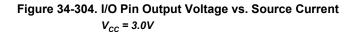

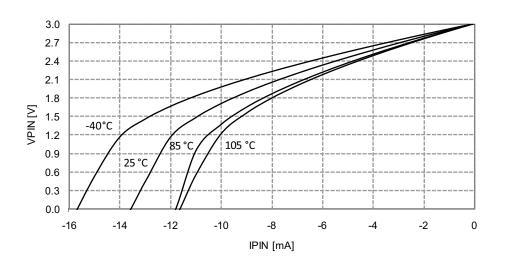

### 34.5.2.2 Output Voltage vs. Sink/Source Current

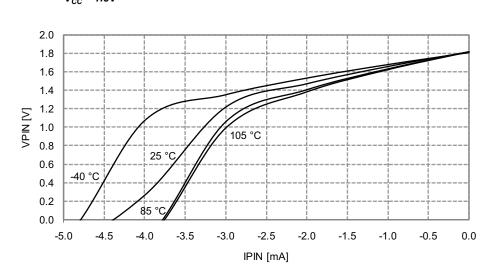

Figure 34-303. I/O Pin Output Voltage vs. Source Current  $V_{CC} = 1.8V$

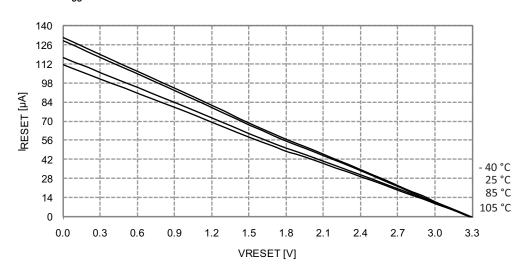

Figure 34-333. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC} = 3.3V$

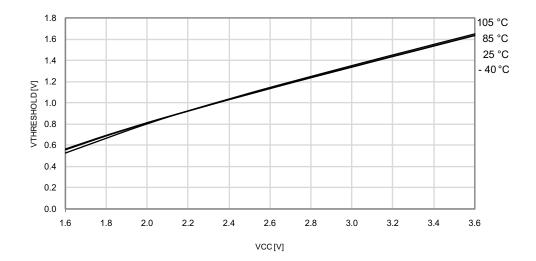

Figure 34-334. Reset Pin Input Threshold Voltage vs.  $V_{CC}$  $V_{IH}$  - Reset pin read as "1"