#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | EBI/EMI, I²C, SIO, UART/USART                                                   |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 8K x 8                                                                          |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-BQFP                                                                        |

| Supplier Device Package    | 100-QFP (14x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f36506nfa-u0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

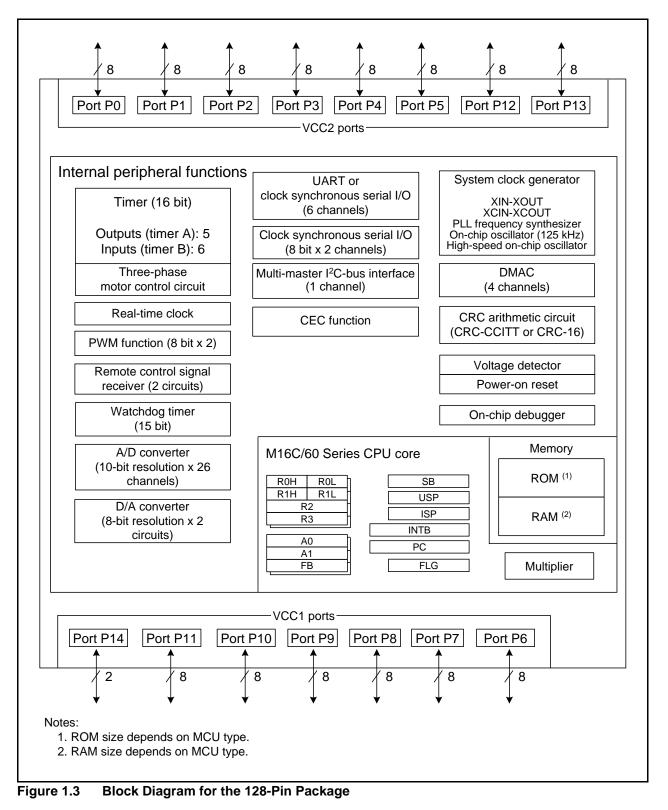

## 1.4 Block Diagram

Figure 1.3 to Figure 1.4 show block diagrams.

| Table 1    | .8 Pi   | n Name    | s for the | 128-Pin P | ackage (2/3)            |                                 |                      |

|------------|---------|-----------|-----------|-----------|-------------------------|---------------------------------|----------------------|

|            | Control |           |           | I/O F     | Pin for Peripheral Func |                                 |                      |

| Pin No.    | Pin     | Port      | Interrupt | Timer     | Serial interface        | A/D converter,<br>D/A converter | Bus Control Pin      |

| 51         |         | P5_6      |           |           |                         |                                 | ALE                  |

| 52         |         | P5_5      |           |           |                         |                                 | HOLD                 |

| 53         |         | P5_4      |           |           |                         |                                 | HLDA                 |

| 54         |         | P13_3     |           |           |                         |                                 |                      |

| 55         |         | P13_2     |           |           |                         |                                 |                      |

| 56         |         | P13_1     |           |           |                         |                                 |                      |

| 57         |         | P13_0     |           |           |                         |                                 |                      |

| 58         |         | P5_3      |           |           |                         |                                 | BCLK                 |

| 59         |         | P5_2      |           |           |                         |                                 | RD                   |

| 50         |         | P5_1      |           |           |                         |                                 | WRH/BHE              |

| 61         |         | P5_0      |           |           |                         |                                 | WRL/WR               |

| 62         |         | P12_7     |           |           |                         |                                 |                      |

| 63         |         | <br>P12_6 | t         | 1         |                         |                                 | 1                    |

| 64         |         | P12_5     |           |           |                         |                                 |                      |

| 65         |         | <br>P4_7  | t         | PWM1      | TXD7/SDA7               |                                 | CS3                  |

| 6          |         | P4_6      |           | PWM0      | RXD7/SCL7               |                                 | CS2                  |

| 67         |         | P4_5      |           |           | CLK7                    |                                 | CS1                  |

| 68         |         | P4_4      |           |           | CTS7/RTS7               |                                 | CS0                  |

| 69         |         | P4_3      |           |           |                         |                                 | A19                  |

| 0          |         | P4_2      |           |           |                         |                                 | A18                  |

| 71         |         | P4_1      |           |           |                         |                                 | A17                  |

| 2          |         | P4_0      |           |           |                         |                                 | A16                  |

| 73         |         | P3_7      |           |           |                         |                                 | A15                  |

| 74         |         | P3_6      |           |           |                         |                                 | A14                  |

| 75         |         | P3_5      |           |           |                         |                                 | A13                  |

| 76         |         | P3_4      |           |           |                         |                                 | A12                  |

| 77         |         | P3_3      |           |           |                         |                                 | A11                  |

| 78         |         | P3_2      |           |           |                         |                                 | A10                  |

| <b>'</b> 9 |         | P3_1      |           |           |                         |                                 | A9                   |

| 30         |         | P12_4     |           |           |                         |                                 |                      |

| 31         |         | P12_3     |           |           |                         |                                 |                      |

| 32         |         | P12_2     |           |           |                         |                                 |                      |

| 33         |         | P12_1     |           |           |                         |                                 |                      |

| 34         |         | P12_0     |           |           |                         |                                 |                      |

| 35         | VCC2    |           |           |           |                         |                                 |                      |

| 36         |         | P3_0      |           |           |                         |                                 | A8, [A8/D7]          |

| 37         | VSS     |           |           |           |                         |                                 |                      |

| 38         |         | P2_7      |           |           |                         | AN2_7                           | A7, [A7/D7], [A7/D6] |

| 9          |         | P2_6      |           |           |                         | AN2_6                           | A6, [A6/D6], [A6/D5] |

| 90         |         | P2_5      | INT7      |           |                         | AN2_5                           | A5, [A5/D5], [A5/D4] |

| )1         |         | P2_4      | INT6      |           |                         | AN2_4                           | A4[A4/D4], [A4/D3]   |

| )2         |         | P2_3      |           |           |                         | AN2_3                           | A3, [A3/D3], [A3/D2] |

| )3         |         | P2_2      |           |           |                         | AN2_2                           | A2, [A2/D2], [A2/D1] |

| 94         |         | P2_1      |           |           |                         | AN2_1                           | A1, [A1/D1], [A1/D0] |

| 95         |         | P2_0      |           |           |                         | AN2_0                           | A0, [A0/D0], A0      |

| 96         |         | P1_7      | INT5      | IDU       |                         |                                 | D15                  |

| 97         |         | P1_6      | INT4      | IDW       |                         |                                 | D14                  |

| 8          |         | P1_5      | ĪNT3      | IDV       |                         |                                 | D13                  |

| 99         |         | P1_4      |           |           |                         |                                 | D12                  |

| 100        |         | D1 2      | 1         | 1         |                         |                                 | D11                  |

Table 1.8 Pin Names for the 128-Pin Package (2/3)

P1\_3

100

TXD6/SDA6

D11

| Pin | Control |       |           | I/O F | Pin for Peripheral Fund |                                 |                 |

|-----|---------|-------|-----------|-------|-------------------------|---------------------------------|-----------------|

| No. | Pin     | Port  | Interrupt | Timer | Serial interface        | A/D converter,<br>D/A converter | Bus Control Pin |

| 101 |         | P1_2  |           |       | RXD6/SCL6               |                                 | D10             |

| 102 |         | P1_1  |           |       | CLK6                    |                                 | D9              |

| 103 |         | P1_0  |           |       | CTS6/RTS6               |                                 | D8              |

| 104 |         | P0_7  |           |       |                         | AN0_7                           | D7              |

| 105 |         | P0_6  |           |       |                         | AN0_6                           | D6              |

| 106 |         | P0_5  |           |       |                         | AN0_5                           | D5              |

| 107 |         | P0_4  |           |       |                         | AN0_4                           | D4              |

| 108 |         | P0_3  |           |       |                         | AN0_3                           | D3              |

| 109 |         | P0_2  |           |       |                         | AN0_2                           | D2              |

| 110 |         | P0_1  |           |       |                         | AN0_1                           | D1              |

| 111 |         | P0_0  |           |       |                         | AN0_0                           | D0              |

| 112 |         | P11_7 |           |       |                         |                                 |                 |

| 113 |         | P11_6 |           |       |                         |                                 |                 |

| 114 |         | P11_5 |           |       |                         |                                 |                 |

| 115 |         | P11_4 |           |       |                         |                                 |                 |

| 116 |         | P11_3 |           |       |                         |                                 |                 |

| 117 |         | P11_2 |           |       |                         |                                 |                 |

| 118 |         | P11_1 |           |       |                         |                                 |                 |

| 119 |         | P11_0 |           |       |                         |                                 |                 |

| 120 |         | P10_7 | KI3       |       |                         | AN7                             |                 |

| 121 |         | P10_6 | KI2       |       |                         | AN6                             |                 |

| 122 |         | P10_5 | KI1       |       |                         | AN5                             |                 |

| 123 |         | P10_4 | KI0       |       |                         | AN4                             |                 |

| 124 |         | P10_3 |           |       |                         | AN3                             |                 |

| 125 |         | P10_2 |           |       |                         | AN2                             |                 |

| 126 |         | P10_1 |           |       |                         | AN1                             |                 |

| 127 | AVSS    |       |           |       |                         |                                 |                 |

| 128 |         | P10_0 |           |       |                         | AN0                             |                 |

Table 1.9

Pin Names for the 128-Pin Package (3/3)

| Pin      | No.      |                |              |           | I/O P | in for Peripheral Fund | ction                           |                                              |

|----------|----------|----------------|--------------|-----------|-------|------------------------|---------------------------------|----------------------------------------------|

| FA       | FB       | Control<br>Pin | Port         | Interrupt |       | Serial interface       | A/D converter,<br>D/A converter | Bus Control Pin                              |

| 51       | 49       |                | P4_3         |           |       |                        |                                 | A19                                          |

| 52       | 50       |                | P4_2         |           |       |                        |                                 | A18                                          |

| 53       | 51       |                | P4_1         |           |       |                        |                                 | A17                                          |

| 54       | 52       |                | <br>P4_0     |           |       |                        |                                 | A16                                          |

| 55       | 53       |                | P3_7         |           |       |                        |                                 | A15                                          |

| 56       | 54       |                | P3_6         |           |       |                        |                                 | A14                                          |

| 57       | 55       |                | P3_5         |           |       |                        |                                 | A13                                          |

| 58       | 56       |                | P3_4         |           |       |                        |                                 | A12                                          |

| 59       | 57       |                | P3_3         |           |       |                        |                                 | A11                                          |

| 60       | 58       |                | P3_2         |           |       |                        |                                 | A10                                          |

| 61       | 59       |                | P3_1         |           |       |                        |                                 | A9                                           |

| 62       | 60       | VCC2           |              |           |       |                        |                                 |                                              |

| 63       | 61       | 1002           | P3_0         |           |       |                        |                                 | A8, [A8/D7]                                  |

| 64       | 62       | VSS            |              |           |       |                        |                                 |                                              |

| 65       | 63       |                | P2_7         |           |       |                        | AN2_7                           | A7, [A7/D7], [A7/D6]                         |

| 66<br>66 | 64       |                | P2_6         |           |       |                        | AN2_6                           | A6, [A6/D6], [A6/D5]                         |

| 67       | 65       |                | P2_0<br>P2_5 | INT7      |       |                        | AN2_5                           | A5, [A5/D5], [A5/D4]                         |

| 68       | 66       |                | P2_3         | INT6      |       |                        | AN2_3                           | A4, [A4/D4], [A4/D3]                         |

| 69       | 67       |                | P2_4<br>P2_3 |           |       |                        | AN2_3                           | A3, [A3/D3], [A3/D2]                         |

| 70       | 68       |                | P2_3         |           |       |                        | AN2_3                           | A3, [A3/D3], [A3/D2]<br>A2, [A2/D2], [A2/D1] |

| 71       | 69       |                | P2_2<br>P2_1 |           |       |                        | AN2_2<br>AN2_1                  | A2, [A2/D2], [A2/D1]<br>A1, [A1/D1], [A1/D0] |

| 72       |          |                |              |           |       |                        |                                 |                                              |

| 73       | 70<br>71 |                | P2_0         | INT5      | IDU   |                        | AN2_0                           | A0, [A0/D0], A0<br>D15                       |

|          | 71       |                | P1_7         |           |       |                        |                                 |                                              |

| 74       |          |                | P1_6         | INT4      | IDW   |                        |                                 | D14                                          |

| 75       | 73       |                | P1_5         | INT3      | IDV   |                        |                                 | D13                                          |

| 76       | 74       |                | P1_4         |           |       |                        |                                 | D12                                          |

| 77       | 75       |                | P1_3         |           |       | TXD6/SDA6              |                                 | D11                                          |

| 78       | 76       |                | P1_2         |           |       | RXD6/SCL6              |                                 | D10                                          |

| 79       | 77       |                | P1_1         |           |       | CLK6                   |                                 | D9                                           |

| 80       | 78       |                | P1_0         |           |       | CTS6/RTS6              |                                 | D8                                           |

| 81       | 79       |                | P0_7         |           |       |                        | AN0_7                           | D7                                           |

| 82       | 80       |                | P0_6         |           |       |                        | AN0_6                           | D6                                           |

| 83       | 81       |                | P0_5         |           |       |                        | AN0_5                           | D5                                           |

| 84       | 82       |                | P0_4         |           |       |                        | AN0_4                           | D4                                           |

| 85       | 83       |                | P0_3         |           |       |                        | AN0_3                           | D3                                           |

| 86       | 84       |                | P0_2         |           |       |                        | AN0_2                           | D2                                           |

| 87       | 85       |                | P0_1         |           |       |                        | AN0_1                           | D1                                           |

| 88       | 86       |                | P0_0         |           |       |                        | AN0_0                           | D0                                           |

| 89       | 87       |                | P10_7        |           |       |                        | AN7                             |                                              |

| 90       | 88       |                | P10_6        |           |       |                        | AN6                             |                                              |

| 91       | 89       |                | P10_5        |           |       |                        | AN5                             |                                              |

| 92       | 90       |                | P10_4        | KI0       |       |                        | AN4                             |                                              |

| 93       | 91       |                | P10_3        |           |       |                        | AN3                             |                                              |

| 94       | 92       |                | P10_2        |           |       |                        | AN2                             |                                              |

| 95       | 93       |                | P10_1        |           |       |                        | AN1                             |                                              |

| 96       | 94       | AVSS           |              |           |       |                        |                                 |                                              |

| 97       | 95       |                | P10_0        |           |       |                        | AN0                             |                                              |

| 98       | 96       | VREF           |              |           |       |                        |                                 |                                              |

| 99       | 97       | AVCC           |              |           |       |                        |                                 |                                              |

| 100      | 98       |                | P9_7         |           |       | SIN4                   | ADTRG                           |                                              |

Table 1.11

Pin Names for the 100-Pin Package (2/2)

| Signal Name                      | Pin Name                                                                                                                         | I/O | Power Supply | Description                                                                                                                                                                                                                               |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UART0 to                         | SDA0 to SDA2,<br>SDA5                                                                                                            | I/O | VCC1         | Serial data I/O.                                                                                                                                                                                                                          |

| UART2,<br>UART5 to               | SDA6, SDA7                                                                                                                       | I/O | VCC2         |                                                                                                                                                                                                                                           |

| UART7<br>I <sup>2</sup> C mode   | SCL0 to SCL2,<br>SCL5                                                                                                            | I/O | VCC1         | Transmit/receive clock I/O.                                                                                                                                                                                                               |

|                                  | SCL6, SCL7                                                                                                                       | I/O | VCC2         |                                                                                                                                                                                                                                           |

|                                  | CLK3, CLK4                                                                                                                       | I/O | VCC1         | Transmit/receive clock I/O.                                                                                                                                                                                                               |

| Serial interface<br>SI/O3, SI/O4 | SIN3, SIN4                                                                                                                       | I   | VCC1         | Serial data input.                                                                                                                                                                                                                        |

|                                  | SOUT3, SOUT4                                                                                                                     | 0   | VCC1         | Serial data output.                                                                                                                                                                                                                       |

| Multi-master I <sup>2</sup> C-   | SDAMM                                                                                                                            | I/O | VCC1         | Serial data I/O (N-channel open drain output).                                                                                                                                                                                            |

| bus interface                    | SCLMM                                                                                                                            | I/O | VCC1         | Transmit/receive clock I/O (N-channel open drain output).                                                                                                                                                                                 |

| CEC I/O                          | CEC                                                                                                                              | I/O | VCC1         | CEC I/O (N-channel open drain output).                                                                                                                                                                                                    |

| Reference<br>voltage input       | VREF                                                                                                                             | I   | VCC1         | Reference voltage input for the A/D and D/A converters.                                                                                                                                                                                   |

| A/D converter                    | AN0 to AN7                                                                                                                       | Ι   | VCC1         |                                                                                                                                                                                                                                           |

|                                  | AN0_0 to AN0_7<br>AN2_0 to AN2_7                                                                                                 | I   | VCC2         | Analog input.                                                                                                                                                                                                                             |

|                                  | ADTRG                                                                                                                            | Ι   | VCC1         | External trigger input.                                                                                                                                                                                                                   |

|                                  | ANEX0, ANEX1                                                                                                                     | I   | VCC1         | Extended analog input.                                                                                                                                                                                                                    |

| D/A converter                    | DA0, DA1                                                                                                                         | 0   | VCC1         | Output pin the D/A converter.                                                                                                                                                                                                             |

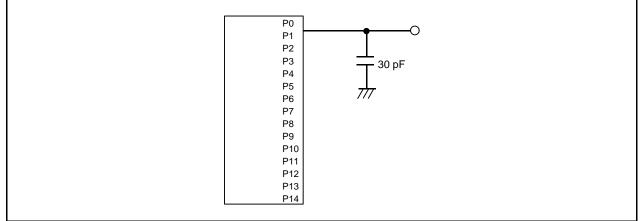

| I/O ports                        | P0_0 to P0_7<br>P1_0 to P1_7<br>P2_0 to P2_7<br>P3_0 to P3_7<br>P4_0 to P4_7<br>P5_0 to P5_7<br>P12_0 to P12_7<br>P13_0 to P13_7 | I/O | VCC2         | 8-bit CMOS I/O ports. A direction register determines<br>whether each pin is used as an input port or an output<br>port. A pull-up resistor may be enabled or disabled for<br>input ports in 4-bit units.                                 |

|                                  | P6_0 to P6_7<br>P7_0 to P7_7<br>P8_0 to P8_7<br>P9_0 to P9_7<br>P10_0 to P10_7<br>P11_0 to P11_7                                 | I/O | VCC1         | 8-bit I/O ports having equivalent functions to P0. However, P7_0, P7_1, and P8_5 are N-channel open drain output ports. No pull-up resistor is provided. P8_5 is an input port for verifying the NMI pin level and shares a pin with NMI. |

|                                  | P14_0, P14_1                                                                                                                     | I/O | VCC1         | I/O ports having equivalent functions to P0.                                                                                                                                                                                              |

Table 1.14

Pin Functions for the 128-Pin Package (3/3)

## 2.8.7 Interrupt Enable Flag (I Flag)

The I flag enables maskable interrupts.

Maskable interrupts are disabled when the I flag is 0, and enabled when it is 1. The I flag becomes 0 when an interrupt request is accepted.

## 2.8.8 Stack Pointer Select Flag (U Flag)

ISP is selected when the U flag is 0. USP is selected when the U flag is 1. The U flag becomes 0 when a hardware interrupt request is accepted, or the INT instruction of software interrupt number 0 to 31 is executed.

## 2.8.9 Processor Interrupt Priority Level (IPL)

IPL is 3 bits wide and assigns processor interrupt priority levels from 0 to 7. If a requested interrupt has higher priority than IPL, the interrupt request is enabled.

### 2.8.10 Reserved Areas

Only set these bits to 0. The read value is undefined.

| Address | Register                                                                                        | Symbol           | Reset Value |

|---------|-------------------------------------------------------------------------------------------------|------------------|-------------|

| 0040h   |                                                                                                 |                  |             |

| 0041h   |                                                                                                 |                  |             |

| 0042h   | INT7 Interrupt Control Register                                                                 | INT7IC           | XX00 X000b  |

| 0043h   | INT6 Interrupt Control Register                                                                 | INT6IC           | XX00 X000b  |

| 0044h   | INT3 Interrupt Control Register                                                                 | INT3IC           | XX00 X000b  |

| 0045h   | Timer B5 Interrupt Control Register                                                             | TB5IC            | XXXX X000b  |

| 0046h   | Timer B4 Interrupt Control Register<br>UART1 Bus Collision Detection Interrupt Control Register | TB4IC<br>U1BCNIC | XXXX X000b  |

| 0047h   | Timer B3 Interrupt Control Register<br>UART0 Bus Collision Detection Interrupt Control Register | TB3IC<br>U0BCNIC | XXXX X000b  |

| 0048h   | SI/O4 Interrupt Control Register<br>INT5 Interrupt Control Register                             | S4IC<br>INT5IC   | XX00 X000b  |

| 0049h   | SI/O3 Interrupt Control Register<br>INT4 Interrupt Control Register                             | S3IC<br>INT4IC   | XX00 X000b  |

| 004Ah   | UART2 Bus Collision Detection Interrupt Control Register                                        | BCNIC            | XXXX X000b  |

| 004Bh   | DMA0 Interrupt Control Register                                                                 | DM0IC            | XXXX X000b  |

| 004Ch   | DMA1 Interrupt Control Register                                                                 | DM1IC            | XXXX X000b  |

| 004Dh   | Key Input Interrupt Control Register                                                            | KUPIC            | XXXX X000b  |

| 004Eh   | A/D Conversion Interrupt Control Register                                                       | ADIC             | XXXX X000b  |

| 004Fh   | UART2 Transmit Interrupt Control Register                                                       | S2TIC            | XXXX X000b  |

| 0050h   | UART2 Receive Interrupt Control Register                                                        | S2RIC            | XXXX X000b  |

| 0051h   | UART0 Transmit Interrupt Control Register                                                       | SOTIC            | XXXX X000b  |

| 0052h   | UART0 Receive Interrupt Control Register                                                        | SORIC            | XXXX X000b  |

| 0053h   | UART1 Transmit Interrupt Control Register                                                       | S1TIC            | XXXX X000b  |

| 0054h   | UART1 Receive Interrupt Control Register                                                        | S1RIC            | XXXX X000b  |

| 0055h   | Timer A0 Interrupt Control Register                                                             | TA0IC            | XXXX X000b  |

| 0056h   | Timer A1 Interrupt Control Register                                                             | TA1IC            | XXXX X000b  |

| 0057h   | Timer A2 Interrupt Control Register                                                             | TA2IC            | XXXX X000b  |

| 0058h   | Timer A3 Interrupt Control Register                                                             | TA3IC            | XXXX X000b  |

| 0059h   | Timer A4 Interrupt Control Register                                                             | TA4IC            | XXXX X000b  |

| 005Ah   | Timer B0 Interrupt Control Register                                                             | TB0IC            | XXXX X000b  |

| 005Bh   | Timer B1 Interrupt Control Register                                                             | TB1IC            | XXXX X000b  |

| 005Ch   | Timer B2 Interrupt Control Register                                                             | TB2IC            | XXXX X000b  |

| 005Dh   | INTO Interrupt Control Register                                                                 | INTOIC           | XX00 X000b  |

| 005Eh   | INT1 Interrupt Control Register                                                                 | INT1IC           | XX00 X000b  |

| 005Fh   | INT2 Interrupt Control Register                                                                 | INT2IC           | XX00 X000b  |

### Table 4.3SFR Information (3) (1)

Note:

1. The blank areas are reserved. No access is allowed.

| Table 4.4 | SFR information (4)                                                                                                     |                   |             |

|-----------|-------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|

| Address   | Register                                                                                                                | Symbol            | Reset Value |

| 0060h     |                                                                                                                         | 1                 |             |

| 0061h     |                                                                                                                         |                   |             |

| 0062h     |                                                                                                                         |                   |             |

| 0063h     |                                                                                                                         |                   |             |

| 0064h     |                                                                                                                         |                   |             |

| 0065h     |                                                                                                                         |                   |             |

| 0066h     |                                                                                                                         |                   |             |

| 0067h     |                                                                                                                         |                   |             |

| 0068h     |                                                                                                                         |                   |             |

| 0069h     | DMA2 Interrupt Control Register                                                                                         | DM2IC             | XXXX X000b  |

| 006Ah     | DMA3 Interrupt Control Register                                                                                         | DM3IC             | XXXX X000b  |

| 006Bh     | UART5 Bus Collision Detection Interrupt Control Register<br>CEC1 Interrupt Control Register                             | U5BCNIC<br>CEC1IC | XXXX X000b  |

| 006Ch     | UART5 Transmit Interrupt Control Register<br>CEC2 Interrupt Control Register                                            | S5TIC<br>CEC2IC   | XXXX X000b  |

| 006Dh     | UART5 Receive Interrupt Control Register                                                                                | S5RIC             | XXXX X000b  |

| 006Eh     | UART6 Bus Collision Detection Interrupt Control Register<br>Real-Time Clock Periodic Interrupt Control Register         | U6BCNIC<br>RTCTIC | XXXX X000b  |

| 006Fh     | UART6 Transmit Interrupt Control Register<br>Real-Time Clock Compare Interrupt Control Register                         | S6TIC<br>RTCCIC   | XXXX X000b  |

| 0070h     | UART6 Receive Interrupt Control Register                                                                                | S6RIC             | XXXX X000b  |

| 0071h     | UART7 Bus Collision Detection Interrupt Control Register<br>Remote Control Signal Receiver 0 Interrupt Control Register | U7BCNIC<br>PMC0IC | XXXX X000b  |

| 0072h     | UART7 Transmit Interrupt Control Register<br>Remote Control Signal Receiver 1 Interrupt Control Register                | S7TIC<br>PMC1IC   | XXXX X000b  |

| 0073h     | UART7 Receive Interrupt Control Register                                                                                | S7RIC             | XXXX X000b  |

| 0074h     |                                                                                                                         | 1 1               |             |

| 0075h     |                                                                                                                         | 1 1               |             |

| 0076h     |                                                                                                                         | 1 1               |             |

| 0077h     |                                                                                                                         | 1                 |             |

| 0078h     |                                                                                                                         | 1                 |             |

| 0079h     |                                                                                                                         | 1 1               |             |

| 007Ah     |                                                                                                                         | 1 1               |             |

| 007Bh     | I2C-bus Interface Interrupt Control Register                                                                            | IICIC             | XXXX X000b  |

| 007Ch     | SCL/SDA Interrupt Control Register                                                                                      | SCLDAIC           | XXXX X000b  |

| 007Dh     |                                                                                                                         | 1 1               |             |

| 007Eh     |                                                                                                                         | 1 1               |             |

| 007Fh     |                                                                                                                         |                   |             |

| 0080h to  |                                                                                                                         | <u> </u>          |             |

| 017Fh     |                                                                                                                         |                   |             |

#### Table 4.4SFR Information (4) (1)

Note:

1. The blank areas are reserved. No access is allowed.

## 4.2 Notes on SFRs

## 4.2.1 Register Settings

Table 4.19 lists Registers with Write-Only Bits and registers whose function differs between reading and writing. Set these registers with immediate values. Do not use read-modify-write instructions. When establishing the next value by altering the existing value, write the existing value to the RAM as well as to the register. Transfer the next value to the register after making changes in the RAM. Read-modify-write instructions can be used when writing to the no register bits.

| Address        | Register                                            | Symbol |

|----------------|-----------------------------------------------------|--------|

| 0249h          | UART0 Bit Rate Register                             | U0BRG  |

| 024Bh to 024Ah | UART0 Transmit Buffer Register                      | U0TB   |

| 0259h          | UART1 Bit Rate Register                             | U1BRG  |

| 025Bh to 025Ah | UART1 Transmit Buffer Register                      | U1TB   |

| 0269h          | UART2 Bit Rate Register                             | U2BRG  |

| 026Bh to 026Ah | UART2 Transmit Buffer Register                      | U2TB   |

| 0273h          | SI/O3 Bit Rate Register                             | S3BRG  |

| 0277h          | SI/O4 Bit Rate Register                             | S4BRG  |

| 0289h          | UART5 Bit Rate Register                             | U5BRG  |

| 028Bh to 028Ah | UART5 Transmit Buffer Register                      | U5TB   |

| 0299h          | UART6 Bit Rate Register                             | U6BRG  |

| 029Bh to 029Ah | UART6 Transmit Buffer Register                      | U6TB   |

| 02A9h          | UART7 Bit Rate Register                             | U7BRG  |

| 02ABh to 02AAh | UART7 Transmit Buffer Register                      | U7TB   |

| 02B6h          | I2C0 Control Register 1                             | S3D0   |

| 02B8h          | I2C0 Status Register 0                              | S10    |

| 0303h to 0302h | Timer A1-1 Register                                 | TA11   |

| 0305h to 0304h | Timer A2-1 Register                                 | TA21   |

| 0307h to 0306h | Timer A4-1 Register                                 | TA41   |

| 030Ah          | Three-Phase Output Buffer Register 0                | IDB0   |

| 030Bh          | Three-Phase Output Buffer Register 1                | IDB1   |

| 030Ch          | Dead Time Timer                                     | DTT    |

| 030Dh          | Timer B2 Interrupt Generation Frequency Set Counter | ICTB2  |

| 0327h to 0326h | Timer A0 Register                                   | TA0    |

| 0329h to 0328h | Timer A1 Register                                   | TA1    |

| 032Bh to 032Ah | Timer A2 Register                                   | TA2    |

| 032Dh to 032Ch | Timer A3 Register                                   | TA3    |

| 032Fh to 032Eh | Timer A4 Register                                   | TA4    |

| 037Dh          | Watchdog Timer Refresh Register                     | WDTR   |

| 037Eh          | Watchdog Timer Start Register                       | WDTS   |

| Table 4.19 | Registers with Write-Only Bits |

|------------|--------------------------------|

|------------|--------------------------------|

## 5.1.2 Recommended Operating Conditions

## Table 5.2 Recommended Operating Conditions (1/3)

$V_{CC1} = V_{CC2} = 2.7$  to 5.5 V at  $T_{opr} = -20^{\circ}$ C to 85°C/-40°C to 85°C unless otherwise specified.

| Symbol                |                                                     | Parameter                                                                                                                                                                                         |                                                                                                                        | Unit                |                  |                      |      |

|-----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|----------------------|------|

| Cymbol                |                                                     |                                                                                                                                                                                                   |                                                                                                                        | Min.                | Тур.             | Max.                 | Onit |

| V <sub>CC1</sub> ,    | Supply volt                                         | age ( $V_{CC1} \ge V_{CC2}$ ) CE                                                                                                                                                                  | EC function is not used                                                                                                | 2.7                 | 5.0              | 5.5                  | V    |

| V <sub>CC2</sub>      |                                                     | CE                                                                                                                                                                                                | EC function is used                                                                                                    | 2.7                 |                  | 3.63                 | V    |

| AV <sub>CC</sub>      | Analog sup                                          | ply voltage                                                                                                                                                                                       |                                                                                                                        |                     | V <sub>CC1</sub> |                      | V    |

| V <sub>SS</sub>       | Supply volt                                         | age                                                                                                                                                                                               |                                                                                                                        |                     | 0                |                      | V    |

| AV <sub>SS</sub>      | Analog sup                                          | ply voltage                                                                                                                                                                                       |                                                                                                                        |                     | 0                |                      | V    |

| V <sub>IH</sub>       | High input<br>voltage                               | P3_1 to P3_7, P4_0 to P4_7, P5_0 to<br>P12_0 to P12_7, P13_0 to P13_7                                                                                                                             | P5_7,                                                                                                                  | 0.8V <sub>CC2</sub> |                  | V <sub>CC2</sub>     | V    |

|                       |                                                     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to (in single-chip mode)                                                                                                                                         | P2_7, P3_0                                                                                                             | 0.8V <sub>CC2</sub> |                  | V <sub>CC2</sub>     | V    |

|                       |                                                     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to (data input in memory expansion and modes)                                                                                                                    |                                                                                                                        | 0.5V <sub>CC2</sub> |                  | V <sub>CC2</sub>     | V    |

|                       |                                                     |                                                                                                                                                                                                   | P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_4, P8_6, P8_7,<br>P9_0 to P9_7, P10_0 to P10_7, P11_0 to P11_7, P14_0,<br>P14_1 |                     |                  | V <sub>CC1</sub>     | V    |

|                       |                                                     | P7_0, P7_1, P8_5                                                                                                                                                                                  | 0.8V <sub>CC1</sub>                                                                                                    |                     | 6.5              | V                    |      |

|                       |                                                     | CEC                                                                                                                                                                                               |                                                                                                                        | 0.7V <sub>CC1</sub> |                  |                      | V    |

| V <sub>IL</sub>       | Low input<br>voltage                                | P3_1 to P3_7, P4_0 to P4_7, P5_0 to<br>P12_0 to P12_7, P13_0 to P13_7                                                                                                                             | P5_7,                                                                                                                  | 0                   |                  | 0.2V <sub>CC2</sub>  | V    |

|                       |                                                     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to<br>(in single-chip mode)                                                                                                                                      | P2_7, P3_0                                                                                                             | 0                   |                  | 0.2V <sub>CC2</sub>  | V    |

|                       |                                                     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to (data input in memory expansion and I                                                                                                                         | -                                                                                                                      | 0                   |                  | 0.16V <sub>CC2</sub> | V    |

|                       |                                                     | P6_0 to P6_7, P7_0 to P7_7, P8_0 to<br>P10_0 to P10_7,P11_0 to P11_7, P14<br>XIN, RESET, CNVSS, BYTE                                                                                              |                                                                                                                        | 0                   |                  | 0.2V <sub>CC1</sub>  | V    |

|                       |                                                     | CEC                                                                                                                                                                                               |                                                                                                                        |                     |                  | 0.26V <sub>CC1</sub> | V    |

| I <sub>OH(sum)</sub>  | High peak<br>output                                 | Sum of I <sub>OH(peak)</sub> at P0_0 to P0_7, P1_<br>P2_0 to P2_7                                                                                                                                 | _0 to P1_7,                                                                                                            |                     |                  | -40.0                | mA   |

|                       | current                                             | Sum of $I_{OH(peak)}$ at P3_0 to P3_7, P4_<br>P5_0 to P5_7, P12_0 to P12_7, and F                                                                                                                 |                                                                                                                        |                     |                  | -40.0                | mA   |

|                       |                                                     | Sum of I <sub>OH(peak)</sub> at P6_0 to P6_7, P7_<br>P8_0 to P8_4                                                                                                                                 |                                                                                                                        |                     |                  | -40.0                | mA   |

|                       |                                                     | Sum of I <sub>OH(peak)</sub> at P8_6, P8_7, P9_0<br>P10_0 to P10_7, P11_0 to P11_7, P14                                                                                                           |                                                                                                                        |                     |                  | -40.0                | mA   |

| I <sub>OH(peak)</sub> | High peak<br>output<br>current                      | P0_0 to P0_7, P1_0 to P1_7, P2_0 to<br>P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_2 to P7_7, P8_0 to<br>P9_0 to P9_7, P10_0 to P10_7, P11_0<br>P12_0 to P12_7, P13_0 to P13_7, P13_0         | P8_4, P8_6, P8_7,<br>0 to P11_7,                                                                                       |                     |                  | -10.0                | mA   |

| I <sub>OH(avg)</sub>  | High<br>average<br>output<br>current <sup>(1)</sup> | P0_0 to P0_7, P1_0 to P1_7, P2_0 to<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to<br>P6_0 to P6_7, P7_2 to P7_7, P8_0 to<br>P9_0 to P9_7, P10_0 to P10_7, P11_1<br>P12_0 to P12_7, P13_0 to P13_7, P12_0 | P5_7,<br>P8_4, P8_6, P8_7,<br>0 to P11_7,                                                                              |                     |                  | -5.0                 | mA   |

Note:

1. The average output current is the mean value within 100 ms.

### Table 5.10 Flash Memory (Data Flash) Electrical Characteristics

$V_{CC1}$  = 2.7 to 5.5 V at  $T_{opr}$  = -20 to 85°C/-40 to 85°C, unless otherwise specified.

| Symbol          | Parameter                                         | Conditions                                                      |            | Unit |      |       |

|-----------------|---------------------------------------------------|-----------------------------------------------------------------|------------|------|------|-------|

|                 | T diameter                                        | Conditions                                                      | Min.       | Тур. | Max. | 01111 |

| -               | Program and erase cycles <sup>(1), (3), (4)</sup> | V <sub>CC1</sub> = 3.3 V, T <sub>opr</sub> = 25°C               | 10,000 (2) |      |      | times |

| -               | 2 word program time                               | $V_{CC1} = 3.3 \text{ V}, \text{ T}_{opr} = 25^{\circ}\text{C}$ |            | 300  | 4000 | μS    |

| -               | Lock bit program time                             | $V_{CC1} = 3.3 \text{ V}, \text{ T}_{opr} = 25^{\circ}\text{C}$ |            | 140  | 3000 | μS    |

| -               | Block erase time                                  | $V_{CC1} = 3.3 \text{ V}, \text{ T}_{opr} = 25^{\circ}\text{C}$ |            | 0.2  | 3.0  | S     |

| -               | Program, erase voltage                            |                                                                 | 2.7        |      | 5.5  | V     |

| -               | Read voltage                                      |                                                                 | 2.7        |      | 5.5  | V     |

| -               | Program, erase temperature                        |                                                                 | -20/-40    |      | 85   | °C    |

| t <sub>PS</sub> | Flash memory circuit stabilization wait time      |                                                                 |            |      | 50   | μS    |

| -               | Data hold time <sup>(6)</sup>                     | Ambient temperature = 55°C                                      | 20         |      |      | year  |

Notes:

1. Definition of program and erase cycles

The program and erase cycles refer to the number of per-block erasures.

If the program and erase cycles are n (n = 10,000), each block can be erased n times.

For example, if a 4 KB block is erased after writing 2 word data 1,024 times, each to a different address, this counts as one program and erase cycles. Data cannot be written to the same address more than once without erasing the block (rewrite prohibited).

2. Cycles to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

- 3. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 256 groups before erasing them all in one operation. In addition, averaging the erasure cycles between blocks A and B can further reduce the actual erasure cycles. It is also advisable to retain data on the erasure cycles of each block and limit the number of erase operations to a certain number.

- 4. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

5. Customers desiring program/erase failure rate information should contact a Renesas Electronics sales office.

6. The data hold time includes time that the power supply is off or the clock is not supplied.

## $V_{\rm CC1} = V_{\rm CC2} = 5 \text{ V}$

## Table 5.20 Electrical Characteristics (2) <sup>(1)</sup>

$V_{CC1} = V_{CC2} = 4.2 \text{ to } 5.5 \text{ V}, \\ V_{SS} = 0 \text{ V at } \\ T_{opr} = -20^{\circ} \text{C to } 85^{\circ} \text{C} \\ -40^{\circ} \text{C to } 85^{\circ} \text{C}, \\ f_{(BCLK)} = 32 \text{ MHz unless otherwise specified.}$

| Symbol                            |                       | Parameter                                                                                                                                                                                                                                                                                                              | Measuring            | Sta  | Unit |      |      |

|-----------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|------|------|------|

| Symbol                            |                       | Falameter                                                                                                                                                                                                                                                                                                              | Condition            | Min. | Тур. | Max. | Unit |

| V <sub>T+</sub> - V <sub>T-</sub> | Hysteresis            | HOLD, RDY, TA0IN to TA4IN, TB0IN to TB5IN,<br>INTO to INT7, NMI, ADTRG, CTS0 to CTS2,<br>CTS5 to CTS7, SCL0 to SCL2, SCL5 to SCL7,<br>SDA0 to SDA2, SDA5 to SDA7, CLK0 to CLK7,<br>TA0OUT to TA4OUT,<br>KI0 to KI3, RXD0 to RXD2, RXD5 to RXD7,<br>SIN3, SIN4, SD, PMC0, PMC1, SCLMM,<br>SDAMM, CEC, ZP, IDU, IDV, IDW |                      | 0.5  |      | 2.0  | V    |

| V <sub>T+</sub> - V <sub>T-</sub> | Hysteresis            | RESET                                                                                                                                                                                                                                                                                                                  |                      | 0.5  |      | 2.5  | V    |

| I <sub>IH</sub>                   | High input<br>current | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7,<br>P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P12_0 to P12_7,<br>P13_0 to P13_7, P14_0, P14_1<br>XIN, RESET, CNVSS, BYTE                                                     | V <sub>I</sub> = 5 V |      |      | 5.0  | μΑ   |

| IIL                               | Low input<br>current  | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7,<br>P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P12_0 to P12_7,<br>P13_0 to P13_7, P14_0, P14_1<br>XIN, RESET, CNVSS, BYTE                                                     | V <sub>I</sub> = 0 V |      |      | -5.0 | μΑ   |

| R <sub>PULLUP</sub>               | Pull-up<br>resistance | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P12_0 to P12_7,<br>P13_0 to P13_7, P14_0, P14_1                                                                    | V <sub>I</sub> = 0 V | 30   | 50   | 100  | kΩ   |

| R <sub>fXIN</sub>                 | Feedback re           | esistance XIN                                                                                                                                                                                                                                                                                                          |                      |      | 1.5  |      | MΩ   |

| V <sub>RAM</sub>                  | RAM retenti           | on voltage                                                                                                                                                                                                                                                                                                             | In stop mode         | 1.8  |      |      | V    |

Note:

1. When  $V_{CC1} \neq V_{CC2}$ , refer to 5 V or 3 V standard depending on the voltage.

## 5.2.2 Timing Requirements (Peripheral Functions and Others)

(V<sub>CC1</sub> = V<sub>CC2</sub> = 5 V, V<sub>SS</sub> = 0 V, at T<sub>opr</sub> = -20°C to  $85^{\circ}$ C/-40°C to  $85^{\circ}$ C unless otherwise specified)

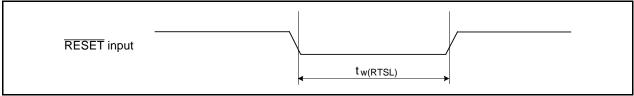

## 5.2.2.1 Reset Input (RESET Input)

#### Table 5.24 Reset Input (RESET Input)

| Symbol               | Parameter                   | Stan | Unit |      |

|----------------------|-----------------------------|------|------|------|

|                      |                             | Min. | Max. | Onit |

| t <sub>w(RSTL)</sub> | RESET input low pulse width | 10   |      | μS   |

## Figure 5.5 Reset Input (RESET Input)

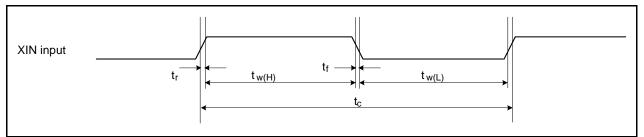

## 5.2.2.2 External Clock Input

#### Table 5.25 External Clock Input (XIN Input) <sup>(1)</sup>

| Symbol            | Parameter                             | Stan | Unit |      |

|-------------------|---------------------------------------|------|------|------|

|                   |                                       | Min. | Max. | Onic |

| t <sub>c</sub>    | External clock input cycle time       | 50   |      | ns   |

| t <sub>w(H)</sub> | External clock input high pulse width | 20   |      | ns   |

| t <sub>w(L)</sub> | External clock input low pulse width  | 20   |      | ns   |

| t <sub>r</sub>    | External clock rise time              |      | 9    | ns   |

| t <sub>f</sub>    | External clock fall time              |      | 9    | ns   |

Note:

1. The condition is  $V_{CC1} = V_{CC2} = 3.0$  to 5.0 V.

## Timing Requirements

$(V_{CC1} = V_{CC2} = 5 \text{ V}, V_{SS} = 0 \text{ V}, \text{ at } T_{opr} = -20^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}/-40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise specified})$

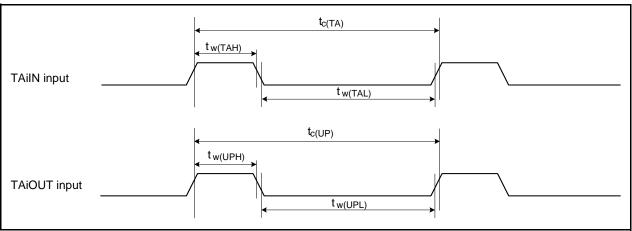

## 5.2.2.3 Timer A Input

#### Table 5.26 Timer A Input (Counter Input in Event Counter Mode)

| Symbol              | Parameter                    | Standard |      | Unit |

|---------------------|------------------------------|----------|------|------|

|                     |                              | Min.     | Max. | Onic |

| t <sub>c(TA)</sub>  | TAilN input cycle time       | 100      |      | ns   |

| t <sub>w(TAH)</sub> | TAilN input high pulse width | 40       |      | ns   |

| t <sub>w(TAL)</sub> | TAilN input low pulse width  | 40       |      | ns   |

#### Table 5.27 Timer A Input (Gating Input in Timer Mode)

| Symbol              | Parameter                    | Standard |      | Unit  |

|---------------------|------------------------------|----------|------|-------|

|                     |                              | Min.     | Max. | Offic |

| t <sub>c(TA)</sub>  | TAilN input cycle time       | 400      |      | ns    |

| t <sub>w(TAH)</sub> | TAilN input high pulse width | 200      |      | ns    |

| t <sub>w(TAL)</sub> | TAilN input low pulse width  | 200      |      | ns    |

#### Table 5.28 Timer A Input (External Trigger Input in One-Shot Timer Mode)

| Symbol              | Parameter                    | Stan | Unit |       |

|---------------------|------------------------------|------|------|-------|

|                     |                              | Min. | Max. | Offic |

| t <sub>c(TA)</sub>  | TAilN input cycle time       | 200  |      | ns    |

| t <sub>w(TAH)</sub> | TAiIN input high pulse width | 100  |      | ns    |

| t <sub>w(TAL)</sub> | TAiIN input low pulse width  | 100  |      | ns    |

# Table 5.29Timer A Input (External Trigger Input in Pulse Width Modulation Mode and<br/>Programmable Output Mode)

| Symbol              | Parameter                    | Stan | Unit |      |

|---------------------|------------------------------|------|------|------|

|                     |                              | Min. | Max. | Onit |

| t <sub>w(TAH)</sub> | TAilN input high pulse width | 100  |      | ns   |

| t <sub>w(TAL)</sub> | TAilN input low pulse width  | 100  |      | ns   |

Figure 5.7 Timer A Input

### **Timing Requirements**

$(V_{CC1} = V_{CC2} = 5 \text{ V}, V_{SS} = 0 \text{ V}, \text{ at } T_{opr} = -20^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}/-40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise specified})$

## 5.2.2.4 Timer B Input

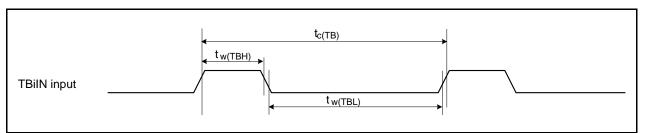

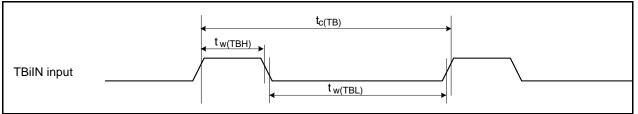

#### Table 5.31 Timer B Input (Counter Input in Event Counter Mode)

| Symbol              | Parameter                                            | Star | Standard |        |

|---------------------|------------------------------------------------------|------|----------|--------|

|                     |                                                      | Min. | Max.     | - Unit |

| t <sub>c(TB)</sub>  | TBiIN input cycle time (counted on one edge)         | 100  |          | ns     |

| t <sub>w(TBH)</sub> | TBiIN input high pulse width (counted on one edge)   | 40   |          | ns     |

| t <sub>w(TBL)</sub> | TBiIN input low pulse width (counted on one edge)    | 40   |          | ns     |

| t <sub>c(TB)</sub>  | TBiIN input cycle time (counted on both edges)       | 200  |          | ns     |

| t <sub>w(TBH)</sub> | TBiIN input high pulse width (counted on both edges) | 80   |          | ns     |

| t <sub>w(TBL)</sub> | TBiIN input low pulse width (counted on both edges)  | 80   |          | ns     |

### Table 5.32 Timer B Input (Pulse Period Measurement Mode)

| Symbol              | Parameter                    | Stan | Unit |       |

|---------------------|------------------------------|------|------|-------|

|                     |                              | Min. | Max. | Offic |

| t <sub>c(TB)</sub>  | TBiIN input cycle time       | 400  |      | ns    |

| t <sub>w(TBH)</sub> | TBiIN input high pulse width | 200  |      | ns    |

| t <sub>w(TBL)</sub> | TBiIN input low pulse width  | 200  |      | ns    |

#### Table 5.33 Timer B Input (Pulse Width Measurement Mode)

| Symbol              | Parameter                    | Stan | Unit |      |

|---------------------|------------------------------|------|------|------|

|                     |                              | Min. | Max. | Onit |

| t <sub>c(TB)</sub>  | TBiIN input cycle time       | 400  |      | ns   |

| t <sub>w(TBH)</sub> | TBiIN input high pulse width | 200  |      | ns   |

| t <sub>w(TBL)</sub> | TBiIN input low pulse width  | 200  |      | ns   |

Figure 5.9 Timer B Input

## Timing Requirements

$(V_{CC1} = V_{CC2} = 5 \text{ V}, V_{SS} = 0 \text{ V}, \text{ at } T_{opr} = -20^{\circ}\text{C to } 85^{\circ}\text{C}/-40^{\circ}\text{C to } 85^{\circ}\text{C} \text{ unless otherwise specified})$

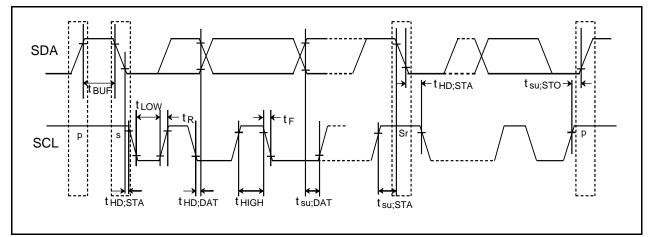

## 5.2.2.7 Multi-master I<sup>2</sup>C-bus

#### Table 5.36Multi-master I<sup>2</sup>C-bus

| Cumhal              | Deremeter                       | Standard Clock Mode |      | Fast-r      | node | Linit  |

|---------------------|---------------------------------|---------------------|------|-------------|------|--------|

| Symbol              | Parameter                       | Min.                | Max. | Min.        | Max. | – Unit |

| t <sub>BUF</sub>    | Bus free time                   | 4.7                 |      | 1.3         |      | μS     |

| t <sub>HD;STA</sub> | Hold time in start condition    | 4.0                 |      | 0.6         |      | μS     |

| t <sub>LOW</sub>    | Hold time in SCL clock 0 status | 4.7                 |      | 1.3         |      | μS     |