#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SIO, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 768KB (768K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 8K x 8                                                                          |

| RAM Size                   | 47K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

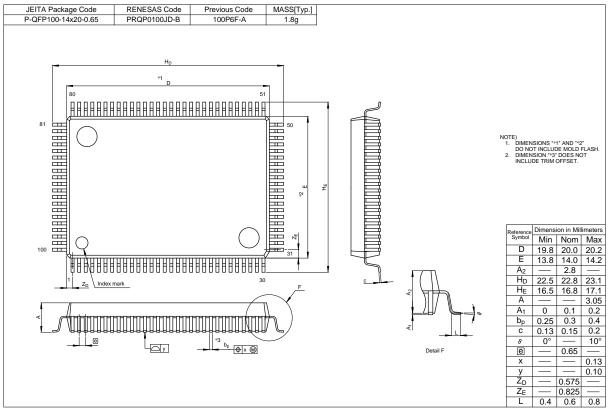

| Package / Case             | 100-BQFP                                                                        |

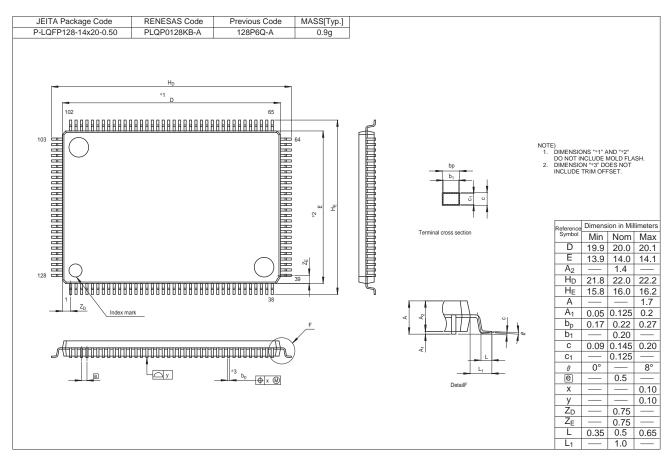

| Supplier Device Package    | 100-QFP (14x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f3650tdfa-u0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.6 Pin Functions

| Signal Name                             | Pin Name                                           | I/O | Power Supply | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------------------------------|----------------------------------------------------|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power supply input                      | VCC1,<br>VCC2,<br>VSS                              | I   | -            | Apply 2.7 to 5.5 V to pins VCC1 and VCC2 (VCC1 $\geq$ VCC2), and 0 V to the VSS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Analog power<br>supply input            | AVCC,<br>AVSS                                      | I   | VCC1         | Apply 2.7 to 5.5 V to pins VCC1 and VCC2 (VCC1 $\ge$ VCC2),<br>and 0 V to the VSS pin.<br>This is the power supply for the A/D and D/A converters.                                                                                                                                                                                                                                                                                                                                                                                                       |  |

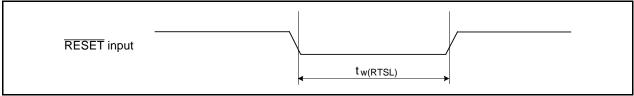

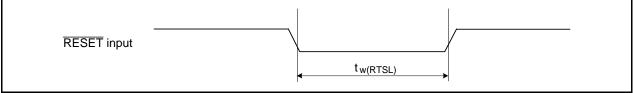

| Reset input                             | RESET                                              | I   | VCC1         | Driving this pin low resets the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| CNVSS                                   | CNVSS                                              | I   | VCC1         | operating in single-chip mode, connect the CNVSS pin to VSS via a resistor. To start operating in microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| External data bus<br>width select input | BYTE                                               | I   | VCC1         | bus is 16 bits when it is low and 8 bits when it is high. This<br>pin must be fixed either high or low. Connect the BYTE pin to                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                         | D0 to D7                                           | I/O | VCC2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                         | D8 to D15                                          | I/O | VCC2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                         | A0 to A19                                          | 0   | VCC2         | Outputs address bits A0 to A19.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                         | A0/D0 to<br>A7/D7                                  | I/O | VCC2         | (A0 to A7) by timesharing, while accessing an external area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                         | A1/D0 to<br>A8/D7                                  | I/O | VCC2         | (A1 to A8) by timesharing, while accessing an external area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                         | $\overline{\text{CS0}}$ to $\overline{\text{CS3}}$ | 0   | VCC2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Bus control<br>pins                     | WRL/WR<br>WRH/BHE<br>RD                            | 0   | VCC2         | <ul> <li>WRH can be switched with BHE and WR.</li> <li>WRL, WRH, and RD selected<br/>If the external data bus is 16 bits, data is written to an even<br/>address in an external area when WRL is driven low. Data<br/>is written to an odd address when WRH is driven low. Data<br/>is read when RD is driven low.</li> <li>WR, BHE, and RD selected<br/>Data is written to an external area when WR is driven low.<br/>Data in an external area is read when RD is driven low.<br/>An odd address is accessed when BHE is driven low. Select</li> </ul> |  |

|                                         | ALE                                                | 0   | VCC2         | Outputs an ALE signal to latch the address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                         | HOLD                                               | Ι   | VCC2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                         | HLDA                                               | 0   | VCC2         | In a hold state, HLDA outputs a low-level signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                         | RDY                                                | I   | VCC2         | The MCU bus is placed in wait state while the $\overline{\text{RDY}}$ pin is driven low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

Table 1.12Pin Functions for the 128-Pin Package (1/3)

Power supply: VCC2 is used to supply power to the external bus associated pins. The dual power supply configuration allows VCC2 to interface at a different voltage than VCC1.

| Signal Name                          | Pin Name                                           | I/O | Power Supply | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|----------------------------------------------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply<br>input                | VCC1,<br>VCC2, VSS                                 | I   | -            | Apply 2.7 to 5.5 V to pins VCC1 and VCC2 (VCC1 $\geq$ VCC2) and 0 V to the VSS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Analog power<br>supply input         | AVCC, AVSS                                         | I   | VCC1         | This is the power supply for the A/D and D/A converters.<br>Connect the AVCC pin to VCC1, and connect the AVSS pin<br>to VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Reset input                          | RESET                                              | I   | VCC1         | Driving this pin low resets the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CNVSS                                | CNVSS                                              | I   | VCC1         | Input pin to switch processor modes. After a reset, to start<br>operating in single-chip mode, connect the CNVSS pin to<br>VSS via a resistor. To start operating in microprocessor<br>mode, connect the pin to VCC1.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| External data bus width select input | BYTE                                               | I   | VCC1         | Input pin to select the data bus of the external area. The data<br>bus is 16 bits when it is low, and 8 bits when it is high. This<br>pin must be fixed either high or low. Connect the BYTE pin to<br>VSS in single-chip mode.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                      | D0 to D7                                           | I/O | VCC2         | Inputs or outputs data (D0 to D7) while accessing an external area with a separate bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                      | D8 to D15                                          | I/O | VCC2         | Inputs or outputs data (D8 to D15) while accessing an external area with a 16-bit separate bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                      | A0 to A19                                          | 0   | VCC2         | Outputs address bits A0 to A19.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                      | A0/D0 to<br>A7/D7                                  | I/O | VCC2         | Inputs or outputs data (D0 to D7) and outputs address bits (A0 to A7) by timesharing, while accessing an external area with an 8-bit multiplexed bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                      | A1/D0 to<br>A8/D7                                  | I/O | VCC2         | Inputs or outputs data (D0 to D7) and outputs address bits (A1 to A8) by timesharing, while accessing an external area with a 16-bit multiplexed bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                      | $\overline{\text{CS0}}$ to $\overline{\text{CS3}}$ | 0   | VCC2         | Outputs chip-select signals $\overline{CS0}$ to $\overline{CS3}$ to specify an external area.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bus control pins                     | WRL/WR<br>WRH/BHE<br>RD                            | 0   | VCC2         | <ul> <li>Outputs WRL, WRH, (WR, BHE), and RD signals. WRL and WRH can be switched with BHE and WR.</li> <li>WRL, WRH, and RD selected</li> <li>If the external data bus is 16 bits, data is written to an even address in an external area when WRL is driven low. Data is written to an odd address when WRH is driven low. Data is read when RD is driven low.</li> <li>WR, BHE, and RD selected</li> <li>Data is written to an external area when WRH is driven low. Data is written to an external area when WRH is driven low. An odd address is accessed when RD is driven low. Select</li> <li>WR, BHE, and RD when using an 8-bit external data bus.</li> </ul> |

|                                      | ALE                                                | 0   | VCC2         | Outputs an ALE signal to latch the address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                      | HOLD                                               | ļ   | VCC2         | $\overline{\text{HOLD}}$ input is unavailable. Connect the $\overline{\text{HOLD}}$ pin to VCC2 via a resistor (pull-up).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                      | HLDA                                               | 0   | VCC2         | In a hold state, HLDA outputs a low-level signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                      | RDY                                                | I   | VCC2         | The MCU bus is placed in a wait state while the $\overline{\text{RDY}}$ pin is driven low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 1.15 Pin Functions for the 100-Pin Package (1/3)

Power supply: VCC2 is used to supply power to the external bus associated pins. The dual power supply configuration allows VCC2 to interface at a different voltage than VCC1.

| Table 4.7 | SFR Information (7)                                                       |                      |                   |

|-----------|---------------------------------------------------------------------------|----------------------|-------------------|

| Address   | Register                                                                  | Symbol               | Reset Value       |

| 01E0h     | Timer B3-1 Register                                                       | TB31                 | XXh               |

| 01E1h     | Timer B3-1 Register                                                       |                      | XXh               |

| 01E2h     | Timor P4 4 Decision                                                       | TD 44                | XXh               |

| 01E3h     | Timer B4-1 Register                                                       | TB41                 | XXh               |

| 01E4h     | Times DE 4 De sister                                                      |                      | XXh               |

| 01E5h     | Timer B5-1 Register                                                       | TB51                 | XXh               |

| 01E6h     | Pulse Period/Pulse Width Measurement Mode Function Select Reg-<br>ister 2 | PPWFS2               | XXXX X000b        |

| 01E7h     |                                                                           |                      |                   |

| 01E8h     | Timer B Count Source Select Register 2                                    | TBCS2                | 00h               |

| 01E9h     | Timer B Count Source Select Register 3                                    | TBCS3                | X0h               |

| 01EAh     | 5                                                                         |                      |                   |

| 01EBh     |                                                                           |                      |                   |

| 01ECh     |                                                                           |                      |                   |

| 01EDh     |                                                                           |                      |                   |

| 01EEh     |                                                                           |                      |                   |

| 01EFh     |                                                                           |                      |                   |

| 01F0h     | PMC0 Function Select Register 0                                           | PMC0CON0             | 00h               |

| 01F1h     | PMC0 Function Select Register 1                                           | PMC0CON1             | 00XX 0000b        |

| 01F2h     | PMC0 Function Select Register 2                                           | PMC0CON2             | 0000 00X0b        |

| 01F3h     | PMC0 Function Select Register 3                                           | PMC0CON3             | 00h               |

| 01F4h     | PMC0 Status Register                                                      | PMC0STS              | 00h               |

| 01F5h     | PMC0 Interrupt Source Select Register                                     | PMC0INT              | 00h               |

| 01F6h     | PMC0 Compare Control Register                                             | PMC0CPC              | XXX0 X000b        |

| 01F7h     | PMC0 Compare Data Register                                                | PMC0CPD              | 00h               |

| 01F8h     | PMC1 Function Select Register 0                                           | PMC1CON0             | XXX0 X000b        |

| 01F9h     | PMC1 Function Select Register 1                                           | PMC1CON1             | XXXX 0X00b        |

| 01FAh     | PMC1 Function Select Register 2                                           | PMC1CON1<br>PMC1CON2 | 0000 00X0b        |

| 01FBh     | PMC1 Function Select Register 3                                           | PMC1CON2<br>PMC1CON3 | 0000 00X00<br>00h |

| 01FBh     | PMC1 Status Register                                                      | PMC1STS              | X000 X00Xb        |

| 01FDh     | PMC1 Interrupt Source Select Register                                     | PMC1313<br>PMC1INT   | X000 X00Xb        |

| 01FEh     |                                                                           | PINCTINT             |                   |

|           |                                                                           |                      |                   |

| 01FFh     |                                                                           |                      |                   |

| 0200h     |                                                                           |                      |                   |

| 0201h     |                                                                           |                      |                   |

| 0202h     |                                                                           |                      |                   |

| 0203h     |                                                                           |                      |                   |

| 0204h     |                                                                           | 150004               | 0.01              |

| 0205h     | Interrupt Source Select Register 3                                        | IFSR3A               | 00h               |

| 0206h     | Interrupt Source Select Register 2                                        | IFSR2A               | 00h               |

| 0207h     | Interrupt Source Select Register                                          | IFSR                 | 00h               |

| 0208h     |                                                                           |                      |                   |

| 0209h     |                                                                           |                      |                   |

| 020Ah     |                                                                           |                      |                   |

| 020Bh     |                                                                           |                      |                   |

| 020Ch     |                                                                           |                      |                   |

| 020Dh     |                                                                           |                      |                   |

| 020Eh     | Address Match Interrupt Enable Register                                   | AIER                 | XXXX XX00b        |

| 020Fh     | Address Match Interrupt Enable Register 2                                 | AIER2                | XXXX XX00b        |

#### Table 4.7SFR Information (7) (1)

Note:

1. The blank areas are reserved. No access is allowed.

| Address         | Register                                        | Symbol  | Reset Value |

|-----------------|-------------------------------------------------|---------|-------------|

| 0390h           | DMA2 Source Select Register                     | DM2SL   | 00h         |

| 0391h           |                                                 | DIVIZOL | 0011        |

| 0392h           | DMA3 Source Select Register                     | DM3SL   | 00h         |

| 0393h           |                                                 | DIVISOE | 0011        |

| 0393h<br>0394h  |                                                 |         |             |

| 039411<br>0395h |                                                 |         |             |

| 0396h           |                                                 |         |             |

|                 |                                                 |         |             |

| 0397h           |                                                 |         | 2.21        |

| 0398h           | DMA0 Source Select Register                     | DM0SL   | 00h         |

| 0399h           |                                                 |         |             |

| 039Ah           | DMA1 Source Select Register                     | DM1SL   | 00h         |

| 039Bh           |                                                 |         |             |

| 039Ch           |                                                 |         |             |

| 039Dh           |                                                 |         |             |

| 039Eh           |                                                 |         |             |

| 039Fh           |                                                 |         |             |

| 03A0h           |                                                 |         |             |

| 03A1h           |                                                 |         |             |

| 03A2h           | Open-Circuit Detection Assist Function Register | AINRST  | XX00 XXXXb  |

| 03A3h           |                                                 |         |             |

| 03A4h           |                                                 |         |             |

| 03A5h           |                                                 |         |             |

| 03A6h           |                                                 |         |             |

| 03A7h           |                                                 |         |             |

| 03A8h           |                                                 |         |             |

| 03A9h           |                                                 |         |             |

| 03AAh           |                                                 |         |             |

| 03ABh           |                                                 |         |             |

| 03ACh           |                                                 |         |             |

| 03ADh           |                                                 |         |             |

| 03AEh           |                                                 |         |             |

| 03AEh<br>03AFh  |                                                 |         |             |

| 03A0h           |                                                 |         |             |

| 03B0n<br>03B1h  |                                                 |         |             |

|                 |                                                 |         |             |

| 03B2h           |                                                 |         |             |

| 03B3h           |                                                 |         |             |

| 03B4h           | SFR Snoop Address Register                      | CRCSAR  | XXXX XXXXb  |

| 03B5h           |                                                 |         | 00XX XXXXb  |

| 03B6h           | CRC Mode Register                               | CRCMR   | 0XXX XXX0b  |

| 03B7h           |                                                 |         |             |

| 03B8h           |                                                 |         |             |

| 03B9h           |                                                 |         |             |

| 03BAh           |                                                 |         |             |

| 03BBh           |                                                 |         |             |

| 03BCh           | CRC Data Register                               | CRCD    | XXh         |

| 03BDh           |                                                 |         | XXh         |

| 03BEh           | CRC Input Register                              | CRCIN   | XXh         |

| 03BFh           |                                                 |         |             |

#### Table 4.15SFR Information (15) (1)

Note:

1. The blank areas are reserved. No access is allowed.

| Address | Register                    | Symbol | Reset Value |

|---------|-----------------------------|--------|-------------|

| 03F0h   | Port P8 Register            | P8     | XXh         |

| 03F1h   | Port P9 Register            | P9     | XXh         |

| 03F2h   | Port P8 Direction Register  | PD8    | 00h         |

| 03F3h   | Port P9 Direction Register  | PD9    | 00h         |

| 03F4h   | Port P10 Register           | P10    | XXh         |

| 03F5h   | Port P11 Register           | P11    | XXh         |

| 03F6h   | Port P10 Direction Register | PD10   | 00h         |

| 03F7h   | Port P11 Direction Register | PD11   | 00h         |

| 03F8h   | Port P12 Register           | P12    | XXh         |

| 03F9h   | Port P13 Register           | P13    | XXh         |

| 03FAh   | Port P12 Direction Register | PD12   | 00h         |

| 03FBh   | Port P13 Direction Register | PD13   | 00h         |

| 03FCh   | Port P14 Register           | P14    | XXh         |

| 03FDh   |                             |        |             |

| 03FEh   | Port P14 Direction Register | PD14   | XXXX XX00b  |

| 03FFh   |                             |        |             |

#### Table 4.17SFR Information (17) (1)

Note:

1. The blank areas are reserved. No access is allowed.

## 4.2 Notes on SFRs

## 4.2.1 Register Settings

Table 4.19 lists Registers with Write-Only Bits and registers whose function differs between reading and writing. Set these registers with immediate values. Do not use read-modify-write instructions. When establishing the next value by altering the existing value, write the existing value to the RAM as well as to the register. Transfer the next value to the register after making changes in the RAM. Read-modify-write instructions can be used when writing to the no register bits.

| Address        | Register                                            | Symbol |

|----------------|-----------------------------------------------------|--------|

| 0249h          | UART0 Bit Rate Register                             | U0BRG  |

| 024Bh to 024Ah | UART0 Transmit Buffer Register                      | U0TB   |

| 0259h          | UART1 Bit Rate Register                             | U1BRG  |

| 025Bh to 025Ah | UART1 Transmit Buffer Register                      | U1TB   |

| 0269h          | UART2 Bit Rate Register                             | U2BRG  |

| 026Bh to 026Ah | UART2 Transmit Buffer Register                      | U2TB   |

| 0273h          | SI/O3 Bit Rate Register                             | S3BRG  |

| 0277h          | SI/O4 Bit Rate Register                             | S4BRG  |

| 0289h          | UART5 Bit Rate Register                             | U5BRG  |

| 028Bh to 028Ah | UART5 Transmit Buffer Register                      | U5TB   |

| 0299h          | UART6 Bit Rate Register                             | U6BRG  |

| 029Bh to 029Ah | UART6 Transmit Buffer Register                      | U6TB   |

| 02A9h          | UART7 Bit Rate Register                             | U7BRG  |

| 02ABh to 02AAh | UART7 Transmit Buffer Register                      | U7TB   |

| 02B6h          | I2C0 Control Register 1                             | S3D0   |

| 02B8h          | I2C0 Status Register 0                              | S10    |

| 0303h to 0302h | Timer A1-1 Register                                 | TA11   |

| 0305h to 0304h | Timer A2-1 Register                                 | TA21   |

| 0307h to 0306h | Timer A4-1 Register                                 | TA41   |

| 030Ah          | Three-Phase Output Buffer Register 0                | IDB0   |

| 030Bh          | Three-Phase Output Buffer Register 1                | IDB1   |

| 030Ch          | Dead Time Timer                                     | DTT    |

| 030Dh          | Timer B2 Interrupt Generation Frequency Set Counter | ICTB2  |

| 0327h to 0326h | Timer A0 Register                                   | TA0    |

| 0329h to 0328h | Timer A1 Register                                   | TA1    |

| 032Bh to 032Ah | Timer A2 Register                                   | TA2    |

| 032Dh to 032Ch | Timer A3 Register                                   | TA3    |

| 032Fh to 032Eh | Timer A4 Register                                   | TA4    |

| 037Dh          | Watchdog Timer Refresh Register                     | WDTR   |

| 037Eh          | Watchdog Timer Start Register                       | WDTS   |

| Table 4.19 | Registers with Write-Only Bits |

|------------|--------------------------------|

|------------|--------------------------------|

# 5. Electrical Characteristics

# 5.1 Electrical Characteristics (Common to 3 V and 5 V)

## 5.1.1 Absolute Maximum Rating

#### Table 5.1Absolute Maximum Ratings

| Symbol           |                | Parameter                                                                                                                                               | Condition                                                     | Rated Value                                   | Unit |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------|------|

| V <sub>CC1</sub> | Supply voltage |                                                                                                                                                         | $V_{CC1} = AV_{CC}$                                           | -0.3 to 6.5                                   | V    |

| V <sub>CC2</sub> | Supply voltage |                                                                                                                                                         | $V_{CC1} = AV_{CC}$                                           | -0.3 to V <sub>CC1</sub> + 0.1 <sup>(1)</sup> | V    |

| AV <sub>CC</sub> | Analog supply  | voltage                                                                                                                                                 | $V_{CC1} = AV_{CC}$                                           | -0.3 to 6.5                                   | V    |

| V <sub>REF</sub> | Analog referen | ce voltage                                                                                                                                              | $V_{CC1} = AV_{CC}$                                           | -0.3 to V <sub>CC1</sub> + 0.1 <sup>(1)</sup> | V    |

| Vı               | Input voltage  | RESET, CNVSS, BYTE,<br>P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7,<br>P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P14_0, P14_1<br>XIN |                                                               | -0.3 to V <sub>CC1</sub> + 0.3 <sup>(1)</sup> | V    |

|                  |                | P0_0 to P0_7, P1_0 to P1_7,<br>P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7,<br>P12_0 to P12_7, P13_0 to P13_7                             |                                                               | -0.3 to V <sub>CC2</sub> + 0.3 <sup>(1)</sup> | V    |

|                  |                | P7_0, P7_1, P8_5                                                                                                                                        |                                                               | -0.3 to 6.5                                   | V    |

| Vo               | Output voltage | P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7,<br>P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P14_0, P14_1<br>XOUT                       |                                                               | -0.3 to V <sub>CC1</sub> + 0.3 <sup>(1)</sup> | V    |

|                  |                | P0_0 to P0_7, P1_0 to P1_7,<br>P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7,<br>P12_0 to P12_7, P13_0 to P13_7                             |                                                               | -0.3 to V <sub>CC2</sub> + 0.3 <sup>(1)</sup> | V    |

|                  |                | P7_0, P7_1, P8_5                                                                                                                                        |                                                               | -0.3 to 6.5                                   | V    |

| P <sub>d</sub>   | Power consum   | ption                                                                                                                                                   | $-40^{\circ}\text{C} < \text{T}_{opr} \le 85^{\circ}\text{C}$ | 300                                           | mW   |

| T <sub>opr</sub> | Operating      | When the MCU is operating                                                                                                                               |                                                               | -20 to 85/-40 to 85                           | °C   |

| - <b>r</b>       | temperature    | Flash program erase                                                                                                                                     | Program area                                                  | 0 to 60                                       |      |

|                  |                |                                                                                                                                                         | Data area                                                     | -20 to 85/-40 to 85                           |      |

| T <sub>stg</sub> | Storage tempe  | rature                                                                                                                                                  |                                                               | –65 to 150                                    | °C   |

Note:

1. Maximum value is 6.5 V.

# 5.1.2 Recommended Operating Conditions

## Table 5.2 Recommended Operating Conditions (1/3)

$V_{CC1} = V_{CC2} = 2.7$  to 5.5 V at  $T_{opr} = -20^{\circ}$ C to 85°C/-40°C to 85°C unless otherwise specified.

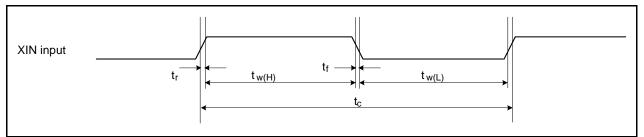

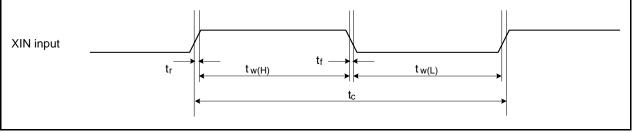

| Symbol                               |                                                     | Parameter                                                                                                                                                                                         | Standard                                  |                     |                      |                  |    |

|--------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------|----------------------|------------------|----|

| Cymbol                               |                                                     |                                                                                                                                                                                                   | Min.                                      | Тур.                | Max.                 | Unit             |    |

| V <sub>CC1</sub> ,                   | Supply volt                                         | age ( $V_{CC1} \ge V_{CC2}$ ) CE                                                                                                                                                                  | EC function is not used                   | 2.7                 | 5.0                  | 5.5              | V  |

| V <sub>CC2</sub>                     |                                                     | CE                                                                                                                                                                                                | EC function is used                       | 2.7                 |                      | 3.63             | V  |

| AV <sub>CC</sub>                     | Analog sup                                          | ply voltage                                                                                                                                                                                       |                                           |                     | V <sub>CC1</sub>     |                  | V  |

| V <sub>SS</sub>                      | Supply volt                                         | age                                                                                                                                                                                               |                                           |                     | 0                    |                  | V  |

| AV <sub>SS</sub>                     | Analog sup                                          | ply voltage                                                                                                                                                                                       |                                           | 0                   |                      | V                |    |

| V <sub>IH</sub>                      | High input<br>voltage                               | P3_1 to P3_7, P4_0 to P4_7, P5_0 to<br>P12_0 to P12_7, P13_0 to P13_7                                                                                                                             | P5_7,                                     | 0.8V <sub>CC2</sub> |                      | V <sub>CC2</sub> | V  |

|                                      |                                                     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to (in single-chip mode)                                                                                                                                         | P2_7, P3_0                                | 0.8V <sub>CC2</sub> |                      | V <sub>CC2</sub> | V  |

|                                      |                                                     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to (data input in memory expansion and modes)                                                                                                                    |                                           | 0.5V <sub>CC2</sub> |                      | V <sub>CC2</sub> | V  |

|                                      |                                                     | P6_0 to P6_7, P7_2 to P7_7, P8_0 to<br>P9_0 to P9_7, P10_0 to P10_7, P11_0<br>P14_1<br>XIN, RESET, CNVSS, BYTE                                                                                    |                                           | 0.8V <sub>CC1</sub> |                      | V <sub>CC1</sub> | V  |

|                                      |                                                     | P7_0, P7_1, P8_5                                                                                                                                                                                  | 0.8V <sub>CC1</sub>                       |                     | 6.5                  | V                |    |

|                                      |                                                     | CEC                                                                                                                                                                                               |                                           | 0.7V <sub>CC1</sub> |                      |                  | V  |

| V <sub>IL</sub> Low input<br>voltage |                                                     | P3_1 to P3_7, P4_0 to P4_7, P5_0 to<br>P12_0 to P12_7, P13_0 to P13_7                                                                                                                             | 0                                         |                     | 0.2V <sub>CC2</sub>  | V                |    |

|                                      |                                                     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to<br>(in single-chip mode)                                                                                                                                      | 0                                         |                     | 0.2V <sub>CC2</sub>  | V                |    |

|                                      |                                                     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to (data input in memory expansion and I                                                                                                                         | 0                                         |                     | 0.16V <sub>CC2</sub> | V                |    |

|                                      |                                                     | P6_0 to P6_7, P7_0 to P7_7, P8_0 to<br>P10_0 to P10_7,P11_0 to P11_7, P14<br>XIN, RESET, CNVSS, BYTE                                                                                              | 0                                         |                     | 0.2V <sub>CC1</sub>  | V                |    |

|                                      |                                                     | CEC                                                                                                                                                                                               |                                           |                     | 0.26V <sub>CC1</sub> | V                |    |

| I <sub>OH(sum)</sub>                 | High peak<br>output                                 | Sum of I <sub>OH(peak)</sub> at P0_0 to P0_7, P1_<br>P2_0 to P2_7                                                                                                                                 | _0 to P1_7,                               |                     |                      | -40.0            | mA |

|                                      | current                                             | Sum of $I_{OH(peak)}$ at P3_0 to P3_7, P4_<br>P5_0 to P5_7, P12_0 to P12_7, and F                                                                                                                 |                                           |                     |                      | -40.0            | mA |

|                                      |                                                     | Sum of I <sub>OH(peak)</sub> at P6_0 to P6_7, P7_<br>P8_0 to P8_4                                                                                                                                 |                                           |                     |                      | -40.0            | mA |

|                                      |                                                     | Sum of I <sub>OH(peak)</sub> at P8_6, P8_7, P9_0<br>P10_0 to P10_7, P11_0 to P11_7, P14                                                                                                           |                                           |                     |                      | -40.0            | mA |

| I <sub>OH(peak)</sub>                | High peak<br>output<br>current                      | P0_0 to P0_7, P1_0 to P1_7, P2_0 to<br>P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_2 to P7_7, P8_0 to<br>P9_0 to P9_7, P10_0 to P10_7, P11_0<br>P12_0 to P12_7, P13_0 to P13_7, P13_0         |                                           |                     | -10.0                | mA               |    |

| I <sub>OH(avg)</sub>                 | High<br>average<br>output<br>current <sup>(1)</sup> | P0_0 to P0_7, P1_0 to P1_7, P2_0 to<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to<br>P6_0 to P6_7, P7_2 to P7_7, P8_0 to<br>P9_0 to P9_7, P10_0 to P10_7, P11_1<br>P12_0 to P12_7, P13_0 to P13_7, P12_0 | P5_7,<br>P8_4, P8_6, P8_7,<br>0 to P11_7, |                     |                      | -5.0             | mA |

Note:

1. The average output current is the mean value within 100 ms.

# 5.1.3 A/D Conversion Characteristics

## Table 5.5 A/D Conversion Characteristics (1/2) <sup>(1)</sup>

$V_{CC1} = AV_{CC} = 3.0$  to  $5.5 \text{ V} \ge V_{CC2} \ge V_{REF}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$  at  $T_{opr} = -20^{\circ}C$  to  $85^{\circ}C/-40^{\circ}C$  to  $85^{\circ}C$  unless otherwise specified.

| Symbol          | Parameter                    |         | N                           | leasuring Condition                                                                                   |  | Standar | b    | Unit  |

|-----------------|------------------------------|---------|-----------------------------|-------------------------------------------------------------------------------------------------------|--|---------|------|-------|

| Symbol          | i didilletei                 |         | IV                          | Medsuning Condition                                                                                   |  | Тур.    | Max. | 01111 |

| -               | Resolution                   |         | $AV_{CC} =$                 | $V_{CC1} \ge V_{CC2} \ge V_{REF}$                                                                     |  |         | 10   | Bits  |

| I <sub>NL</sub> | Integral non-linearity error | 10 bits | V <sub>CC1</sub> =<br>5.0 V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input<br>(Note 2) |  |         | ±3   | LSB   |

|                 |                              |         | V <sub>CC1</sub> =<br>3.3 V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input<br>(Note 2) |  |         | ±3   | LSB   |

|                 |                              |         | V <sub>CC1</sub> =<br>3.0 V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input<br>(Note 2) |  |         | ±3   | LSB   |

| -               | Absolute accuracy            | 10 bits | V <sub>CC1</sub> =<br>5.0 V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input<br>(Note 2) |  |         | ±3   | LSB   |

|                 |                              |         | V <sub>CC1</sub> =<br>3.3 V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input<br>(Note 2) |  |         | ±3   | LSB   |

|                 |                              |         | V <sub>CC1</sub> =<br>3.0 V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input<br>(Note 2) |  |         | ±3   | LSB   |

Notes:

1. Use when  $AV_{CC} = V_{CC1}$ .

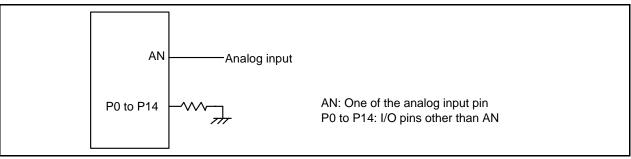

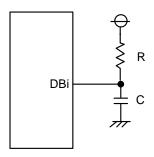

2. Flash memory rewrite disabled. Except for the analog input pin, set the pins to be measured as input ports and connect them to V<sub>SS</sub>. See Figure 5.2 "A/D Accuracy Measure Circuit".

Figure 5.2 A/D Accuracy Measure Circuit

## Table 5.6 A/D Conversion Characteristics (2/2) <sup>(1)</sup>

$V_{CC1} = AV_{CC} = 3.0 \text{ to } 5.5 \text{ V} \ge V_{CC2} \ge V_{REF}, V_{SS} = AV_{SS} = 0 \text{ V at } T_{opr} = -20^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}/-40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise specified.}$

| Symbol                                                              | Paran                  | actor           | Magguring Condition                                         | Standard |      |                  | Unit |

|---------------------------------------------------------------------|------------------------|-----------------|-------------------------------------------------------------|----------|------|------------------|------|

| - Tolerand<br>D <sub>NL</sub> Different<br>- Offset e<br>- Gain err | Falal                  | leter           | Measuring Condition                                         | Min.     | Тур. | Max.             | Unit |

|                                                                     | A/D operating clock    |                 | $4.0~V \leq V_{CC1} \leq 5.5~V$                             | 2        |      | 25               | MHz  |

|                                                                     | frequency              | ANEX0 to ANEX1  | $3.2~V \leq V_{CC1} \leq 4.0~V$                             | 2        |      | 16               | MHz  |

|                                                                     |                        | input           | $3.0~\text{V} \leq \text{V}_{\text{CC1}} \leq 3.2~\text{V}$ | 2        |      | 10               | MHz  |

|                                                                     |                        | AN0_0 to AN0_7  | $4.0~\text{V} \leq \text{V}_{\text{CC2}} \leq 5.5~\text{V}$ | 2        |      | 25               | MHz  |

|                                                                     |                        | input, AN2_0 to | $3.2~\text{V} \leq \text{V}_{CC2} \leq 4.0~\text{V}$        | 2        |      | 16               | MHz  |

|                                                                     | AN2_7 input            | AN2_7 input     | $3.0~\text{V} \leq \text{V}_{\text{CC2}} \leq 3.2~\text{V}$ | 2        |      | 10               | MHz  |

| -                                                                   | Tolerance level impe   | dance           |                                                             |          | 3    |                  | kΩ   |

| D <sub>NL</sub>                                                     | Differential non-linea | rity error      | (4)                                                         |          |      | ±1               | LSB  |

| -                                                                   | Offset error           |                 | (4)                                                         |          |      | ±3               | LSB  |

| -                                                                   | Gain error             |                 | (4)                                                         |          |      | ±3               | LSB  |

| t <sub>CONV</sub>                                                   | 10-bit conversion tim  | e               | V <sub>CC1</sub> = 5 V, φAD = 25 MHz                        | 1.60     |      |                  | μS   |

| t <sub>SAMP</sub>                                                   | Sampling time          |                 |                                                             | 0.60     |      |                  | μS   |

| V <sub>REF</sub>                                                    | Reference voltage      |                 |                                                             | 3.0      |      | V <sub>CC1</sub> | V    |

| V <sub>IA</sub>                                                     | Analog input voltage   | (2), (3)        |                                                             | 0        |      | V <sub>REF</sub> | V    |

Notes:

1. Use when  $AV_{CC} = V_{CC1}$ .

2. When  $V_{CC1} \ge V_{CC2}$ , set as below: Analog input voltage (AN0 to AN7, ANEX0, and ANEX1)  $\le V_{CC1}$ Analog input voltage (AN0\_0 to AN0\_7 and AN2\_0 to AN2\_7)  $\le V_{CC2}$ .

- 3. When analog input voltage is over reference voltage, the result of A/D conversion is 3FFh.

- 4. Flash memory rewrite disabled. Except for the analog input pin, set the pins to be measured as input ports and connect them to V<sub>SS</sub>. See Figure 5.2 "A/D Accuracy Measure Circuit".

# 5.1.4 D/A Conversion Characteristics

### Table 5.7 D/A Conversion Characteristics

$V_{CC1} = AV_{CC} = V_{REF} = 3.0$  to 5.5 V,  $V_{SS} = AV_{SS} = 0$  V at  $T_{opr} = -20^{\circ}C$  to 85°C/-40°C to 85°C unless otherwise specified.

| Symbol            | Parameter                            | Measuring Condition                     |      | Unit |      |      |

|-------------------|--------------------------------------|-----------------------------------------|------|------|------|------|

|                   |                                      | Measuring Condition                     | Min. | Тур. | Max. | Unit |

| -                 | Resolution                           |                                         |      |      | 8    | Bits |

| -                 | Absolute Accuracy                    |                                         |      |      | 2.5  | LSB  |

| t <sub>SU</sub>   | Setup Time                           |                                         |      |      | 3    | μS   |

| R <sub>O</sub>    | Output Resistance                    |                                         | 5    | 6    | 8.2  | kΩ   |

| I <sub>VREF</sub> | Reference Power Supply Input Current | See Notes <sup>1</sup> and <sup>2</sup> |      |      | 1.5  | mA   |

Notes:

1. This applies when using one D/A converter, with the D/A register for the unused D/A converter set to 00h.

2. The current consumption of the A/D converter is not included. Also, the I<sub>VREF</sub> of the D/A converter will flow even if the ADSTBY bit in the ADCON1 register is 0 (A/D operation stopped (standby)).

# $V_{CC1} = V_{CC2} = 5 V$

#### Table 5.21

able 5.21 Electrical Characteristics (3) R5F36506NFA, R5F36506NFB, R5F36506DFA, R5F36506DFB, R5F3650ENFA, R5F3650ENFB, R5F3650EDFA, R5F3650EDFB

$V_{CC1} = V_{CC2} = 4.2 \text{ to } 5.5 \text{ V}, V_{SS} = 0 \text{ V at } T_{opr} = -20^{\circ}\text{C to } 85^{\circ}\text{C} / -40^{\circ}\text{C to } 85^{\circ}\text{C}, f_{(BCLK)} = 32 \text{ MHz unless otherwise specified.}$

| Symbol             | Parameter                                                        | Parameter Measuring Condition      |                                                                                                                                                                                                       |      | Standar | d    | Unit  |  |

|--------------------|------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|-------|--|

| -                  |                                                                  |                                    | Measuring contaiton                                                                                                                                                                                   | Min. | Тур.    | Max. | 01110 |  |

| R <sub>fXCIN</sub> | Feedback resistance XCIN                                         |                                    |                                                                                                                                                                                                       |      | 8       |      | MΩ    |  |

| I <sub>CC</sub>    | Power supply current<br>In single-chip, mode,                    | High-speed mode                    | f <sub>(BCLK)</sub> = 32 MHz<br>XIN = 4 MHz (square wave), PLL multiplied by 8<br>125 kHz on-chip oscillator stopped                                                                                  |      | 24.0    |      | mA    |  |

|                    | the output pin are<br>open and other pins<br>are V <sub>SS</sub> |                                    | f <sub>(BCLK)</sub> =32 MHz, A/D conversion<br>XIN = 4 MHz (square wave), PLL multiplied by 8<br>125 kHz on-chip oscillator stopped                                                                   |      | 24.7    |      | mA    |  |

|                    |                                                                  |                                    | f <sub>(BCLK)</sub> = 20 MHz<br>XIN = 20 MHz (square wave)<br>125 kHz on-chip oscillator stopped                                                                                                      |      | 16.0    |      | mA    |  |

|                    |                                                                  | 40 MHz on-chip<br>oscillator mode  | Main clock stopped<br>40 MHz on-chip oscillator on,<br>divide-by-4 (f <sub>(BCLK)</sub> = 10 MHz)<br>125 kHz on-chip oscillator stopped                                                               |      | 17.0    |      | mA    |  |

|                    |                                                                  | 125 kHz on-chip<br>oscillator mode | Main clock stopped<br>40 MHz on-chip oscillator stopped,<br>125 kHz on-chip oscillator on, no division<br>FMR22 = 1 (slow read mode)                                                                  |      | 500.0   |      | μA    |  |

|                    |                                                                  | Low-power mode                     | $f_{(BCLK)} = 32 \text{ kHz}$<br>In low-power mode<br>FMR22 = FMR23 = 1<br>On flash memory <sup>(1)</sup>                                                                                             |      | 160.0   |      | μΑ    |  |

|                    |                                                                  |                                    | f <sub>(BCLK)</sub> = 32 kHz<br>In low-power mode<br>On RAM <sup>(1)</sup>                                                                                                                            |      | 45.0    |      | μA    |  |

|                    |                                                                  | Wait mode                          | Main clock stopped<br>40 MHz on-chip oscillator stopped<br>125 kHz on-chip oscillator on<br>Peripheral clock operating<br>T <sub>opr</sub> = 25°C                                                     |      | 20.0    |      | μΑ    |  |

|                    |                                                                  |                                    | $f_{(BCLK)} = 32 \text{ kHz} \text{ (oscillation capacity High)}$<br>40 MHz on-chip oscillator stopped<br>125 kHz on-chip oscillator stopped<br>Peripheral clock operating<br>$T_{opr} = 25^{\circ}C$ |      | 11.0    |      | μΑ    |  |

|                    |                                                                  |                                    | $f_{(BCLK)} = 32 \text{ kHz}$ (oscillation capacity Low)<br>40 MHz on-chip oscillator stopped<br>125 kHz on-chip oscillator stopped<br>Peripheral clock operating<br>$T_{opr} = 25^{\circ}C$          |      | 6.0     |      | μΑ    |  |

|                    |                                                                  | Stop mode                          | Main clock stopped<br>40 MHz on-chip oscillator stopped<br>125 kHz on-chip oscillator stopped<br>Peripheral clock stopped<br>T <sub>opr</sub> = 25°C                                                  |      | 1.7     |      | μΑ    |  |

|                    |                                                                  | During flash<br>memory program     | f <sub>(BCLK)</sub> = 10 MHz, PM17 = 1 (one wait)<br>V <sub>CC1</sub> = 5.0 V                                                                                                                         |      | 20.0    |      | mA    |  |

|                    |                                                                  | During flash<br>memory erase       | f <sub>(BCLK)</sub> = 10 MHz, PM17 = 1 (one wait)<br>V <sub>CC1</sub> = 5.0 V                                                                                                                         |      | 30.0    |      | mA    |  |

Note: 1.

This indicates the memory in which the program to be executed exists.

# $V_{CC1} = V_{CC2} = 5 V$

#### Table 5.23Electrical Characteristics (5)

R5F3651RNFC, R5F3650RNFA, R5F3650RNFB, R5F3651RDFC, R5F3650RDFA, R5F3650RDFB, R5F3651TNFC, R5F3650TNFA, R5F3650TNFB, R5F3651TDFC, R5F3650TDFA, R5F3650TDFB

$V_{CC1} = V_{CC2} = 4.2$  to 5.5 V,  $V_{SS} = 0$  V at  $T_{opr} = -20$  to 85°C/-40 to 85°C,  $f_{(BCLK)} = 32$  MHz unless otherwise specified.