# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 20x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f340-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 14.5.2.USB Clock Selection       139         15. Port Input/Output       142         15.1.Priority Crossbar Decoder       144         15.2.Port I/O Initialization       147         15.3.General Purpose Port I/O       150         16. Universal Serial Bus Controller (USB0)       159         16.1.Endpoint Addressing       160         16.2.USB Transceiver       160         16.3.USB Register Access       162         16.4.USB Clock Configuration       166         16.5.7.FIFO Management       167         16.5.2.FIFO Double Buffering       168         16.5.2.FIFO Double Buffering       168         16.5.3.FIFO Access       168         16.6.Function Addressing       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       176         16.10.Endpoint0 SETUP Transactions       177         16.10.Endpoint0 IN Transactions       177         16.10.Endpoint0 OUT Transactions       178         16.11.Configuring Endpoints1-3       180         16.12.Endpoint0 IN Transactions       177         16.10.Endpoint1-3 IN Interrupt or Bulk Mode       181         16.13.Lendpoints1-3 IN Interrupt or Bulk Mode       181         16.13.Lendpoints1-3 OUT Interrupt                                                             | 14.5.1.System Clock Selection        | 139 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|

| 15. Port Input/Output.       142         15. 1. Priority Crossbar Decoder       144         15.2. Port I/O Initialization       147         15.3. General Purpose Port I/O.       150         16. Universal Serial Bus Controller (USB0).       159         16.1. Andpoint Addressing       160         16.2. USB Transceiver       160         16.3. USB Register Access       162         16.4. USB Clock Configuration       166         16.5. FIFO Management       167         16.5.2. FIFO Double Buffering       168         16.5.3. FIFO Access       168         16.6. Function Addressing       169         16.7. Function Configuration and Control       169         16.3.0. Endpoint0       172         16.9. The Serial Interface Engine       176         16.10. Endpoint0 IN Transactions       177         16.10.2. Endpoint0 SETUP Transactions       177         16.10.2. Endpoint0 IN Transactions       177         16.10.2. Endpoint0 IN Transactions       177         16.12. Controlling Endpoints1-3 IN       180         16.12. Controlling Endpoints1-3 IN Interrupt or Bulk Mode       181         16.13. Controlling Endpoints1-3 OUT       183         16.13.2. Endpoints1-3 OUT Interrupt or Bulk Mode       183 </td <td></td> <td></td>           |                                      |     |

| 15.1.Priority Crossbar Decoder       144         15.2.Port I/O Initialization       147         15.3.General Purpose Port I/O       150         16. Universal Serial Bus Controller (USB0)       159         16.1.Endpoint Addressing       160         16.2.USB Transceiver       160         16.3.USB Register Access       162         16.4.USB Clock Configuration       166         16.5.FIFO Management       167         16.5.2.FIFO Double Buffering       168         16.5.2.FIFO Access       168         16.6.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       177         16.10.1.Endpoint0 NI Transactions       177         16.10.2.Endpoint0 NI Transactions       177         16.10.2.Endpoint0 NI Transactions       178         16.11.Configuring Endpoints1-3       180         16.12.2.Endpoint0 NI Transactions       178         16.12.Endpoint0 NI Transactions       178         16.12.Endpoint1-3 IN Interrupt or Bulk Mode       180         16.12.Endpoints1-3 IN Interrupt or Bulk Mode       181         16.13.Endpoints1-3 OUT Interrupt or Bulk Mode       183                                                                     |                                      |     |

| 15.2.Port I/O       147         15.3.General Purpose Port I/O       150         16. Universal Serial Bus Controller (USB0)       159         16.1.Endpoint Addressing       160         16.2.USB Transceiver       160         16.3.USB Register Access       162         16.4.USB Clock Configuration       166         16.3.USB Cock Configuration       166         16.5.FIFO Management       167         16.5.2.FIFO Double Buffering       168         16.5.3.FIFO Access       168         16.6.Function Addressing       169         16.7.Function Configuration and Control       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0 SETUP Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.2.Endpoint0 OUT Transactions       177         16.10.2.Endpoints1-3 IN       180         16.12.1.Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.1.Endpoints1-3 OUT Interrupt or Bulk Mode       181         16.13.Controlling Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183     <                                       |                                      |     |

| 15.3.General Purpose Port I/O.       150         16.Universal Serial Bus Controller (USB0).       159         16.1.Endpoint Addressing       160         16.2.USB Transceiver       160         16.3.USB Register Access       162         16.4.USB Clock Configuration       166         16.5.FIFO Management       167         16.5.1.FIFO Split Mode       167         16.5.2.FIFO Access       168         16.6.Function Addressing       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0 SETUP Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.2.Endpoint0 UT Transactions       178         16.11.Configuring Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.Controlling Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       184         17.SMBus       Onfiguration       189 <t< td=""><td></td><td></td></t<>       |                                      |     |

| 16. Universal Serial Bus Controller (USB0)       159         16.1. Endpoint Addressing       160         16.2. USB Transceiver       160         16.3. USB Register Access       162         16.4. USB Clock Configuration       166         16.5. FIFO Management       167         16.5.2. FIFO Double Buffering       168         16.5.2. FIFO Double Buffering       168         16.5.2. FIFO Access       168         16.6. Function Addressing       169         16.7. Inction Configuration and Control       169         16.8. Interrupts       172         16.9. The Serial Interface Engine       176         16.10. Endpoint0       177         16.10.2. Endpoint0 IN Transactions       177         16.10.3. Endpoint0 OUT Transactions       177         16.10.2. Endpoint0 IN Transactions       177         16.10.2. Endpoints1-3 IN       180         16.12.1. Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.2. Endpoints1-3 UT Interrupt or Bulk Mode       181         16.13.2. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2. Endpoints1-3 OUT Interrupt or                          |                                      |     |

| 16.1.Endpoint Addressing       160         16.2.USB Transceiver       160         16.3.USB Register Access       162         16.4.USB Clock Configuration       166         16.5.USB Clock Configuration       166         16.5.FIFO Management       167         16.5.1.FIFO Split Mode       167         16.5.2.FIFO Double Buffering       168         16.5.3.FIFO Access       168         16.6.Function Addressing       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       176         16.10.1.Endpoint0 SETUP Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.3.Endpoint0 OUT Transactions       178         16.11.Configuring Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.Endpoints1-3 IN Isochronous Mode       181         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       184 <td></td> <td></td>                 |                                      |     |

| 16.2.USB Transceiver       160         16.3.USB Register Access       162         16.4.USB Clock Configuration       166         16.5.FIFO Management       167         16.5.1.FIFO Split Mode       167         16.5.2.FIFO Double Buffering       168         16.5.3.FIFO Access       168         16.5.1.FIFO Access       168         16.5.1.FIFO Access       168         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       176         16.10.Endpoint0 IN Transactions       177         16.10.3.Endpoint0 IN Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.3.Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Endpoints1-3 IN Interrupt or Bulk Mode       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       184         17.SMBus       189         17.3.SMBus Configuration       189                                                                     |                                      |     |

| 16.3.USB Register Access       162         16.4.USB Clock Configuration       166         16.5.FIFO Management       167         16.5.FIFO Split Mode       167         16.5.2.FIFO Double Buffering       168         16.5.3.FIFO Access       168         16.5.4.FIFO Mode       167         16.5.3.FIFO Access       168         16.6.Function Addressing       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0 SETUP Transactions       177         16.10.Endpoint0 IN Transactions       177         16.10.Sendpoint0 OUT Transactions       177         16.10.Sendpoint0 OUT Transactions       177         16.11.Configuring Endpoints1-3       180         16.12.Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.Endpoints1-3 IN Interrupt or Bulk Mode       183         16.13.Controlling Endpoints1-3 OUT       183         16.13.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.Endpoints1-3 OUT Interrupt or Bulk Mode       184         17.SMBus Configuration       189         17.2.SMBus Configuration       189         17.3.Arbitration </td <td></td> <td></td>                                     |                                      |     |

| 16.4.USB Clock Configuration       166         16.5.FIFO Management       167         16.5.FIFO Double Buffering       167         16.5.2.FIFO Double Buffering       168         16.5.3.FIFO Access       168         16.5.1.FIFO Access       168         16.5.3.FIFO Access       169         16.7.Function Configuration and Control       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       176         16.10.I.Endpoint0 SETUP Transactions       177         16.10.Lendpoint0 OUT Transactions       177         16.10.Lendpoint0 IN Transactions       177         16.11.Configuring Endpoints1-3 IN       180         16.12.Centrolling Endpoints1-3 IN       180         16.12.Lendpoints1-3 IN Interrupt or Bulk Mode       181         16.13.Controlling Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.Lendpoints1-3 OUT Isochronous Mode       184         17.SMBus       189         17.2.SMBus Onfiguration       189         17.3.Arbitration       190         17.3.1.Arbitration <td></td> <td></td>                                           |                                      |     |

| 16.5.FIFO Management       167         16.5.1.FIFO Split Mode       167         16.5.2.FIFO Double Buffering       168         16.5.2.FIFO Access       168         16.6.Function Addressing       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       176         16.10.Endpoint0 SETUP Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.2.Endpoint0 OUT Transactions       177         16.10.2.Endpoint0 OUT Transactions       177         16.10.2.Endpoint0 OUT Transactions       177         16.10.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 OUT       183         16.13.Controlling Endpoints1-3 OUT       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.12.2.Endpoints1-3 OUT Isochronous Mode       184         17.SMBus Configuration       189         17.3.SMBus Operation       189                                                   | •                                    |     |

| 16.5.1.FIFO Split Mode       167         16.5.2.FIFO Double Buffering       168         16.5.3.FIFO Access       168         16.6.Function Addressing       169         16.7.Function Configuration and Control       169         16.7.Function Configuration and Control       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       176         16.10.1.Endpoint0 SETUP Transactions       177         16.10.2.Endpoint0 OUT Transactions       177         16.10.3.Endpoint0 OUT Transactions       177         16.10.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 IN Interrupt or Bulk Mode       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       184         17.SMBus       189         17.3.SMBus Operation       189         17.3.SMBus Operation       191         17.3.SCL Low Timeout       191         17.4.1.SMBus Configuration Register       192                                                               | •                                    |     |

| 16.5.2.FIFO Double Buffering       168         16.5.3.FIFO Access       168         16.6.Function Addressing       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       176         16.10.1.Endpoint0 NETUP Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.3.Endpoint0 OUT Transactions       177         16.10.2.Endpoint0 UUT Transactions       177         16.10.2.Endpoint0 UUT Transactions       177         16.10.2.Endpoint0 UUT Transactions       177         16.11.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.2.Endpoints1-3 IN Interrupt or Bulk Mode       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       184         17.SMBus       189         17.3.Arbitration       190         17.3.2.Clock Low Extension       191         17.3.4xBus Configuration Register       191         17.4.1.SMBus Configuration Register       192                                  | •                                    |     |

| 16.5.3.FIFO Access       168         16.6.Function Addressing       169         16.7.Function Configuration and Control       169         16.8.Interrupts       172         16.9.The Serial Interface Engine       176         16.10.Endpoint0       176         16.10.1.Endpoint0 SETUP Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.3.Endpoint0 OUT Transactions       177         16.10.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3       180         16.12.Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.Controlling Endpoints1-3 OUT       180         16.13.Controlling Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Isochronous Mode       184 <b>17.SMBus</b> 189         17.3.SMBus Operation       189         17.3.2.Clock Low Extension       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMBOCN Control Register       192         17.4.3.Data Register       198         17.5.1.Master Transmitter Mode       198                                                             |                                      |     |

| 16.6. Function Addressing.       169         16.7. Function Configuration and Control.       169         16.8. Interrupts       172         16.9. The Serial Interface Engine.       176         16.10. Endpoint0       176         16.10.1. Endpoint0 SETUP Transactions       177         16.10.2. Endpoint0 OUT Transactions       177         16.10.3. Endpoint0 OUT Transactions       177         16.10.3. Endpoint0 OUT Transactions       177         16.10.4. Endpoint0 OUT Transactions       177         16.10.3. Endpoint0 OUT Transactions       177         16.10.3. Endpoints 1-3       180         16.12.1. Endpoints 1-3 IN       180         16.12.2. Endpoints 1-3 IN Interrupt or Bulk Mode       180         16.12.2. Endpoints 1-3 OUT       183         16.13.1. Endpoints 1-3 OUT Interrupt or Bulk Mode       183         16.13.2. Endpoints 1-3 OUT Isochronous Mode       184 <b>17. SMBus</b> 189         17.3. Arbitration       190         17.3.2. Clock Low Extension       191         17.3.3. SCL Low Timeout       191         17.4.1. SMBus Configuration Register       192         17.4.2. SMBOCN Control Register       192         17.4.3. Data Register       198                                                                         |                                      |     |

| 16.7. Function Configuration and Control       169         16.8. Interrupts       172         16.9. The Serial Interface Engine       176         16.10. Endpoint0       176         16.10. Endpoint0 SETUP Transactions       177         16.10.1. Endpoint0 SETUP Transactions       177         16.10.2. Endpoint0 IN Transactions       177         16.10.3. Endpoint0 OUT Transactions       177         16.10.2. Endpoint0 OUT Transactions       178         16.11. Configuring Endpoints1-3       180         16.12. Controlling Endpoints1-3 IN       180         16.12. Lendpoints1-3 IN Interrupt or Bulk Mode       180         16.12. Lendpoints1-3 IN Inscription Bulk Mode       183         16.13. Lendpoints1-3 OUT       183         16.13. Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2. Endpoints1-3 OUT Isochronous Mode       184         17. SMBus       189       17.3. SMBus Configuration       189         17.3. SMBus Configuration       189       17.3. Arbitration       190         17.3. SCL Low Extension       191       17.4. SMBus       191         17.4.1. SMBus Configuration Register       192       17.4.2. SMB0CN Control Register       192< |                                      |     |

| 16.8. Interrupts       172         16.9. The Serial Interface Engine       176         16.10. Endpoint0       176         16.10.1. Endpoint0 SETUP Transactions       177         16.10.2. Endpoint0 IN Transactions       177         16.10.3. Endpoint0 OUT Transactions       177         16.10.3. Endpoint0 OUT Transactions       178         16.11. Configuring Endpoints1-3 IN       180         16.12. Controlling Endpoints1-3 IN       180         16.12.1. Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.2. Endpoints1-3 IN Isochronous Mode       181         16.13. Controlling Endpoints1-3 OUT       183         16.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2. Endpoints1-3 OUT Isochronous Mode       184         17. SMBus       189         17.1. Supporting Documents       189         17.3. SMBus Configuration       189         17.3. Arbitration       190         17.3.2. Clock Low Extension       191         17.3.3. SCL Low Timeout       191         17.4.1. SMBus Configuration Register       192         17.4.2. SMBuC Configuration                         | •                                    |     |

| 16.9. The Serial Interface Engine       176         16.10. Endpoint0       176         16.10.1. Endpoint0 SETUP Transactions       177         16.10.2. Endpoint0 IN Transactions       177         16.10.3. Endpoint0 OUT Transactions       177         16.10.3. Endpoint0 OUT Transactions       178         16.11. Configuring Endpoints1-3       180         16.12. Controlling Endpoints1-3 IN       180         16.12.1. Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.2. Endpoints1-3 IN Isochronous Mode       181         16.13. Controlling Endpoints1-3 OUT       183         16.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2. Endpoints1-3 OUT Isochronous Mode       184 <b>17. SMBus</b> 189         17.1. Supporting Documents       189         17.3. SMBus Configuration       189         17.3. Arbitration       190         17.3.2. Clock Low Extension       191         17.4.2. SMBUS Configuration Register       191         17.4.1. SMBus Configuration Register       192         17.4.2. SMBOC N Control Register       192         17.4.2. SMBOC N Control Register       192         17.4.3. Data Re                                  |                                      |     |

| 16.10.Endpoint0       176         16.10.1.Endpoint0 SETUP Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.3.Endpoint0 OUT Transactions       178         16.11.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 OUT       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.LEndpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.LEndpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Isochronous Mode       184 <b>17.SMBus</b> 189         17.1.Supporting Documents       189         17.3.SMBus Configuration       189         17.3.1.Arbitration       190         17.3.2.Clock Low Extension       191         17.4.Using the SMBus       191         17.4.J.SMBus Configuration Register       192         17.4.1.SMBus Configuration Register       192         17.4.2.SMBOCN Control Register       192         17.4.3.Data Register       198                                                           |                                      |     |

| 16.10.1.Endpoint0 SETUP Transactions       177         16.10.2.Endpoint0 IN Transactions       177         16.10.3.Endpoint0 OUT Transactions       178         16.11.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Controlling Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.Endpoints1-3 IN Interrupt or Bulk Mode       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         17.SMBus       189         17.1.Supporting Documents       189         17.3.SMBus Configuration       189         17.3.LArbitration       190         17.3.2.Clock Low Extension       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMBOCN Control Register       192         17.4.2.SMBUC Notrol Register       192         17.4.2.SMBUC Notrol Register       198         17.5.SMBus T                         |                                      |     |

| 16.10.2.Endpoint0 IN Transactions       177         16.10.3.Endpoint0 OUT Transactions       178         16.11.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3 IN       180         16.12.Lendpoints1-3 IN Interrupt or Bulk Mode       180         16.12.Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.Endpoints1-3 IN Isochronous Mode       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Isochronous Mode       184 <b>17. SMBus</b> 188         17.1.Supporting Documents       189         17.3.SMBus Configuration       189         17.3.2.Clock Low Extension       191         17.3.3.SCL Low Timeout       191         17.4.SMBus       191         17.4.SMBus Configuration Register       192         17.4.SMBus Configuration Register       192         17.4.SMBus Configuration Register       192         17.4.3.Data Register       198         17.5.MBus Transfer Modes       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                     | 16.10.1.Endpoint0 SETUP Transactions | 177 |

| 16.10.3.Endpoint0 OUT Transactions       178         16.11.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3 IN       180         16.12.I.Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.Endpoints1-3 IN Isochronous Mode       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.Lendpoints1-3 OUT       183         16.13.Lendpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Isochronous Mode       184 <b>17. SMBus 188</b> 17.1.Supporting Documents       189         17.2.SMBus Configuration       189         17.3.SMBus Operation       189         17.3.2.Clock Low Extension       191         17.3.4.SCL Low Timeout       191         17.4.SMBus       191         17.4.SMBus Configuration Register       192         17.4.1.SMBus Configuration Register       192         17.4.2.SMBOCN Control Register       195         17.4.3.Data Register       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                           |                                      |     |

| 16.11.Configuring Endpoints1-3       180         16.12.Controlling Endpoints1-3 IN       180         16.12.1.Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.2.Endpoints1-3 IN Isochronous Mode       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Isochronous Mode       184 <b>17.SMBus</b> 188         17.1.Supporting Documents       189         17.3.SMBus Operation       189         17.3.LArbitration       190         17.3.2.Clock Low Extension       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.Using the SMBus       191         17.4.SMBus Configuration Register       192         17.4.2.SMB0CN Control Register       193         17.5.SMBus Transfer Modes       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                              |                                      |     |

| 16.12.Controlling Endpoints1-3 IN       180         16.12.1.Endpoints1-3 IN Interrupt or Bulk Mode       180         16.12.2.Endpoints1-3 IN Isochronous Mode       181         16.13.Controlling Endpoints1-3 OUT       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Isochronous Mode       184 <b>17.SMBus</b> 188         17.1.Supporting Documents       189         17.2.SMBus Configuration       189         17.3.SMBus Operation       189         17.3.2.Clock Low Extension       191         17.3.3.SCL Low Timeout       191         17.4.Using the SMBus       191         17.4.SMBUS Configuration Register       192         17.4.2.SMBOCN Control Register       192         17.4.3.Data Register       198         17.5.SMBus Transfer Modes       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                               |                                      |     |

| 16.12.1.Endpoints1-3 IN Interrupt or Bulk Mode.       180         16.12.2.Endpoints1-3 IN Isochronous Mode.       181         16.13.Controlling Endpoints1-3 OUT.       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode.       183         16.13.2.Endpoints1-3 OUT Isochronous Mode.       184         17.SMBus       188         17.1.Supporting Documents.       189         17.2.SMBus Configuration.       189         17.3.SMBus Operation       189         17.3.1.Arbitration.       190         17.3.2.Clock Low Extension.       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.Using the SMBus.       191         17.4.2.SMBOCN Control Register       192         17.4.2.SMBus Transfer Modes.       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |     |

| 16.12.2.Endpoints1-3 IN Isochronous Mode.       181         16.13.Controlling Endpoints1-3 OUT.       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode.       183         16.13.2.Endpoints1-3 OUT Isochronous Mode.       184         17.SMBus       184         17.SMBus       189         17.1.Supporting Documents.       189         17.3.SMBus Configuration.       189         17.3.SMBus Operation       189         17.3.2.Clock Low Extension.       191         17.3.3.SCL Low Timeout.       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMBOCN Control Register       195         17.4.3.Data Register       198         17.5.MBus Transfer Modes       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      |     |

| 16.13.Controlling Endpoints1-3 OUT       183         16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Isochronous Mode       184 <b>17.SMBus</b> 188         17.1.Supporting Documents       189         17.2.SMBus Configuration       189         17.3.SMBus Operation       189         17.3.1.Arbitration       190         17.3.2.Clock Low Extension       191         17.3.3.SCL Low Timeout       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMBOCN Control Register       192         17.4.3.Data Register       198         17.5.SMBus Transfer Modes       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      |     |

| 16.13.1.Endpoints1-3 OUT Interrupt or Bulk Mode       183         16.13.2.Endpoints1-3 OUT Isochronous Mode       184 <b>17.SMBus</b> 188         17.1.Supporting Documents       189         17.2.SMBus Configuration       189         17.3.SMBus Operation       189         17.3.1.Arbitration       190         17.3.2.Clock Low Extension       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMB0CN Control Register       195         17.4.3.Data Register       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |     |

| 16.13.2.Endpoints1-3 OUT Isochronous Mode.       184         17.SMBus       189         17.1.Supporting Documents.       189         17.2.SMBus Configuration.       189         17.3.SMBus Operation       189         17.3.1.Arbitration.       190         17.3.2.Clock Low Extension.       191         17.3.3.SCL Low Timeout.       191         17.4.Using the SMBus.       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMB0CN Control Register       195         17.4.3.Data Register       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |     |

| 17. SMBus       188         17.1. Supporting Documents       189         17.2. SMBus Configuration       189         17.3. SMBus Operation       189         17.3.1. Arbitration       190         17.3.2. Clock Low Extension       191         17.3.3. SCL Low Timeout       191         17.3.4. SCL High (SMBus Free) Timeout       191         17.4.Using the SMBus       191         17.4.1. SMBus Configuration Register       192         17.4.2. SMB0CN Control Register       195         17.4.3. Data Register       198         17.5. SMBus Transfer Modes       198         17.5.1. Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |     |

| 17.1.Supporting Documents       189         17.2.SMBus Configuration       189         17.3.SMBus Operation       189         17.3.SMBus Operation       189         17.3.1.Arbitration       190         17.3.2.Clock Low Extension       191         17.3.3.SCL Low Timeout       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.Using the SMBus       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMB0CN Control Register       195         17.4.3.Data Register       198         17.5.SMBus Transfer Modes       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |     |

| 17.2.SMBus Configuration.       189         17.3.SMBus Operation       189         17.3.SMBus Operation       190         17.3.1.Arbitration       190         17.3.2.Clock Low Extension       191         17.3.3.SCL Low Timeout       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.Using the SMBus       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMB0CN Control Register       195         17.4.3.Data Register       198         17.5.SMBus Transfer Modes       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |     |

| 17.3.SMBus Operation       189         17.3.1.Arbitration       190         17.3.2.Clock Low Extension       191         17.3.3.SCL Low Timeout       191         17.3.4.SCL High (SMBus Free) Timeout       191         17.4.Using the SMBus       191         17.4.1.SMBus Configuration Register       192         17.4.2.SMB0CN Control Register       195         17.4.3.Data Register       198         17.5.SMBus Transfer Modes       198         17.5.1.Master Transmitter Mode       198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      |     |

| 17.3.1.Arbitration19017.3.2.Clock Low Extension19117.3.3.SCL Low Timeout19117.3.4.SCL High (SMBus Free) Timeout19117.4.Using the SMBus19117.4.1.SMBus Configuration Register19217.4.2.SMB0CN Control Register19517.4.3.Data Register19817.5.SMBus Transfer Modes19817.5.1.Master Transmitter Mode198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |     |

| 17.3.2.Clock Low Extension19117.3.3.SCL Low Timeout19117.3.4.SCL High (SMBus Free) Timeout19117.4.Using the SMBus19117.4.1.SMBus Configuration Register19217.4.2.SMB0CN Control Register19517.4.3.Data Register19817.5.SMBus Transfer Modes19817.5.1.Master Transmitter Mode198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                    |     |

| 17.3.3.SCL Low Timeout.19117.3.4.SCL High (SMBus Free) Timeout19117.4.Using the SMBus.19117.4.1.SMBus Configuration Register19217.4.2.SMB0CN Control Register19517.4.3.Data Register19817.5.SMBus Transfer Modes19817.5.1.Master Transmitter Mode198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |     |

| 17.3.4.SCL High (SMBus Free) Timeout19117.4.Using the SMBus19117.4.1.SMBus Configuration Register19217.4.2.SMB0CN Control Register19517.4.3.Data Register19817.5.SMBus Transfer Modes19817.5.1.Master Transmitter Mode198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      |     |

| 17.4.Using the SMBus19117.4.1.SMBus Configuration Register19217.4.2.SMB0CN Control Register19517.4.3.Data Register19817.5.SMBus Transfer Modes19817.5.1.Master Transmitter Mode198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      |     |

| 17.4.1.SMBus Configuration Register19217.4.2.SMB0CN Control Register19517.4.3.Data Register19817.5.SMBus Transfer Modes19817.5.1.Master Transmitter Mode198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |     |

| 17.4.2.SMB0CN Control Register19517.4.3.Data Register19817.5.SMBus Transfer Modes19817.5.1.Master Transmitter Mode198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |     |

| 17.4.3.Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |     |

| 17.5.SMBus Transfer Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                    |     |

| 17.5.1.Master Transmitter Mode 198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17.5.2.Master Receiver Mode          |     |

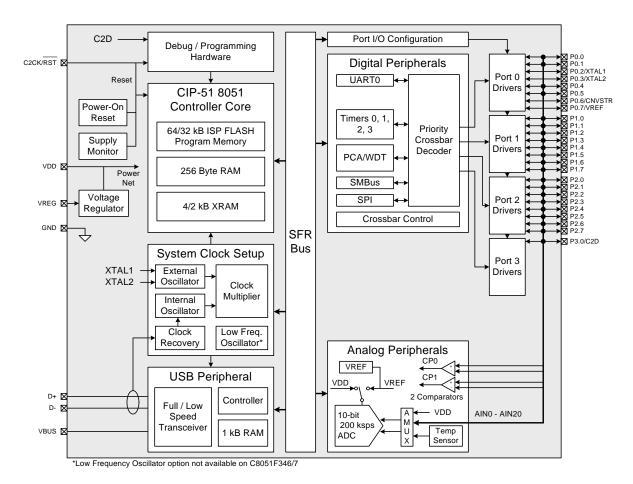

### 1. System Overview

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 48 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Universal Serial Bus (USB) Function Controller with eight flexible endpoint pipes, integrated transceiver, and 1 kB FIFO RAM

- Supply Voltage Regulator

- True 10-bit 200 ksps differential / single-ended ADC with analog multiplexer

- On-chip Voltage Reference and Temperature Sensor

- On-chip Voltage Comparators (2)

- Precision internal calibrated 12 MHz internal oscillator and 4x clock multiplier

- Internal low-frequency oscillator for additional power savings

- Up to 64 kB of on-chip Flash memory

- Up to 4352 Bytes of on-chip RAM (256 + 4 kB)

- External Memory Interface (EMIF) available on 48-pin versions.

- SMBus/I2C, up to 2 UARTs, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

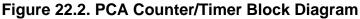

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Missing Clock Detector

- Up to 40 Port I/O (5 V tolerant)

With on-chip Power-On Reset, V<sub>DD</sub> monitor, Voltage Regulator, Watchdog Timer, and clock oscillator, C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

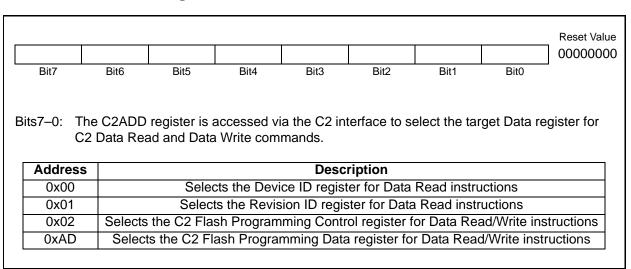

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 2.7–5.25 V operation over the industrial temperature range (-40 to +85 °C). For voltages above 3.6 V, the on-chip Voltage Regulator must be used. A minimum of 3.0 V is required for USB communication. The Port I/O and RST pins are tolerant of input signals up to 5 V. C8051F340/1/2/3/ 4/5/6/7/8/9/A/B/C/D devices are available in 48-pin TQFP, 32-pin LQFP, or 32-pin QFN packages. See Table 1.1, "Product Selection Guide," on page 18 for feature and package choices.

| Ordering Part Number | MIPS (Peak) | Flash Memory (Bytes) | RAM  | Calibrated Internal Oscillator | Low Frequency Oscillator | USB with 1k Endpoint RAM | Supply Voltage Regulator | SMBus/I2C    | Enhanced SPI | UARTs | Timers (16-bit) | Programmable Counter Array | Digital Port I/Os | External Memory Interface (EMIF) | 10-bit 200 ksps ADC | Temperature Sensor | Voltage Reference | Analog Comparators | Package |

|----------------------|-------------|----------------------|------|--------------------------------|--------------------------|--------------------------|--------------------------|--------------|--------------|-------|-----------------|----------------------------|-------------------|----------------------------------|---------------------|--------------------|-------------------|--------------------|---------|

| C8051F340-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | TQFP48  |

| C8051F341-GQ         | 48          | 32k                  | 2304 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | TQFP48  |

| C8051F342-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F342-GM         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F343-GQ         | 48          | 32k                  | 2304 | $\checkmark$                   | ~                        | ~                        | ~                        | $\checkmark$ | $\checkmark$ | 1     | 4               | ~                          | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F343-GM         | 48          | 32k                  | 2304 | $\checkmark$                   | ~                        | ~                        | ~                        | $\checkmark$ | $\checkmark$ | 1     | 4               | ~                          | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F344-GQ         | 25          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | TQFP48  |

| C8051F345-GQ         | 25          | 32k                  | 2304 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | TQFP48  |

| C8051F346-GQ         | 25          | 64k                  | 4352 | $\checkmark$                   | —                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F346-GM         | 25          | 64k                  | 4352 | $\checkmark$                   | —                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | _                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F347-GQ         | 25          | 32k                  | 2304 | $\checkmark$                   | _                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F347-GM         | 25          | 32k                  | 2304 | $\checkmark$                   | _                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | _                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F348-GQ         | 25          | 32k                  | 2304 | $\checkmark$                   | ~                        | ~                        | $\checkmark$             | <            | $\checkmark$ | 2     | 4               | ~                          | 40                | $\checkmark$                     |                     | _                  | _                 | 2                  | TQFP48  |

| C8051F349-GQ         | 25          | 32k                  | 2304 | $\checkmark$                   | ~                        | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | _                                |                     | —                  | _                 | 2                  | LQFP32  |

| C8051F349-GM         | 25          | 32k                  | 2304 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | _                                |                     | —                  | —                 | 2                  | QFN32   |

| C8051F34A-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 25                | _                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F34A-GM         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 25                | _                                | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | QFN32   |

| C8051F34B-GQ         | 48          | 32k                  | 2304 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 25                |                                  | $\checkmark$        | $\checkmark$       | $\checkmark$      | 2                  | LQFP32  |

| C8051F34B-GM         | 48          | 32k                  | 2304 | ~                              | ~                        | ~                        | ~                        | $\checkmark$ | ~            | 2     | 4               | ~                          | 25                | _                                | $\checkmark$        | ~                  | ~                 | 2                  | QFN32   |

| C8051F34C-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 2     | 4               | $\checkmark$               | 40                | $\checkmark$                     | _                   |                    |                   | 2                  | TQFP48  |

| C8051F34D-GQ         | 48          | 64k                  | 4352 | $\checkmark$                   | $\checkmark$             | $\checkmark$             | $\checkmark$             | $\checkmark$ | $\checkmark$ | 1     | 4               | $\checkmark$               | 25                | —                                | _                   | —                  | —                 | 2                  | LQFP32  |

Table 1.1. Product Selection Guide

### 14.3.3. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 14.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$$f = \frac{1.23(10^3)}{\text{RC}} = \frac{1.23(10^3)}{[246 \times 50]} = 0.1 \text{ MHz} = 100 \text{ kHz}$$

Referring to the table in SFR Definition 14.4, the required XFCN setting is 010b. Programming XFCN to a higher setting in RC mode will improve frequency accuracy at an increased external oscillator supply current.

### 14.3.4. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 14.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation from the equations below. Assume  $V_{DD} = 3.0$  V and C = 50 pF:

$$f = \frac{KF}{(C \times V_{DD})} = \frac{KF}{(50 \text{ x } 3)\text{MHz}}$$

$$f = \frac{KF}{150 \text{ MHz}}$$

If a frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 14.4 as KF = 22:

$$f = \frac{22}{150} = 0.146$$

MHz, or 146 kHz

Therefore, the XFCN value to use in this example is 011b.

136

| SFR Definition | 15.8. P1: | Port1 Latch |

|----------------|-----------|-------------|

|----------------|-----------|-------------|

| R/W      | R/W<br>P1.6                                                                                                                 | R/W<br>P1.5                                                              | R/W<br>P1.4                               | R/W<br>P1.3                  | R/W<br>P1.2 | R/W<br>P1.1  | R/W<br>P1.0           | Reset Value<br>11111111 |

|----------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------|------------------------------|-------------|--------------|-----------------------|-------------------------|

| Bit7     | Bit6                                                                                                                        | Bit5                                                                     | Bit4                                      | Bit3                         | Bit2        | Bit1<br>(bit | Bit0<br>t addressable | SFR Address:<br>0x90    |

| Bits7–0: | P1.[7:0]<br>Write - Outp<br>0: Logic Low<br>1: Logic Higl<br>Read - Alwa<br>pin when co<br>0: P1.n pin is<br>1: P1.n pin is | / Output.<br>h Output (hi<br>ys reads '0'<br>nfigured as<br>s logic low. | gh impedar<br>if selected<br>digital inpu | nce if corres<br>as analog i | ponding P1  | MDOUT.n l    | bit = 0).             |                         |

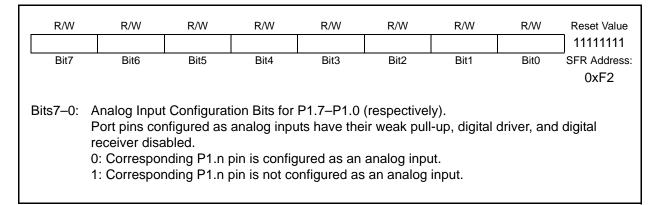

### SFR Definition 15.9. P1MDIN: Port1 Input Mode

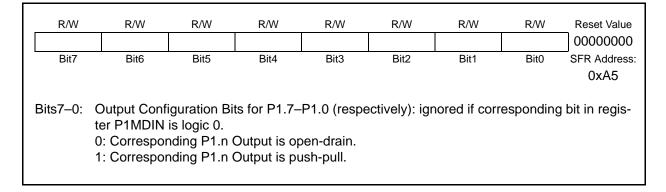

### SFR Definition 15.10. P1MDOUT: Port1 Output Mode

| R/W                                                                                                                                                                                                                                                                                                                                                                                  | R/W  | R/W  | R/W   | R/W  | R/W  | R/W  | R/W  | Reset Value |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|------|------|------|-------------|--|--|--|