# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25К х 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 20x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f341-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

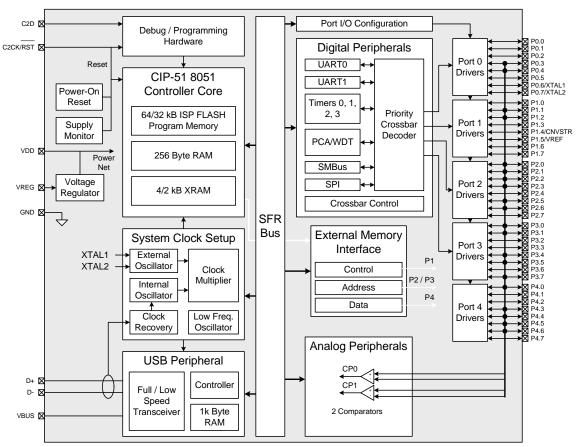

Figure 1.3. C8051F348/C Block Diagram

## C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

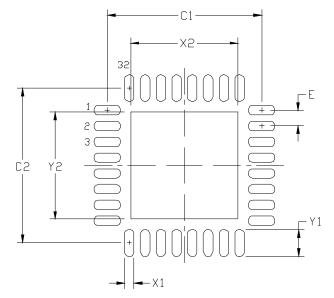

Figure 4.9. QFN-32 Recommended PCB Land Pattern

| Dimension | Min  | Max  |

|-----------|------|------|

| C1        | 4.80 | 4.90 |

| C2        | 4.80 | 4.90 |

| E         | 0.50 | BSC  |

| X1        | 0.20 | 0.30 |

| Dimension | Min  | Max  |

|-----------|------|------|

| X2        | 3.20 | 3.40 |

| Y1        | 0.75 | 0.85 |

| Y2        | 3.20 | 3.40 |

#### Notes:

#### General:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design:

All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60µm minimum, all the way around the pad.

#### Stencil Design:

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- **7.** A 3x3 array of 1.0 mm openings on a 1.2mm pitch should be used for the center pad to assure the proper paste volume.

#### Card Assembly:

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

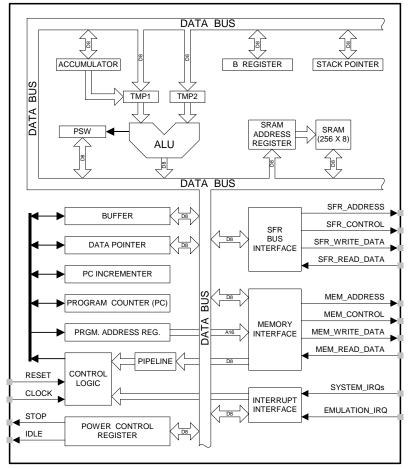

## 9. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are four 16-bit counter/timers (see description in **Section 21**), an enhanced full-duplex UART (see description in **Section 18**), an Enhanced SPI (see description in **Section 20**), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (**Section 9.2.6**), and 25 Port I/O (see description in **Section 15**). The CIP-51 also includes on-chip debug hardware (see description in **Section 23**), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 9.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 0 to 48 MHz Clock Frequency

- 256 Bytes of Internal RAM

- 25 Port I/O

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

## Figure 9.1. CIP-51 Block Diagram

## Table 9.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | Description                       | Page |

|----------|---------|-----------------------------------|------|

| P1MDIN   | 0xF2    | Port 1 Input Mode Configuration   | 152  |

| P1MDOUT  | 0xA5    | Port 1 Output Mode Configuration  | 152  |

| P1SKIP   | 0xD5    | Port 1 Skip                       | 153  |

| P2       | 0xA0    | Port 2 Latch                      | 153  |

| P2MDIN   | 0xF3    | Port 2 Input Mode Configuration   | 153  |

| P2MDOUT  | 0xA6    | Port 2 Output Mode Configuration  | 154  |

| P2SKIP   | 0xD6    | Port 2 Skip                       | 154  |

| P3       | 0xB0    | Port 3 Latch                      | 155  |

| P3MDIN   | 0xF4    | Port 3 Input Mode Configuration   | 155  |

| P3MDOUT  | 0xA7    | Port 3 Output Mode Configuration  | 155  |

| P3SKIP   | 0xDF    | Port 3Skip                        | 156  |

| P4       | 0xC7    | Port 4 Latch                      | 156  |

| P4MDIN   | 0xF5    | Port 4 Input Mode Configuration   | 157  |

| P4MDOUT  | 0xAE    | Port 4 Output Mode Configuration  | 157  |

| PCA0CN   | 0xD8    | PCA Control                       | 266  |

| PCA0CPH0 | 0xFC    | PCA Capture 0 High                | 270  |

| PCA0CPH1 | 0xEA    | PCA Capture 1 High                | 270  |

| PCA0CPH2 | 0xEC    | PCA Capture 2 High                | 270  |

| PCA0CPH3 | 0xEE    | PCA Capture 3High                 | 270  |

| PCA0CPH4 | 0xFE    | PCA Capture 4 High                | 270  |

| PCA0CPL0 | 0xFB    | PCA Capture 0 Low                 | 269  |

| PCA0CPL1 | 0xE9    | PCA Capture 1 Low                 | 269  |

| PCA0CPL2 | 0xEB    | PCA Capture 2 Low                 | 269  |

| PCA0CPL3 | 0xED    | PCA Capture 3 Low                 | 269  |

| PCA0CPL4 | 0xFD    | PCA Capture 4 Low                 | 269  |

| PCA0CPM0 | 0xDA    | PCA Module 0 Mode Register        | 268  |

| PCA0CPM1 | 0xDB    | PCA Module 1 Mode Register        | 268  |

| PCA0CPM2 | 0xDC    | PCA Module 2 Mode Register        | 268  |

| PCA0CPM3 | 0xDD    | PCA Module 3 Mode Register        | 268  |

| PCA0CPM4 | 0xDE    | PCA Module 4 Mode Register        | 268  |

| PCA0H    | 0xFA    | PCA Counter High                  | 269  |

| PCA0L    | 0xF9    | PCA Counter Low                   | 269  |

| PCA0MD   | 0xD9    | PCA Mode                          | 267  |

| PCON     | 0x87    | Power Control                     | 98   |

| PFE0CN   | 0xAF    | Prefetch Engine Control           | 99   |

| PSCTL    | 0x8F    | Program Store R/W Control         | 112  |

| PSW      | 0xD0    | Program Status Word               | 87   |

| REF0CN   | 0xD1    | Voltage Reference Control         | 58   |

| REG0CN   | 0xC9    | Voltage Regulator Control         | 72   |

| RSTSRC   | 0xEF    | Reset Source Configuration/Status | 105  |

| SBCON1   | 0xAC    | UART1 Baud Rate Generator Control | 220  |

| SBRLH1   | 0xB5    | UART1 Baud Rate Generator High    | 221  |

| SBRLL1   | 0xB4    | UART1 Baud Rate Generator Low     | 221  |

| SBUF1    | 0xD3    | UART1 Data Buffer                 | 220  |

| SCON1    | 0xD2    | UART1 Control                     | 218  |

| SFR Definition 9.11. EIE2: Extended Interrupt Enable 2 |

|--------------------------------------------------------|

|--------------------------------------------------------|

| R/W                        | R/W                                                                                                                                       | R/W                                                                                             | R/W                                                                        | R/W                                | R/W       | R/W  | R/W   | Reset Value  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------|-----------|------|-------|--------------|

| -                          | -                                                                                                                                         | -                                                                                               | -                                                                          | -                                  | -         | ES1  | EVBUS | 00000000     |

| Bit7                       | Bit6                                                                                                                                      | Bit5                                                                                            | Bit4                                                                       | Bit3                               | Bit2      | Bit1 | Bit0  | SFR Address: |

|                            |                                                                                                                                           |                                                                                                 |                                                                            |                                    |           |      |       | 0xE7         |

| Bits7–2:<br>Bit1:<br>Bit0: | UNUSED. R<br>ES1: Enable<br>This bit sets<br>0: Disable U<br>1: Enable U<br>EVBUS: Ena<br>This bit sets<br>0: Disable al<br>1: Enable int | UART1 Int<br>the maskin<br>ART1 intern<br>ART1 intern<br>able VBUS<br>the maskin<br>I VBUS inte | errupt.<br>g of the UA<br>upt.<br>Level Interri<br>g of the VB<br>errupts. | RT1 interru<br>upt.<br>US interrup | pt.<br>t. | ISE. |       |              |

## SFR Definition 9.12. EIP2: Extended Interrupt Priority 2

| R/W                        | R/W                                                                                                                                     | R/W                                                                                                          | R/W                                                                                                         | R/W                                                                                            | R/W  | R/W  | R/W   | Reset Value  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|-------|--------------|

| -                          | -                                                                                                                                       | -                                                                                                            | -                                                                                                           | -                                                                                              | -    | PS1  | PVBUS | 0000000      |

| Bit7                       | Bit6                                                                                                                                    | Bit5                                                                                                         | Bit4                                                                                                        | Bit3                                                                                           | Bit2 | Bit1 | Bit0  | SFR Address: |

|                            |                                                                                                                                         |                                                                                                              |                                                                                                             |                                                                                                |      |      |       | 0xF7         |

| Bits7–2:<br>Bit1:<br>Bit0: | UNUSED. R<br>PS1: UART1<br>This bit sets<br>0: UART1 int<br>1: UART1 int<br>PVBUS: VBU<br>This bit sets<br>0: VBUS inte<br>1: VBUS inte | Interrupt F<br>the priority<br>terrupt set t<br>terrupts set<br>JS Level In<br>the priority<br>errupt set to | Priority Cont<br>of the UAR<br>o low priorit<br>to high prior<br>terrupt Prio<br>of the VBU<br>low priority | rol.<br>T1 interrupt<br>ty level.<br>prity level.<br>rity Control.<br>S interrupt.<br>y level. |      |      |       |              |

## 11.8. Software Reset

Software may force a reset by writing a '1' to the SWRSF bit (RSTSRC.4). The SWRSF bit will read '1' following a software forced reset. The state of the RST pin is unaffected by this reset.

## 11.9. USB Reset

Writing '1' to the USBRSF bit in register RSTSRC selects USB0 as a reset source. With USB0 selected as a reset source, a system reset will be generated when either of the following occur:

- 1. RESET signaling is detected on the USB network. The USB Function Controller (USB0) must be enabled for RESET signaling to be detected. See **Section "16. Universal Serial Bus Controller (USB0)" on page 159** for information on the USB Function Controller.

- 2. The voltage on the VBUS pin matches the polarity selected by the VBPOL bit in register REG0CN. See Section "8. Voltage Regulator (REG0)" on page 69 for details on the VBUS detection circuit.

The USBRSF bit will read '1' following a USB reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

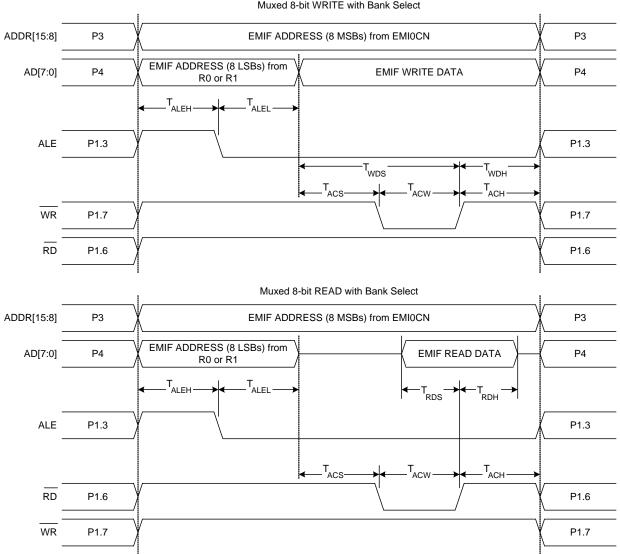

#### 13.7.1.3.8-bit MOVX with Bank Select: EMI0CF[4:2] = '110'.

Muxed 8-bit WRITE with Bank Select

Figure 13.7. Non-multiplexed 8-bit MOVX with Bank Select Timing

| R/W                         | R/W                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                           | R/W                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                           | R/W                                                                                                                         | R/W                                                                                                                        | R/W                                                                                                      | Reset Value                                                                            |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| BUSY                        |                                                                                                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                           | <b>K</b> /W                                                                                                                                                                                                                                         |                                                                                                                                                                                                                               |                                                                                                                             | R/W                                                                                                                        | K/ VV                                                                                                    |                                                                                        |

|                             |                                                                                                                                                                                                                                                                                                                                                     | Dite                                                                                                                                                                                                                          | Ditt                                                                                                                                                                                                                                                |                                                                                                                                                                                                                               |                                                                                                                             | D'14                                                                                                                       | D'10                                                                                                     | 0000000                                                                                |

| Bit7                        | Bit6                                                                                                                                                                                                                                                                                                                                                | Bit5                                                                                                                                                                                                                          | Bit4                                                                                                                                                                                                                                                | Bit3                                                                                                                                                                                                                          | Bit2                                                                                                                        | Bit1                                                                                                                       | Bit0                                                                                                     | SFR Address:                                                                           |

|                             |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |                                                                                                                             |                                                                                                                            |                                                                                                          | 0x96                                                                                   |

| Bits7:<br>Bit6:<br>Bits5–0: | BUSY: USB0<br>This bit is user<br>initiate a read<br>target address<br>set to '1', hard<br>USB0DAT reg<br>Write:<br>0: No effect.<br>1: A USB0 ind<br>Read:<br>0: USB0DAT r<br>1: USB0 is bu<br>AUTORD: US<br>This bit is use<br>0: BUSY must<br>1: The next in<br>USB0DAT (US<br>USBADDR: U<br>These bits hol<br>lists the USB0<br>will target the | d during ir<br>of the US<br>s and BUS<br>ware will<br>jister. Soft<br>lirect regis<br>register da<br>sy access<br>B0 Regis<br>d for bloc<br>t be writte<br>direct regis<br>SBADDR<br>SB0 Indir<br>d a 6-bit a<br>) core regis | adirect USB<br>B0 register<br>SY bit may b<br>clear BUSY<br>ware shoul<br>ster read is<br>ata is valid.<br>sing an indir<br>ter Auto-reat<br>k FIFO reat<br>n manually<br>ster read w<br>bits will not<br>ect Registe<br>ddress use<br>sters and th | 0 register ad<br>targeted by<br>be written in<br>' when the t<br>d check BU<br>initiated at t<br>rect register<br>ad Flag<br>ds.<br>for each US<br>ill automatic<br>be changed<br>r Address<br>d to indirect<br>heir indirect | the USBAI<br>the same v<br>argeted reg<br>SY for '0' be<br>he address<br>(USB0DAT<br>SB0 indirect<br>cally be initia<br>d). | DDR bits (U<br>vrite to USE<br>ister data is<br>efore writing<br>specified b<br>register da<br>register rea<br>ated when s | ISB0ADR.<br>B0ADR. Af<br>s ready in t<br>g to USB0I<br>by the USB<br>ta is invali-<br>ad.<br>software re | [5-0]). The<br>ter BUSY is<br>the<br>DAT.<br>ADDR bits.<br>d.<br>eads<br>s. Table 16.2 |

mode feature of the internal oscillator.

USB0 exits Suspend mode when any of the following occur: (1) Resume signaling is detected or generated, (2) Reset signaling is detected, or (3) a device or USB reset occurs. If suspended, the internal oscillator will exit Suspend mode upon any of the above listed events.

**Resume Signaling:** USB0 will exit Suspend mode if Resume signaling is detected on the bus. A Resume interrupt will be generated upon detection if enabled (RESINTE = '1'). Software may force a Remote Wakeup by writing '1' to the RESUME bit (POWER.2). When forcing a Remote Wakeup, software should write RESUME = '0' to end Resume signaling 10-15 ms after the Remote Wakeup is initiated (RESUME = '1').

**ISO Update:** When software writes '1' to the ISOUP bit (POWER.7), the ISO Update function is enabled. With ISO Update enabled, new packets written to an ISO IN endpoint will not be transmitted until a new Start-Of-Frame (SOF) is received. If the ISO IN endpoint receives an IN token before a SOF, USB0 will transmit a zero-length packet. When ISOUP = '1', ISO Update is enabled for all ISO endpoints.

**USB Enable:** USB0 is disabled following a Power-On-Reset (POR). USB0 is enabled by clearing the USBINH bit (POWER.4). Once written to '0', the USBINH can only be set to '1' by one of the following: (1) a Power-On-Reset (POR), or (2) an asynchronous USB0 reset generated by writing '1' to the USBRST bit (POWER.3).

Software should perform all USB0 configuration before enabling USB0. The configuration sequence should be performed as follows:

- Step 1. Select and enable the USB clock source.

- Step 2. Reset USB0 by writing USBRST= '1'.

- Step 3. Configure and enable the USB Transceiver.

- Step 4. Perform any USB0 function configuration (interrupts, Suspend detect).

- Step 5. Enable USB0 by writing USBINH =  $0^{\circ}$ .

## USB Register Definition 16.8. POWER: USB0 Power

| R/W   | R/W                             | R/W          | R/W           | R/W           | R/W             | R            | R/W           | Reset Value        |

|-------|---------------------------------|--------------|---------------|---------------|-----------------|--------------|---------------|--------------------|

| ISOUD | -                               | -            | USBINH        | USBRST        | RESUME          | SUSMD        | SUSEN         | 00010000           |

| Bit7  | Bit6                            | Bit5         | Bit4          | Bit3          | Bit2            | Bit1         | Bit0          | USB Addres<br>0x01 |

| Bit7: | ISOUD: ISO                      | •            |               |               |                 |              |               |                    |

|       | This bit affect                 |              |               |               |                 |              |               |                    |

|       | 0: When soft                    | ware write   | s INPRDY =    | : '1', USB0 \ | vill send the   | packet wh    | en the next   | IN token is        |

|       | received.<br>1: When soft       | ware write   | s INPRDY -    | - '1' USB0 y  | will wait for a | a SOE toke   | n hefore se   | anding the         |

|       | packet. If an                   |              |               |               |                 |              |               |                    |

|       | ,<br>packet.                    |              |               |               | ,               |              |               | 0                  |

|       | Unused. Rea                     |              | Vrite = don't | care.         |                 |              |               |                    |

| Bit4: | USBINH: US                      |              |               |               |                 |              |               | react (coo         |

|       | This bit is se<br>Bit3: RESET   |              |               |               |                 |              |               |                    |

|       | complete. So                    | ,            |               |               |                 |              |               | 1201101113         |

|       | 0: USB0 ena                     |              |               |               |                 |              |               |                    |

|       | 1: USB0 inhi                    |              |               | ignored.      |                 |              |               |                    |

| Bit3: | USBRST: Re                      |              |               |               |                 |              | 1.26 1.1.     |                    |

|       | Writing '1' to status inform    |              | ces an asynd  | chronous U    | SBU reset. H    | ceading this | s bit provide | es dus rese        |

|       | Read:                           |              |               |               |                 |              |               |                    |

|       | 0: Reset sigr                   | naling is no | ot present or | n the bus.    |                 |              |               |                    |

|       | 1: Reset sigr                   |              |               | bus.          |                 |              |               |                    |

| Bit2: | RESUME: F                       |              |               |               |                 |              |               |                    |

|       | Software car<br>a '1' to this b |              |               |               |                 |              |               |                    |

|       | naling on the                   |              |               |               |                 |              |               |                    |

|       | 10 ms to15 r                    |              |               |               |                 |              |               |                    |

|       | SUSMD, wh                       |              |               | SUME = '0'.   |                 |              |               |                    |

| Bit1: | SUSMD: Su                       |              |               |               |                 |              |               |                    |

|       | Set to '1' by ware writes I     |              |               |               |                 |              |               |                    |

|       | detection of                    |              | ``            | •             | wallcup) of     |              | own through   |                    |

|       | 0: USB0 not                     |              | • •           |               |                 |              |               |                    |

|       | 1: USB0 in s                    |              |               |               |                 |              |               |                    |

| Bit0: | SUSEN: Sus                      |              |               |               |                 | alama Barra  |               |                    |

|       | 0: Suspend of 1: Suspend of     |              |               |               |                 |              |               | nd signalin        |

|       | 1. Suspend (                    |              |               |               |                 |              | 2013 303081   |                    |

## 16.11. Configuring Endpoints1-3

Endpoints1-3 are configured and controlled through their own sets of the following control/status registers: IN registers EINCSRL and EINCSRH, and OUT registers EOUTCSRL and EOUTCSRH. Only one set of endpoint control/status registers is mapped into the USB register address space at a time, defined by the contents of the INDEX register (USB Register Definition 16.4).

Endpoints1-3 can be configured as IN, OUT, or both IN/OUT (Split Mode) as described in **Section 16.5.1**. The endpoint mode (Split/Normal) is selected via the SPLIT bit in register EINCSRH.

When SPLIT = '1', the corresponding endpoint FIFO is split, and both IN and OUT pipes are available.

When SPLIT = '0', the corresponding endpoint functions as either IN or OUT; the endpoint direction is selected by the DIRSEL bit in register EINCSRH.

## 16.12. Controlling Endpoints1-3 IN

Endpoints1-3 IN are managed via USB registers EINCSRL and EINCSRH. All IN endpoints can be used for Interrupt, Bulk, or Isochronous transfers. Isochronous (ISO) mode is enabled by writing '1' to the ISO bit in register EINCSRH. Bulk and Interrupt transfers are handled identically by hardware.

An Endpoint1-3 IN interrupt is generated by any of the following conditions:

- 1. An IN packet is successfully transferred to the host.

- 2. Software writes '1' to the FLUSH bit (EINCSRL.3) when the target FIFO is not empty.

- 3. Hardware generates a STALL condition.

#### 16.12.1.Endpoints1-3 IN Interrupt or Bulk Mode

When the ISO bit (EINCSRH.6) = '0' the target endpoint operates in Bulk or Interrupt Mode. Once an endpoint has been configured to operate in Bulk/Interrupt IN mode (typically following an Endpoint0 SET\_IN-TERFACE command), firmware should load an IN packet into the endpoint IN FIFO and set the INPRDY bit (EINCSRL.0). Upon reception of an IN token, hardware will transmit the data, clear the INPRDY bit, and generate an interrupt.

## 17. SMBus

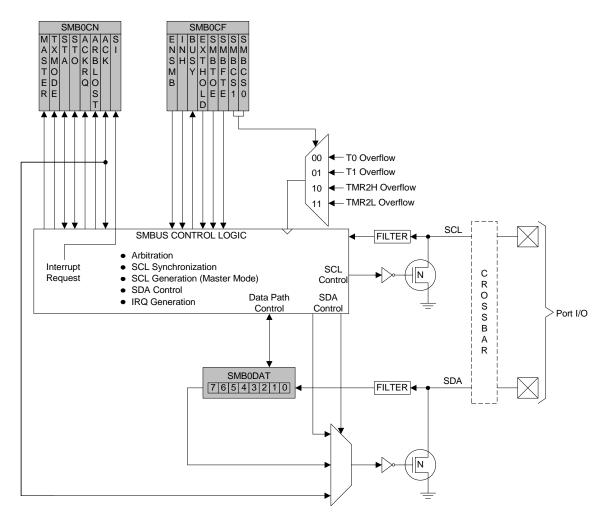

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I2C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock as a master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The SMBus interface may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. Three SFRs are associated with the SMBus: SMB0CF configures the SMBus; SMB0CN controls the status of the SMBus; and SMB0DAT is the data register, used for both transmitting and receiving SMBus data and slave addresses.

Figure 17.1. SMBus Block Diagram

SMBus configuration options include:

- Timeout detection (SCL Low Timeout and/or Bus Free Timeout)

- SDA setup and hold time extensions

- Slave event enable/disable

- Clock source selection

These options are selected in the SMB0CF register, as described in **Section "17.4.1. SMBus Configura**tion Register" on page 192.

#### 17.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes, select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however, the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of the current transfer).

| SMBCS1 | SMBCS0 | SMBus Clock Source         |

|--------|--------|----------------------------|

| 0      | 0      | Timer 0 Overflow           |

| 0      | 1      | Timer 1 Overflow           |

| 1      | 0      | Timer 2 High Byte Overflow |

| 1      | 1      | Timer 2 Low Byte Overflow  |

#### Table 17.1. SMBus Clock Source Selection

The SMBCS1-0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 17.1. Note that the selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in **Section "21. Timers" on page 235**.

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

## Equation 17.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 17.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 17.2.

$$BitRate = \frac{f_{ClockSourceOverflow}}{3}$$

## Equation 17.2. Typical SMBus Bit Rate

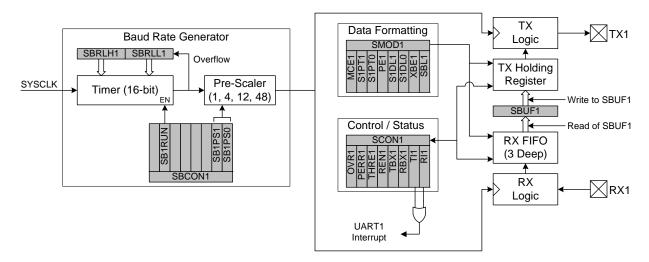

## 19. UART1 (C8051F340/1/4/5/8/A/B/C Only)

UART1 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates (details in **Section "19.1. Baud Rate Generator" on page 214**). A received data FIFO allows UART1 to receive up to three data bytes before data is lost and an overflow occurs.

UART1 has six associated SFRs. Three are used for the Baud Rate Generator (SBCON1, SBRLH1, and SBRLL1), two are used for data formatting, control, and status functions (SCON1, SMOD1), and one is used to send and receive data (SBUF1). The single SBUF1 location provides access to both the transmit holding register and the receive FIFO. Writes to SBUF1 always access the Transmit Holding Register. Reads of SBUF1 always access the first byte of the Receive FIFO; it is not possible to read data from the Transmit Holding Register.

With UART1 interrupts enabled, an interrupt is generated each time a transmit is completed (TI1 is set in SCON1), or a data byte has been received (RI1 is set in SCON1). The UART1 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART1 interrupt (transmit complete or receive complete). Note that if additional bytes are available in the Receive FIFO, the RI1 bit cannot be cleared by software.

Figure 19.1. UART1 Block Diagram

## 19.1. Baud Rate Generator

The UART1 baud rate is generated by a dedicated 16-bit timer which runs from the controller's core clock (SYSCLK), and has prescaler options of 1, 4, 12, or 48. The timer and prescaler options combined allow for a wide selection of baud rates over many SYSCLK frequencies.

The baud rate generator is configured using three registers: SBCON1, SBRLH1, and SBRLL1. The UART1 Baud Rate Generator Control Register (SBCON1, SFR Definition 19.4) enables or disables the baud rate generator, and selects the prescaler value for the timer. The baud rate generator must be enabled for UART1 to function. Registers SBRLH1 and SBRLL1 contain a 16-bit reload value for the dedicated 16-bit timer. The internal timer counts up from the reload value on every clock tick. On timer overflows (0xFFFF to 0x0000), the timer is reloaded. For reliable UART operation, it is recommended that the UART baud rate is not configured for baud rates faster than SYSCLK/16. The baud rate for UART1 is defined in Equation 19.1.

Baud Rate =  $\frac{\text{SYSCLK}}{(65536 - (\text{SBRLH1:SBRLL1}))} \times \frac{1}{2} \times \frac{1}{\text{Prescaler}}$

#### Equation 19.1. UART1 Baud Rate

A quick reference for typical baud rates and system clock frequencies is given in Table 19.1.

|        | Target Baud<br>Rate (bps) | Actual Baud<br>Rate (bps) | Baud Rate<br>Error | Oscillator<br>Divide<br>Factor | SB1PS[1:0]<br>(Prescaler Bits) | Reload Value in SBRLH1:SBRLL1 |

|--------|---------------------------|---------------------------|--------------------|--------------------------------|--------------------------------|-------------------------------|

|        | 230400                    | 230769                    | 0.16%              | 52                             | 11                             | 0xFFE6                        |

| N      | 115200                    | 115385                    | 0.16%              | 104                            | 11                             | 0xFFCC                        |

| MHz    | 57600                     | 57692                     | 0.16%              | 208                            | 11                             | 0xFF98                        |

| 12     | 28800                     | 28846                     | 0.16%              | 416                            | 11                             | 0xFF30                        |

| Ш      | 14400                     | 14388                     | 0.08%              | 834                            | 11                             | 0xFE5F                        |

| SCLK   | 9600                      | 9600                      | 0.0%               | 1250                           | 11                             | 0xFD8F                        |

| SC     | 2400                      | 2400                      | 0.0%               | 5000                           | 11                             | 0xF63C                        |

| S      | 1200                      | 1200                      | 0.0%               | 10000                          | 11                             | 0xEC78                        |

|        | 230400                    | 230769                    | 0.16%              | 104                            | 11                             | 0xFFCC                        |

| 부      | 115200                    | 115385                    | 0.16%              | 208                            | 11                             | 0xFF98                        |

| MHz    | 57600                     | 57692                     | 0.16%              | 416                            | 11                             | 0xFF30                        |

| 24     | 28800                     | 28777                     | 0.08%              | 834                            | 11                             | 0xFE5F                        |

|        | 14400                     | 14406                     | 0.04%              | 1666                           | 11                             | 0xFCBF                        |

| SYSCLK | 9600                      | 9600                      | 0.0%               | 2500                           | 11                             | 0xFB1E                        |

| S<br>S | 2400                      | 2400                      | 0.0%               | 10000                          | 11                             | 0xEC78                        |

| S      | 1200                      | 1200                      | 0.0%               | 20000                          | 11                             | 0xD8F0                        |

|        | 230400                    | 230769                    | 0.16%              | 208                            | 11                             | 0xFF98                        |

| 부      | 115200                    | 115385                    | 0.16%              | 416                            | 11                             | 0xFF30                        |

| MHz    | 57600                     | 57554                     | 0.08%              | 834                            | 11                             | 0xFE5F                        |

| 48     | 28800                     | 28812                     | 0.04%              | 1666                           | 11                             | 0xFCBF                        |

|        | 14400                     | 14397                     | 0.02%              | 3334                           | 11                             | 0xF97D                        |

| SYSCLK | 9600                      | 9600                      | 0.0%               | 5000                           | 11                             | 0xF63C                        |

| ,SC    | 2400                      | 2400                      | 0.0%               | 20000                          | 11                             | 0xD8F0                        |

| ŝ      | 1200                      | 1200                      | 0.0%               | 40000                          | 11                             | 0xB1E0                        |

## Table 19.1. Baud Rate Generator Settings for Standard Baud Rates

## SFR Definition 19.2. SMOD1: UART1 Mode

| R/W      | R/W                                                                                           | R/W        | R/W          | R/W           | R/W         | R/W           | R/W         | Reset Value |  |  |

|----------|-----------------------------------------------------------------------------------------------|------------|--------------|---------------|-------------|---------------|-------------|-------------|--|--|

| MCE1     | S1PT1                                                                                         | S1PT0      | PE1          | S1DL1         | S1DL0       | XBE1          | SBL1        | 00001100    |  |  |

| Bit7     | Bit6                                                                                          | Bit5       | Bit4         | Bit3          | Bit2        | Bit1          | Bit0        |             |  |  |

|          | SFR Address: 0xE5                                                                             |            |              |               |             |               |             |             |  |  |

|          |                                                                                               |            |              |               |             |               |             |             |  |  |

| Bit7:    | MCE1: Multi                                                                                   | •          |              |               |             |               |             |             |  |  |

|          | 0: RI will be activated if stop bit(s) are '1'.                                               |            |              |               |             |               |             |             |  |  |

|          | 1: RI will be activated if stop bit(s) and extra bit are '1' (extra bit must be enabled using |            |              |               |             |               |             |             |  |  |

|          | XBE1).<br>Note: This function is not available when hardware parity is enabled.               |            |              |               |             |               |             |             |  |  |

|          |                                                                                               |            | ot available | when hard     | vare parity | is enabled.   |             |             |  |  |

| DIISO-D. | S1PT[1:0]: F<br>00: Odd                                                                       | anty type. |              |               |             |               |             |             |  |  |

|          | 00. Odd<br>01: Even                                                                           |            |              |               |             |               |             |             |  |  |

|          | 10: Mark                                                                                      |            |              |               |             |               |             |             |  |  |

|          | 11: Space                                                                                     |            |              |               |             |               |             |             |  |  |

| Bit4:    | PE1: Parity                                                                                   | Enable.    |              |               |             |               |             |             |  |  |

|          | This bit activates hardware parity generation and checking. The parity type is selected by    |            |              |               |             |               |             |             |  |  |

|          | bits S1PT1-0 when parity is enabled.                                                          |            |              |               |             |               |             |             |  |  |

|          | 0: Hardware parity is disabled.                                                               |            |              |               |             |               |             |             |  |  |

|          | 1: Hardware parity is enabled.                                                                |            |              |               |             |               |             |             |  |  |

| Bits3–2: | S1DL[1:0]: [                                                                                  |            |              |               |             |               |             |             |  |  |

|          | 00: 5-bit data                                                                                |            |              |               |             |               |             |             |  |  |

|          | 01: 6-bit data                                                                                |            |              |               |             |               |             |             |  |  |

|          | 10: 7-bit data<br>11: 8-bit data                                                              |            |              |               |             |               |             |             |  |  |

| Bit1:    | XBE1: Extra                                                                                   |            |              |               |             |               |             |             |  |  |

| Ditt.    | When enable                                                                                   |            | e of TBX1    | will be appe  | nded to the | data field    |             |             |  |  |

|          | 0: Extra Bit [                                                                                |            |              |               |             |               |             |             |  |  |

|          | 1: Extra Bit B                                                                                | Enabled.   |              |               |             |               |             |             |  |  |

| Bit0:    | SBL1: Stop                                                                                    | Bit Length |              |               |             |               |             |             |  |  |

|          | 0: Short - Ste                                                                                | •          |              |               |             |               |             |             |  |  |

|          | 1: Long - Sto                                                                                 | •          | ve for two b | oit times (da | ta length = | 6, 7, or 8 bi | ts), or 1.5 | bit times   |  |  |

|          | (data length                                                                                  | = 5 bits). |              |               |             |               |             |             |  |  |

|          |                                                                                               |            |              |               |             |               |             |             |  |  |

| L        |                                                                                               |            |              |               |             |               |             |             |  |  |

## C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

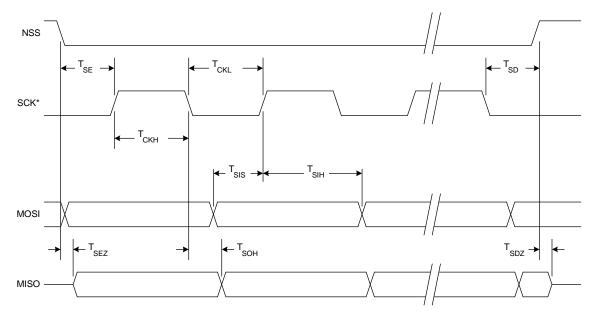

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

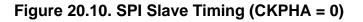

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 20.11. SPI Slave Timing (CKPHA = 1)

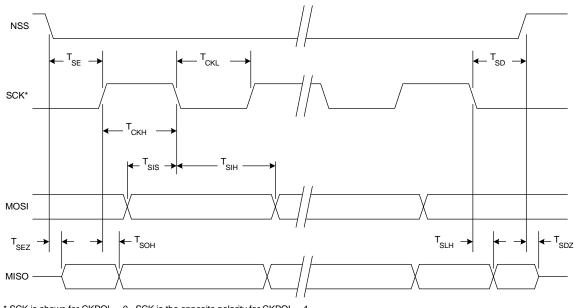

## 21.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode, (split) 8-bit auto-reload mode, USB Start-of-Frame (SOF) capture mode, or Low-Frequency Oscillator (LFO) Falling Edge capture mode. The Timer 2 operation mode is defined by the T2SPLIT (TMR2CN.3), T2CE (TMR2CN.4) bits, and T2CSS (TMR2CN.1) bits.

Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 2 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 21.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT = '0' and T2CE = '0', Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 21.4, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled, an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x000.

Figure 21.4. Timer 2 16-Bit Mode Block Diagram

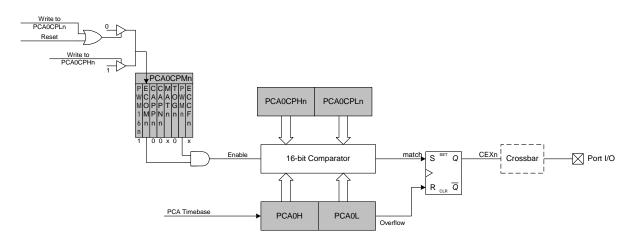

#### 22.2.6. 16-Bit Pulse Width Modulator Mode

A PCA module may also be operated in 16-Bit PWM mode. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. The duty cycle for 16-Bit PWM Mode is given by Equation 22.3.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

$$DutyCycle = \frac{(65536 - PCA0CPn)}{65536}$$

#### Equation 22.3. 16-Bit PWM Duty Cycle

Using Equation 22.3, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

Figure 22.9. PCA 16-Bit PWM Mode

## 22.4. Register Descriptions for PCA

Following are detailed descriptions of the special function registers related to the operation of the PCA.

## SFR Definition 22.1. PCA0CN: PCA Control

| ~ -   | R/W                                                                                                            | R/W                                                                                                                | R/W                                                                                                                | R/W                                                                                                            | R/W                                                                                      | R/W                                                                                      | R/W                                                                                  | Reset Value                                            |

|-------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------|

| CF    | CR                                                                                                             | -                                                                                                                  | CCF4                                                                                                               | CCF3                                                                                                           | CCF2                                                                                     | CCF1                                                                                     | CCF0                                                                                 | 00000000                                               |

| Bit7  | Bit6                                                                                                           | Bit5                                                                                                               | Bit4                                                                                                               | Bit3                                                                                                           | Bit2                                                                                     | Bit1                                                                                     | Bit0                                                                                 | SFR Addres                                             |

|       |                                                                                                                |                                                                                                                    |                                                                                                                    |                                                                                                                |                                                                                          | (bit                                                                                     | addressable                                                                          | ) 0xD8                                                 |

| Bit7: | CF: PCA Co                                                                                                     | unter/Time                                                                                                         | r Overflow F                                                                                                       | lag.                                                                                                           |                                                                                          |                                                                                          |                                                                                      |                                                        |

|       | Set by hardv                                                                                                   | vare when                                                                                                          | the PCA Co                                                                                                         | unter/Timer                                                                                                    | overflows f                                                                              | rom 0xFFFI                                                                               | to 0x000                                                                             | 0. When the                                            |

|       | Counter/Tim                                                                                                    | er Overflov                                                                                                        | v (CF) interr                                                                                                      | upt is enabl                                                                                                   | ed, setting                                                                              | this bit caus                                                                            | ses the CP                                                                           | U to vector                                            |

|       | to the PCA in                                                                                                  | nterrupt se                                                                                                        | rvice routine                                                                                                      | . This bit is                                                                                                  | not automa                                                                               | tically clear                                                                            | ed by harc                                                                           | lware and                                              |

|       | must be clea                                                                                                   | red by sof                                                                                                         | ware.                                                                                                              |                                                                                                                |                                                                                          |                                                                                          |                                                                                      |                                                        |

| Bit6: | CR: PCA Co                                                                                                     | unter/Time                                                                                                         | r Run Contr                                                                                                        | ol.                                                                                                            |                                                                                          |                                                                                          |                                                                                      |                                                        |

|       | This bit enab                                                                                                  | les/disable                                                                                                        | es the PCA (                                                                                                       | Counter/Tim                                                                                                    | ner.                                                                                     |                                                                                          |                                                                                      |                                                        |

|       | 0: PCA Cour                                                                                                    |                                                                                                                    |                                                                                                                    |                                                                                                                |                                                                                          |                                                                                          |                                                                                      |                                                        |

|       | 1: PCA Cour                                                                                                    |                                                                                                                    |                                                                                                                    |                                                                                                                |                                                                                          |                                                                                          |                                                                                      |                                                        |

| Bit5: | UNUSED. R                                                                                                      | ,                                                                                                                  |                                                                                                                    |                                                                                                                |                                                                                          |                                                                                          |                                                                                      |                                                        |

| Bit4: | CCF4: PCA                                                                                                      |                                                                                                                    |                                                                                                                    |                                                                                                                |                                                                                          |                                                                                          |                                                                                      |                                                        |

|       | This bit is se                                                                                                 |                                                                                                                    |                                                                                                                    |                                                                                                                | •                                                                                        |                                                                                          |                                                                                      | •                                                      |

|       | enabled, set                                                                                                   | -                                                                                                                  |                                                                                                                    |                                                                                                                |                                                                                          | •                                                                                        |                                                                                      | outine. Thi                                            |

|       | bit is not aut                                                                                                 |                                                                                                                    |                                                                                                                    |                                                                                                                | d must be o                                                                              | cleared by s                                                                             | software.                                                                            |                                                        |

| Bit3: | CCF3: PCA                                                                                                      |                                                                                                                    |                                                                                                                    |                                                                                                                |                                                                                          | a Mhaath                                                                                 | а ООГО ind                                                                           | annunt in                                              |

|       | This bit is se                                                                                                 |                                                                                                                    |                                                                                                                    |                                                                                                                |                                                                                          |                                                                                          |                                                                                      |                                                        |

|       | enabled, set<br>bit is not aut                                                                                 | •                                                                                                                  |                                                                                                                    |                                                                                                                |                                                                                          |                                                                                          |                                                                                      |                                                        |

| Bit2: | CCF2: PCA                                                                                                      |                                                                                                                    |                                                                                                                    |                                                                                                                |                                                                                          | Sleared by s                                                                             | onware.                                                                              |                                                        |

|       |                                                                                                                |                                                                                                                    |                                                                                                                    |                                                                                                                |                                                                                          |                                                                                          |                                                                                      |                                                        |